改善信号链路阻抗的方法、装置、pcb板、设备、介质

技术领域

1.本发明涉及pcb设计技术领域,具体涉及一种改善信号链路阻抗的方法、装置、pcb板、设备、介质。

背景技术:

2.在目前高速服务器主板设计中,随着高速信号速率的提升,为满足高速信号长距离传输质量,设计开发者通常会采用电性能较好的板材,管控pcb上走线及连接器线缆等部件的生产加工阻抗质量及优化改善信号耦合传输时的串扰控制等方式来提升信号传输质量。

3.为满足服务器主板上高速信号在长距离互连时的信号传输质量,通常会采用电性较好的板材,管控pcb上走线及连接器线缆阻抗及优化高速差分对间耦合串扰等方式设计,在pcb布线时,因部分器件的球状矩阵排列引脚区域本身结构设计问题,差分对走线布线时,通常是球状矩阵排列引脚区域以适应物理结构空间允许下的线宽尺寸布线,而在非球状矩阵排列引脚区域将以满足目标设计阻抗值的标准线宽尺寸进行布线。

4.因叠层设计各参数指标不变,这样信号由球状矩阵排列引脚区域路径到非球状矩阵排列引脚区域差分对走线会存两种差分对走线尺寸,因在相同叠层参数设计下,标准线宽是按目标阻抗设计的,当切换成球状矩阵排列引脚区域的线宽数值时,其阻抗值会偏高,因而造成信号传输路径上阻抗不连续问题,导致信号反射增加,从而降低了信号传输质量。

技术实现要素:

5.针对因而造成信号传输路径上阻抗不连续问题,导致信号反射增加,从而降低了信号传输质量的问题,本发明提供一种改善信号链路阻抗的方法、装置、pcb板、设备、介质。

6.本发明的技术方案是:

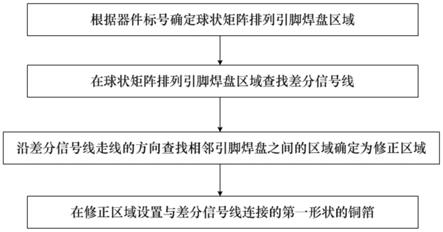

7.第一方面,本发明技术方案提供一种改善信号链路阻抗的方法,包括如下步骤:

8.根据器件标号确定球状矩阵排列引脚焊盘区域;

9.在球状矩阵排列引脚焊盘区域查找差分信号线;

10.沿差分信号线走线的方向查找相邻引脚焊盘之间的区域确定为修正区域;

11.在修正区域设置与差分信号线连接的第一形状的铜箔。

12.修正区域指的是两个差分信号对之间的相邻的两个引脚焊盘之间的区域。修正区域是指需要在该区域进行走线链路改进的区域。在修正区域设置与差分信号线连接的第一形状的铜箔,实际上是,增大部分差分信号线的宽度,来整体提高差分信号线的阻抗值。

13.进一步的,沿差分信号线走线的方向查找相邻引脚焊盘之间的区域确定为修正区域的步骤包括:

14.每对差分信号线的两侧分别确定一排引脚焊盘;

15.每一排引脚焊盘中相邻的引脚焊盘之间的区域确定为修正区域。本步骤中确定修正区域的目的是找到能增大差分信号线宽度的区域。

16.进一步的,每对差分信号线包括左侧差分信号线和右侧差分信号线;在修正区域设置与差分信号线连接的第一形状的铜箔的步骤包括:

17.在与左侧差分信号线相邻的一排引脚焊盘的修正区域设置与左侧差分信号线连接的第一形状的铜箔;

18.在与右侧差分信号线相邻的一排引脚焊盘的修正区域设置与右侧差分信号线连接的第一形状的铜箔。也就是在同一个修正区域,左侧差分信号线需要加宽,右侧差分信号线也需要加宽,需要说明的是,在所有的修正区域差分信号线的加宽的值是相同的,进一步的,要求第一形状的铜箔的周长和面积相同,即,形状和大小相同。

19.进一步的,该方法还包括:

20.第一对差分信号线中的右侧差分信号线连接的第一形状的铜箔与第二对差分信号线中的左侧差分信号线连接的第一形状的铜箔之间的距离大于第一阈值。增大差分信号线的宽度,但是需要保证,差分信号的走线之间需要一定的间隔,防止影响pcb板的性能。

21.进一步的,第一形状包括六边形,六边形的铜箔的两个顶点设置在与该六边形的铜箔连接的差分信号线上。

22.第二方面,本发明技术方案提供一种改善信号链路阻抗的装置,包括引脚区域确定模块、差分信号线查找模块、修正区域确定模块、设置执行模块;

23.引脚区域确定模块,用于根据器件标号确定球状矩阵排列引脚焊盘区域;

24.差分信号线查找模块,用于在球状矩阵排列引脚焊盘区域查找差分信号线;

25.修正区域确定模块,用于沿差分信号线的走线方向查找相邻引脚焊盘之间的区域确定为修正区域;

26.设置执行模块,用于在修正区域设置与差分信号线连接的第一形状的铜箔。在修正区域设置与差分信号线连接的第一形状的铜箔,实际上是,增大部分差分信号线的宽度,来整体提高差分信号线的阻抗值。

27.进一步的,修正区域确定模块包括第一确定单元、第二确定单元;

28.第一确定单元,用于在每对差分信号线的两侧分别确定一排引脚焊盘;

29.第二确定单元,用于将每一排引脚焊盘中相邻的引脚焊盘之间的区域确定为修正区域。确定修正区域的目的是找到能增大差分信号线宽度的区域。

30.进一步的,每对差分信号线包括左侧差分信号线和右侧差分信号线;

31.设置执行模块,具体用于在与左侧差分信号线相邻的一排引脚焊盘的修正区域设置与左侧差分信号线连接的第一形状的铜箔;在与右侧差分信号线相邻的一排引脚焊盘的修正区域设置与右侧差分信号线连接的第一形状的铜箔,其中,第一对差分信号线中的右侧差分信号线连接的第一形状的铜箔与第二对差分信号线中的左侧差分信号线连接的第一形状的铜箔之间的距离大于第一阈值。也就是在同一个修正区域,左侧差分信号线需要加宽,右侧差分信号线也需要加宽,需要说明的是,在所有的修正区域差分信号线的加宽的值是相同的,进一步的,要求第一形状的铜箔的周长和面积相同,即,形状和大小相同。

32.进一步的,第一形状包括六边形;

33.设置执行模块,用于将六边形的铜箔的两个顶点设置在与该六边形的铜箔连接的差分信号线上。

34.第三方面,本发明技术方案还提供一种改善信号链路阻抗的pcb板,所述的pcb板

为通过第一方面所述的改善信号链路阻抗的方法设计的pcb板。

35.pcb板上设置有球状矩阵排列引脚的器件,在球状矩阵排列引脚焊盘的区域布设有差分信号对,相邻的差分信号对之间设置一排引脚焊盘,每排引脚焊盘中相邻的两个引脚焊盘之间的区域为修正区域,每对差分信号线包括左侧差分信号线和右侧差分信号线,在与左侧差分信号线相邻的一排引脚焊盘的修正区域设置与左侧差分信号线连接的第一形状的铜箔;该修正区域设置与右侧差分信号线连接的第一形状的铜箔。

36.第四方面,本发明技术方案还提供一种计算机设备,包括处理器和存储器,所述处理器和所述存储器通过总线完成相互间的通信;所述存储器存储有可被所述处理器执行的程序指令,所述处理器调用所述程序指令能够执行如第一方面所述的改善信号链路阻抗的方法。

37.第五方面,本发明技术方案还提供一种非暂态计算机可读存储介质,所述非暂态计算机可读存储介质存储计算机指令,所述计算机指令使所述计算机执行如第一方面所述的改善信号链路阻抗的方法。

38.从以上技术方案可以看出,本发明具有以下优点:可以有效降低信号传输链路上球状矩阵排列引脚区域路径到非球状矩阵排列引脚区域间的阻抗不连接,造成阻抗反射偏大的问题,以此进一步提升高频信号的传输质量,同时可作为设计指标为其他项目高速信号设计参考使用。

39.此外,本发明设计原理可靠,结构简单,具有非常广泛的应用前景。

40.由此可见,本发明与现有技术相比,具有突出的实质性特点和显著地进步,其实施的有益效果也是显而易见的。

附图说明

41.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

42.图1是本发明一个实施例的方法的示意性流程图。

43.图2是本发明一个实施例的装置的示意性框图。

44.图3是本发明实施例提供的pcb板示意图。

45.图4是本发明实施例提供的六边形铜箔示意图。

46.图5是本发明实施例提供的六边形铜箔的尺寸。

具体实施方式

47.为满足服务器主板上高速信号在长距离互连时的信号传输质量,通常会采用电性较好的板材,管控pcb上走线及连接器线缆阻抗及优化高速差分对间耦合串扰等方式设计,在pcb布线时,因部分器件的球状矩阵排列引脚区域本身结构设计问题,差分对走线布线时,通常是球状矩阵排列引脚区域以适应物理结构空间允许下的线宽尺寸布线,而在非球状矩阵排列引脚区域将以满足目标设计阻抗值的标准线宽尺寸进行布线。

48.因叠层设计各参数指标不变,这样信号由球状矩阵排列引脚区域路径到非球状矩阵排列引脚区域差分对走线会存两种差分对走线尺寸,因在相同叠层参数设计下,标准线

宽是按目标阻抗设计的,当切换成球状矩阵排列引脚区域的线宽数值时,其阻抗值会偏高,因而造成信号传输路径上阻抗不连续问题,导致信号反射增加,从而降低了信号传输质量。本发明设计主要从信号传输链路的阻抗方面做进一步优化处理,即针对芯片球状矩阵排列引脚区域中走线进行优化改善,使此部分阻抗能值能尽量趋近与非球状矩阵排列引脚区域标准宽度走线的阻抗值,因而降低了信号在传输链路上阻抗不连续性,以减少高频信号反射效果来提升信号长距离传输时质量。

49.为了使本技术领域的人员更好地理解本发明中的技术方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

50.如图1所示,本发明实施例提供一种改善信号链路阻抗的方法,包括如下步骤:

51.步骤1:根据器件标号确定球状矩阵排列引脚焊盘区域;

52.本技术中提到的球状矩阵排列引脚指的是器件的引脚排列方式,比如cpu芯片;

53.步骤2:在球状矩阵排列引脚焊盘区域查找差分信号线;

54.差分信号的走线都是成对存在,每一对差分信号的走线变化趋势是相同的,也就是,走线弯的时候同时弯,走线直的时候同时直。

55.步骤3:沿差分信号线走线的方向查找相邻引脚焊盘之间的区域确定为修正区域;

56.修正区域指的是两个差分信号对之间的相邻的两个引脚焊盘之间的区域。修正区域是指需要在该区域进行走线链路改进的区域。

57.步骤4:在修正区域设置与差分信号线连接的第一形状的铜箔。

58.在修正区域设置与差分信号线连接的第一形状的铜箔,实际上是,增大部分差分信号的走线宽度,来整体提高差分信号线的阻抗值。

59.在有些实施例中,步骤3中,沿差分信号线走线的方向查找相邻引脚焊盘之间的区域确定为修正区域的步骤包括:

60.步骤31:每对差分信号线的两侧分别确定一排引脚焊盘;

61.步骤32:每一排引脚焊盘中相邻的引脚焊盘之间的区域确定为修正区域。

62.本步骤中确定修正区域的目的是找到能增大差分信号的走线宽度的区域。

63.每对差分信号线对包括左侧差分信号线和右侧差分信号线;在有些实施例中,步骤4中,在修正区域设置与差分信号线连接的第一形状的铜箔的步骤包括:

64.步骤41:在与左侧差分信号线相邻的一排引脚焊盘的修正区域设置与左侧差分信号线连接的第一形状的铜箔;

65.步骤42:在与右侧差分信号线相邻的一排引脚焊盘的修正区域设置与右侧差分信号线连接的第一形状的铜箔。

66.也就是在同一个修正区域,左侧差分信号线需要加宽,右侧差分信号线也需要加宽,需要说明的是,在所有的修正区域差分信号的走线的加宽的值是相同的,进一步的,要求第一形状的铜箔的周长和面积相同,即,形状和大小相同。

67.在有些实施例中,该方法还包括:

68.第一对差分信号线中的右侧差分信号线连接的第一形状的铜箔与第二对差分信

号线中的左侧差分信号线连接的第一形状的铜箔之间的距离大于第一阈值。

69.也就是说,增大差分信号的走线的宽度,但是需要保证,差分信号的走线之间需要一定的间隔,防止影响pcb板的性能。

70.在有些实施例中,第一形状包括六边形,六边形的铜箔的两个顶点设置在与该六边形的铜箔连接的差分信号线上。

71.为提高pcie5.0信号长距离传输质量,本发明提出一种改善pcie5.0信号链路阻抗质量的设计方法,通过在芯片bga pin field区域增加6边形shape铜箔,以此降低pin field区域窄线宽距差分对的阻抗值,从而,减少了bga pin field区域和open field区域之间的阻抗不连续问题,提升了信号传输质量,并作为设计指标,供其他项目开发时高速信号bga pin field区域中差分信号走线设计应用参考。

72.因叠层设计各参数指标不变,这样信号由球状矩阵排列引脚区域路径到非球状矩阵排列引脚区域差分对走线会存两种差分对走线尺寸,因在相同叠层参数设计下,标准线宽是按目标阻抗设计的,当切换成球状矩阵排列引脚区域的线宽数值时,其阻抗值会偏高,因而造成信号传输路径上阻抗不连续问题,导致信号反射增加,从而降低了信号传输质量。本发明设计主要从信号传输链路的阻抗方面做进一步优化处理,即针对芯片球状矩阵排列引脚区域中走线进行优化改善,使此部分阻抗能值能尽量趋近与非球状矩阵排列引脚区域标准宽度走线的阻抗值,因而降低了信号在传输链路上阻抗不连续性,以减少高频信号反射效果来提升信号长距离传输时质量。

73.如图2所示,本发明实施例提供一种改善信号链路阻抗的装置,包括引脚区域确定模块、差分信号线查找模块、修正区域确定模块、设置执行模块;

74.引脚区域确定模块,用于根据器件标号确定球状矩阵排列引脚焊盘区域;本技术中提到的球状矩阵排列引脚指的是器件的引脚排列方式,比如cpu芯片;

75.差分信号线查找模块,用于在球状矩阵排列引脚焊盘区域查找差分信号线;差分信号的走线都是成对存在,每一对差分信号的走线变化趋势是相同的,也就是,走线弯的时候同时弯,走线直的时候同时直。

76.修正区域确定模块,用于沿差分信号线走线的方向查找相邻引脚焊盘之间的区域确定为修正区域;修正区域指的是两个差分信号对之间的相邻的两个引脚焊盘之间的区域。修正区域是指需要在该区域进行走线链路改进的区域。

77.设置执行模块,用于在修正区域设置与差分信号线连接的第一形状的铜箔。在修正区域设置与差分信号线连接的第一形状的铜箔,实际上是,增大部分差分信号的走线的宽度,来整体提高差分信号的走线的阻抗值。

78.在有些实施例中,修正区域确定模块包括第一确定单元、第二确定单元;

79.第一确定单元,用于在每对差分信号线的两侧分别确定一排引脚焊盘;

80.第二确定单元,用于将每一排引脚焊盘中相邻的引脚焊盘之间的区域确定为修正区域。确定修正区域的目的是找到能增大差分信号的走线宽度的区域。

81.在有些实施例中,每对差分信号线包括左侧差分信号线和右侧差分信号线;

82.设置执行模块,具体用于在与左侧差分信号线相邻的一排引脚焊盘的修正区域设置与左侧差分信号线连接的第一形状的铜箔;在与右侧差分信号线相邻的一排引脚焊盘的修正区域设置与右侧差分信号线连接的第一形状的铜箔,其中,第一对差分信号线中的右

侧差分信号线连接的第一形状的铜箔与第二对差分信号线中的左侧差分信号线连接的第一形状的铜箔之间的距离大于第一阈值。

83.也就是在同一个修正区域,左侧差分信号的走线需要加宽,右侧差分信号的走线也需要加宽,需要说明的是,在所有的修正区域差分信号的走线的加宽的值是相同的,进一步的,要求第一形状的铜箔的周长和面积相同,即,形状和大小相同。

84.在有些实施例中,第一形状包括六边形;

85.设置执行模块,用于将六边形的铜箔的两个顶点设置在与该六边形的铜箔连接的差分信号线上。

86.因pcie5.0信号从芯片bga pin field到open field区域路径高速走线通常是在同一个叠层面上,因此叠层面对于pin field和open field两区域各阻抗计算参数一样,但pin field区域用的narrow width/spacing布线,而open field区域用normal width/spacing布线,因而,当open field区域模拟阻抗达到目标设计阻抗值时,其bga pin field区域的模拟阻抗值将比目标设计阻抗值偏高些,因而造成高速信号传输链路上阻抗不一致性问题,降低pcie5.0信号传输质量。

87.根据上述针对bga pin field区域阻抗偏高问题,本发明将采用在其narrow width走线线宽上加6边角tab shape,以增大差分对走线上的电容值,以此降低bga pin field区域的阻抗值,从而优化pcie5.0信号传输链路上的阻抗不一致性问题,提升pcie5.0信号传输质量。

88.如图3所示,本发明实施例还提供一种改善信号链路阻抗的pcb板,所述的pcb板为通过上述方法实施例中所述的改善信号链路阻抗的方法设计的pcb板。

89.pcb板上设置有球状矩阵排列引脚的器件,在球状矩阵排列引脚焊盘的区域布设有差分信号对100,相邻的差分信号对之间设置一排引脚焊盘,每排引脚焊盘200中相邻的两个引脚焊盘400之间的区域为修正区域600,每对差分信号线100包括左侧差分信号线101和右侧差分信号线102,在与左侧差分信号线101相邻的一排引脚焊盘的修正区域设置与左侧差分信号线101连接的第一形状的铜箔301;该修正区域设置与右侧差分信号线102连接的第一形状的铜箔302。

90.在有些实施例中,第一形状包括六边形;针对当前服务器主板设计开发,为实现pcie5.0高频信号长距离传输,通常会采用电性较好的pcb板材,管控pcb trace/connector连接器/cable阻抗及增加大差分对间耦合间距,以此降低差分对间耦合串扰噪声影响等方式提升pcie5.0信号传输质量,然而,对于pcie5.0信号传输路径上,因芯片bga pin field区域本身结构空间限制问题,其pcie5.0信号在此pin field(球状矩阵排列)区域路径,通常只能以3.5/4/3.5mil narrow width/spacing方式布线,然后,在到达open field(非球状矩阵排列)区域时,以满足目标阻抗值要求下的normal width/spacing方式进行布线。为满足open field区域上85ohm(欧姆)目标阻抗值要求,利用polar软件,在pp厚度为2.8mil,板材dk值为3.2时,模拟阻抗满足85ohm数值下的差分对线宽距为5.5/5.6/5.5mil,因bga pin field区域差分对通常和open field区域差分对同层布线,且因bga pin field本身结构空间限制,差分对需以线宽距3.5/4/3.5mil布线,再采用pp厚度为2.8mil,板材dk值为3.2时,其polar模拟bga pin field区域的阻抗值是95.25ohm,由此可见,bga pin field区域阻抗值会比open field区域阻抗值偏高较多,造成pcie5.0信号传输链路存在阻抗不一

致性问题,因信号反射作用增加,影响到pcie5.0信号传输质量。本发明提供的pcb板是在bga pin field区域3.5/4/3.5mil差分对上增加6边形shape铜箔,其增加的shape铜箔结构及尺寸要求如附图4和图5所示,将六边形的铜箔301的两个顶点设置在与该六边形的铜箔连接的差分信号线101上.将其导入芯片bga pin field区域narrow width差分对上路径,减少了高频信号链路上的阻抗反射影响,提升了pcie5.0信号传输质量。

91.本发明实施例提供的一种计算机设备,该设备可以包括:处理器、通信接口、存储器和总线,其中,处理器,通信接口,存储器通过总线完成相互间的通信。总线可以用于电子设备与传感器之间的信息传输。处理器可以调用存储器中的逻辑指令,以执行如下方法:步骤1:根据器件标号确定球状矩阵排列引脚焊盘区域;步骤2:在球状矩阵排列引脚焊盘区域查找差分信号线;步骤3:沿差分信号线走线的方向查找相邻引脚焊盘之间的区域确定为修正区域;步骤4:在修正区域设置与差分信号线连接的第一形状的铜箔。

92.在一些具体的实施例中,被处理器执行的程序指令,具体可以实现以下步骤:步骤31:每对差分信号线的两侧分别确定一排引脚焊盘;步骤32:每一排引脚焊盘中相邻的引脚焊盘之间的区域确定为修正区域。

93.在一些具体的实施例中,被处理器执行的程序指令,具体可以实现以下步骤:步骤41:在与左侧差分信号线相邻的一排引脚焊盘的修正区域设置与左侧差分信号线连接的第一形状的铜箔;步骤42:在与右侧差分信号线相邻的一排引脚焊盘的修正区域设置与右侧差分信号线连接的第一形状的铜箔。

94.此外,上述的存储器中的逻辑指令可以通过软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本发明各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、磁碟或者光盘等各种可以存储程序代码的介质。

95.本发明实施例提供一种非暂态计算机可读存储介质,该非暂态计算机可读存储介质存储计算机指令,该计算机指令使计算机执行上述方法实施例所提供的方法,例如包括:步骤1:根据器件标号确定球状矩阵排列引脚焊盘区域;步骤2:在球状矩阵排列引脚焊盘区域查找差分信号线;步骤3:沿差分信号线走线的方向查找相邻引脚焊盘之间的区域确定为修正区域;步骤4:在修正区域设置与差分信号线连接的第一形状的铜箔。

96.在一些具体的实施例中,所述可读存储介质中被处理器执行的程序指令,具体可以实现以下步骤:步骤31:每对差分信号线的两侧分别确定一排引脚焊盘;步骤32:每一排引脚焊盘中相邻的引脚焊盘之间的区域确定为修正区域。本技术中,每对差分信号线也称为差分信号线对。

97.在一些具体的实施例中,所述可读存储介质中被处理器执行的程序指令,具体可以实现以下步骤:步骤41:在与左侧差分信号线相邻的一排引脚焊盘的修正区域设置与左侧差分信号线连接的第一形状的铜箔;步骤42:在与右侧差分信号线相邻的一排引脚焊盘的修正区域设置与右侧差分信号线连接的第一形状的铜箔。

98.尽管通过参考附图并结合优选实施例的方式对本发明进行了详细描述,但本发明并不限于此。在不脱离本发明的精神和实质的前提下,本领域普通技术人员可以对本发明的实施例进行各种等效的修改或替换,而这些修改或替换都应在本发明的涵盖范围内/任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。