1.本发明属于功率半导体器件制造技术领域,具体涉及一种改进功率半导体器件性能的器件结构及制造方法。

背景技术:

2.目前生产的mos、igbt等功率半导体器件通常都是3个电极,即正面的源极或发射极、和栅极两个电极,以及背面的漏极或集电极一个电极。半导体产业的历程是从低频、小功率慢慢发展而来,伴随着器件应用的不同需要逐步向高频、大功率方向发展。

3.早期半导体器件的设计、制造水平都比较低下,因此生产工艺主要是追求简单、易行,显然一个电极方便焊接,两个电极容易造成电极短路,焊接工艺难控制,因此传统半导体器件制造都是将芯片漏极或集电极,也就是芯片的背面焊接、或是粘接到封装框架上;也正因为如此,该封装框架表面都是平整的,芯片背面焊接到框架后,正面通过打线方式将源极或发射极、和栅极连接到框架引线;近些年来为了适应半导体器件功率增加,需要降低封装阻抗,也发展了clip跳线等工艺。

4.虽然近期有很少量厂家最新推出了源极底置mos产品,也就是说源极连接到封装底座,但是无论是传统的正装工艺、clip跳线封装、还是最新发展而来的源极底置工艺,其封装框架底板一直都是平的,源极底置也仅仅是推出了少量小功率、低压、贴片封装的mos产品,至今没有推广到高压、大功率器件范畴。

5.因此,如何降低大功率半导体器件的热阻、提升功率半导体器件的散热性能、降低功率器件外壳的高频辐射、提升功率器件的开关频率特性已成为半导体大功率器件需要解决的问题。

技术实现要素:

6.为解决上述现有半导体器件技术中存在的问题,满足半导体技术应用市场功率持续加大的发展趋势,本发明采用如下技术方案:

7.一种功率半导体器件,其芯片源极或发射极直接焊接到封装框架,芯片发热经源极或发射极、通过封装框架底座传导向外散热;所述框架和功率芯片的源极或发射极、栅极焊接区域为凸起。

8.如附图2,为挤压成型的铜条,其中左边部分用于制作封装框架散热底座,右边用于制作框架电连接引脚部分,中间凸起部分用于制作源极或发射极、和栅极的焊接区。

9.所述功率半导体器件的制造方法:

10.功率芯片的源极或发射极、和栅极,对位贴合到封装框架用于焊接源极或发射极、和栅极的凸起部分,芯片和框架之间预制焊片、或焊料,通过加温使框架和芯片焊接,实现物理连接和电连接;框架凸起来的主要目的是为了保证芯片背面漏极或集电极、与器件框架的源极或发射极之间的最小物理距离,确保器件抗电压击穿能力;凸起的框架可以满足溢出的焊料流向其下部的框架,避免焊料横向延展造成电极之间出现短路现象。

11.由于芯片源极或发射极、栅极周边钝化保护层的疏锡特性、框架铜材料的亲锡特性、和焊料的重力作用,器件焊接过程中溢出的焊料,将流向芯片下部框架如图4(b)、4(c)、4(d)所示,可有效规避焊接过程中,功率器件电极之间产生短路。

12.所述框架的源极或发射极、栅极凸起区域为框架挤压成条状铜带后冲切成型制作,其他如化学腐蚀、以及机械切削等方式也能加工出所需框架,但是成本太高,除了可以用来研发新产品、试制样品外,缺少实际应用价值。

13.首先通过挤压方式制作封装框架条状铜材,该条状铜材对应焊接功率芯片源极或发射极、和栅极的区域凸出来;其凸起高度取决于功率器件的应用电压要求、芯片面积(也就是电流、或者功耗)要求、框架成型冲切工艺、以及铜材成本等多重因素。

14.具体来说:源极或发射极、与漏极或集电极击穿电压要求越高,其凸起高度要求越大;芯片面积(或者说功率)越大,焊接过程中溢出的焊料可能越多,其凸起高度要求越大;凸起高度越大,铜材消耗就多,将会造成成本上涨;与此同时凸起高度越大,机械冲切越困难,生产难度也会有所增加,乃至于增加框架源极和栅极之间的间距,缩小源极实际焊接面积,造成封装热阻的相应加大;因此框架凸起高度需综合考虑以上多重因素后确定,凸起高度一般在0.1-1mm。

15.封装框架制作过程中,保留焊接源极或发射极、和栅极凸起区域,其它部位如图3(a)、图3(b)通过机械冲切方式去除,确保芯片漏极或集电极与封装框架源极或发射极之间的最小绝缘距离;其它部位(如右侧电极引线部分,左侧螺栓固定孔位等等)一并经过冲切、和折弯处理形成封装框架,封装框架的表面处理同常规半导体器件封装办法相一致。

16.本技术方案的功率半导体器件可以是硅基、碳化硅、氮化镓、或其它化合物半导体mos、igbt等大功率器件;封装形式可以是to-220、to-263、to-247等普遍应用的标准封装形式,以及模块、或其它自定义非标封装结构。

17.本技术技术方案,总体生产工艺与普通功率半导体器件塑封工艺相类似,区别在于:

18.框架挤压成型时,将用于焊接芯片源极或发射极、栅极部位凸起来,其凸起高度的确定,取决于功率器件的应用电压要求、芯片面积(功率器件的功耗)要求、框架成型冲压工艺、以及铜材成本等多重因素。源极或发射极、与漏极或集电极击穿电压要求越高,其凸起高度要求越大;芯片面积越大,焊接过程中溢出的焊料可能越多,其凸起高度要求越大;凸起高度大,铜材消耗多,成本上涨,同时凸起高度越大,机械冲切越困难;因此需要综合考虑多方面因素后确定框架凸起高度。

19.为了避免焊料造成芯片电极之间发生短路现象,芯片周边框架凸起部位,在框架制造过程中,借助于冲切等加工方式,在框架成型过程中予以去除;

20.芯片正面,用于电连接的源极或发射极、栅极金属区,贴合到框架对应焊接凸起区域,不同于普通半导体器件漏极或集电极焊接到框架底座;

21.上芯过程中,增加芯片翻面加工步骤,普通半导体器件制作为背面焊接到框架,只需取片、然后放置到框架上就可以;本技术制造方式是将芯片正面贴合到框架上,需要增加芯片翻面这一操作步骤;

22.芯片正面源极、栅极金属层需要做不同的镀层处理,便于源极、栅极和框架的焊接;普通塑封半导体器件源极、栅极大多通过打线实现电连接,芯片正面一般是金属铝,倒

装后源极、栅极采用焊接工艺,芯片正面需要电镀铜、银或银合金层、金或金合金层、或者其它适合与铜框架焊接的镀层。漏极金属层则依据跳线、或者打铝带具体工艺要求,选择合适的金属材料。

23.其它如打线、打铝带、或者跳线连接芯片和框架引线,框架表面处理,塑封成型等等制造技术及要求,与普通功率半导体器件制造相一致。

24.有益效果

25.1、本发明方案对于半导体功率器件的性能改进是非常显著的,以n沟道mos为例,由于发射极通常都是接低电位,乃至于部分应用场所接地,还可以降低功率器件外壳的高频辐射;对于源极接地的应用中,器件发射极直接散热器、并接地,消除散热器寄生电容效应;能取到提升功率半导体器件的散热性能、载流能力、以及开关频率特性等实际效果。

26.2、本发明方案便于框架和芯片进行焊接,避免溢出的焊料造成源极或发射极与栅极、源极或发射极与漏极或集电极、和栅极与漏极或集电极之间出现焊接短路,降低生产难度提升成品率;

27.3、本发明方案增加芯片漏极或集电极与封装底座源极或发射极之间的物理距离,提升功率器件抗电压击穿能力,满足功率器件倒装技术在高压mos、和igbt等领域的应用。

28.4、本发明方案生产的功率半导体器件,和普通封装功率半导体器件外形一致、引脚排列一致,但是热阻降低一半以上,散热性能得到明显改善。

附图说明

29.图1为本发明的芯片结构示意图;

30.图2为本发明的挤压铜条结构示意图;

31.图3(a)为本发明的功率半导体器件铜框架结构示意图;

32.图3(b)为本发明的框架结构局部放大图;

33.图4(a)为本发明的芯片贴片、焊接加工示意图;

34.图4(b)、图4(c)、图4(d)分别为本发明的源极焊接区、栅极焊接区域局部放大详图;

35.图5为本发明实施例塑封后成品结构图。

36.上图1-5中,以mos为例说明:

37.1-功率芯片,11-功率芯片源极金属,111-功率芯片源极焊料层,12-功率芯片漏极金属,13-功率芯片栅极金属,131-功率芯片栅极焊料层,14-功率芯片钝化层保护区;

38.2-铜框架,21-铜框架源极、或源极引脚,211-铜框架与芯片源极金属焊接区,22-铜框架漏极、或漏极引脚,23-铜框架栅极、或栅极引脚,231-铜框架与芯片栅极金属焊接区。2l-铜框架左边部分,用于制作器件封装底座,并负责将功率芯片发热传递给散热器;2m-铜框架中间部分,其凸起面用于制作焊接芯片源极和栅极的凸出焊接平台;2r-铜框架右边部分,用于制作器件电极引脚。

具体实施方式

39.以下以功率mos器件为例结合附图具体说明本技术方案。

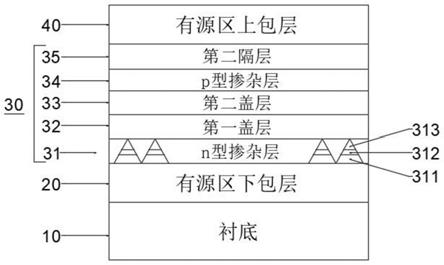

40.功率芯片设计制作如图1,功率半导体器件芯片,按照功率器件的应用参数要求,

设计制作功率芯片1;功率芯片1包括有芯片正面的源极11、和栅极13,以及电极之间的钝化保护层14,和芯片背面的漏极12;

41.功率芯片源极11直接焊接到封装框架2,与凸起的封装铜框架与芯片源极金属焊接区211相贴合,经过焊接后形成源极连接,芯片1发热经源极11、通过封装框架2传导向外散热;

42.功率芯片漏极12通过打线、或者clip跳线焊接到封装框架2,与封装铜框架漏极引脚22实现连接;

43.功率芯片栅极13直接焊接到封装框架2,与凸起的封装铜框架与芯片栅极金属焊接区231相贴合,经过焊接后形成栅极连接;

44.本实施例的功率芯片,是一款高压平面结构的mos器件,外形尺寸是4.5mm*3.1mm,厚度150um,设计击穿电压为650v,设计电流为10a;

45.具体框架制造方法如下:

46.本实施例是一款标准to-220铁封封装,首先将金属铜挤压成铜条如图2所示,其左边部分2l用于制作功率器件的散热底座,实际应用中承担器件与散热器的连接,并负责将功率芯片1的发热传导给散热器;其右边部分2r用于制作电极引脚,分别是源极引脚21、漏极引脚22、和栅极引脚23,实际应用中承担功率器件和应用电路一一对应的电连接;中间区2m向上凸起部分用于加工铜框架与芯片源极金属焊接区211、铜框架与芯片栅极金属焊接区231,分别与芯片的源极11、和栅极13电极对应焊接,实现功率器件的源极、和栅极连接。

47.如图3,按照图2挤压成型的铜条带,经过机械冲切、折弯加工后,形成正式封装用铜框架2;右边部分2r经过冲切和折弯后,制备形成器件源极引脚21、漏极引脚22、栅极引脚23。

48.如图3(a)、图3(b),对于框架凸起部分,除保留源极或发射极11焊接区211、栅极焊接区231外,芯片1周边的其它凸起区域、以及源极或发射极11和栅极13中间区域通过机械冲切去除。

49.关于框架的凸起高度:源极、与漏极击穿电压要求越高,为了满足足够的漏极和源极之间的最小物理距离,其凸起高度要求越大;功率越大,要求芯片面积越大,焊接过程中溢出的焊料可能越多,也就更容易造成电极之间的短路发生,因此为了尽量规避电极短路发生,其凸起高度要求越大;另一方面凸起高度大,铜材消耗多,成本上涨越多;此外凸起高度越大,框架的厚度越厚,机械冲切将更加困难,生产难度也会有所增加,乃至于必须增加框架源极和栅极之间的间距,缩小源极实际焊接面积,造成封装热阻的相应加大;因此框架凸起高度是综合考虑以上多重因素后确定的,本实施例凸起高度为0.3mm,框架源极和栅极之间的间距为0.6mm。

50.完成芯片设计制造、和专用框架制备后,接着是与普通功率半导体器件制造相类似的封装、测试各项工作,具体步骤简述如下:

51.1、上锡:铜框架源极21、栅极23对应部位印刷锡膏,或者预先放置焊片、或焊料;

52.2、上芯:如图4(a),不同于普通功率半导体器件制造方法;将功率芯片1翻面,并对应贴合到铜框架2上;如图4(a)所示,将芯片1正面的源极11、栅极13与框架凸起区源极211、栅极231对位贴合;正装工艺由于是芯片背面,也就是漏极焊接到封装框架,只需要将芯片放置到框架上就行,而不需要翻面这一道工序。

53.3、漏极跳线:在芯片漏极12和框架漏极22引脚之间放置电连接片和适量的锡膏;

54.4、加温、焊接:如图4(a),将功率芯片1的源极11、栅极13,和框架源极焊接区211、栅极焊接区231对位贴合好后,贴合好的芯片和框架经过加温,焊料熔接将芯片1与框架2焊接到一起;同时形成芯片1与框架2之间的,芯片源极11与框架21、芯片栅极13与框架23、芯片漏极12与框架22的电连接;

55.芯片漏极12与框架22也可以选择在完成源极、和栅极焊接后,通过打线方式实现电连接。

56.如图4(b)、4(c)、4(d)放大说明焊接局部细节所示,焊接过程中芯片1和框架2之间溢出的焊料,由于芯片1钝化层14的疏锡特性、铜框架2金属铜的亲锡特性、和焊料的重力作用,流向下部的铜框架2,而不是横向延展跨越钝化层14造成源极11、栅极13短路,更不会跨越钝化层14、并向上延展,造成源极11与漏极12,或者栅极13与漏极12之间的短路。

57.5、清洁焊接残留物:与普通功率器件封装工艺类似,加温焊接后清理、清洁焊接残留物,增加器件的可靠性和使用寿命。

58.6、塑封成型:如图5本案例是一款标准to-220铁封形式,经过贴片、焊接等工序加工还不是最终产品,需要进行塑封保护。如图5所示本技术方案制造的功率半导体器件产品,和普通封装功率半导体器件外形一致、引脚排列一致。

59.7、测试:将制备完成的产品,按照技术要求进行测试筛选,剔除不合格产品,就完成了本发明所需要的正式产品。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。