1.本发明实施例涉及半导体技术领域,特别涉及一种时钟产生电路、存储器以及时钟占空比校准方法。

背景技术:

2.半导体存储器被用于许多电子系统中,以存储可取回的数据。随着对电子系统更快、具有更大数据容量和消耗更少电力的需求不断增长,为了满足不断变化的需求,半导体存储器可能需要更快的速度,存储更多的数据并使用更少的电力。

3.通常的,通过向存储器提供命令(commands)、存储地址(memory address)以及时钟(clocks)来控制半导体存储器,且各种命令、存储地址以及时钟可以由存储控制器(memory controller)提供。这三类信号可以控制存储器执行各种存储操作,例如从存储器中读取数据的读取操作,以及将数据存储到存储器的写入操作。基于与存储器接收到的“相关命令”相关的已知时序,在存储器与存储控制器之间传输数据。具体地,可以向存储器提供用于对命令和地址进行计时的系统时钟(system clock),进一步地,还可以向存储器提供数据时钟(data clock),该数据时钟用于作为读取数据的时序以及写入数据的时序。此外,存储器还可以向控制器提供时钟,以作为向控制器传输数据的时序。提供给存储器的外部时钟用于产生内部时钟,这些内部时钟在存储器的存储操作期间控制各种内部电路的时序。在存储器操作期间内部电路的时序很关键,并且内部时钟的偏差可能会导致错误的操作,时钟的偏差包括占空比失真,即时钟信号的占空比偏离预设占空比。

4.因此,存储器需具备dca功能以及dcm功能,即存储器包括占空比调节(dca,duty cycle adjust)电路以及占空比监测(dcm,duty cycle monitor)电路,占空比调节电路可以用于调节外部时钟生成的内部时钟的占空比,占空比监测电路可用于监测时钟的占空比是否偏离预设占空比。

5.此外,在存储器出厂前需要对存储器进行测试,然而测试机的性能对测试结果影响较大,影响测试结果的准确性。分析发现,目前采用测试机向存储器提供输入信号,该输入信号为存储器完成读写操作所需的工作信号。然而,目前主流的测试机通常仅能工作于较低的频率(如200mhz左右),远远达不到高速存储器的最高工作频率,高速存储器包括dram,例如为lpddr4或者lpddr5或者lpddr6,因此利用测试机难以对dram的高速输入端口的特性进行良好的判断及筛选,高速输入端口包括数据端口/系统时钟端口/数据时钟端口(dq/ck/wck)。另外,一些高速测试机仅能对输入信号的频率进行设置,难以确保占空比精确稳定在预设占空比内,由此会产生测试偏差,影响测试结果的准确性。

技术实现要素:

6.本发明实施例解决的技术问题为提供一种时钟产生电路、存储器以及时钟占空比校准方法,该时钟产生电路不仅能够产生可用于存储器测试的第一振荡信号和第二振荡信号,还能够用于实现存储器的dcm功能和dca功能。

7.为解决上述问题,本发明实施例提供一种时钟产生电路,包括:振荡电路,用于产生第一振荡信号和第二振荡信号,所述第一振荡信号与所述第二振荡信号的频率相同且相位相反;比较单元,接收所述第一振荡信号和所述第二振荡信号,用于对所述第一振荡信号的占空比和/或所述第二振荡信号的占空比进行比较;逻辑单元,连接所述比较单元和所述振荡电路,用于根据所述比较单元的输出结果对所述振荡电路进行控制,使得所述占空比到达一预设范围内。

8.另外,所述比较单元包括:积分单元,其具有第一输入端和第二输入端,所述第一输入端接收所述第一振荡信号或所述第二振荡信号中的一者,所述第二输入端接收所述第二振荡信号或所述第一振荡信号中的另一者;比较器,连接所述积分单元的输出端。

9.另外,所述积分单元被配置为:所述积分单元的所述第一输入端在一翻转标识信号为低电平时接收所述第一振荡信号,在所述翻转标识信号为高电平时接收所述第二振荡信号;所述积分单元的所述第二输入端在所述翻转标识信号为低电平时接收所述第二振荡信号,在所述翻转标识信号为高电平时接收所述第一振荡信号。

10.另外,所述逻辑单元包括:计数器,用于调节所述第一振荡信号的占空比和/或所述第二振荡信号的占空比;第一寄存器组,当所述翻转标识信号为低电平时,根据所述比较器的输出存储所述计数器的第一值;第二寄存器组,当所述翻转标识信号为高电平时,根据所述比较器的输出存储所述计数器的第二值。

11.另外,所述逻辑单元还包括:运算组件,连接所述第一寄存器组和所述第二寄存器组,用于对所述第一寄存器组和所述第二寄存器组的输出做加减乘除运算;第三寄存器组,连接所述运算组件,用于存储所述运算组件的输出结果。

12.另外,所述比较单元由一采样时钟驱动,所述采样时钟的频率低于所述第一振荡信号和/或所述第二振荡信号的频率。

13.另外,所述计数器由一计算器时钟驱动,所述计算器时钟的频率低于所述第一振荡信号的频率和/或所述第二振荡信号的频率。

14.另外,所述采样时钟的频率和所述计算器时钟的频率相同。

15.另外,还包括:分频器,接收一外部时钟信号,产生所述采样时钟和所述计算器时钟。

16.另外,还包括:第五寄存器组,与所述分频器连接,用于配置所述采样时钟和所述计算器时钟的频率。

17.另外,所述振荡电路包括:振荡器,用于产生第一初始振荡信号和第二初始振荡信号,所述第一初始振荡信号与所述第二初始振荡信号的频率相同且相位相反;路径模拟电路,介于所述振荡器和所述比较单元之间,一端连接所述振荡器的输出端,另一端连接所述比较单元的输入端,用于模拟第一路径的电路特性,接收所述第一初始振荡信号以产生所述第一振荡信号,接收所述第二初始振荡信号以产生所述第二振荡信号。

18.另外,还包括:第四寄存器组,与所述振荡器连接,用于配置所述第一振荡信号的频率和所述第二振荡信号的频率。

19.另外,还包括:第六寄存器组,与所述路径模拟电路连接,用于配置所述路径模拟电路的电性参数。

20.相应的,本发明实施例还提供一种存储器,包括上述的时钟产生电路。

21.相应的,本发明实施例还提供一种时钟占空比校准方法,包括:振荡电路产生第一振荡信号和第二振荡信号,所述第一振荡信号与所述第二振荡信号的频率相同且相位相反,所述第一振荡信号具有一初始占空比;比较单元接收所述第一振荡信号和所述第二振荡信号,并对所述第一振荡信号的占空比和/或所述第二振荡信号的占空比进行比较;逻辑单元根据所述比较单元的输出结果对所述振荡电路进行控制,使得所述振荡电路产生的所述第一振荡信号的占空比由所述初始占空比变为预设占空比。

22.另外,所述比较单元接收所述第一振荡信号和所述第二振荡信号包括:当翻转标识信号为低电平时,所述比较单元对所述第一振荡信号的占空比进行比较;当所述翻转标识信号为高电平时,所述比较单元对所述第二振荡信号的占空比进行比较。

23.另外,所述逻辑单元根据所述比较单元的输出结果对所述振荡电路进行控制包括:所述逻辑单元包括计数器、第一寄存器组、第二寄存器组;当所述翻转标识信号为低电平时,所述计数器从m计数至n,当所述计数器为m时对应所述第一振荡信号的占空比为p%,当所述计数器为n时对应所述第一振荡信号的占空比为q%,当所述比较单元的输出结果由低电平变为高电平时,将此时所述计数器对应的计数器值存入所述第一寄存器组;当所述翻转标识信号为高电平时,所述计数器从m计数至n,当所述计数器为m时对应所述第二振荡信号的占空比为q%,当所述计数器为n时对应所述第二振荡信号的占空比为p%,当所述比较单元的输出结果由高电平变为低电平时,将此时所述计数器对应的计数器值存入所述第二寄存器组;其中,所述m和n均为整数,所述m小于n,所述p和q均为正整数,所述p小于50,所述q大于50。

24.另外,所述逻辑单元根据所述比较单元的输出结果对所述振荡电路进行控制还包括:所述逻辑单元还包括运算组件、第三寄存器组;所述运算组件将所述第一寄存器组和所述第二寄存器组的输出做加减乘除运算,并将得到的数值l存入所述第三寄存器组;其中,所述l为整数,所述l大于等于所述m且小于等于所述n。

25.另外,所述l对应所述第一振荡信号的占空比为所述预设占空比。

26.与现有技术相比,本发明实施例提供的技术方案具有以下优点:

27.本发明实施例提供一种结构性能优越的时钟产生电路,包括用于产生差分的第一振荡信号和第二振荡信号的振荡电路;比较单元用于对第一振荡信号的占空比和/或第二振荡信号的占空比进行比较,以监测第一振荡信号的占空比和/或第二振荡信号的占空比是否到达预设范围内;还包括连接比较单元和振荡电路的逻辑单元,该逻辑单元基于比较单元的输出结构对振荡电路进行控制,使得占空比到达预设范围内。因此,本发明实施例中的时钟产生电路能够产生占空比符合预设范围且稳定的第一振荡信号和第二振荡信号,该第一振荡信号和第二振荡信号可作为测试存储器的输入信号,因此有利于提高存储器的测试准确度;此外,该时钟产生电路还具有占空比校准功能和占空比监测功能,因此,具有该时钟产生电路的存储器不仅具有内置自测功能,且还可以用于实现dca功能以及dcm功能。

附图说明

28.一个或多个实施例通过与之对应的附图中的图片进行示例性说明,这些示例性说明并不构成对实施例的限定,附图中具有相同参考数字标号的元件表示为类似的元件,除非有特别申明,附图中的图不构成比例限制。

29.图1为本发明一实施例提供的时钟产生电路的功能框图;

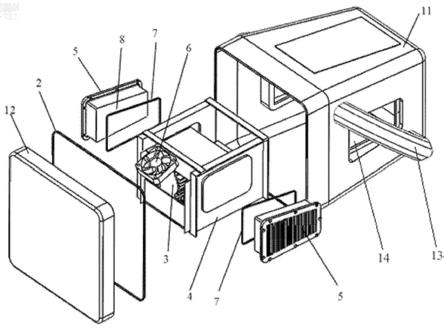

30.图2为本发明一实施例提供的时钟产生电路的结构示意图;

31.图3为图1中振荡电路中的振荡器的一种电路结构示意图;

32.图4为一种存储系统示意图;

33.图5为本发明一实施例提供的时钟占空比校准方法的流程示意图。

具体实施方式

34.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合附图对本发明的各实施例进行详细的阐述。然而,本领域的普通技术人员可以理解,在本发明各实施例中,为了使读者更好地理解本技术而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本技术所要求保护的技术方案。

35.图1为本发明一实施例提供的时钟产生电路的功能框图,图2为本发明一实施例提供的时钟产生电路的结构示意图。

36.参考图1及图2,本实施例中,时钟产生电路包括:振荡电路101,用于产生第一振荡信号osc 和第二振荡信号osc-,第一振荡信号osc 和第二振荡信号osc-的频率相同且相位相反;比较单元102,接收第一振荡信号osc 和第二振荡信号osc-,用于对第一振荡信号osc 的占空比和/或第二振荡信号osc-的占空比进行比较;逻辑单元103,连接比较单元102和振荡电路101,用于根据比较单元102的输出结果对振荡电路101进行控制,使得占空比达到一预设范围内。

37.该时钟产生电路内置于存储器内,可作为存储器的内置自测系统(bist,(built-in self test)的关键组成部分,利用振荡电路产生差分的高速振荡信号,即高频的第一振荡信号和第二振荡信号,可测试到高速输入电路的特性,从而解决了测试机提供的输入信号的频率过低导致的测试结果准确性差的问题,且极大的降低了对自动测试机(ate,automatic test equipment)的依赖性,从而降低测试成本。此外,时钟产生电路还可以实现存储器的占空比校准功能以及占空比监测功能。

38.以下将结合附图对本实施例提供的时钟产生电路进行详细说明。

39.第一振荡信号osc 和第二振荡信号osc-为差分的时钟信号。此外,本实施例中,第一振荡信号osc 和第二振荡信号osc-具有高频特性,也就是说,第一振荡信号osc 的频率与第二振荡信号osc-的频率与存储器进行读写操作所需的时钟信号的频率相当,此处的相当既可以为频率相同,也可以指频率差异在测试允许范围内。例如,第一振荡信号osc 和第二振荡信号osc-的频率可以达到3.2ghz或4.8ghz甚至6.4ghz。

40.具体地,振荡电路101包括振荡器111,用于产生第一初始振荡信号osc 和第二初始振荡信号osc-,且第一初始振荡信号osc 与第二初始振荡信号osc-的频率相同且相位相反,即第一初始振荡信号osc 与第二初始振荡信号osc-为差分信号。

41.图3为本实施例提供的振荡器111的一种电路结构示意图。更具体地,如图3所示,振荡器111包括相互电连接的第一环形拓扑结构和第二环形拓扑结构,第一环形拓扑结构由多个第一反相器11首尾相连,以第一传输速度传播振荡信号,第二环形拓扑结构由多个第二反相器12首尾相连,以第二传输速度传播振荡信号,且第二传播速度小于第一传播速度。

42.其中,第一反相器11的数量为大于或等于4的整数,第二反相器12的数量为大于或等于2的整数。此外,第二传播速度可以大于或等于0.5倍的第一传播速度。

43.振荡器111还可以包括:第三环拓扑结构,由多个第三反相器13首尾相连,以第三传播速度传播振荡信号,且第一环形拓扑结构与第三环形拓扑结构电连接,第三传播速度小于第一传播速度。具体地的,第三反相器13的数量为大于或等于2的整数,且第三传播速度可以与第二传播速度相同。

44.相对于仅通过第一环形拓扑结构传播振荡信号,由于第二环形拓扑结构具有的第二传输速度小于第一环形拓扑结构具有的第一传输速度,第二环形拓扑结构的设置可使得振荡信号在单位时间内翻转更多次,从而获取高速的第一初始振荡信号osc 与第二初始振荡信号osc-,进而获取高速的第一振荡信号osc 和第二振荡信号osc-。

45.本实施例中,振荡电路101还可以包括:路径模拟电路121,介于振荡器111与比较单元102之间,一端连接振荡器111的输出端,另一端连接比较单元102的输入端,用于模拟第一路径的电路特性,且接收第一初始振荡信号osc 以产生第一振荡信号osc ,接收第二初始振荡信号osc-以产生第二振荡信号osc-。

46.电路特性包括:第一路径的器件电阻、器件电容、寄生电阻、寄生电容、输入输出阻抗、驱动能力以及噪声环境中的一者或任意组合。具体地,第一路径指的是,时钟信号经由控制器(controller)传输至存储器的高速差分输入电路的输出端的信号路径。为便于理解和说明,以下将结合图3对第一路径进行说明:

47.图4为一种存储系统示意图。参考图4,存储系统包括控制器10以及多个存储器20,各存储器20和控制器10均耦接命令/地址总线21、数据总线22以及时钟总线23。例如,存储器20可以是lpddr4或lpddr5或者lpddr6,存储器20通过命令/地址总线21接收控制器10提供的命令/地址信号,以cmd/add标示命令/地址信号;通过数据总线22在控制器10与存储器20之间传输数据信号,以dq标示数据信号;通过时钟总线23在控制器10与存储器20之间传输多种时钟信号,时钟信号可以包括系统时钟信号、读写数据时钟信号,以ck_t和ck_c标示差分的系统时钟信号,以wck_t和wck_c标示差分的读写数据时钟信号。

48.具体地,控制器10与存储器20的高速差分输入电路耦接,高速差分输入电路24用于接收外部时钟信号并产生内部时钟信号,该内部时钟信号可用于作为完成数据的读写操作的差分输入信号。更具体地,高速差分输入电路24接收ck_t、ck_c、wck_t和wck_c产生内部时钟信号。高速差分输入电路24可以包括输入缓冲器(ib,input buffer)。

49.命令/地址总线21、数据总线22以及时钟总线23均具有电阻且还可能产生寄生电阻或者寄生电容,此外,高速差分输入电路24本身也具有电阻或电容等电路特性,在振荡电路101中设置路径模拟电路121,可模拟这些电路特性。本实施例中,通过在振荡电路中设置路径模拟电路121,该路径模拟电路121不仅能够将第一初始振荡信号osc 和第二初始振荡信号osc-放大输出,且还能够模拟控制器10到高速差分输入电路24的输出端的电路特性,使得第一振荡信号osc 以及第二振荡信号osc-更加符合存储器的真实应用情景的高速时钟信号,从而使得测试结果更加准确有效。

50.如图2所示,路径模拟电路121可包括模拟缓冲器1以及模拟片上终结电阻(odt,on die termination)2。

51.一般地,采用高速测试机提供输入信号时,为了能保证输入信号的稳定性,输入信

号的电平通常为固定值且不能随意改变,这与存储器的实际应用情况不同,因此会引入测试偏差,影响测试结果的准确性。而本实施例中,第一振荡信号osc 和第二振荡信号osc-作为输入信号,可以通过路径模拟电路121调整第一振荡信号osc 的电平和第二振荡信号osc-的电平,从而使得测试结果更加准确。

52.需要说明的是,在其他实施例中,振荡电路也可以仅包括振荡器,即振荡器直接产生第一振荡信号osc 以及第二振荡信号osc-。

53.本实施例中,振荡电路101还可以包括:第四寄存器组131,与振荡器111连接,用于配置第一振荡信号osc 和第二振荡信号osc-的频率。具体地,第四寄存器组131通过配置第一初始振荡信号osc 的频率以配置第一振荡信号osc 的频率,通过配置第二初始振荡信号osc-的频率以配置第二振荡信号osc-的频率。

54.其中,第四寄存器组131可以为模式寄存器(mr,model register),该模式寄存器还可以集成于存储器为实现读写操作功能所需的模式寄存器中,该模式寄存器也可以为与存储器的模式寄存器相互独立的功能模块。

55.振荡电路101还可以包括:第六寄存器组141,与路径模拟电路121连接,用于配置路径模拟电路121的电性参数。具体地,通过第六寄存器组141调整路径模拟电路121的电性参数,以调整路径模拟电路121模拟的第一路径的电路特性。

56.其中,第六寄存器组141可以为模式寄存器,该模式寄存器还可以集成于存储器为实现读写操作功能所需的模式寄存器中,该模式寄存器也可以为与存储器的模式寄存器相互独立的功能模块。

57.举例来说,通过第六寄存器组141设置选择路径模拟电路121的输出状态,以lpddr4为例,设置voh=(1/3)*vddq或者voh=(1/2.5)*vddq,pdds=40ohm,odt=40ohm,其中,voh为输出驱动电压,pdds(pull down drive strength)为输入下拉驱动强度,odt(on-die termination)为片上终结电阻。

58.由于第一振荡信号osc 与第二振荡信号osc-为差分信号,因此第一振荡信号osc 的占空比与第二振荡信号osc-的占空比之和为100%,通过设置比较单元102检测差分的第一振荡信号osc 和第二振荡信号osc-的占空比大小。具体地,比较单元102对第一振荡信号osc 的占空比和/或第二振荡信号osc-的占空比进行比较,包括以下三种情况中的至少一种:

59.比较单元102对第一振荡信号osc 的占空比进行比较。具体地,比较单元102比较第一振荡信号osc 的占空比是否到达预设范围内,例如,该预设范围可以为48%~52%。若比较单元102比较第一振荡信号osc 的占空比在预设范围内,则说明第二振荡信号osc-的占空比也在预设范围内;若比较单元102比较第一振荡信号osc 的占空比不在预设范围内,则说明第二振荡信号osc-的占空比也不在预设范围内。

60.比较单元102对第二振荡信号osc-的占空比进行比较。具体地,比较单元102比较第二振荡信号osc-的占空比是否到达预设范围内,该预设范围可以为48%~52%。若比较单元102比较第二振荡信号osc-的占空比在预设范围内,则说明第一振荡信号osc 的占空比也在预设范围内;若比较单元102比较第二振荡信号osc-的占空比不在预设范围内,则说明第一振荡信号osc 的占空比也不在预设范围内。

61.比较单元102对第一振荡信号osc 的占空比与第二振荡信号osc-的占空比进行比

较。具体地,比较单元102获取第一振荡信号osc 的占空比与第二振荡信号osc-的占空比的差值是否在预设差值范围内,该预设差值范围可以为-4%~4%;若比较单元102比较该差值在预设差值范围内,则说明第一振荡信号osc 和第二振荡信号osc-的占空比在预设范围内,否则,第一振荡信号osc 和第二振荡信号osc-的占空比未到达预设范围。

62.需要说明的是,上述的预设范围以及预设差值范围的数值范围均为示例性说明,本实施例并不对预设范围以及预设差值范围做限定,可根据存储器的实际性能需求合理设置预设范围以及预设差值范围。

63.本实施例中,比较单元102包括:积分单元112,其具有第一输入端3和第二输入端4,第一输入端3接收第一振荡信号osc 或者第二振荡信号osc-中的一者,第二输入端4接收第一振荡信号osc 或第二振荡信号osc-中的另一者;比较器122,连接积分单元112的输出端。

64.具体地,积分单元112包括两个积分电路,且第一输入端3作为一积分电路的输入端,第二输入端4作为另一积分电路的输入端。比较器122用于比较两个积分电路的输出并输出高电平或者低电平。

65.更具体地,比较单元102由两个积分电路对输入的第一振荡信号osc 和第二振荡信号osc-进行积分运算,且积分运算的结果输入至比较器122中,且比较器122输出比较结果。

66.以第一振荡信号osc 为正端(duty )且第二振荡信号osc-为负端(duty-)为例,在一个例子中,比较器122的输出为高电平,则表明第一振荡信号osc 的占空比大于第二振荡信号osc-的占空比;比较器122的输出为低电平,则表明第一振荡信号osc 的占空比小于第二振荡信号osc-的占空比。

67.需要说明的是,上述关于比较单元102的输出结果与第一振荡信号osc 的占空比和第二振荡信号osc-的占空比之间的对应关系仅为示例,本实施例并不限定高电平以及低电平与第一振荡信号osc 的占空比和第二振荡信号osc-的占空比之间的对应关系,只要保证不同的输出结果对应不同的第一振荡信号osc 的占空比和第二振荡信号osc-的占空比之间的对应关系即可。

68.如图2所示,比较单元102的输出结果可以经采样时钟clk1采样输出。本实施例中,比较单元102由一采样时钟clk1驱动,采样时钟clk1的频率低于第一振荡信号osc 的频率和/或第二振荡信号osc-的频率。采样时钟clk1的频率越快,则采样误差越大;采样时钟clk1的频率越慢,则采样误差越小,但测试时间越长。因此,可根据采样误差以及测试时间综合选择采样时钟clk1的最优频率。

69.本实施例中,时钟产生电路还包括:分频器104,接收一外部时钟信号clk,产生采样时钟clk1。该外部时钟信号clk既可以是测试机提供的,也可以是存储器的主时钟信号。

70.此外,由前述分析可知,若采样时钟clk1的频率可调,则可根据实际情况选择不同的采样时钟clk1频率,为此,本实施例中,时钟产生电路还可以包括:第五寄存器组105,与分频器104连接,用于配置采样时钟的频率。第五寄存器组105可以为模式寄存器,有关第五寄存器组105的详细说明,可参考前述关于第四寄存器组131以及第六寄存器组141的描述。

71.由于比较单元102的固有特性可能会带来输入偏差,为了消除比较单元102自由的输入偏差对测试结果带来的误差,本实施例中,比较单元102还可以被配置为第一输入端和

第二输入端可互换。具体地,比较单元102被配置为:

72.积分单元112的第一输入端在一翻转标识信号为低电平时接收第一振荡信号osc ,在翻转标识信号为高电平时接收第二振荡信号osc-;积分单元112的第二输入端在翻转标识信号为低电平时接收第二振荡信号osc-,在翻转标识信号为高电平时接收第一振荡信号osc 。其中,存储器中具有模式寄存器,该翻转标识信号可以由模式寄存器提供,例如,在lpddr4或lpddr5或者lpddr6中,可以为dcm mr op[1],dcm mr op[1]=0表示翻转标识信号为低电平,dcm mr op[1]=1表示翻转标识信号为高电平。

[0073]

逻辑单元103包括:计数器113,用于调节第一振荡信号osc 和/或第二振荡信号osc-的占空比;第一寄存器组123,当翻转标识信号为低电平时,根据比较器122的输出存储计数器113的第一值;第二寄存器组133,当翻转标识信号为高电平时,根据比较器122的输出存储计数器113的第二值。

[0074]

具体地,计数器113的作用包括:调节振荡电路101输出的第一振荡信号osc 的占空比以及第二振荡信号osc-的占空比,且第一振荡信号osc 的占空比以及第二振荡信号osc-的占空比的变化为单调性变化,例如在一个计数周期内占空比从最小变大最大或者从最大变大最小。在一个计数周期内,比较器122的输出结果将有且仅有一个反转点,该反转点对应的计数器113的值是振荡电路101输出的第一振荡信号osc 和第二振荡信号osc-的占空比最接近预设范围的设置,将这个值作为计数器的值存入第一寄存器组123或者第二寄存器组133。

[0075]

更具体地,当翻转标识信号为低电平时,根据比较器122的输出存储计数器113的第一值,该第一值存入第一寄存器组123;当翻转标识信号为高电平时,根据比较器122的输出存储计数器113的第二值,该第二值存入第二寄存器组133。为便于理解,以下将对逻辑单元103的工作原理进行详细说明:

[0076]

当翻转标识信号为低电平时,积分单元112的第一输入端接收第一振荡信号osc ,第二输入端接收第二振荡信号osc-;计数器113开始计数,例如在一个计数周期内从0开始计数且计到31,同时振荡电路101输出的第一振荡信号osc 和第二振荡信号osc-的占空比也从最小变大最大(例如从40%变到60%)或者从最大变到最小;这样,在一个计数周期(例如从0到31)内,比较器122将有且仅有一个反转点,该反转点对应的计数器113的值为第一值,该第一值是振荡器111经由路径模拟电路121输出的振荡信号的占空比最接近预设范围的设置,例如可以是占空比最接近50%的设置,该第一值存入第一寄存器组123中。

[0077]

当翻转标识信号为高电平时,积分单元112的第一输入端接收第二振荡信号osc-,第二输入端接收第一振荡信号osc ,即比较单元102的输入端互换,计数器113进入新的计数周期,例如从0开始计数且计到31,同样的,将比较器122的输出反转点对应的计数器113的第二值存入第二寄存器组133中。

[0078]

需要说明的是,上述从0到31的计数周期仅为示例说明,本实施例中并不对计数器113的计数方式进行限定,计数器113除为加法计数器外也可以为减法计数器,既可以为依次递增或者递减式计数,也可以为步进式递增或者递减计数,保证计数器113在单个计数周期内单调性变化即可。

[0079]

比较单元102的第一输入端与第二输入端互换,通过两次计数控制振荡电路101的方式,可以消除比较单元102自身的输入偏差带来的不良影响,进一步的提高测试结果的准

确性。

[0080]

此外,逻辑单元103还可以包括:运算组件143,连接第一寄存器组123和第二寄存器组133,用于对第一寄存器组123和第二寄存器组133的输出做加减乘除运算;第三寄存器组153,连接运算组件143,用于存储运算组件143的输出结果。

[0081]

具体地,第一寄存器组123的输出指的是存入第一寄存器组123的第一值,第二寄存器组133的输出指的是存入第二寄存器组133的第二值。本实施例中,运算组件143对第一值和第二值进行相加除以2,得到平均值,且该平均值作为运算组件143的输出结果,该平均值被存入第三寄存器组153。由于该平均值已经消除掉比较单元102自有的输入偏差,因此该平均值为振荡电路101输出的第一振荡信号osc 和第二振荡信号osc-的占空比最接近预设范围的设置,例如第一振荡信号osc 和第二振荡信号osc-的占空比最接近50%。

[0082]

可以理解的是,该平均值既可以是第一值和第二值进行相加除以2向上取整的整数,也可以是第一值和第二值进行相加除以2向下取整的整数。

[0083]

需要说明的是,本实施例中以对第一值和第二值取平均作为示例,在其他实施例中,也可以采用其他的运算方式对第一值和第二值进行运算。

[0084]

第一寄存器组123、第二寄存器组133以及第三寄存器组153均可以为模式寄存器。

[0085]

本实施例中,计数器113由一计算器时钟驱动,计算器时钟的频率低于第一振荡信号osc 的频率和/或第二振荡信号osc-的频率。计算器时钟的频率可调,根据调整振荡电路101的速度合理选择计算器时钟的频率。

[0086]

此外,采样时钟的频率可以与计算器时钟的频率相同。分频器还可以用于接收一外部时钟信号,产生采样时钟和计算器时钟;同样的,第五寄存器组还可以用于配置计算器时钟的频率。

[0087]

存入第三寄存器组153的值对应为振荡电路101的设置,此时,振荡电路101的占空比选择由计数器113切换为第三寄存器组153,使得振荡电路101固定输出具有最优占空比的第一振荡信号osc 和第二振荡信号osc-。可以理解的是,在振荡电路101固定以最优占空比输出第一振荡信号osc 和第二振荡信号osc-期间,比较单元102可以持续对第一振荡信号osc 的占空比和/或第二振荡信号osc-的占空比进行比较,若第一振荡信号osc 的占空比和第二振荡信号osc-的真空比偏离预设范围,能够及时检测出这一问题。

[0088]

本实施例提供的时钟产生电路,通过振荡电路101、比较单元102以及逻辑单元103,能够在存储器内部产生高速且占空比可调的第一振荡信号和第二振荡信号,且第一振荡信号与第二振荡信号为差分信号,该第一振荡信号和第二振荡信号满足存储器高频工作信号的需求,因此能够作为测试存储器的测试输入信号,使得存储器能够实现内置自测功能,无需利用额外的测试机提供测试输入信号,同时解决了测试机难以提供高频的测试输入信号的问题。

[0089]

此外,本实施例中,比较单元102对振荡电路101的输出进行检测,且逻辑单元103基于比较单元102的输出结果对振荡电路101进行控制,从而保证第一振荡信号和第二振荡信号的占空比能够稳定在预设范围内,从而避免了占空比偏差对测试准确度带来的不良影响,提高利用第一振荡信号和第二振荡信号对存储器进行测试的测试准确度。例如,第一振荡信号的占空比和第二振荡信号的占空比可精确控制在50%。

[0090]

另外,由于振荡电路101还包括路径模拟电路121,该路径模拟电路121不仅能够将

高速振荡信号放大输出,且还可以模拟从口控制器到高速差分输入电路的输出端的信号特性,使得第一振荡信号和第二振荡信号更加符合存储器的实际应用情况,从而进一步的提高利用第一振荡信号和第二振荡信号进行测试的测试准确性。

[0091]

同时,本实施例提供的时钟产生电路,还具有占空比监测功能以及占空比校准功能。

[0092]

相应的,本发明实施例还提供一种存储器,包括前述实施例提供的时钟产生电路。具体地,该存储器可以为dram、sram、mram、feram、pcram、nand、nor等存储器。

[0093]

由前述分析可知,存储器具有内置自测功能,因而能够在存储器内部产生可用于测试的高速第一振荡信号和第二振荡信号,且第一振荡信号和第二振荡信号的占空比能够维持在预设范围内,因而无需利用额外的测试机提供测试信号,从而有利于提高对存储器进行测试的测试准确度。

[0094]

相应的,本发明实施例还提供一种时钟占空比校准方法。图5为本发明一实施例提供的时钟占空比校准方法的流程示意图。以下将结合附图对本发明实施例中时钟占空比校准方法进行详细说明。需要说明的是,该时钟占空比校准方法可利用前述实施例提供的时钟产生电路进行。

[0095]

参考图5,本实施例中,时钟占空比校准方法包括以下步骤:

[0096]

步骤s1、振荡电路产生第一振荡信号和第二振荡信号,第一振荡信号与第二振荡信号的频率相同且相位相反,第一振荡信号具有一初始占空比。

[0097]

具体地,该初始占空比可以在预设范围内,例如初始占空比在48%~52%;该初始占空比也可以未达到预设范围,例如初始占空比为45%。此外,第一振荡信号的占空比与第二振荡信号的占空比之和为100%。

[0098]

步骤s2、比较单元接收第一振荡信号和第二振荡信号,并对第一振荡信号的占空比和/或第二振荡信号的占空比进行比较。

[0099]

具体地,当翻转标识信号为低电平时,比较单元对第一振荡信号的占空比进行比较,例如,比较单元可以判断第一振荡信号的占空比是否等于一预设占空比,如果小于预设占空比,比较单元输出低电平,如果大于等于预设占空比,比较单元输出高电平;当翻转标识信号为高电平时,比较单元对第二振荡信号的占空比进行比较,例如,比较单元可以判断第二振荡信号的占空比是否等于预设占空比,如果小于预设占空比,比较单元输出低电平,如果大于等于预设占空比,比较单元输出高电平。该预设占空比例如可以为50%,该比较单元的输出并不限定高电平以及低电平与第一振荡信号osc 的占空比和第二振荡信号osc-的占空比之间的对应关系,只要保证不同的输出结果对应不同的第一振荡信号osc 的占空比和第二振荡信号osc-的占空比之间的对应关系即可。

[0100]

比较单元的输出结果还可以表征第一振荡信号的占空比与第二振荡信号的占空比之间的差值。例如,比较单元的输出结果为高电平,表征第一振荡信号的占空比大于第二振荡信号的占空比;比较单元的输出结果为低电平,表征第一振荡信号的占空比小于第二振荡信号的占空比。第一振荡信号的占空比与第二振荡信号的占空比之和为100%,例如,当第一振荡信号的占空比由49%变为51%时,比较单元的输出结果由低电平变为高电平。

[0101]

比较单元包括:积分单元,其具有第一输入端和第二输入端,第一输入端接收第一振荡信号或第二振荡信号中的一者,第二输入端接收第二振荡信号或第一振荡信号中的另

一者;比较器,连接积分单元的输出端。

[0102]

当翻转标识信号为低电平时,第一输入端接收第一振荡信号且第二输入端接收第二振荡信号,比较器对第一振荡信号的占空比进行比较且具有相应的输出;比较器对第一振荡信号的占空比进行比较,可以为:比较第一振荡信号的占空比与第二振荡信号的占空比,或者,比较第一振荡信号的占空比与预设占空比。

[0103]

当翻转标识信号为高电平时,第一输入端接收第二振荡信号且第二输入端接收第一振荡信号,比较器对第二振荡信号的占空比件比较且具有相应的输出;比较器对第二振荡信号的占空比进行比较,可以为:比较第二振荡信号的占空比与第一振荡信号的占空比,或者,比较第二振荡信号的占空比与预设占空比。

[0104]

步骤s3、逻辑单元根据比较单元的输出结果对振荡电路进行控制,使得振荡电路产生的所述第一振荡信号的占空比由初始占空比变为预设占空比。

[0105]

具体地,逻辑单元包括计数器、第一寄存器组、第二寄存器组。通过计数器控制振荡电路,以调整第一振荡信号的占空比和第二振荡信号的占空比。

[0106]

当翻转标识信号为低电平时,计数器从m计数至n,当计数器为m时对应第一振荡信号的占空比为p%,当计数器为n时对应第一振荡信号的占空比为q%,当比较单元的输出结果由低电平变为高电平时,将此时计数器对应的计数器值存入所述第一寄存器组。例如,m可以为0,n可以为31,p可以为45,q可以为55,初始占空比可以为45%,也可以为其他值。

[0107]

当翻转标识信号为高电平时,计数器从m计数至n,当计数器为m时对应第二振荡信号的占空比为q%,当计数器为n时对应第二振荡信号的占空比为p%,当比较单元的输出结果由高电平变为低电平时,将此时计数器对应的计数器值存入第二寄存器组。例如,m可以为0,n可以为31,p可以为45,q可以为55,初始占空比可以为45%,也可以为其他值。

[0108]

其中,m和n均为整数,m小于n,p和q均为正整数,p小于50,q大于50。初始占空比例如可以为介于1%至99%的任意值,预设占空比例如可以为48%至52%的任意值,甚至预设占空比可以等于50%。

[0109]

更具体地,当翻转标识信号为低电平时,第一输入端接收第一振荡信号且第二输入端接收第二振荡信号,计数器在一个计数周期内由0计数至31,比较单元的输出结果为低电平时,说明第一振荡信号的占空比小于第二振荡信号的占空比;比较单元的输出结果为高电平时,说明第一振荡信号的占空比大于第二振荡信号的占空比。因此,比较单元的输出结果由低电平跳转为高电平对应具有一个反转点,该反转点对应的计数器的计数器值作为第一值存入第一寄存器组。

[0110]

当翻转标识信号为高电平时,第一输入端接收第二振荡信号且第二输入端接收第一振荡信号,计数器在一个计数周期内由0计数至31,比较单元的输出结果为高电平时,说明第一振荡信号的占空比小于第二振荡信号的占空比;比较单元的输出结果为低电平时,说明第一振荡信号的占空比大于第二振荡信号的占空比。因此,比较单元的输出结果由高电平跳转为低电平对应具有一个反转点,该反转点对应的计数器的计数器值作为第二值存入第二寄存器组。

[0111]

需要说明的是,当翻转标识信号为低电平,计数器从0计数至31,第一振荡信号的占空比单调性变化,例如可以为预设步进式递增,如计数器的计数器值每增加1则第一振荡信号的占空比增加((55-45)/32)%。同理,当翻转标识信号为高电平,计数器从0计数至31,

第二振荡信号的占空比单调性变化,例如可以为预设步进式递增,如计数器的计数器值每增加1则第二振荡信号的占空比增加((55-45)/32)%。

[0112]

逻辑单元还包括运算组件、第三寄存器组;运算组件将第一寄存器组和第二寄存器组的输出做加减乘除运算,并将得到的数值l存入第三寄存器组;其中,l为正整数,l大于等于m且小于等于n。

[0113]

本实施例中,数值l为第一值和第二值相加除以2,即数值l为第一值和第二值取平均,该数值l即为对应振荡电路输出的第一振荡信号和第二振荡信号到达预设范围的设置。也就是说,数值l对应第一振荡信号的占空比为预设占空比,该预设占空比可以为48%~52%,例如为50%。

[0114]

在获取数值l后,不再由计数器控制振荡电路,而是将数值l作为振荡电路的设置,以使振荡电路输出具有预设占空比的第一振荡信号,相应的第二振荡信号也为占空比符合要求的振荡信号。

[0115]

本实施例提供的时钟占空比校准方法的技术方案,能够获取高速且高质量的第一振荡信号和第二振荡信号,第一振荡信号的占空比和第二振荡信号的占空比可稳定在预设占空比。

[0116]

本领域的普通技术人员可以理解,上述各实施方式是实现本发明的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本发明的精神和范围。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各自更动与修改,因此本发明的保护范围应当以权利要求限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。