1.本发明属于铁电材料技术领域,更具体地说,涉及一种基于极性拓扑畴结构的复合薄膜和铁电存储器及其制备方法。

背景技术:

2.在大数据时代的背景下,传统半导体芯片尺寸已经接近量子极限,难以进一步发展,这推动人们探寻新型半导体电子材料体系下的存储器以满足现实需要。铁电材料走向低维化的通常路线是从块体材料出发,逐步对其尺寸进行降维。然而,当尺寸减低时,铁电材料会遇到“死层”的瓶颈,因此难以突破纳米量级。最近,人们提出了利用拓扑结构实现铁电材料低维化的全新思路。

3.2013年,诺贝尔物理学奖获得者fert教授等提出,将具有拓扑保护特性的磁性拓扑缺陷(如磁性斯格明子)作为信息存储单元,用其记录二进制数据信息,可实现非接触式读写。然而实验上观测到的磁性拓扑结构尺寸都在20nm以上,而由于铁电畴的尺寸通常小于磁畴的尺寸,人们希望在铁电材料中,寻找更小尺寸的类似于磁性材料中的自发极性拓扑结构。naumov等采用第一性原理计算,预言铁电纳米点中可能存在尺寸小至3.2纳米双稳态极性涡旋畴结构,并从理论上推测基于这种极性拓扑结构的信息存储单元可以实现面密度超过60tbit/in2的超高密度存储器。陆续有研究工作表明,在尺寸效应、界面耦合及其相互作用、外延应变等作用下,铁电材料中也会出现自发的非平庸的极性拓扑畴结构,包括流量闭合型、涡旋、极性“磁泡”畴、极性斯格明子、半子等,同时这些极性拓扑畴结构表现出丰富的物理性能。在低维铁性系统中,探索具有极性拓扑畴结构的低维铁电材料,给未来高密度存储器件带来了全新的机遇。

4.尽管具有潜在的应用前景,但由于钙钛矿氧化物体系与当前成熟的互补金属氧化物半导体工艺(cmos)缺乏兼容性,因此仍然难以将上述极性拓扑畴结构集成到常规的硅存储技术中。此外,有关涡旋等拓扑畴的研究是在无底电极或是多层体系中,这种材料结构的设计可以通过对薄膜中退极化场的精确调控来产生环形/摆线拓扑。然而,在实际信息存储中,需要金属底电极来施加电场从而实现独立存储单元的操纵;由于层间作用,在这种多层/超晶格的结构中翻转拓扑畴可能需要更高的能耗,除此之外,多个拓扑畴结构单元在厚度方向上出现重叠,信号交叠难以进行读写操作。

5.为解决钙钛矿氧化物与半导体材料的兼容性问题,人们尝试将过渡金属氧化制备成高质量自支撑晶体膜,并将这些独立的功能单元进行组合及转移到半导体基片上以实现功能的整合。经过多年的努力,但未能取得长足的进展。该方面的技术在2016年得到突破,斯坦福大学的harold hwang教授等利用脉冲激光沉积的技术在水溶性材料中间层sr3al2o6上生长钙钛矿薄膜,通过溶解过渡层的方式获得了自支撑的钙钛矿薄膜。借鉴该方法将水溶性sr3al2o6薄膜作为过渡牺牲层,申请人通过氧化物分子束外延技术成功制备且转移得到高晶格质量的接近单晶胞层极限厚度的二维srtio3和bifeo3自支撑薄膜。特别地,当

bifeo3自支撑薄膜的厚度接近二维极限时,薄膜中产生四方相和巨大的铁电极化。自支撑二维氧化物铁电材料的成功制备激励进一步探索基于氧化物的新型铁电、多铁二维材料的机理与器件应用。

技术实现要素:

6.1.要解决的问题

7.针对现有技术中传统铁电存储器难以低维化发展,而现有的基于拓扑畴结构的存储器能耗高、读写难的问题,提供一种基于极性拓扑畴结构的复合薄膜和铁电存储器及其制备方法,制得高密度、能够与硅半导体相结合的基于极性类斯格明子的铁电阻抗存储器,从而有效解决现有铁电存储器能耗高、读写难的问题。

8.2.技术方案

9.为了解决上述问题,本发明所采用的技术方案如下:

10.本发明的一种基于极性拓扑畴结构的复合薄膜,其包括介电层和铁电层,介电层包括介电材料,铁电层包括铁电材料,所述铁电层平行设置于介电层表面;在所述介电层和铁电层中,其中一层是在另外一层表面生长形成;所述介电层的厚度为其中介电材料单个晶胞层厚度的x倍,铁电层的厚度为其中铁电材料单个晶胞层厚度的y倍,0.5<y/x<10,复合薄膜的厚度不超过30nm;所述铁电层可被操作的通过极性拓扑畴结构产生二极管导通特性,且可被操作地通过所述极性拓扑畴结构的变化调制所述二极管导通特性。本发明通过物理或化学方法生长制备介电层或铁电层,以及介电层和铁电层的厚度调控,实现铁电层中单层极性类斯格明子拓扑纳米畴的制备,解决了现有技术中多层/超晶格的结构中翻转拓扑畴能耗高、读写难的问题。

11.优选地,所述介电层和铁电层均为单晶薄膜层,铁电材料和介电材料均为氧化物材料。

12.优选地,所述x=5~16,复合薄膜的厚度不超过20nm,1.6<y/x<5;更优选地,y/x=1.8~2.2。

13.优选地,所述介电材料包括srtio3、catio3、laalo3、sio2、hfo2其中一种或多种;所述铁电材料包括bifeo3、pbtio3、batio3、pzt、pmn-pt其中一种或多种。

14.优选地,所述生长的方法包括外延生长法;外延生长法包括分子束外延法、脉冲激光沉积法、电子束沉积法、原子束沉积法、电泳沉积法、化学气相沉积法、液相外延法其中一种或多种。

15.本发明的一种复合薄膜制备方法,所述复合薄膜为本发明中所述的一种基于极性拓扑畴结构的复合薄膜,先在单晶衬底上外延生长牺牲层,再在牺牲层表面依次外延生长介电层和铁电层,最后用水将牺牲层溶解,得到所述复合薄膜;所述牺牲层包括酸腐蚀牺牲层或碱腐蚀牺牲层或水溶性牺牲层。其中酸腐蚀牺牲层可用酸溶液将其腐蚀,从而将复合薄膜从衬底上剥落;碱腐蚀牺牲层或水溶性牺牲层同理,分别可用碱溶液或水将其溶解。

16.优选地,具体步骤为:

17.(1)采用氧化物分子束外延法在单晶衬底上沉积一层水溶性牺牲层作为过渡层,所述水溶性牺牲层的材料包括sr3al2o6;

18.(2)采用氧化物分子束外延法在过渡层上沉积一层srtio3薄膜;

19.(3)采用氧化物分子束外延法在(2)所述的srtio3层上沉积一层pbtio3薄膜;

20.(4)将水溶性牺牲层用去离子水溶解去除,使得pbtio3/srtio3双层结构与衬底分离,得到pbtio3/srtio3复合薄膜。

21.本发明的一种铁电存储器,其包括导电衬底和复合薄膜,所述导电衬底和复合薄膜平行设置并相连,其中复合薄膜为本发明中所述的一种基于极性拓扑畴结构的复合薄膜,所述铁电存储器通过复合薄膜的二极管导通特性的调制变化存储信息。

22.优选地,铁电存储器的制备方法为:将所述复合薄膜转移至镀铂的硅衬底上,介电层与硅衬底接触。

23.优选地,调制二极管导通特性的方法为:在铁电存储器两端施加外电场e,通过改变外电场的大小或方向进行调制;外电场e的最大绝对值为|e|m,|e|m≥0.083v/nm。

24.优选地,所述|e|m≥0.25v/nm。

25.3.有益效果

26.相比于现有技术,本发明的有益效果为:

27.(1)本发明的一种基于极性拓扑畴结构的复合薄膜,由于只有单层极性类斯格明子而不是多层相互作用的极性斯格明子,因此更容易通过外部电场切换每个独立的极性类斯格明子,允许有效地进行“写入”操作;此外,由于没有多层类斯格明子之间的干扰,它还可以通过pfm直接进行测试,这实际上是一种非破坏性的“读取”操作,从而实现数据更加快捷有效的读写。

28.(2)本发明的一种基于极性拓扑畴结构的复合薄膜,基于铁电层中单层极性类斯格明子,使得整个复合足够薄,极性类斯格明子电导率的改变可以有效地调整纳米畴核心附近双层膜的电阻状态。

29.(3)本发明的一种铁电存储器,将本发明的复合薄膜集成于硅片等导电衬底上获得,可以通过对铁电存储器施加不同大小或方向的外电场,实现对铁电存储器在高导电态的中心发散畴和低导电态的中心会聚畴之间转换,从而将这一可控的导电性差异用于数据存储。本发明的铁电存储器具有高密度、高响应速度和低能耗调控等优势,有助于利用氧化物拓扑极性结构的非易失性存储器的发展。

附图说明

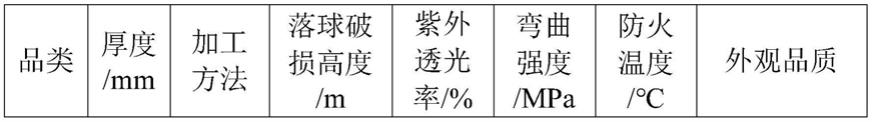

30.图1为本发明的铁电层/介电层复合薄膜的生长和剥离过程示意图;

31.图2为单层极性类斯格明子纳米畴结构的示意图:(a)自支撑复合薄膜中高密度极性类斯格明子示意图,(b)中心发散型和(c)中心会聚型极性类斯格明子的铁电畴结构示意图,(d)自支撑铁电/介电双层结构薄膜的截面示意图,(e)自支撑节电/铁电/介电双层结构薄膜的截面示意图;

32.图3为极性类斯格明子的pfm表征:(a)自支撑双层膜的形貌、vpfm振幅、vpfm相位、lpfm振幅和lpfm相位图,(b)中心发散型和(d)中心会聚型纳米畴的pfm图像放大图;

33.图4为极性类斯格明子的矢量pfm表征:(a)形貌图、vpfm图及四种不同悬臂梁旋转方向(α=0

°

,30

°

,60

°

,90

°

,其中α是悬臂梁与[010]轴的夹角)采集的lpfm图,(b)图(a)中相同区域的极化分布图;

[0034]

图5为极性类斯格明子的4d-stem表征:(a,b)4d-stem的极化分布图;

[0035]

图6为极性类斯格明子的cafm表征:(a)在 5v i)和-5v ii)扫描后在同一区域收集的形貌、vpfm/lpfm及cafm图像;

[0036]

图7为极性类斯格明子在外电场作用下的可逆翻转:(a)外加电场作用下拓扑纳米畴翻转的示意图,(b-d)示意图中三种情况对应的vpfm相位,vpfm振幅,lpfm相位及lpfm振幅图;

[0037]

图8为单个极性类斯格明子在外电场作用下的翻转过程:(a)在依次施加0v、-1v、-4v、-2v, 1v以及 4v外电场后的vpfm振幅(左上图)、vpfm相位(左下图)、lpfm振幅(右上图)及lpfm相位(右下图),(b)极化斯格明子的翻转回线;

[0038]

图9为两种极性类斯格明子不同的阻抗特点(ef,费米能级;ec,导带;ev,价带;eg,带隙);

[0039]

图10为自支撑pton/sto

10

(n=12,16,20)复合薄膜中畴结构与n的依赖关系:(a)n=20,(b)n=16,(c)n=12时的形貌、lpfm振幅和lpfm相位图;

[0040]

图11为经过传统电子束光刻工艺后单层极性类斯格明子的稳定性示意图:(a)电子束光刻工艺流程示意图,(b)转移在p掺杂硅衬底上的pto/sto双层膜经过电子束光刻后形成的周期性方形图案(小图为单个方形区域的afm形貌图),(c)转移在p型掺杂硅衬底上的pto

20

/sto

10

双层膜的vpfm振幅、vpfm相位、lpfm振幅和lpfm相位图。

具体实施方式

[0041]

下文对本发明的示例性实施例的详细描述参考了附图,该附图形成描述的一部分,在该附图中作为示例示出了本发明可实施的示例性实施例,其中本发明的特征由附图标记标识。下文对本发明的实施例的更详细的描述并不用于限制所要求的本发明的范围,而仅仅为了进行举例说明且不限制对本发明的特点和特征的描述,以提出执行本发明的最佳方式,并足以使得本领域技术人员能够实施本发明。但是,应当理解,可在不脱离由所附权利要求限定的本发明的范围的情况下进行各种修改和变型。详细的描述和附图应仅被认为是说明性的,而不是限制性的,如果存在任何这样的修改和变型,那么它们都将落入在此描述的本发明的范围内。此外,背景技术旨在为了说明本技术的研发现状和意义,并不旨在限制本发明或本技术和本发明的应用领域。

[0042]

除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同;本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。

[0043]

需要说明的是,当元件被称为“设置于”另一个元件,它可以直接在另一个元件上或者也可以存在居中的元件;本文所使用的术语“一层”、“另一层”、“一端”以及类似的表述只是为了说明的目的。下面结合具体实施例对本发明进一步进行描述。

[0044]

实施例1

[0045]

本实施例提供一种基于极性拓扑畴结构的复合薄膜,其包括介电层和铁电层,介电层的材料为srtio3,铁电层的材料为pbtio3,所述铁电层平行设置于介电层表面,铁电层是在介电层表面外延生长形成。本实施例通过氧化物分子束外延法进行制备,但这不是限制性的,在其他实施例中,铁电层的生长方法还可以是脉冲激光沉积法、电子束沉积法、原子束沉积法、电泳沉积法、化学气相沉积法、液相外延法等其他外延生长方法,也可以是溶

胶凝胶法等适合氧化物生长的物理或化学薄膜制备方法。

[0046]

在本实施例中,介电层的厚度为其中介电材料单个晶胞层厚度的x倍,铁电层的厚度为其中铁电材料单个晶胞层厚度的y倍,其中x=10,y=20,因此y/x=2,复合薄膜的厚度约为12nm,复合薄膜在本发明中表示为pbtio3(20u.c.)/srtio3(10u.c.)或pto

20

/sto

10

,其具体制备方法如下:

[0047]

(1)采用氧化物分子束外延法在(001)方向的sto(srtio3)单晶衬底上沉积一层sao(sr3al2o6)水溶性牺牲层作为过渡层(图1);需要说明的是,该过渡层并不局限于水溶性牺牲层,在其他实施例中,还可以是酸腐蚀牺牲层或碱腐蚀牺牲层,分别可用酸溶液或碱溶液将过渡层去除;

[0048]

(2)采用氧化物分子束外延法在sao过渡层上沉积一层10个sto(srtio3)晶胞层厚度的薄膜(图1);

[0049]

(3)采用氧化物分子束外延法在(2)所述的sto层上沉积一层20个pto(pbtio3)晶胞层厚度的薄膜(图1);

[0050]

(4)将sao水溶性牺牲层用去离子水溶解去除,使得pto/sto双层结构与衬底分离,得到pto

20

/sto

10

(铁电体/介电体)复合薄膜。

[0051]

本实施例通过调节pto和sto层的厚度,借助氧化物分子束外延法及水溶法制备自支撑pto

20

/sto

10

复合薄膜,最终在pto

20

/sto

10

结构中实现了单层极性类斯格明子拓扑纳米畴的制备,如图3和图7所示,这些极性类斯格明子密度高且相互独立。

[0052]

本发明采用导电原子力显微镜(cafm)表征样品的导电性以及采用矢量压电力显微镜(vector pfm)探测纳米畴类型,分析出畴结构的演变与导电性高低的关联。如图3~图5所示,通过压电力显微镜(pfm)和扫描/透射电子显微镜(s/tem)进行表征,可以看到复合薄膜中具有中心发散型和中心会聚型的极性类斯格明子拓扑纳米畴,在导电原子力显微镜(cafm)下可以表征这两类拓扑纳米畴不同的阻抗信息(图6),cafm图像显示中心发散型纳米畴处于高导电状态,中心会聚型纳米畴处于低导电状态。

[0053]

进一步地,本实施将上述复合薄膜转移在表面镀pt的si衬底上(图2),用作铁电存储器。从图7中看到复合薄膜中存在两种纳米畴的自发状态(i),施加 5v外加电场将纳米畴全部翻转为中心发散型拓扑畴(ii),继续施加-5v将纳米畴全部翻转为中心会聚型拓扑畴(iii),说明中心发散型和中心会聚型的纳米畴可以通过施加外电场相互转换,且具有不同的电阻行为。

[0054]

因此,在本实施例中,在铁电存储器两端(即铁电层远离si衬底的一端和si衬底远离复合薄膜的一端)偏置正向电压时(如 5v),极化形成的中心发散型纳米畴使得复合薄膜中的载流子形成正向导通的二极管特性;相反地,在铁电存储器两端偏置负向电压时(如-5v),极化形成的中心会聚型纳米畴使得复合薄膜中的载流子形成负向导通的二极管特性。在正负向极化操作后分别以同一电压偏置于铁电存储器两端时,可以读取出不同的电流,而这种电流信息可以作为存储信息。例如图9a所示,偏置 5v作为读取电压时,正向极化后的电流约0.5

×

102pa,其可定义为存储状态“1”(低阻态),而偏置-5v产生负向极化后的电流近似于零,其可定义为存储状态“0”(高阻态),施加 5v和-5v偏置电压可以实现在高导电态中心发散型纳米畴和低导电态中心会聚型纳米畴之间的可逆切换,实现信息读写。图9b示出了两种不同类型拓扑结构的能带示意图:极性类斯格明子中心发散,空穴型载流子注

入纳米畴中心区域,将费米能级移动到价带以下,因此,势垒宽度变窄,从而导致高导电状态(i);相比之下,由于发散度较小,中心会聚型的纳米畴保持在低导电状态(ii)。

[0055]

需要说明的是,铁电存储器的读写电压并非限定于

±

5v,本领域技术人员可以根据高低阻状态的电流比、读功耗等因素选择读写电压。如图8所示,本实施例的铁电存储器在偏置电压的大小超过1v时(本实施例中|e|m≈0.083v/nm)均可以使得极性类斯格明子的极化方向产生偏转,从而改变铁电存储器的电阻状态,实现信息读写;进一步地,在偏置电压的大小达到3v时(本实施例中|e|m=0.25v/nm),可以实现极性类斯格明子的极化方向产生180

°

最大角度的偏转,因此在实际应用时,可以根据所需的高低阻状态的电流比合理选取读写电压。

[0056]

此外,上述单层极性类斯格明子可以与硅基半导体工业兼容,如图11所示,将自支撑复合薄膜转移在p掺杂的硅衬底上,并通过电子束光刻工艺将薄膜蚀刻成周期性排列的方形图案,拓扑纳米畴仍然存在并且是可翻转的。这表明独立薄膜与其中的极性类斯格明子可以与硅集成,并且能够一定程度上承受工艺流程中损伤。

[0057]

对比例1

[0058]

本对比例提供一种复合薄膜,其结构和制备方法与实施例1基本相同,主要区别在于:

[0059]

1)本对比例中x=10,y=16,因此y/x=1.6,复合薄膜的厚度约为10nm,复合薄膜在本发明中表示为pto

16

/sto

10

。

[0060]

最终表征pto

16

/sto

10

复合薄膜的形貌、lpfm振幅和lpfm相位图,与实施例1的表征结果汇总于图10中。

[0061]

对比例2

[0062]

本对比例提供一种复合薄膜,其结构和制备方法与实施例1基本相同,主要区别在于:

[0063]

1)本对比例中x=10,y=12,因此y/x=1.2,复合薄膜的厚度约为9nm,复合薄膜在本发明中表示为pto

12

/sto

10

。

[0064]

最终表征pto

12

/sto

10

复合薄膜的形貌、lpfm振幅和lpfm相位图,与实施例1的表征结果汇总于图10中。

[0065]

实施例2

[0066]

本实施例提供一种基于极性拓扑畴结构的复合薄膜和铁电存储器,其结构和制备方法与实施例1基本相同,主要区别在于:

[0067]

1)本对比例中x=12,y=21,因此y/x=1.75,复合薄膜的厚度约为13nm,复合薄膜在本发明中表示为pto

21

/sto

12

。

[0068]

最终表征pto

21

/sto

12

复合薄膜的lpfm振幅和lpfm相位图与图10a结果类似。

[0069]

实施例3

[0070]

本实施例提供一种基于极性拓扑畴结构的复合薄膜和铁电存储器,其结构和制备方法与实施例1基本相同,主要区别在于:

[0071]

1)本对比例中x=8,y=18,因此y/x=2.25,复合薄膜的厚度约为10nm,复合薄膜在本发明中表示为pto

18

/sto8。

[0072]

最终表征pto

18

/sto8复合薄膜的lpfm振幅和lpfm相位图与图10a结果类似。

[0073]

实施例4

[0074]

本实施例提供一种基于极性拓扑畴结构的复合薄膜和铁电存储器,其结构和制备方法与实施例1基本相同,主要区别在于:

[0075]

1)本对比例中x=15,y=27,因此y/x=1.8,复合薄膜的厚度约为17nm,复合薄膜在本发明中表示为pto

27

/sto

15

。

[0076]

最终表征pto

27

/sto

15

复合薄膜的lpfm振幅和lpfm相位图与图10a结果类似。

[0077]

实施例5

[0078]

本实施例提供一种基于极性拓扑畴结构的复合薄膜和铁电存储器,其结构和制备方法与实施例1基本相同,主要区别在于:

[0079]

1)本对比例中x=5,y=11,因此y/x=2.2,复合薄膜的厚度约为6nm,复合薄膜在本发明中表示为pto

11

/sto5。

[0080]

最终表征pto

11

/sto5复合薄膜的lpfm振幅和lpfm相位图与图10a结果类似。

[0081]

如图10所示,将实施例1~5和对比例1~2进行对比可以看到,对比例1和2的复合薄膜中均无法观察到单层极性类斯格明子纳米畴结构的存在,这说明复合薄膜中铁电层和介电层的层数比和厚度对极性拓扑畴结构的制备起到了关键性的作用,只有在优选范围内才能在复合薄膜中制备出单层极性类斯格明子。

[0082]

实施例6

[0083]

本实施例提供一种基于极性拓扑畴结构的复合薄膜和铁电存储器,其结构和制备方法与实施例1基本相同,主要区别在于:

[0084]

1)所述铁电层的材料由pbtio3替换为bifeo3,制备得到bfo

20

/sto

10

复合薄膜。

[0085]

最终表征bfo

20

/sto

10

复合薄膜的lpfm振幅和lpfm相位图与图10a结果类似。

[0086]

实施例7

[0087]

本实施例提供一种基于极性拓扑畴结构的复合薄膜和铁电存储器,其结构和制备方法与实施例1基本相同,主要区别在于:

[0088]

1)所述介电层的材料由srtio3替换为catio3,制备得到pto

20

/cto

10

复合薄膜。

[0089]

最终表征pto

20

/cto

10

复合薄膜的lpfm振幅和lpfm相位图与图10a结果类似。

[0090]

实施例8

[0091]

本实施例提供一种基于极性拓扑畴结构的复合薄膜和铁电存储器,其结构和制备方法与实施例1基本相同,主要区别在于:

[0092]

1)在pto

20

/sto

10

复合薄膜的pto表面再沉积一层10个sto晶胞层厚度的薄膜,如图2所示,得到sto

10

/pto

20

/sto

10

三层结构复合薄膜。

[0093]

最终表征sto

10

/pto

20

/sto

10

三层结构复合薄膜的lpfm振幅和lpfm相位图与图10a结果类似。

[0094]

需要说明的是,在其他实施例中,所述铁电层的材料还可以是batio3、pzt、pmn-pt,所述介电层的材料还可以是laalo3、sio2、hfo2,本发明只是对几种常见的材料进行举例说明,无法对介电氧化物材料和铁电氧化物材料进行穷举,这并非对介电氧化物材料和铁电氧化物材料种类的限定;相反地,本发明对于众多介电氧化物材料和铁电氧化物材料制备基于极性拓扑畴结构的复合薄膜具有普适性。

[0095]

在上文中结合具体的示例性实施例详细描述了本发明。但是,应当理解,可在不脱

离由所附权利要求限定的本发明的范围的情况下进行各种修改和变型。详细的描述和附图应仅被认为是说明性的,而不是限制性的,如果存在任何这样的修改和变型,那么它们都将落入在此描述的本发明的范围内。此外,背景技术旨在为了说明本技术的研发现状和意义,并不旨在限制本发明或本技术和本发明的应用领域。

[0096]

更具体地,尽管在此已经描述了本发明的示例性实施例,但是本发明并不局限于这些实施例,而是包括本领域技术人员根据前面的详细描述可认识到的经过修改、省略、例如各个实施例之间的组合、适应性改变和/或替换的任何和全部实施例。权利要求中的限定可根据权利要求中使用的语言而进行广泛的解释,且不限于在前述详细描述中或在实施该申请期间描述的示例,这些示例应被认为是非排他性的。在任何方法或过程权利要求中列举的任何步骤可以以任何顺序执行并且不限于权利要求中提出的顺序。因此,本发明的范围应当仅由所附权利要求及其合法等同物来确定,而不是由上文给出的说明和示例来确定。

[0097]

除非另有限定,本文使用的所有技术以及科学术语具有与本发明所属领域普通技术人员通常理解的相同的含义。当存在矛盾时,以本说明书中的定义为准。厚度、电场强度或者其它值或参数以范围、优选范围、或一系列上限优选值和下限优选值限定的范围表示时,这应当被理解为具体公开了由任何范围上限或优选值与任何范围下限或优选值的任一配对所形成的所有范围,而不论该范围是否单独公开了。例如,1-50的范围应理解为包括选自1、2、3、4、5、6、7、8、9、10、11、12、13、14、15、16、17、18、19、20、21、22、23、24、25、26、27、28、29、30、31、32、33、34、35、36、37、38、39、40、41、42、43、44、45、46、47、48、49或50的任何数字、数字的组合、或子范围、以及所有介于上述整数之间的小数值,例如,1.1、1.2、1.3、1.4、1.5、1.6、1.7、1.8和1.9。关于子范围,具体考虑从范围内的任意端点开始延伸的“嵌套的子范围”。例如,示例性范围1-50的嵌套子范围可以包括一个方向上的1-10、1-20、1-30和1-40,或在另一方向上的50-40、50-30、50-20和50-10。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。