1.本技术涉及半导体技术领域,尤其涉及一种多晶硅电阻。

背景技术:

2.电阻是模拟电路以及混合信号系统中最基本的无源器件,随着工艺的演进,集成电路中常用的电阻从扩散电阻(diffused resistor)和注入电阻(implanted resistor)逐步演进为多晶硅(poly)电阻。

3.在一般的应用场景中,通常可以不考虑poly电阻的电压系数,即认为poly电阻的阻值不随加在其两端的电压变化而发生变化。但在一些对于线性度要求非常高的应用领域,如模拟数字转换(analog to digital convert,da)或数字模拟转换(digital to analog convert,da)、音频驱动等领域,poly电阻的电压系数会造成输出信号的失真,极大影响系统的性能,如果此时仍不考虑poly电阻的电压系数对电阻值的影响,会导致半导体芯片的测试性能远低于仿真性能。

4.但目前少有对poly电阻的电压系数的研究,也没有调整poly电阻的电压系数的方法。

技术实现要素:

5.本技术实施例提供了一种多晶硅电阻,用于降低多晶硅电阻的电压系数。

6.为解决上述技术问题,本技术实施例提供以下技术方案:

7.第一方面,本技术实施例提供一种多晶硅电阻,所述多晶硅电阻包括:多晶硅层、电压模块和衬底层,其中,所述电压模块,用于将所述多晶硅层上的电压传递给所述衬底层。

8.在本技术实施例中,多晶硅电阻包括:多晶硅层、电压模块和衬底层,其中,电压模块用于将多晶硅层上的电压传递给衬底层。本技术实施例中多晶硅电阻中包括有电压模块,该电压模块可以将多晶硅层的电压传递给衬底层,因此衬底层接通有多晶硅层的电压,当多晶硅层的正端电压与负端电压变化时,多晶硅层的电压可以传递至衬底层,因此使得衬底层的电压可以跟随多晶硅层的正端电压与负端电压变化进行调整,即该衬底层的电压值不再固定为零电位,通过衬底层的电压值的调整可以改变多晶硅电阻的耗尽分布,降低多晶硅电阻的衬底电压对阻值的调制作用,进而降低多晶硅电阻的电压系数。

9.在第一方面的一种可能设计中,所述衬底层包括:n阱和p型衬底,所述电压模块传递给所述衬底层的电压施加于所述n阱;或,所述衬底层包括:深n阱,p阱和p型衬底,所述电压模块传递给所述衬底层的电压施加于所述p阱。其中,p型衬底也可以称为半导体衬底。若衬底层为n阱,则通过该衬底层形成的多晶硅电阻为在n阱的多晶硅电阻,电压模块传递给衬底层的电压施加于n阱,例如电压模块连接多晶硅层和该n阱,从而可以将多晶硅层的电压传递给该n阱,该n阱上的衬底电位不能小于0。若衬底层为dnw和p阱,则通过该衬底层形成的多晶硅电阻为在p阱的多晶硅电阻,电压模块传递给衬底层的电压施加于p阱,例如电

压模块连接多晶硅层和该p阱,从而可以将多晶硅层的电压传递给该p阱。

10.在第一方面的一种可能设计中,所述多晶硅层,包括:所述多晶硅层的正端电压对应的第一多晶硅节点、所述多晶硅层的负端电压对应的第二多晶硅节点;所述p型衬底、所述n阱、所述第一多晶硅节点、所述第二多晶硅节点在所述衬底层上形成欧姆接触;或,所述p型衬底、所述p阱、所述第一多晶硅节点、所述第二多晶硅节点在所述衬底层上形成欧姆接触。其中,多晶硅层上输入有正端电压和负端电压,在多晶硅层上输入正端电压的节点为第一多晶硅节点,在多晶硅层上输入负端电压的节点为第二多晶硅节点。以衬底层中包括有n阱和p型衬底为例,p型衬底、n阱、多晶硅层的正端电压对应的第一多晶硅节点、多晶硅层的负端电压对应的第二多晶硅节点与半导体芯片的半导体衬底在衬底层上形成欧姆接触。金属与半导体形成欧姆接触是指在金属和半导体接触的地方是一个纯电阻,而且该电阻越小越好,使得多晶硅电阻操作时,大部分的电压下降在活动区而不在接触面。因此,形成欧姆接触的多晶硅电阻的电流与电压特性是线性关系,斜率越大接触电阻越小,接触电阻的大小直接影响器件的性能指标。

11.在第一方面的一种可能设计中,所述电压模块的输入来自于所述多晶硅层的中间电压,所述中间电压是所述多晶硅层的正端电压与负端电压之间的电压值。其中,电压模块可以连接多晶硅层的中间电压对应的多晶硅节点,因此电压模块的输入来自于多晶硅层的中间电压,该电压模块还可以连接衬底层的衬底节点,因此衬底节点的输入来自于电压模块的输出。

12.在第一方面的一种可能设计中,所述电压模块的输入来自于所述多晶硅层的正端电压和负端电压的平均值。电压模块的输入来自于所述多晶硅层的正端电压和负端电压的平均值,从而衬底层的电压值可以等于多晶硅层的正端电压和负端电压的平均值。多晶硅电阻的电阻值在有效误差范围内保持恒定,多晶硅层的耗尽对多晶硅电阻的阻值的影响消除,因此可以降低多晶硅电阻的电压系数。

13.在第一方面的一种可能设计中,所述电压模块包括:第一导线、第二导线、缓冲器,其中,所述第一导线和所述第二导线都具有两端;所述缓冲器分别连接所述第一导线的一端、所述第二导线的一端;所述第一导线的另一端连接所述衬底层,所述第二导线的另一端连接所述多晶硅层。其中,电压模块中包括有缓冲器,该缓冲器的输出端连接第一导线,第一导线再连接衬底层,缓冲器的输入端连接第二导线,第二导线再连接多晶硅层,从而通过第一导线和第二导线以及缓冲器,可以将多晶硅层的电压传递给衬底层,使得衬底层可以输入有多晶硅层的电压。

14.在第一方面的一种可能设计中,所述电压模块,包括:第一电压单元和第二电压单元,其中,所述第一电压单元的两端分别连接所述衬底层的第一衬底节点、所述多晶硅层的正端电压对应的第一多晶硅节点;所述第二电压单元的两端分别连接所述衬底层的第二衬底节点、所述多晶硅层的负端电压对应的第二多晶硅节点;其中,所述第一衬底节点是所述衬底层中与所述第一多晶硅节点处于同一侧面上的节点,所述第二衬底节点是所述衬底层中与所述第二多晶硅节点处于同一侧面上的节点。具体的,衬底层的第一衬底节点通过第一电压单元连接到多晶硅层的正端电压对应的第一多晶硅节点,衬底层的第二衬底节点通过第二电压单元连接到多晶硅层的负端电压对应的第二多晶硅节点,第一衬底节点是衬底层中与第一多晶硅节点处于同一侧面上的衬底节点,第二衬底节点是衬底层中与第二多晶

硅节点处于同一侧面上的衬底节点。第一衬底节点是衬底层中与第一多晶硅节点处于同一侧面上的衬底节点,该同一侧面可以指的是左面,第二衬底节点是衬底层中与第二多晶硅节点处于同一侧面上的衬底节点,该同一侧面可以指的是右面。

15.在第一方面的一种可能设计中,所述第一衬底节点和所述第二衬底节点关于所述衬底层的中心点对称。第一衬底节点通过第一电压单元可以输入多晶硅层的正端电压,第二衬底节点通过第二电压单元可以输入多晶硅层的负端电压,若第一衬底节点和第二衬底节点关于衬底层的中心点对称,而在衬底层上第一衬底节点和第二衬底节点上的电压可以进行平均,从而衬底层的电压值可以等于第一衬底节点和第二衬底节点上的电压平均值,可以实现对衬底层的电压值的动态调节,使得多晶硅电阻的电阻值在有效误差范围内保持恒定,进而降低多晶硅电阻的电压系数。

16.在第一方面的一种可能设计中,所述第一电压单元包括:第三导线、第四导线、第一缓冲器,其中,所述第三导线和所述第四导线都具有两端;所述第一缓冲器分别连接所述第三导线的一端、所述第四导线的一端;所述第三导线的另一端连接所述第一衬底节点,所述第四导线的另一端连接所述第一多晶硅节点。其中,第一电压单元中包括有第一缓冲器,该第一缓冲器的输出端连接第三导线,第三导线再连接衬底层,第一缓冲器的输入端连接第四导线,第四导线再连接多晶硅层,从而通过第三导线和第四导线以及第一缓冲器,可以将多晶硅层的正端电压传递给衬底层,使得衬底层可以输入有多晶硅层的电压。

17.在第一方面的一种可能设计中,所述第二电压单元包括:第五导线、第六导线、第二缓冲器,其中,所述第五导线和所述第六导线都具有两端;所述第二缓冲器分别连接所述第五导线的一端、所述第六导线的一端;所述第五导线的另一端连接所述第二衬底节点,所述第六导线的另一端连接所述第二多晶硅节点。其中,第二电压单元中包括有第二缓冲器,该第二缓冲器的输出端连接第五导线,第五导线再连接衬底层,第二缓冲器的输入端连接第六导线,第六导线再连接多晶硅层,从而通过第五导线和第六导线以及第二缓冲器,可以将多晶硅层的负端电压传递给衬底层,使得衬底层可以输入有多晶硅层的电压。

18.在第一方面的一种可能设计中,所述多晶硅电阻,还包括:隔离层,其中,所述多晶硅层位于所述隔离层的上表层区域;所述隔离层位于所述衬底层的上表层区域。

19.第二方面,本技术实施例还提供一种多晶硅电阻,所述多晶硅电阻包括:多晶硅层和衬底层,其中,所述多晶硅层上设有多晶硅节点;所述衬底层上设有衬底节点,所述衬底节点与所述多晶硅节点相连。

20.在第二方面的一种可能设计中,所述衬底节点为欧姆接触点。

21.在第二方面的一种可能设计中,所述衬底节点与所述多晶硅节点相连,包括:所述衬底节点与所述多晶硅节点之间通过缓冲器相连。

22.在第二方面的一种可能设计中,所述多晶硅节点设于所述多晶硅层的内部,所述衬底节点和所述多晶硅节点通过金属导线和过孔中的金属相连接。

23.在第二方面的一种可能设计中,当所述多晶硅层有电压输入时,所述多晶硅节点采集的是所述多晶硅层的中间电压,所述中间电压是所述多晶硅层的正端电压和负端电压之间的电压值。

24.在第二方面的一种可能设计中,所述多晶硅节点处于所述多晶硅层的中线所在的截面上。

25.在第二方面的一种可能设计中,所述衬底节点处于所述衬底层的中线所在的截面上。

26.在第二方面的一种可能设计中,所述多晶硅节点采集的是所述多晶硅层的正端电压和负端电压的平均值。

27.在第二方面的一种可能设计中,所述多晶硅层上设有的多晶硅节点包括:所述多晶硅层的正端电压对应的第一多晶硅节点、所述多晶硅层的负端电压对应的第二多晶硅节点。

28.在第二方面的一种可能设计中,所述衬底层上设有的衬底节点包括:第一衬底节点和第二衬底节点,其中,所述第一衬底节点连接到所述第一多晶硅节点,所述第二衬底节点连接到所述第二多晶硅节点;其中,所述第一衬底节点是所述衬底层中与所述第一多晶硅节点处于同一侧面上的节点,所述第二衬底节点是所述衬底层中与所述第二多晶硅节点处于同一侧面上的节点。

29.在第二方面的一种可能设计中,所述第一衬底节点和所述第二衬底节点关于所述衬底层的中心点对称。

30.第三方面,本技术实施例还提供一种半导体芯片的制造方法,包括:提供半导体衬底;在所述半导体衬底的上表层区域注入n阱,或者注入p阱和深n阱以形成衬底层;在所述衬底层的上表层区域生长出隔离层;在所述隔离层的上表层区域注入多晶硅层,所述多晶硅层、所述隔离层和所述衬底层形成多晶硅电阻;将所述多晶硅层上的电压传递给所述衬底层。

31.在第三方面的一种可能设计中,所述将所述多晶硅层上的电压传递给所述衬底层,包括:将所述衬底层的衬底节点连接到所述多晶硅层的中间电压对应的多晶硅节点,所述中间电压是所述多晶硅层的正端电压与负端电压之间的电压值。

32.在第三方面的一种可能设计中,所述将所述多晶硅层上的电压传递给所述衬底层,包括:将所述衬底层的第一衬底节点连接到所述多晶硅层的正端电压对应的第一多晶硅节点;以及,将所述衬底层的第二衬底节点连接到所述多晶硅层的负端电压对应的第二多晶硅节点;其中,所述第一衬底节点是所述衬底层中与所述第一多晶硅节点处于同一侧面上的衬底节点,所述第二衬底节点是所述衬底层中与所述第二多晶硅节点处于同一侧面上的衬底节点。

33.在第三方面的一种可能设计中,所述将所述多晶硅层上的电压传递给所述衬底层,包括:将所述衬底层的电压值调整为所述多晶硅层的正端电压和负端电压的平均值。

附图说明

34.图1为本技术实施例提供的一种多晶硅电阻的组成结构示意图;

35.图2为本技术实施例提供的另一种多晶硅电阻的组成结构示意图;

36.图3为本技术实施例提供的多晶硅电阻内形成的衬底端子的示意图;

37.图4为本技术实施例提供的一种多晶硅电阻的衬底电压的可调整结构示意图;

38.图5为本技术实施例提供的另一种多晶硅电阻的衬底电压的可调整结构示意图;

39.图6为本技术实施例提供的另一种多晶硅电阻的组成结构示意图;

40.图7为本技术实施例提供的另一种多晶硅电阻的组成结构示意图;

41.图8为本技术实施例提供的另一种多晶硅电阻的组成结构示意图;

42.图9为本技术实施例提供的一种半导体芯片的制造方法的流程方框示意图;

43.图10为本技术实施例中包括n阱的多晶硅电阻的半导体芯片的一种应用场景示意图;

44.图11为本技术实施例中包括p阱的多晶硅电阻的半导体芯片的一种应用场景示意图;

45.图12为本技术实施例提供的一种多晶硅电阻的阻值随衬底电压变化的示意图;

46.图13为本技术实施例提供的另一种多晶硅电阻的阻值随衬底电压变化的示意图;

47.图14为本技术实施例提供的多晶硅电阻的阻值随两端电压、衬底电压变化的曲线示意图;

48.图15为现有技术中多晶硅电阻的电压系数示意图;

49.图16为本技术实施例中多晶硅电阻的电压系数示意图;

50.图17为本技术实施例中通过多晶硅电阻提升功率放大器的线性度的示意图。

具体实施方式

51.本技术实施例提供了一种多晶硅电阻,用于降低多晶硅电阻的电压系数。

52.下面结合附图,对本技术的实施例进行描述。

53.本技术的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的术语在适当情况下可以互换,这仅仅是描述本技术的实施例中对相同属性的对象在描述时所采用的区分方式。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,以便包含一系列单元的过程、方法、系统、产品或设备不必限于那些单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它单元。

54.以下分别进行详细说明。

55.本技术实施例提供的多晶硅电阻也可以称为poly电阻,多晶硅电阻的电压系数是指在规定的电压范围内,电压每改变一伏,电阻值的相对变化。由于阻值随电压增高而下降,因此,电压系数通常用负数表示。举例说明如下,可以通过如下计算公式计算出电压系数:

56.α=(r-r0)/r0(v-v0)*106(ppm/v)。

57.其中,r0表示多晶硅电阻的初始值,r表示多晶硅电阻在温度改变后的测量值,v0表示初始的电压,v表示改变后的电压。ppm表示百万分之一。

58.首先请参阅图1所示,本技术一个实施例提供的多晶硅电阻10,多晶硅电阻10包括:多晶硅层101、电压模块102和衬底层103,其中,

59.电压模块102,用于将多晶硅层101上的电压传递给衬底层103。

60.在本技术实施例中,电压模块是连接在多晶硅层和衬底层之间的导电模块,该电压模块可以将多晶硅层上的电压传递给衬底层,从而使得衬底层上可以输入有多晶硅层的电压。在实际应用场景下,该电压模块具有多种实现方式,只要能够实现从多晶硅层到衬底层的电压传递功能即可。例如该电压模块可以是一段导线,通过该导线将多晶硅层上的电压传递给衬底层。又如,该电压模块还可以是缓冲器以及导线,通过该导线将多晶硅层上的

电压输入给缓冲器,经过缓冲器的缓冲之后再通过导线将电压输入给衬底层。

61.需要说明的是,前述的缓冲器是一种使输入等于输出的电路,可以用于增加驱动能力,由于直接连接可能对多晶硅电阻产生不良影响,增加缓冲器能避免产生这些影响。

62.通过前述对本技术实施例的举例说明可知,多晶硅电阻包括:多晶硅层、电压模块和衬底层,其中,电压模块用于将多晶硅层上的电压传递给衬底层。本技术实施例中多晶硅电阻中包括有电压模块,该电压模块可以将多晶硅层的电压传递给衬底层,因此衬底层接通有多晶硅层的电压,当多晶硅层的正端电压与负端电压变化时,多晶硅层的电压可以传递至衬底层,因此使得衬底层的电压可以跟随多晶硅层的正端电压与负端电压变化进行调整,即该衬底层的电压值不再固定为零电位,通过衬底层的电压值的调整可以改变多晶硅电阻的耗尽分布,降低多晶硅电阻的衬底电压对阻值的调制作用,进而降低多晶硅电阻的电压系数。

63.如图2所示,本技术实施例提供的多晶硅电阻10,包括:多晶硅层101、电压模块102衬底层103和隔离层104,其中,

64.电压模块102,用于将多晶硅层101上的电压传递给衬底层103;

65.多晶硅层101位于隔离层104的上表层区域;

66.隔离层104位于衬底层103的上表层区域。

67.其中,当多晶硅层101上有电压输入时,衬底层103可以接收到电压模块102传递给的多晶硅层101的电压,多晶硅层101的电压由多晶硅层101的正端电压与负端电压形成,因此当多晶硅层101的正端电压与负端电压的变化时,电压模块传递给衬底层的电压跟随多晶硅层101的正端电压与负端电压的变化而调整。例如,衬底层103的电压值可以是多晶硅层101的正端电压和负端电压的平均值,可以使得多晶硅电阻10的电阻值在有效误差范围内保持恒定,多晶硅电阻的有效误差范围可以根据实际场景下的多晶硅电阻的精度来确定,例如该有效误差范围可以十万分之一,即电阻值的浮动误差控制在该有效误差范围内时仍然可以确定多晶硅电阻的电阻值(即电阻率)保持恒定。

68.本技术实施例中该多晶硅电阻中具有衬底层,衬底层的电压值(即衬底电压或者衬底电位)可以在多晶硅层的正端电压与负端电压变化时进行调整。即该衬底层的电压值不再固定为零电位,通过衬底层的电压值的调整可以改变多晶硅电阻的耗尽分布,降低多晶硅电阻的衬底电压对阻值的调制作用,进而降低多晶硅电阻的电压系数。

69.需要说明的是,在本技术实施例中,多晶硅电阻的电阻率与掺杂离子的浓度成反比,掺杂离子浓度越大,多晶硅电阻的电阻率越小。而在同一次的离子注入工艺中,不同位置处的离子注入剂量相同,从而多晶硅层内的杂质离子浓度相同,同一次离子注入过程中,形成的多晶硅电阻的电阻率是相同的。

70.在本技术实施例中,多晶硅层的材料是硅,隔离层是用于隔离多晶硅层,隔离层104可以是浅沟槽隔离结构(shallow trench isolation,sti),也可以是场氧化层(field oxide,fox)或者其他隔离结构。通过隔离层可以防止多晶硅层与其下的衬底层产生漏电。

71.在本技术的一些实施例中,衬底层包括:n阱和p型衬底,电压模块传递给衬底层的电压施加于n阱;或,衬底层包括:深n阱(deep n well,dnw),p阱和p型衬底,电压模块传递给衬底层的电压施加于p阱。

72.其中,p型衬底也可以称为半导体衬底。若衬底层为n阱,则通过该衬底层形成的多

晶硅电阻为在n阱的多晶硅电阻,电压模块传递给衬底层的电压施加于n阱,例如电压模块连接多晶硅层和该n阱,从而可以将多晶硅层的电压传递给该n阱,该n阱上的衬底电位不能小于0。若衬底层为dnw和p阱,则通过该衬底层形成的多晶硅电阻为在p阱的多晶硅电阻,电压模块传递给衬底层的电压施加于p阱,例如电压模块连接多晶硅层和该p阱,从而可以将多晶硅层的电压传递给该p阱。

73.可以理解的是,多晶硅电阻类型由注入离子类型决定,电阻的注入离子类型与衬底层无关。

74.在本技术的一些实施例中,衬底层的电压值由电压模块将多晶硅层上的电压传递给衬底层得到。在多晶硅电阻的正端电压与负端电压的变化时,衬底层的电压值可以跟随这种变化而调整,具体的调整方式可以有多种,例如采用电阻值与三端子电压关系的试验方法,可以采集多晶硅电阻的多组正端电压与负端电压,分别测试在衬底层的电压取值,调整衬底层的电压值。例如,可以将衬底层的电压值等于多晶硅层的正端电压和负端电压的平均值,其中,正端电压和负端电压的平均值是指对正端电压值和负端电压值进行平均值计算,计算出的平均值即为衬底层的电压值。例如衬底层的电压值为v

sub

,多晶硅电阻的正端电压为v

plus

,多晶硅电阻的负端电压为v

minus

,当v

sub

是v

plus

和v

minus

的一半时,多晶硅电阻的电阻值在有效误差范围内保持恒定,多晶硅层的耗尽对多晶硅电阻的阻值的影响消除,因此可以降低多晶硅电阻的电压系数。

75.在本技术的一些实施例中,多晶硅层,包括:多晶硅层的正端电压对应的第一多晶硅节点、多晶硅层的负端电压对应的第二多晶硅节点;

76.p型衬底、n阱、第一多晶硅节点、第二多晶硅节点在衬底层上形成欧姆接触;或,

77.p型衬底、p阱、第一多晶硅节点、第二多晶硅节点在衬底层上形成欧姆接触。

78.其中,多晶硅层上输入有正端电压和负端电压,在多晶硅层上输入正端电压的节点为第一多晶硅节点,在多晶硅层上输入负端电压的节点为第二多晶硅节点。以衬底层中包括有n阱和p型衬底为例,p型衬底、n阱、多晶硅层的正端电压对应的第一多晶硅节点、多晶硅层的负端电压对应的第二多晶硅节点与半导体芯片的半导体衬底在衬底层上形成欧姆接触。

79.如图3所示,为本技术实施例提供的多晶硅电阻内形成的衬底端子的示意图。可以将图1和图2所示的多晶硅电阻等效于如图3所示的三端器件,多晶硅电阻的两端节点分别是plus和minus,多晶硅电阻的衬底层上包括有衬底节点,该衬底节点即为图3中的衬底端子rsub,例如该衬底节点可以是欧姆接触点。其中,欧姆接触是指金属和半导体接触形成较小的电阻,衬底端子是外部通过金属再和衬底层连接。金属与半导体形成欧姆接触是指在金属和半导体接触的地方是一个纯电阻,而且该电阻越小越好,使得多晶硅电阻操作时,大部分的电压下降在活动区(active region)而不在接触面。因此,形成欧姆接触的多晶硅电阻的电流与电压(i-v)特性是线性关系,斜率越大接触电阻越小,接触电阻的大小直接影响器件的性能指标。

80.在本技术的一些实施例中,电压模块的输入来自于多晶硅层的中间电压,中间电压是所述多晶硅层的正端电压与负端电压之间的电压值。

81.其中,电压模块可以连接多晶硅层的中间电压对应的多晶硅节点,因此电压模块的输入来自于多晶硅层的中间电压,该电压模块还可以连接衬底层的衬底节点,因此衬底

节点的输入来自于电压模块的输出。

82.衬底层中设有衬底节点,多晶硅层中设有多晶硅节点,当多晶硅层有电压输入时,多晶硅层在正端和负端分别产生正端电压与负端电压,多晶硅节点的电压值可以是多晶硅层的正端电压与负端电压之间的电压值,例如该多晶硅节点的电压值是正端电压与负端电压之间的某一个电压值,则衬底节点和多晶硅节点通过电压模块相连接,该电压模块可以是金属导线,该衬底节点也可以采集到与多晶硅节点的电压值相同的电压,即衬底层的电压值等于多晶硅层的正端电压和负端电压之间的电压值。可选的,当多晶硅层输入有电压时,该多晶硅节点的电压值是多晶硅层的正端电压与负端电压的正中间值,则电压模块的输入来自于所述多晶硅层的正端电压和负端电压的平均值,从而衬底层的电压值可以等于多晶硅层的正端电压和负端电压的平均值。

83.在本技术的一些实施例中,电压模块包括:第一导线、第二导线、缓冲器,其中,

84.第一导线和第二导线都具有两端;

85.缓冲器分别连接第一导线的一端、第二导线的一端;

86.第一导线的另一端连接衬底层,第二导线的另一端连接多晶硅层。

87.其中,电压模块中包括有缓冲器,该缓冲器的输出端连接第一导线,第一导线再连接衬底层,缓冲器的输入端连接第二导线,第二导线再连接多晶硅层,从而通过第一导线和第二导线以及缓冲器,可以将多晶硅层的电压传递给衬底层,使得衬底层可以输入有多晶硅层的电压。

88.举例说明如下,多晶硅电阻的衬底层、多晶硅层的正端电压对应的第一多晶硅节点、多晶硅层的负端电压对应的第二多晶硅节点与半导体芯片的半导体衬底在衬底层上形成欧姆接触,即在多晶硅电阻的衬底层上会形成多个欧姆接触点。如图4所示,为本技术实施例提供的一种多晶硅电阻的衬底电压的可调整结构示意图,从多晶硅电阻上确定出中间电压对应的多晶硅节点,将衬底层的衬底节点通过电压模块连接到中间电压对应的多晶硅节点,中间电压是多晶硅层的正端电压与负端电压之间的电压值,即可以将多晶硅电阻的衬底层通过电压模块接到多晶硅电阻的正端电压与负端电压之间的电压值,如通过电压模块对正端电压与负端电压取平均值,再将电压平均值通过电压模块传递到衬底层上,从而可以实现对衬底层的电压值的动态调节,使得多晶硅电阻的电阻值在有效误差范围内保持恒定,进而降低多晶硅电阻的电压系数。

89.需要说明的是,本技术实施例中,衬底层上的衬底节点可以是欧姆接触点,为了便于理解,本领域技术人员在面对本发明方案的情况下能够明白选用小电阻器件来实现衬底层和多晶硅层的连接,至于是否需要达到欧姆接触点的规格可以根据当时的工艺能力以及性能需求来确定。

90.进一步的,衬底层的衬底节点连接到中间电压对应的多晶硅节点时,该电压模块还包括:缓冲器,其中,衬底节点通过第一导线、缓冲器、第二导线和多晶硅节点相连接。如图4所示,例如衬底层的电压值为v

sub

,多晶硅电阻的正端电压为v

plus

,多晶硅电阻的负端电压为v

minus

,中间电压v

mid

是多晶硅层的正端电压与负端电压之间的电压值,为了降低poly电阻的电压系数,将poly电阻的衬底层通过电压模块连接到poly电阻的正端电压与负端电压之间的电压值,如对正端电压与负端电压取平均值,再将电压平均值通过一个缓冲器(buffer)连接到衬底层的衬底节点,缓冲器是一种使输入等于输出的电路,可以用于增加

驱动能力,直接连接可能对poly电阻产生不良影响,增加缓冲器能避免产生这些影响。

91.在本技术的另一些实施例中,电压模块,包括:第一电压单元和第二电压单元,其中,

92.第一电压单元的两端分别连接衬底层的第一衬底节点、多晶硅层的正端电压对应的第一多晶硅节点;

93.第二电压单元的两端分别连接衬底层的第二衬底节点、多晶硅层的负端电压对应的第二多晶硅节点;

94.其中,第一衬底节点是衬底层中与第一多晶硅节点处于同一侧面上的节点,第二衬底节点是衬底层中与第二多晶硅节点处于同一侧面上的节点。

95.具体的,衬底层的第一衬底节点通过第一电压单元连接到多晶硅层的正端电压对应的第一多晶硅节点,衬底层的第二衬底节点通过第二电压单元连接到多晶硅层的负端电压对应的第二多晶硅节点,第一衬底节点是衬底层中与第一多晶硅节点处于同一侧面上的衬底节点,第二衬底节点是衬底层中与第二多晶硅节点处于同一侧面上的衬底节点。

96.需要说明的是,第一衬底节点是衬底层中与第一多晶硅节点处于同一侧面上的衬底节点,该同一侧面可以指的是左面,第二衬底节点是衬底层中与第二多晶硅节点处于同一侧面上的衬底节点,该同一侧面可以指的是右面。

97.在本技术的一些实施例中,第一衬底节点和第二衬底节点关于衬底层的中心点对称。其中衬底层的中心点可以是衬底层的中心,例如衬底层为长方形,则该中心点可以是两条对角线的交点,又如衬底层为圆形,则该中心点可以是圆心。第一衬底节点通过第一电压单元可以输入多晶硅层的正端电压,第二衬底节点通过第二电压单元可以输入多晶硅层的负端电压,若第一衬底节点和第二衬底节点关于衬底层的中心点对称,而在衬底层上第一衬底节点和第二衬底节点上的电压可以进行平均,从而衬底层的电压值可以等于第一衬底节点和第二衬底节点上的电压平均值,可以实现对衬底层的电压值的动态调节,使得多晶硅电阻的电阻值在有效误差范围内保持恒定,进而降低多晶硅电阻的电压系数。

98.在本技术的一些实施例中,第一电压单元包括:第三导线、第四导线、第一缓冲器,其中,

99.第三导线和第四导线都具有两端;

100.第一缓冲器分别连接第三导线的一端、第四导线的一端;

101.第三导线的另一端连接第一衬底节点,第四导线的另一端连接第一多晶硅节点。

102.其中,第一电压单元中包括有第一缓冲器,该第一缓冲器的输出端连接第三导线,第三导线再连接衬底层,第一缓冲器的输入端连接第四导线,第四导线再连接多晶硅层,从而通过第三导线和第四导线以及第一缓冲器,可以将多晶硅层的正端电压传递给衬底层,使得衬底层可以输入有多晶硅层的电压。

103.在本技术的一些实施例中,第二电压单元包括:第五导线、第六导线、第二缓冲器,其中,

104.第五导线和第六导线都具有两端;

105.第二缓冲器分别连接第五导线的一端、第六导线的一端;

106.第五导线的另一端连接第二衬底节点,第六导线的另一端连接第二多晶硅节点。

107.其中,第二电压单元中包括有第二缓冲器,该第二缓冲器的输出端连接第五导线,

第五导线再连接衬底层,第二缓冲器的输入端连接第六导线,第六导线再连接多晶硅层,从而通过第五导线和第六导线以及第二缓冲器,可以将多晶硅层的负端电压传递给衬底层,使得衬底层可以输入有多晶硅层的电压。

108.举例说明如下,多晶硅电阻的衬底层、多晶硅层的正端电压对应的第一多晶硅节点、多晶硅层的负端电压对应的第二多晶硅节点与半导体芯片的半导体衬底在衬底层上形成欧姆接触,即在多晶硅电阻的衬底层上会形成多个欧姆接触点。如图5所示,本技术的前述实施例中还可以将一边的衬底电位接到电阻正端,另一边的衬底电位接到电阻负端,从而可以消除poly电阻的衬底电位对阻值的调制作用,进而降低poly电阻电压系数。

109.如图5所示,衬底层靠近正端电压的电压值为v

sub

,衬底层靠近负端电压的电压值为v

sub-,多晶硅电阻的正端电压为v

plus

,多晶硅电阻的负端电压为v

minus

,可以将正端电压连接到靠近正端的衬底层上的欧姆接触点,将负端电压连接到靠近负端的衬底层上的欧姆接触点,其中连接方式包括通过电压模块连接到衬底层,例如通过第一电压单元和第二电压单元,每个电压单元包括缓冲器(buffer)和导线,缓冲器是一种使输入等于输出的电路,可以用于增加驱动能力,直接连接可能对poly电阻产生不良影响,增加缓冲器能避免产生这些影响。

110.需要说明的是,本技术实施例中衬底层的电压由电压模块将多晶硅层上的电压传递得到,例如该衬底层的电压可以等于多晶硅电阻的正端电压和负端电压的平均值,在图4所示中,多晶硅电阻的正端电压为v

plus

,多晶硅电阻的负端电压为v

minus

,中间电压为v

mid

,图4中左部分的电阻和右部分的电阻是两个完全相同的电阻,将中间电压v

mid

的多晶硅节点和衬底层通过电压模块连接到了一起,则衬底层的电压可以等于该中间电压v

mid

。在图5所示中,左部分的衬底层通过第一电压单元连接多晶硅层的正端电压对应的多晶硅节点,右部分的衬底层通过第二电压单元连接多晶硅层的负端电压对应的多晶硅节点,在衬底层上通过两端电压的综合,也等效于使衬底电位等于正端和负端的平均值。

111.通过前述实施例对本技术的举例说明可知,多晶硅层、电压模块和衬底层,其中,电压模块用于将多晶硅层上的电压传递给衬底层。本技术实施例中多晶硅电阻中包括有电压模块,该电压模块可以将多晶硅层的电压传递给衬底层,因此衬底层接通有多晶硅层的电压,当多晶硅层的正端电压与负端电压变化时,多晶硅层的电压可以传递至衬底层,因此使得衬底层的电压可以跟随多晶硅层的正端电压与负端电压变化进行调整,即该衬底层的电压值不再固定为零电位,通过衬底层的电压值的调整可以改变多晶硅电阻的耗尽分布,降低多晶硅电阻的衬底电压对阻值的调制作用,进而降低多晶硅电阻的电压系数。

112.请参阅图6所示,本技术实施例还提供一种多晶硅电阻10,多晶硅电阻10包括:多晶硅层101和衬底层103,其中,

113.多晶硅层101上设有多晶硅节点1011;

114.衬底层103上设有衬底节点1031,衬底节点1031与多晶硅节点1011相连。

115.其中,图6中以虚线连接衬底节点1031与多晶硅节点1011,以说明衬底节点1031与多晶硅节点1011相连,在实际的半导体芯片制造时,该虚线可以是金属导线,但是该金属导线的位置可以根据加工工艺和需求来调整,此处仅作示意说明,不作为对本技术实施例的限定。

116.本技术实施例中该多晶硅电阻中具有衬底层,衬底节点和多晶硅节点相连接,当

多晶硅层有电压输入时,该多晶硅节点处于多晶硅层中也会采集到电压值,多晶硅节点的电压值会传导给衬底节点,因此衬底层也会产生电压,衬底层的电压值(即衬底电压或者衬底电位)可以在多晶硅层的正端电压与负端电压变化时进行调整。即该衬底层的电压值不再固定为零电位,通过衬底层的电压值的调整可以改变多晶硅电阻的耗尽分布,降低多晶硅电阻的衬底电压对阻值的调制作用,进而降低多晶硅电阻的电压系数。

117.如图7所示,本技术实施例还提供一种多晶硅电阻10,多晶硅电阻10包括:多晶硅层101、衬底层103和隔离层104,其中,

118.多晶硅层101位于隔离层104的上表层区域,多晶硅层101上设有多晶硅节点1011;

119.隔离层104位于衬底层103的上表层区域;

120.衬底层103上设有衬底节点1031,衬底节点1031与多晶硅节点1011相连。

121.在本技术的一些实施例中,衬底节点为欧姆接触点。

122.需要说明的是,衬底层上的衬底节点可以是欧姆接触点,为了便于理解,本领域技术人员在面对本发明方案的情况下能够明白选用小电阻器件来实现衬底层和多晶硅层的连接,至于是否需要达到欧姆接触点的规格可以根据当时的工艺能力以及性能需求来确定。

123.在本技术的一些实施例中,衬底节点与多晶硅节点相连,包括:

124.衬底节点与多晶硅节点之间通过缓冲器相连。

125.其中,衬底节点和多晶硅节点的连接可以包括如下两种情况,一种连接方式是直接通过导线相连接,另一种连接方式是通过缓冲器(buffer)相连。需要说明的是,前述的缓冲器是一种使输入等于输出的电路,可以用于增加驱动能力,由于直接连接可能对多晶硅电阻产生不良影响,增加缓冲器能避免产生这些影响。

126.在本技术的一些实施例中,多晶硅节点设于多晶硅层的内部,衬底节点和多晶硅节点通过金属导线和过孔中的金属相连接。

127.其中,如图6所示,从多晶硅层中的多晶硅节点向外延伸出金属导线,从衬底层中的衬底节点向外延伸出金属导线,两个金属导线再通过过孔中的金属相连接,从而可以实现衬底节点和多晶硅节点通过金属导线以及过孔中的金属相连接,当多晶硅层有电压输入时,该多晶硅节点处于多晶硅层中也会采集到电压值,多晶硅节点的电压值会传导给衬底节点,因此衬底层也会产生电压。

128.在本技术的一些实施例中,当多晶硅层有电压输入时,多晶硅节点采集的是多晶硅层的正端电压和负端电压之前的电压值。

129.其中,衬底层中设有衬底节点,多晶硅层中设有多晶硅节点,当多晶硅层有电压输入时,多晶硅层在正端和负端分别产生正端电压与负端电压,该多晶硅节点的电压值可以是多晶硅层的正端电压与负端电压之间的电压值,例如该多晶硅节点的电压值是正端电压与负端电压之间的某一个电压值,则衬底节点和多晶硅节点通过金属导线相连接,该衬底节点也可以采集到与多晶硅节点的电压值相同的电压,即衬底层的电压值等于多晶硅层的正端电压与负端电压之间的电压值。

130.可选的,当多晶硅层输入有电压时,该多晶硅节点的电压值是多晶硅层的正端电压与负端电压的正中间值,即衬底层的电压值等于多晶硅层的正端电压和负端电压的平均值。

131.在本技术的一些实施例中,多晶硅节点处于多晶硅层的中线所在的截面上。

132.例如,多晶硅层可以是规则形状的矩形或者正方形,多晶硅层的中线可以是矩形或者正方形的中心所在的直线,当多晶硅层为不规则形状时,多晶硅层的中线可以是多晶硅层的最左端节点与最右端节点之间的中点所在的直线。如图6或图7所示,多晶硅节点1011设置在多晶硅层101的中线所在的截面上,当多晶硅层有电压输入时,多晶硅层在正端和负端分别产生正端电压与负端电压,该多晶硅节点的电压值可以是多晶硅层的正端电压与负端电压之间的电压值。

133.在本技术的一些实施例中,衬底节点处于衬底层的中线所在的截面上。

134.例如,衬底层可以是规则形状的矩形或者正方形,衬底层的中线可以是矩形或者正方形的中心所在的直线,当衬底层为不规则形状时,衬底层的中线可以是衬底层的最左端节点与最右端节点之间的中点所在的直线。如图6或图7所示,多晶硅节点1011设置在多晶硅层101的中线所在的截面上,衬底节点1031设置在衬底层103的中线所在的截面上,当多晶硅层有电压输入时,多晶硅层在正端和负端分别产生正端电压与负端电压,该多晶硅节点的电压值可以是多晶硅层的正端电压与负端电压之间的电压值。多晶硅节点的电压值会传导给衬底节点,因此衬底层也会产生电压。

135.在本技术的一些实施例中,如图8所示,多晶硅层上设有的多晶硅节点包括:多晶硅层的正端电压对应的第一多晶硅节点1012、多晶硅层的负端电压对应的第二多晶硅节点1013。其中,第一多晶硅节点1012连接正端电压,第二多晶硅节点1013连接负端电压。

136.在本技术的一些实施例中,衬底层上设有的衬底节点包括:第一衬底节点1032和第二衬底节点1033,其中,

137.第一衬底节点1032连接到第一多晶硅节点1012,第二衬底节点1033连接到第二多晶硅节点1013,第一衬底节点1032是衬底层中与第一多晶硅节点1012处于同一侧面上的节点,第二衬底节点1033是衬底层中与第二多晶硅节点1013处于同一侧面上的节点。

138.需要说明的是,第一衬底节点是衬底层中与第一多晶硅节点处于同一侧面上的衬底节点,该同一侧面可以指的是左面,第二衬底节点是衬底层中与第二多晶硅节点处于同一侧面上的衬底节点,该同一侧面可以指的是右面。

139.在本技术的一些实施例中,第一衬底节点和第二衬底节点关于衬底层的中心点对称。其中衬底层的中心点可以是衬底层的中心,例如衬底层为长方形,则该中心点可以是两条对角线的交点,又如衬底层为圆形,则该中心点可以是圆心。第一衬底节点通过第一电压单元可以输入多晶硅层的正端电压,第二衬底节点通过第二电压单元可以输入多晶硅层的负端电压,若第一衬底节点和第二衬底节点关于衬底层的中心点对称,而在衬底层上第一衬底节点和第二衬底节点上的电压可以进行平均,从而衬底层的电压值可以等于第一衬底节点和第二衬底节点上的电压平均值,可以实现对衬底层的电压值的动态调节,使得多晶硅电阻的电阻值在有效误差范围内保持恒定,进而降低多晶硅电阻的电压系数。

140.前述实施例介绍了本技术实施例提供的半导体电阻,接下来介绍本技术实施例提供的一种半导体芯片的制造方法,如图9所述,本技术实施例提供的一种半导体芯片的制造方法,包括:

141.步骤901、提供半导体衬底。

142.其中,半导体衬底也可以称为p型衬底,半导体衬底的材料包括硅、锗、锗化硅、砷

化嫁等半导体材料,可以根据半导体衬底上形成的半导体器件选择半导体衬底的类型。该半导体衬底可以是p型衬底。

143.步骤902、在半导体衬底的上表层区域注入n阱,或者注入p阱和深n阱,以形成衬底层。

144.其中,在已提供的半导体衬底上注入n阱可以形成衬底层,或者在已提供的半导体衬底上注入p阱和深n阱可以形成衬底层。该衬底层可以有多种,例如衬底层包括:n阱和p型衬底;或,衬底层包括:深n阱(deep n well,dnw)、p阱和p型衬底,深n阱位于p阱的下方外表面区域。其中,若衬底层为n阱,则通过该衬底层形成的多晶硅电阻为n型电阻,若衬底层为dnw和p阱,则通过该衬底层形成的多晶硅电阻为p型电阻。

145.步骤903、在衬底层的上表层区域生长出隔离层。

146.其中,隔离层是用于隔离多晶硅层,隔离层可以是sti,也可以是fox或者其他隔离结构。通过隔离层可以防止多晶硅层与其下的衬底层产生漏电。

147.步骤904、在隔离层的上表层区域注入多晶硅层,多晶硅层、隔离层和衬底层形成多晶硅电阻。

148.其中,多晶硅层的材料是硅,则依次注入的多晶硅层、隔离层和衬底层可以形成前述实施例提供的多晶硅电阻。

149.在本技术的一些实施例中,当半导体芯片上设置有多个多晶硅电阻时,半导体芯片还包括:p阱注入层,其中,

150.p阱注入层将多个多晶硅电阻的衬底层隔离开。

151.其中,同一芯片上有很多独立的n阱时,每个n阱需要用p注入区域隔离开,形成n阱或者深n阱,采用p型注入形成反偏的pn结,使不同的n阱之间形成电气隔离。

152.步骤905、将多晶硅层上的电压传递给衬底层。

153.在本技术实施例中,在半导体衬底上形成多晶硅电阻后,该多晶硅电阻的衬底电压不是固定的0电位,而是可以根据多晶硅层的正端电压与负端电压的变化调整衬底层的电压值。

154.接下来对衬底电压的调整方式进行举例说明,步骤905将多晶硅层上的电压传递给衬底层,包括:

155.将衬底层的电压值调整为多晶硅层的正端电压和负端电压的平均值。

156.本技术实施例中,对于衬底层的电压值跟随多晶硅电阻的正端电压与负端电压的变化而调整的方式可以有多种,例如可以采集多晶硅电阻的多组正端电压与负端电压,分别测试在衬底层的电压取值,以使得多晶硅电阻的阻值保持恒定。

157.本技术的一些实施例中,步骤905将多晶硅层上的电压传递给衬底层,包括:

158.将衬底层的衬底节点连接到多晶硅层的中间电压对应的多晶硅节点,中间电压是多晶硅层的正端电压与负端电压之间的电压值。

159.例如,衬底层的电压值等于多晶硅层的正端电压与负端电压之间的电压值。例如,衬底层的电压值可以等于正端电压和负端电压的平均值,即可以对正端电压值和负端电压值进行平均值计算,计算出的平均值即为衬底层的电压值。例如衬底层的电压值为v

sub

,多晶硅电阻的正端电压为v

plus

,多晶硅电阻的负端电压为v

minus

,当v

sub

是v

plus

和v

minus

的一半时,多晶硅电阻的电阻值在有效误差范围内保持恒定,多晶硅层的耗尽对多晶硅电阻的阻

值的影响消除,因此可以降低多晶硅电阻的电压系数。

160.在本技术的另一些实施例中,步骤905将多晶硅层上的电压传递给衬底层,包括:

161.将衬底层的第一衬底节点连接到多晶硅层的正端电压对应的第一多晶硅节点,衬底层的第二衬底节点连接到多晶硅层的负端电压对应的第二多晶硅节点,第一衬底节点是衬底层中与第一多晶硅节点处于同一侧面上的衬底节点,第二衬底节点是衬底层中与第二多晶硅节点处于同一侧面上的衬底节点。

162.其中,衬底层的第一衬底节点连接到多晶硅层的正端电压对应的第一多晶硅节点,衬底层的第二衬底节点连接到多晶硅层的负端电压对应的第二多晶硅节点,第一衬底节点是衬底层中与第一多晶硅节点处于同一侧面上的衬底节点,第二衬底节点是衬底层中与第二多晶硅节点处于同一侧面上的衬底节点。

163.如图5所示,本技术的前述实施例中还可以将一边的衬底电位接到电阻正端,另一边的衬底电位接到电阻负端,从而可以消除poly电阻的衬底电位对阻值的调制作用,进而降低poly电阻电压系数。需要说明的是,第一衬底节点是衬底层中与第一多晶硅节点处于同一侧面上的衬底节点,该同一侧面可以指的是左面,第二衬底节点是衬底层中与第二多晶硅节点处于同一侧面上的衬底节点,该同一侧面可以指的是右面。

164.通过前述实施例对本技术的举例说明可知,本技术实施例提供的方法中,该衬底层的电压值跟随多晶硅层的正端电压与负端电压的变化而调整,使得多晶硅电阻的电阻值在有效误差范围内保持恒定。本技术实施例中多晶硅电阻的衬底层的电压值(即衬底电压或者衬底电位)可以在多晶硅层的正端电压与负端电压变化时进行调整,即该衬底层的电压值不再固定为零电位,通过衬底层的电压值的调整可以改变多晶硅电阻的耗尽分布,降低多晶硅电阻的衬底电压对阻值的调制作用,进而降低多晶硅电阻的电压系数。

165.为便于更好的理解和实施本技术实施例的上述方案,下面举例相应的应用场景来进行具体说明。

166.本技术实施例提供的半导体芯片中,可以有效的降低poly电阻的电压系数,保证系统的线性度。本技术实施例公布了一种无需更改工艺,通过动态调节poly电阻的衬底电压,来降低poly电阻的电压系数的方法,这里的衬底电压是指poly电阻的衬底层的电压值。本技术实施例中可以将poly电阻的衬底电位接到电阻正负端电压的中间值,使衬底电压等于电阻正端电压值加上负端电压值的一半。本技术实施例中还可以将一边衬底电位接到电阻正端另一边衬底电位接到电阻负端,消除poly电阻的衬底电位对阻值的调制作用,进而降低poly电阻电压系数。

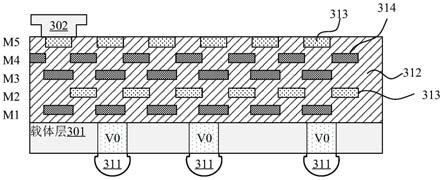

167.可调节衬底电位的poly电阻的结构类型可以分为两大类,p型和n型。本技术实施例提供的poly电阻的剖面结构进行说明,如图10和图11所示。如图10所示的n型poly电阻包括p型衬底,以及在p型衬底(psub)上的n型注入层,同一芯片上会有很多独立的n阱(nwell),每个n阱用p注入区域隔离开,形成图10所示的所示n阱。

168.在图10所示的nwell中,先生长一层sti,防止poly与其下的nwell产生漏电,poly会淀积在sti上方区域内部,作为poly电阻的主体部分。大部分靠中间的poly,这个主体部分和边缘部分的后续处理方式不同,进而阻值有差异,最后是制造形成与psub、poly电阻的衬底层(substrate,简写为sub)、poly电阻正端(plus)、负端(minus)的欧姆接触。psub是芯片最下层的半导体衬底,poly电阻的衬底层是在poly、sti下面且在psub上面的区域。因此

图10中poly电阻的衬底层是nwell,该n型注入层构成所述n型poly电阻的衬底层,该衬底层用于调节降低poly电阻的电压系数,该可调的衬底电压接到此n型衬底上。

169.图11中所示的是n型poly电阻,包括采用p型注入形成反偏的pn结,使不同的n阱之间形成电气隔离。在图11所示的dnw中,再进行一次p型注入,形成p阱(pwell),dnw和pwell。在图11所示的pwell中,先生长一层sti,防止poly与其下的nwell或pwell产生漏电,poly会淀积在sti上方区域内部,作为poly电阻的主体部分。大部分靠中间的poly,这个主体部分和边缘部分的后续处理方式不同,进而阻值有差异,最后是制造形成与psub、poly电阻的衬底层、poly电阻正端(plus)、负端(minus)的欧姆接触。psub是芯片最下层的半导体衬底,poly电阻的衬底层是在poly、sti下面但又在psub上面的区域,图11中poly电阻中的衬底层是dnw中的pwell。该pwell构成所述p型poly电阻的衬底层,该衬底层用于调节降低poly电阻的电压系数,该可调的衬底电压接到此p型衬底上。

170.其中,nwell中的n 是再注入一次浓度较大的n型杂质,使该点接触电阻变小,即形成欧姆接触,以便更好的控制nwell的电位。又如,pwell中的p 再注入一次浓度较大的p型杂质,使该点接触电阻变小,即形成欧姆接触,以便更好的控制pwell的电位。以此同理,图10和图11中衬底层的电压值为v

sub

,多晶硅电阻的正端电压为v

plus

,多晶硅电阻的负端电压为v

minus

,p阱注入层的电压为v

psub

,dnw的电压为v

dnw

。

171.需要说明的是,psub一般接0电位,所以n阱不能接小于0的电位,以防止pn结正偏、芯片出问题,所以图10中的poly电阻的衬底电位不能小于0。但图11中的dnw接的是正电位,pn结永远不会正偏,dnw里面的pwell可正可负,图11中的poly电阻的衬底电位可正可负。poly(多晶硅)是一种常用材料,可以用于做mos管、电阻等,用ploy制作的电阻被称为poly电阻。

172.如图12和图13所示,将poly电阻负端接0电位,在不同衬底电压(符号为vb)下,阻值与正端电压的变化关系,die1表示芯片1,die2表示芯片2,rs表示poly电阻的阻值,单位为欧姆(ohm),图12中6736至6750为实测的欧姆值,图13中6792至6808为实测的欧姆值,在两个不同的芯片上测试衬底电压,从图12和图13中两个不同芯片的结果可以看到,正负端压差相等时,衬底电压对电阻的阻值有着明显的影响。

173.在本技术实施例中,衬底电压会改变poly电阻上的耗尽分布(depletion)。耗尽主要与poly上电压与衬底电压差相关,即poly电阻正端耗尽与v

plus-v

sub

相关,poly电阻负端耗尽与v

minus-v

sub

相关。可粗略地认为阻值受poly整体耗尽影响的比例为α,于是有

[0174][0175]

化简为:

[0176][0177]

其中,r为poly电阻的阻值,r0为poly电阻正端、负端、衬底均为0v时的阻值。从式2可知,当v

sub

是v

plus

和v

minus

的一半时,poly耗尽对poly电阻阻值的影响消除,因此可以降低电压系数。α可以认为是poly电阻两端电压对poly电阻上电子分布的影响因数。

[0178]

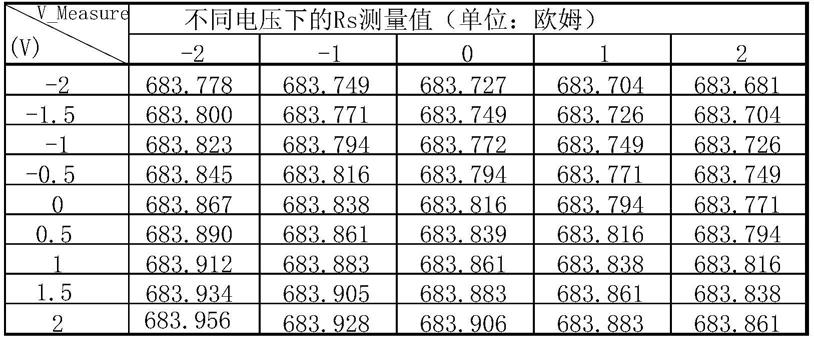

如下表1所示,为poly电阻阻值随两端电压、衬底电压变化关系表,在表1中对角线

上的不同情况下,poly电阻阻值差异很小。

[0179][0180]

如图14所示,为poly电阻阻值随两端电压、衬底电压曲线关系,以衬底电压v

sub

的不同取值为例进行说明,图14给出了将poly电阻负端固定为0v,仿真得到的不同正端电压、衬底电压的阻值情况,图14中所示的数据即为表1中统计所得的数据。从图15中能看出,使衬底的电位跟随电阻正端、负端电压变化时,poly电阻基本恒定,这与式2相符。

[0181]

如图15所示,为现有技术中不采用本技术实施例的方案即衬底层接固定的零电位时,归一化的poly电阻值随poly电阻两端电压的变化关系。图15中,w为电阻的宽度,l是电阻的长度,seg是电阻并联段数,vbs就是poly电阻的衬底电位,固定为0。r(v)/r(-2)就是“归一化的poly电阻值”,是将两端加-2v时的阻值归一化为1,其他电阻值相对于此值的比例,r(v)/r(-2)-1为电阻的变化率。si w/l/seg是指硅测试数据,下面的model是拟合的数据,vin是加在poly电阻两端的电压值,图15中以三条拟合曲线为例,w1=4μm,w2=8μm,w3=12μm,经过测试,现有技术中poly电阻的阻值变化较大,

±

2v内电阻阻值变化幅度达到0.0200%。图16为采用本技术实施例提供的衬底层的电压进行调整方案,poly电阻的电压系数被明显降低。图16中,vin是加在poly电阻两端的电压值,vbs是poly电阻的衬底电位,vbs等于0.5乘以vin,采用本技术实施例的方案后,poly电阻的阻值变化较小,

±

2v内电阻阻值变化幅度小于0.0100%,poly电阻的电压系数被明显降低。

[0182]

如图17,为本技术实施例中通过多晶硅电阻提升功率放大器的线性度的示意图。其中,测试仪器为audio precision,thd n ratio是指总谐波和噪声失真比例,是用来衡量电路、器件等非线性的一种指标。fs表示full scale,满调幅。dbfs表征数字信号的幅度,最大为0,代表的就是16个二进制的1(16bit数字信号),或24个1(24bit数字信号)。ch指的是channel,通道,这里测试的是两个通路的性能。采用现有技术方案时,某功率放大器(power amplifier,pa)的总谐波失真(total harmonic distortion,简称thd)随输出幅度的关系为thd1和thd2,采用本技术实施例提供的衬底电压的调整方案后,某pa的thd随输出幅度的关系为thd3和thd4,可见该功率放大器的thd在输出幅度较大的情况下,本技术实施例提供的pa线性度得到了15db以上的提升。

[0183]

通过前述的举例说明可知,本技术实施例中,poly电阻的衬底电压跟随电阻两端的电压变化,消除poly的耗尽,进而降低poly电阻的电压系数。

[0184]

需要说明的是,对于前述的各方法实施例,为了简单描述,故将其都表述为一系列的动作组合,但是本领域技术人员应该知悉,本技术并不受所描述的动作顺序的限制,因为依据本技术,某些步骤可以采用其他顺序或者同时进行。其次,本领域技术人员也应该知

悉,说明书中所描述的实施例均属于优选实施例,所涉及的动作和模块并不一定。

[0185]

另外需说明的是,以上所描述的装置实施例仅仅是示意性的,其中所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部模块来实现本实施例方案的目的。另外,本技术提供的装置实施例附图中,模块之间的连接关系表示它们之间具有通信连接,具体可以实现为一条或多条通信总线或信号线。

[0186]

通过以上的实施方式的描述,所属领域的技术人员可以清楚地了解到本技术可借助通用硬件的方式来实现,当然也可以通过专用硬件包括专用集成电路、专用cpu、专用存储器、专用元器件等来实现。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。