1.本实用新型涉及电路电子技术领域,特别涉及一种显示屏界面显示加速电路及系统。

背景技术:

2.随着科技水平的提高,电子显示屏的应用越来越广,其中spi接口的显示屏占有相当一部分比重。

3.现有技术驱动spi接口屏时,存储界面资源的存储器和显示屏用了两套不相同的通讯总线,当屏幕需要显示存储器中的界面资源时,需要经历两步操作:第一步,通过存储器的数据总线将存储器中的界面资源读入mcu的内部ram或者外部拓展ram中,第二步,通过显示屏数据总线将读入mcu的内部ram或者外部拓展ram中的数据写入到显示屏。由于需要两步操作,spi显示屏更新存储器中的画面的速度受到限制,分辨率越高,卡顿现象越明显。

技术实现要素:

4.本实用新型针对上述现有技术中存在的问题,提出一种显示屏界面显示加速电路及系统,以解决现有技术中显示屏更新存储器中的画面的速度受限,卡顿现象明显的问题。

5.为解决上述技术问题,本实用新型是通过如下技术方案实现的:

6.根据本实用新型的第一方面,提供一种显示屏界面显示加速电路,其包括:显示屏、控制器以及存储器;其中,所述显示屏与所述控制器相连;所述控制器与所述存储器相连;所述显示屏与所述控制器之间的节点还与所述存储器相连;所述显示屏与所述存储器之间共用数据总线;

7.所述显示屏包括:第一spi接口,所述控制器包括:第一gpio接口;所述第一spi接口的片选引脚cs与所述控制器的第一gpio接口相连。

8.较佳地,所述存储器包括:第二spi接口,所述控制器包括:第三spi接口;

9.所述第一spi接口的时钟引脚clk以及所述第二spi接口的时钟引脚clk与所述第三spi接口的时钟引脚clk公用。

10.较佳地,所述第一spi接口的数据引脚mosi与所述第三spi接口的数据引脚miso相连。

11.较佳地,所述第二spi接口的数据引脚miso通过电阻串联到所述第三spi接口的数据引脚miso。

12.较佳地,所述第二spi接口的数据引脚mosi与所述第三spi接口的数据引脚mosi相连。

13.较佳地,所述控制器包括:第二gpio接口;

14.所述第二spi接口的片选引脚cs与所述第二gpio接口相连。

15.根据本实用新型的第二方面,还提供一种显示屏界面显示加速系统,其包括上述所述的显示屏界面显示加速电路。

16.相较于现有技术,本实用新型实施例具有以下至少一种优点:

17.本实用新型提供的显示屏界面显示加速电路及系统,通过显示屏与存储器公用数据总线,数据从存储器中被全部读出的同时,数据已经被全部写入了显示屏中,不再需要使用ram作为缓存,节省掉数据从ram写入到显示屏的时间,使界面更新速度更快。

18.本实用新型提供的显示屏界面显示加速电路及系统,线路减少,便于减小电路板空间。

19.本实用新型的一可选方案中,控制器只需要一组spi接口便可实现读/写flash、更新显示屏内容,对控制器的要求更低,可降低成本和扩展显示方案的可能性。

附图说明

20.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

21.图1为本实用新型一实施例的显示屏界面显示加速电路的示意图;

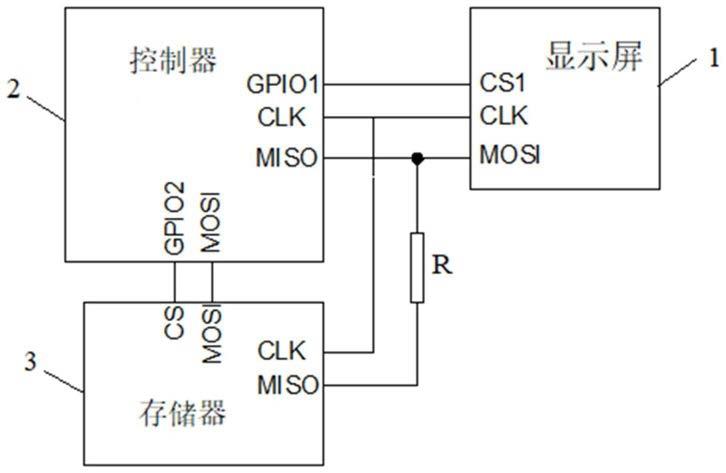

22.图2为本实用新型一较佳实施例的显示屏界面显示加速电路的电路图。

23.附图标记说明:

24.1-显示屏,

25.2-控制器,

26.3-存储器。

具体实施方式

27.下面对本实用新型的实施例作详细说明,本实施例在以本实用新型技术方案为前提下进行实施,给出了详细的实施方式和具体的操作过程,但本实用新型的保护范围不限于下述的实施例。

28.图1为本实用新型一实施例的显示屏界面显示加速电路的示意图。

29.请参考图1,本实施例中,提供一种显示屏界面显示加速电路,包括:显示屏1、控制器2以及存储器3;其中,显示屏1与控制器2相连;控制器2与存储器3相连;显示屏1与控制器2之间的节点还与存储器3相连。一较佳实施例中,显示屏1包括:第一spi接口,控制器包括:第一gpio接口gpio1。第一spi接口的片选引脚cs1与控制器的第一gpio接口gpio1相连,请参考图2。本实施例中,存储器的数据输出引脚与显示屏的数据输入引脚相连,两者共用数据总线,数据会直接从存储器进入显示屏。本实施例能够节省掉数据从ram写入到显示屏的时间,使界面更新速度更快。

30.图2为本实用新型一较佳实施例的显示屏界面显示加速电路的电路图。在该较佳实施例中,存储器3包括:第二spi接口,控制器2包括:第三spi接口,请参考图2。第一spi接口spi1的时钟引脚clk以及第二spi接口spi2的时钟引脚clk与第三spi接口spi3的时钟引脚clk公用。本实施例线路减少,便于减小电路板空间。

31.一较佳实施例中,第一spi接口的数据引脚mosi与第三spi接口的数据引脚miso相连,请参考图2。

32.一较佳实施例中,第二spi接口的数据引脚miso通过电阻r串联到第三spi接口的数据引脚miso,可以解决控制器单独操作显示屏共用总线带来的电平干扰问题,请参考图2。

33.一较佳实施例中,第二spi接口的数据引脚mosi与第三spi接口的数据引脚mosi相连,请参考图2。

34.一较佳实施例中,控制器包括:第二gpio接口gpio2;第二spi接口的片选引脚cs与第二gpio接口gpio2相连,请参考图2。控制器读/写存储器时,用硬件spi寄存器方法操作。当用控制为单独操作显示屏时,用软件模拟spi方法来进行操作。

35.本实用新型上述实施例中,控制器只需要一组spi接口便可实现读/写flash、更新显示屏内容,对控制器的要求更低,可降低成本和扩展显示方案的可能性。

36.在上述实施例基础上,控制器可以采用stm32c8t6控制器。存储器可以采用spi接口的w25q64存储器。显示屏可以采用spi接口的tft-lcd。当然,这里只是举例说明,在其他实施例中,也可以采用其他型号的控制器、存储器以及显示屏,本实用新型并不局限于上述型号。

37.基于上述实施例中的显示屏界面显示加速电路,当显示屏要显示的是存储在存储器中的界面资源时,包括:

38.用控制器的miso引脚软件模拟成mosi输出来配置好显示屏的寄存器;

39.用控制器的硬件spi配置存储器的寄存器;

40.用控制器的硬件spi把存储器中的界面资源读出。

41.上述实施例提供了一种硬件技术方案,当显示屏需要显示存储器中的界面资源时,只需要经历一步,即界面资源数据直接从存储器进入到显示屏,不再需要先将数据从存储器读入ram,再把数据从ram搬入显示屏。

42.基于上述实施例中的显示屏界面显示加速电路,当显示屏要显示的不是存储在存储器中的界面资源时,包括:

43.用控制器的miso引脚软件模拟成mosi输出来配置好显示屏的寄存器;

44.用控制器的miso引脚软件模拟成的mosi把显示内容输出到显示屏。

45.上述实施例提供了一种硬件技术方案,当显示屏需要显示的不是存储在存储器中的界面资源时,解决了显示屏和存储器公用一组数据总线后,存储器输出引脚可能会保持的高电平而对显示屏数据输入引脚的电平信号变化造成干扰的问题。应当理解的是,上述的软件部分均为现有技术,不属于本实用新型保护内容,本实用新型重点在于提供一种上述各硬件构成的电路。

46.基于相同的技术构思,在上述实施例提供的显示屏界面显示加速电路的基础上,在本实用新型另一实施例中,还提供一种显示屏界面显示加速系统,该系统包括上述任一实施例的显示屏界面显示加速电路。

47.上述实施例中显示屏界面显示加速系统,不再需要使用ram作为缓存,节省掉数据从ram写入到显示屏的时间,使界面更新速度更快,当显示屏需要显示的不是存储在存储器中的界面资源时,提供了显示屏总线和存储器公用一组数据总线后,控制器直接对显示屏更新内容的方案。控制器的数据输出引脚miso可以方便地用软件模拟成数据输入引脚,直接对显示屏自由操作,操作方便。具体软件模拟的内容均采用现有技术实现,不属于本实用

新型的保护内容。

48.此处公开的仅为本实用新型的优选实施例,本说明书选取并具体描述这些实施例,是为了更好地解释本实用新型的原理和实际应用,并不是对本实用新型的限定。任何本领域技术人员在说明书范围内所做的修改和变化,均应落在本实用新型所保护的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。