1.本发明涉及具备锁存电路的半导体装置。

背景技术:

2.在半导体装置中,逻辑电路中的锁存电路(也称作触发器电路)的软错误(soft error)成为问题。软错误是指由于宇宙射线等粒子线向锁存电路碰撞从而噪声进入而使锁存器的状态翻转的暂时性错误。

3.作为软错误耐性高的电路,例如专利文献1的图2所示的锁存电路具备4个倒相器(inverter)电路,具有双重的冗余的电路结构。各倒相器电路的pmos晶体管和nmos晶体管的栅极被输入相同的数据,但连接于不同的节点。即使可能成为软错误的噪声进入这4个节点中的某1个,也能够通过其他节点来恢复。

4.此外,专利文献2关于在大规模集成电路(lsi)中以较高的灵敏度和较短的检查时间检测电气故障的检查方法,公开了如下半导体装置。该半导体装置具备基本布线图案,该基本布线图案具有:

“コ”

字状的第1布线,具有平行的一对梳齿状导体;以及

“コ”

字状的第2布线,相对于第1布线以套匣状配置,并且具有平行的一对梳齿状导体。

5.现有技术文献

6.专利文献

7.专利文献1:日本特许第5369771号公报

8.专利文献2:日本特开2007-103598号公报

技术实现要素:

9.发明要解决的课题

10.但是,根据上述现有技术,在成为相同信号电平的冗余布线对发生了短路的情况下,有如下问题,即:虽然软错误耐性劣化,但是在检查阶段无法检测到该短路。

11.本发明提供减轻由冗余布线对的短路引起的软错误耐性的劣化的半导体装置。

12.用来解决课题的手段

13.本发明的一技术方案的半导体装置,具备:第1布线;第2布线,不与上述第1布线连接,并且为了传递与上述第1布线相同的信号电平而设置;以及其他布线,是与上述第1布线及上述第2布线不同的布线;在布线层内,上述第1布线与上述第2布线的距离大于上述第1布线与上述其他布线的距离,并且大于上述第2布线与上述其他布线的距离。

14.发明效果

15.根据本发明的半导体装置,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。

附图说明

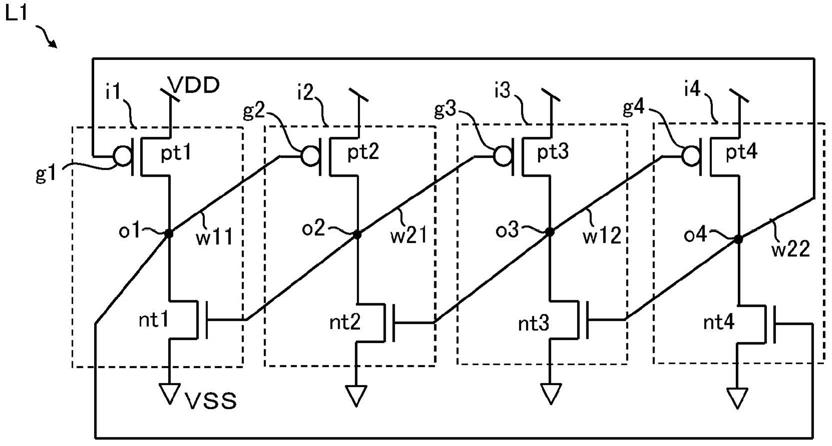

16.图1是表示在实施方式1的半导体装置中形成的电路例的图。

17.图2是表示布线层内的布线布局的第1例的图。

18.图3是表示布线层内的布线布局的第2例的图。

19.图4是表示布线层内的布线布局的第3例的图。

20.图5是表示布线层内的布线布局的第4例的图。

21.图6是表示布线层内的布线布局的第5例的图。

22.图7是表示布线层内的布线布局的第6例的图。

23.图8是表示布线层内的布线布局的第7例的图。

24.图9是表示布线层内的布线布局的第8例的图。

25.图10是表示布线层间的布线布局的第1例的图。

26.图11a是表示布线层间的布线布局的第2例的图。

27.图11b是表示布线层间的布线布局的第2例的变形例的图。

28.图12是表示在实施方式1的半导体装置中形成的另一电路例的图。

29.图13是表示图12中的c要素的一例的电路图。

30.图14是表示比较例的锁存电路的短路例子的说明图。

具体实施方式

31.(作为本发明的基础的认识)

32.本发明的发明人关于在“背景技术”栏中记载的软错误耐性高的电路,发现了会发生以下问题。对于该问题,使用图14具体地进行说明。

33.图14是表示比较例的锁存电路的短路例的说明图。图14的(a)所示的锁存电路具备4个pmos晶体管和4个nmos晶体管。串联连接的pmos晶体管和nmos晶体管的对构成倒相器电路。

34.通常的锁存电路具备两个倒相器电路,相对于此,图14的(a)具备4个倒相器电路。图14的(a)的锁存电路通过双重的冗余结构提高了软错误耐性。

35.在图14的(a)中,4个倒相器电路被4个布线w1~w4连接。布线w1和布线w3是冗余布线对,是成为相同的信号电平但独立的布线。同样,布线w2和布线w4是冗余布线对,是成为相同的信号电平但独立的布线。

36.在该图中,将冗余布线对的布线w1及布线w3用细线描绘,示出了是低电平的例子。此外,将其他冗余布线对的布线w2及布线w4用粗线描绘,示出了是高电平的例子。

37.各倒相器电路的pmos晶体管和nmos晶体管的栅极被输入相同的信号电平,但连接于不同的布线。即,在pmos晶体管的栅极上连接冗余布线对的一方。在nmos晶体管的栅极上连接冗余布线对的另一方。这样,由4个倒相器电路构成了环路,所以成为即使1个倒相器电路的输出翻转也能由其他3个倒相器电路保持正确的值的构造。这样,该图的锁存电路提高了软错误耐性。

38.图14的(b)如虚线框sh1所示,示出了布线w1和布线w3短路了的情况。此外,图14的(c)如虚线框sh2所示,示出了布线w2和布线w4短路了的情况。这样的短路在包含锁存电路的半导体装置的制造工艺中例如可能由于金属粒子等导电性异物的混入而发生。

39.无论是在图14的(b)中还是在图14的(c)中,冗余布线对都发生了短路。即,在虚线框sh1及虚线框sh2中短路了的布线对虽然是没有被相互连接的独立的布线,但在锁存电路

的动作中始终为相同的信号电平。因此,无论是在图14的(b)中还是在图14的(c)中,锁存电路都正常地动作而不表现出异常。但是,由于因短路而失去了布线对的冗余性,所以有软错误耐性劣化的问题。

40.进而,虚线框sh1及虚线框sh2的短路在半导体装置的制造工序的检查阶段中无法检测到。即,有无法检测到由虚线框sh1及虚线框sh2的短路引起的软错误的耐性劣化的问题。

41.因此,本发明提供减轻由冗余布线对的短路引起的软错误耐性的劣化的半导体装置。

42.为了解决这样的问题,本发明的一技术方案的半导体装置,具备:第1布线;第2布线,不与上述第1布线连接,并且为了传递与上述第1布线相同的信号电平而冗余地设置;以及其他布线,是与上述第1布线及上述第2布线不同的布线;在布线层内,上述第1布线与上述第2布线的距离大于上述第1布线与上述其他布线的距离,并且大于上述第2布线与上述其他布线的距离。

43.由此,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。这是因为,在混入了与布线间距离相同程度的大小的异物的情况下,相比于第1布线与第2布线的短路,更容易发生第1布线或第2布线与其他布线的短路。结果,抑制了不可检测的短路的发生,换言之,抑制了冗余布线对的短路的发生。

44.在由于异物混入从而第1布线或第2布线与其他布线短路了的情况下,引起异常动作的概率较高,所以能够在工厂出厂前的检查阶段中检测到短路。

45.这样,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。

46.以下,参照附图对实施方式具体地进行说明。

47.另外,以下说明的实施方式都表示总括性或具体性的例子。以下的实施方式中表示的数值、形状、材料、构成要素、构成要素的配置位置及连接形态、步骤、步骤的顺序等是一例,并不意欲限定本发明。此外,关于以下的实施方式的构成要素中的、在表示本发明的一技术方案的实现形态的独立权利要求中没有记载的构成要素,作为任意的构成要素进行说明。本发明的实现形态并不限定于现行的独立权利要求,也能够通过其他独立权利要求来表现。

48.(实施方式1)

49.[1半导体装置的电路例]

[0050]

图1是表示在实施方式1的半导体装置中形成的电路例的图。

[0051]

该图的电路例具备具有第1~第4翻转电路i1~i4的锁存电路l1。第1~第4翻转电路i1~i4具备4个第1型mos晶体管pt1~pt4和4个第2型mos晶体管nt1~nt4。该锁存电路l1作为具有冗余布线对的电路的一例而表示了所谓的dice(dual interlocked storage cell)锁存电路。

[0052]

第1翻转电路i1具有第1型mos晶体管pt1、第2型mos晶体管nt1、以及与第1型mos晶体管pt1的漏极及第2型mos晶体管nt1的漏极连接的输出节点o1。

[0053]

第2翻转电路i2具有第1型mos晶体管pt2、第2型mos晶体管nt2、以及与第1型mos晶体管pt2的漏极及第2型mos晶体管nt2的漏极连接的输出节点o2。

[0054]

第3翻转电路i3具有第1型mos晶体管pt3、第2型mos晶体管nt3、以及与第1型mos晶

体管pt3的漏极及第2型mos晶体管nt3的漏极连接的输出节点o3。

[0055]

第4翻转电路i4具有第1型mos晶体管pt4、第2型mos晶体管nt4、以及与第1型mos晶体管pt4的漏极及第2型mos晶体管nt4的漏极连接的输出节点o4。

[0056]

第1~第4翻转电路i1~i4的第1型mos晶体管各自的源极与电位vdd的电源线连接,第2型mos晶体管各自的源极与电位vss的gnd(接地)线连接。

[0057]

另外,第1型是指p型及n型中的一个导电型。第2型是指p型及n型中的另一个导电型。在图1的例子中,第1型是p型,第2型是n型。以下,有时将第1型表述为p、将第2型表述为n。此外,有时将第1型mos晶体管表述为pmos晶体管、将第2型mos晶体管表述为nmos晶体管。

[0058]

第1~第4翻转电路被用4个布线w11、w12、w21、w22连接。布线w11和布线w12是冗余布线对,是成为相同信号电平但不相互连接的独立的布线。同样,布线w21和布线w22是冗余布线对,是成为相同信号电平但不相互连接的独立的布线。另外,构成冗余布线对的各布线是指不仅包括布线层内的金属布线部分、还包括布线层间的通孔接触部、晶体管的栅极、源极及漏极的各电极、以及电路元件的各端子电极等的一系列导电体。以下,有时将通孔接触部简单记作通孔。

[0059]

布线w11将第1翻转电路i1的输出节点o1与第2翻转电路i2的第1型mos晶体管pt2的栅极g2以及第4翻转电路i4的第2型mos晶体管nt4的栅极连接。

[0060]

布线w21将第2翻转电路i2的输出节点o2与第3翻转电路i3的第1型mos晶体管pt3的栅极g3以及第1翻转电路i1的第2型mos晶体管nt1的栅极连接。

[0061]

布线w12将第3翻转电路i3的输出节点o3与第4翻转电路i4的第1型mos晶体管pt4的栅极g4以及第2翻转电路i2的第2型mos晶体管nt2的栅极连接。

[0062]

布线w22将第4翻转电路i4的输出节点o4与第1翻转电路i1的第1型mos晶体管pt1的栅极g1以及第3翻转电路i3的第2型mos晶体管nt3的栅极连接。

[0063]

通过这样的连接,由4个倒相器电路构成环路。因此,成为即使1个倒相器电路的输出由于软错误而翻转、也能由其他3个倒相器电路保持正确的值的构造。这样,该图的锁存电路l1提高了软错误耐性。

[0064]

图1所示的锁存电路l1构成在半导体装置内的半导体基板上形成的半导体电路的一部分。在半导体基板上形成的半导体电路包括多个p型杂质区域、多个n型杂质区域、多个布线层、将布线层间相连的多个接触部等。

[0065]

作为图1的锁存电路l1的构成要素的冗余布线对形成于1个以上的布线层。在本实施方式中,以使得在半导体装置的制造工艺中不易因异物的混入等而在冗余布线对中发生短路的方式配置了冗余布线对。

[0066]

接着,对1个布线层内的冗余布线对的布线布局进行说明。

[0067]

[2.1布线层内的布线布局的第1例]

[0068]

图2是表示半导体装置的布线层内的布线布局的第1例的图。该图是将形成有图1的锁存电路l1的半导体基板进行平面观察而得到的图。此外,图2是将形成在1个布线层内的多个布线中的一部分示意地放大了的图。在图2中表示4个布线11、12、21、22的布局。

[0069]

布线11和布线12表示冗余布线对。具体而言,布线12是不与布线11连接、并且为了传递与布线11相同的信号电平而冗余地设置的布线。布线11和布线12例如与图1的布线w11及w12对应。

[0070]

布线21是与布线11及布线12不同的其他布线。布线22也是与布线11及布线12不同的布线。

[0071]

图中的a表示布线11与布线12的距离。b1表示布线11与布线21的距离。b2表示布线12与布线21的距离。b3表示布线11与布线22的距离。b4表示布线12与布线22的距离。另外,这些距离都是布线间的最小距离。

[0072]

这些布线的布局满足以下的关系。

[0073]

布线11与布线12的距离a比布线11与布线21的距离b1大。

[0074]

布线11与布线12的距离a比布线12与布线21的距离b2大。

[0075]

布线11与布线12的距离a比布线11与布线22的距离b3大。

[0076]

布线11与布线12的距离a比布线12与布线22的距离b4大。

[0077]

这是因为,通过满足该关系,在混入了异物的情况下,相比于作为冗余布线对的布线11与布线12的短路,布线11或布线12与其他布线(21、22)的短路更容易发生。结果,抑制了不能检测到的短路的发生,换言之,抑制了冗余布线对的短路的发生。

[0078]

由于布线11或布线12与其他布线(21、22)的短路更容易发生,所以能够检测到短路。因而,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。

[0079]

在图2中,为了满足上述的关系,布线22包括从与布线22的主体部分连接的通孔v2延伸的延伸部分e1。延伸部分e1的端部可以是在布线层内没有被连接的开放端。

[0080]

另外,图2的布线21和布线22例如可以是与图1的布线w21及w22对应的布线。或者,布线21及布线22分别既可以是电源线也可以是接地线。

[0081]

[2.2布线层内的布线布局的第2例]

[0082]

图3是表示布线层内的布线布局的第2例的图。该图是将形成在1个布线层内的多个布线中的一部分示意地放大了的图。在图3中表示布线11、12、21的布局。图中的v1表示将布线21与其他布线层的布线连接的通孔接触部。e1是指布线21的延伸部分。

[0083]

布线11和布线12表示冗余布线对。布线21是与布线11及布线12不同的其他布线。冗余布线对的布线11和布线12具有在布线层内并行配置的并行区间,遍及并行区间地夹着其他布线21。

[0084]

图3的布线布局例与图2同样地满足以下的关系。

[0085]

布线11与布线12的距离a比布线11与布线21的距离b1大。

[0086]

布线11与布线12的距离a比布线12与布线21的距离b2大。

[0087]

在图3中,冗余布线对的布线11和布线12配置为,遍及并行地配置有布线11和布线12的并行区间而夹着其他布线21。为此,布线21具有延伸部分e1。即,布线21包括从与布线21的主体部分连接的通孔v1延伸的延伸部分e1。该延伸部分e1在上述的并行区间内配置在布线11与布线12之间。此外,延伸部分e1的端部可以是在布线层内没有被连接的开放端。

[0088]

根据图3的布线布局例,在混入了异物的情况下,在作为冗余布线对的布线11与布线12短路之前,布线11或布线12与其他布线21容易短路。换言之,冗余布线对的短路置换为能够检测到的其他短路的概率较高。由此,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。

[0089]

另外,图3的布线21例如可以是与图1的布线w21和w22的一方对应的布线,也可以是电源线,也可以是接地线。

[0090]

[2.3布线层内的布线布局的第3例]

[0091]

图4是表示布线层内的布线布局的第3例的图。该图是将形成在1个布线层内的多个布线中的一部分示意地放大了的图。在图4中表示布线11、12、21的布局。图中的v1表示将布线21与其他布线层的布线连接的通孔接触部。

[0092]

布线11和布线12表示冗余布线对。布线21是与布线11及布线12不同的其他布线。冗余布线对的布线11和布线12具有在布线层内并行配置的并行区间,遍及并行区间地夹着其他布线21。

[0093]

图4的布线布局例也与图2同样地满足以下的关系。

[0094]

布线11与布线12的距离a比布线11与布线21的距离b1大。

[0095]

布线11与布线12的距离a比布线12与布线21的距离b2大。

[0096]

在图4中,冗余布线对的布线11和布线12配置为,遍及将布线11和布线12并行配置的并行区间而夹着其他布线21。为此,布线21具有延伸部分e1~e3。即,布线21包括从与布线21的主体部分连接的通孔v1延伸的延伸部分e1~e3。延伸部分e1~e3是连续的1条布线,在布线层内以绕过布线11的端部的方式配置。延伸部分e3的一部分以遍及并行区间地被布线11和布线12夹着的方式配置。此外,延伸部分e3的端部可以是在布线层内没有被连接的开放端。此外,图4的距离b1及b2分别可以是半导体装置的设计规则上的布线间的最小间隔。此外,布线11与布线12的距离a比设计规则上的布线间的最小间隔大。

[0097]

根据图4的布线布局例,在混入了异物的情况下,在作为冗余布线对的布线11和布线12短路之前,布线11或布线12与其他布线21容易短路。换言之,冗余布线对的短路置换为能够检测到的其他短路的概率较高。由此,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。

[0098]

另外,图4的布线21例如可以是与图1的布线w21和w22的一方对应的布线,也可以是电源线,也可以是接地线。

[0099]

[2.4布线层内的布线布局的第4例]

[0100]

图5是表示布线层内的布线布局的第4例的图。该图是将形成在1个布线层内的多个布线中的一部分示意地放大了的图。在图5中表示布线11、12、21、22的布局。图中的v1表示将布线21与其他布线层的布线连接的通孔接触部。

[0101]

布线11和布线12表示冗余布线对。此外,布线21和布线22表示冗余布线对。将布线11和布线12的布线对称作第1冗余对,将布线21和布线22的布线对称作第2冗余对。在图5中,4个布线11、12、21、22按照第1冗余对的一方的布线11、第2冗余对的一方的布线21、第1冗余对的另一方的布线12、第2冗余对的另一方的布线22的顺序排列配置。即,成为将两个冗余对的布线交替配置、相同的信号电平的布线不相邻的配置。

[0102]

图5的布线布局例也与图2同样地满足以下的关系。

[0103]

布线11与布线12的距离a比布线11与布线21的距离b1大。

[0104]

布线11与布线12的距离a比布线12与布线21的距离b2大。

[0105]

图5的布线11、12、21、22分别可以是布线的主体部分,也可以是延伸部分。

[0106]

根据图5的布线布局例,在混入了异物的情况下,在作为冗余布线对的布线11和布线12短路之前,布线11或布线12与其他布线21或布线22容易短路。换言之,冗余布线对的短路置换为能够检测到的其他短路的概率较高。由此,能够减轻由冗余布线对的短路引起的

软错误耐性的劣化。

[0107]

另外,可以是,图5的布线11和布线12是与图1的布线w11和w12对应的布线,布线21和布线22是与图1的布线w21和w22对应的布线。

[0108]

[2.5布线层内的布线布局的第5例]

[0109]

图6是表示布线层内的布线布局的第5例的图。该图是将形成在1个布线层内的多个布线中的一部分示意地放大了的图。在图6中表示布线11、12、21的布局。图中的v1、v2表示将布线21与其他布线层的布线连接的通孔接触部。e1是指布线21的延伸部分。

[0110]

布线11和布线12表示冗余布线对。布线21是与布线11及布线12不同的其他布线。冗余布线对的布线11和布线12具有在布线层内并行配置的并行区间,遍及该并行区间地夹着其他布线21。

[0111]

图6的布线布局例与图2同样地满足以下的关系。

[0112]

布线11与布线12的距离a比布线11与布线21的距离b1大。

[0113]

布线11与布线12的距离a比布线12与布线21的距离b2大。

[0114]

在图6中,冗余布线对的布线11和布线12配置为,遍及将布线11和布线12并行配置的并行区间而夹着其他布线21。为此,布线21具有延伸部分e1。即,布线21包括从布线21的主体部分延伸的延伸部分e1。该延伸部分e1在上述的并行区间内配置在布线11与布线12之间。此外,延伸部分e1的端部可以是在布线层内没有被连接的开放端。

[0115]

根据图6的布线布局例,在混入了异物的情况下,与作为冗余布线对的布线11和布线12的短路相比,布线11或布线12与其他布线21的短路更容易发生。换言之,冗余布线对的短路置换为能够检测到的其他短路的概率较高。由此,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。

[0116]

另外,图6的布线21例如可以是与图1的布线w21和w22的一方对应的布线,也可以是电源线,也可以是接地线。

[0117]

[2.6布线层内的布线布局的第6例]

[0118]

图7是表示布线层内的布线布局的第6例的图。该图与图6相比,布线21的主体部分属于其他布线层这一点、以及延伸部分e1从布线21的主体部分经由通孔v3延伸这一点不同。以下,以不同点为中心进行说明。

[0119]

布线21的主体部分如该图的虚线所示,属于与布线11及布线12所属的布线层不同的其他布线层。

[0120]

延伸部分e1从属于其他布线层的布线21的主体部分经由通孔v3延伸。由此,冗余布线对的布线11和布线12具有在布线层内并行配置的并行区间,遍及该并行区间地夹着其他布线21的延伸部分e1。

[0121]

根据图7的布线布局例,与图6同样,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。

[0122]

[2.7布线层内的布线布局的第7例]

[0123]

图8是表示布线层内的布线布局的第7例的图。该图与图3相比不同点在于追加了电源布线。以下,以不同点为中心进行说明。

[0124]

布线21是电源布线,具有从电源布线的主体部分延伸的延伸部分e1、e2。电源布线例如可以是在布线层内以将锁存电路l1的全部或一部分包围的方式配置的布线,也可以是

形成在其他布线层中的屏蔽布线。

[0125]

根据图8的布线布局例,与图3同样,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。

[0126]

[2.8布线层内的布线布局的第8例]

[0127]

图9是表示布线层内的布线布局的第8例的图。该图是将形成在1个布线层内的多个布线中的一部分示意地放大了的图。在图9中表示布线11、12、21、22的布局。图中的v1表示将布线21与其他布线层的布线连接的通孔接触部。v2表示将布线22与其他布线层的布线连接的通孔接触部。e1表示布线21的延伸部分。e2表示布线22的延伸部分。

[0128]

布线11和布线12表示冗余布线对。布线21是与布线11及布线12不同的其他布线。布线22是与布线11及布线12不同的再其他布线。该布线21和布线22不是冗余布线对。冗余布线对的布线11和布线12具有在布线层内并行配置的并行区间,遍及该并行区间的大部分而夹着其他布线21和再其他布线22。其他布线21和再其他布线22隔开间隔d1配置在相同的直线上。

[0129]

图9的布线布局例与图2同样地满足以下的关系。

[0130]

布线11与布线12的距离a比布线11与布线21或布线22的距离b1大。

[0131]

布线11与布线12的距离a比布线12与布线21或布线22的距离b2大。

[0132]

进而,在图9中,布线11与布线12的距离a比布线21与布线22的距离d1大。换言之,布线11和布线12相邻而并行的区间(即不夹着其他布线的区间)的距离d1比布线11与布线12的距离a小。

[0133]

在图9中,冗余布线对的布线11和布线12配置为,遍及将布线11和布线12并行配置的并行区间的大部分而夹着布线21或布线22。为此,布线21具有延伸部分e1,布线22具有延伸部分e2。即,延伸部分e1、e2的端部可以是在布线层内没有被连接的开放端。

[0134]

根据图9的布线布局例,与图3同样地能够减轻由冗余布线对的短路引起的软错误耐性的劣化。

[0135]

另外,图9的布线21例如可以是电源线,也可以是接地线。布线22也例如可以是电源线,也可以是接地线。

[0136]

在图2~图9中表示了1个布线层内的冗余布线对的配置布局例。以下,对不同布线层中的冗余布线对的配置布局进行说明。

[0137]

[3.1布线层间的布线布局的第1例]

[0138]

图10是表示布线层间的布线布局的第1例的图。图10的(a)表示将形成有锁存电路l1的半导体基板进行平面观察而得到的布线布局。图10的(b)表示图10的(a)的a-a线的截面,包括3个布线层m1~m3。该图是将形成在布线层m1~m3中的布线中的、与冗余布线对关联的部分示意地放大了的图。在图10中表示冗余布线对的布线11和布线12。

[0139]

如图10所示,冗余布线对的布线11和布线12属于不同的布线层。即,布线11属于布线层m3,布线12属于布线层m2和m1,包含通孔接触部。

[0140]

不同布线层中的冗余布线对以满足以下关系的方式配置。即,在布线11和布线12的布线层不同的情况下,布线11与布线12的距离a比相邻的布线层间的层间距离c大。在该图中,作为布线11与布线12的距离,记载了a1、a2、a3这3个,但布线11与布线12的距离a是最小的a1或a3。布线11和布线12以满足a》c的方式配置。

[0141]

更详细而言,在图10中,在半导体装置的平面视图中,布线11和布线12具有重叠的部分,并且交叉。布线12具有与重叠部分对应的第1部分布线12b、与第1部分布线12b的一端连接的第2部分布线12a、以及与第1部分布线12b的另一端连接的第3部分布线12c。第1部分布线12b属于布线层m1。第2部分布线12a及第3部分布线12c属于与布线层m1不同的布线层m2,经由通孔接触部v1、v2而与第1部分布线12b连接。布线11属于距布线层m1比布线层m2更远的布线层m3。通过该配置布局,能够容易地满足上述的关系(即a》c)。在图10中,配置为,重叠的部分中的布线11与布线12的距离a2满足层间距离c的2倍以上。

[0142]

根据图10的配置布局,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。这是因为,在混入了与层间距离c相同程度的大小的异物的情况下,不易发生布线11和布线12的短路。由此,抑制了冗余布线对的短路的发生。

[0143]

另外,图10的布线层m1~m3只要是该配置顺序,也可以是多个布线层中的任意的3个。但是,层间距离c并不限于图10的布线层m2与布线层m3之间的距离,是相邻的两个布线层间的最小距离。

[0144]

[3.2布线层间的布线布局的第2例]

[0145]

图11a是表示布线层间的布线布局的第2例的图。图11a的(a)表示将形成有锁存电路l1的半导体基板进行平面观察而得到的布线布局。图11a的(b)表示图11a的(a)的b-b线的截面,包括两个布线层m2、m3。该图是将形成在布线层m2、m3中的布线中的、与冗余布线对关联的部分示意地放大了的图。在图11a中,表示冗余布线对的布线11和布线12。

[0146]

在图11a的(a)的平面图中,布线12配置为,绕过布线11的端部,以使布线11和布线12不重叠。

[0147]

通过该配置布局,能够容易地满足上述的关系(即a》c)。

[0148]

根据图11a的配置布局,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。这是因为,在混入了与层间距离c相同程度的大小的异物的情况下,不易发生布线11和布线12的短路。由此,抑制了冗余布线对的短路的发生。

[0149]

[3.3布线层间的布线布局的第2例]

[0150]

图11b是表示布线层间的布线布局的第2例的变形例的图。该图与图11a相比不同点在于,具备布线31。以下,以不同点为中心进行说明。布线31配置在布线11或布线12的附近,包括通孔接触部v1和延伸部分e1。通孔接触部v1将其他布线层m4的布线31部分与布线层m3的布线31连接。延伸部分e1从通孔接触部v1延伸。此外,也可以设置以下这样的延伸规则。即,从通孔v1到延伸部分e1的端部为止的长度e1比半导体装置的设计规则中的布线的最小尺寸大。另外,该延伸规则也可以对其他图的延伸部分应用。

[0151]

在图11b中,布线31的延伸部分e1配置为,与冗余布线对的一方的布线在相同的布线层内相邻,与另一方的布线在不同的布线层间相邻。此外,距离a比布线11与布线31的距离大,并且比布线12与布线31的距离大。

[0152]

根据布线设计cad,如果想要没有布线31地实现图11a,则存在导致在冗余对之间必须仅利用最小限度的布线这样的限定的情况,存在布局困难的情况。如果在布线11或布线12附近适当配置布线31,则能够容易地设计冗余布线对的配置。结果,能够容易地实现图11b那样的冗余布线对的布局。

[0153]

[4半导体装置的其他电路例]

[0154]

接着,对具有冗余布线对的其他电路例进行说明。

[0155]

图12是表示在实施方式1的半导体装置中形成的其他电路例的图。该图的半导体装置,作为具有软错误耐性的电路,表示biser(built in soft error resilience)型触发器电路的结构例。

[0156]

该图的触发器电路具备延迟电路dl、倒相器iv、主锁存器ml0、ml1、主c要素cm、副锁存器sl0、sl1、副c要素cs、主弱保持电路wm和副弱保持电路ws,为双重主副构造。图12中的冗余布线对是与副锁存器sl0的输出qn连接的布线、以及与副锁存器sl1的输出qn连接的布线。

[0157]

延迟电路dl将向主锁存器ml0输入的输入数据d延迟时间τ而向主锁存器ml1输出。

[0158]

倒相器iv输出将时钟信号cp翻转后的时钟信号cn。

[0159]

主锁存器ml0与时钟信号cp及时钟信号cn同步,将输入数据d锁存,将数据qp输出。输出数据qp是与数据d相同的逻辑电平的非翻转输出数据。

[0160]

主锁存器ml1与时钟信号cp及时钟信号cn同步,将延迟后的输入数据d锁存,将数据qp输出。输出数据qp是与数据d相同的逻辑电平的非翻转输出数据。

[0161]

主c要素cm是2输入1输出的翻转电路,当2输入为确定的相同的逻辑电平时输出该逻辑电平的翻转了的电平,当2输入不为确定的相同的逻辑电平时成为高阻抗。

[0162]

主弱保持电路wm是弱保持器(weak keeper)电路,保持主c要素cm输出的逻辑电平,当主c要素cm的输出为高阻抗时,输出在即将成为高阻抗之前所保持的逻辑电平。

[0163]

副锁存器sl0与时钟信号cp及时钟信号cn同步,将输入数据d锁存,将数据qn输出。输出数据qn是将数据d翻转了的逻辑电平的数据。

[0164]

副锁存器sl1与时钟信号cp及时钟信号cn同步,将输入数据d锁存,将数据qn输出。输出数据qn是将数据d翻转了的数据。

[0165]

副c要素cs是2输入1输出的翻转电路,当2输入为确定的相同的逻辑电平时输出该逻辑电平的翻转了的逻辑电平,当2输入不为确定的相同的逻辑电平时成为高阻抗。在图13中表示副c要素cs的电路例。该图的副c要素cs由两个pmos晶体管和两个nmos晶体管构成。两个pmos晶体管和两个nmos晶体管被串联连接。另外,主c要素cm也可以与图13相同。

[0166]

副弱保持电路ws是弱保持器(weak keeper)电路,保持与副c要素cs输出的逻辑电平相同的逻辑电平,当副c要素cs的输出为高阻抗时输出在即将成为高阻抗之前所保持的逻辑电平。

[0167]

在这样的触发器电路中,假设在2组主副锁存器中的一方因软错误而翻转了的情况下,主c要素cm或副c要素cs的输出成为高阻抗,但能够通过主弱保持电路wm或副弱保持电路ws所保持的逻辑电平而保持正确的数据。

[0168]

图12的触发器电路中的冗余布线对包括:将副锁存器sl0的输出端子与副c要素cs的两个输入端子中的一个连接的布线、以及将副锁存器sl1的输出端子与副c要素cs的两个输入端子中的另一个连接的布线。换言之,副锁存器sl0的输出布线及副锁存器sl1的输出布线是冗余布线对。

[0169]

该布线对满足在图2~图11b中说明的配置布局的关系。由此,能够减轻图12的触发器电路内的由冗余布线对的短路引起的软错误耐性的劣化。

[0170]

另外,图12中的主锁存器ml0的输出布线及主锁存器ml1的输出布线也可以进行与

冗余布线对相同的处理。即,也可以满足在图2~图11b中说明的配置布局的关系。

[0171]

主锁存器ml1的输入数据d比主锁存器ml0的输入数据d延迟了时间τ。由此,主锁存器ml1的输出数据qp比主锁存器ml0的输出数据qp延迟了时间τ。在本说明书中,定义为“冗余布线对是成为相同的信号电平但不相互连接的独立的布线”。主锁存器ml0的输出布线及主锁存器ml1的输出布线不满足该定义。但是,主锁存器ml0的输出布线及主锁存器ml1的输出布线可能发生图14所示的布线短路的问题,此外,除了延迟时间τ以外大致符合冗余布线对的定义。因此,主锁存器ml0的输出布线及主锁存器ml1的输出布线通过满足在图2~图11b中说明的配置布局的关系,能够减轻软错误耐性的劣化。

[0172]

另外,在实施方式中,作为冗余布线对,表示了双重化的例子,但也可以将三重以上的多重化的多个布线中的两个布线的组合分别看作布线对。该情况下,被看作布线对的两个布线满足在图2~图11b中说明的配置布局的关系即可。

[0173]

如以上说明的那样,实施方式的半导体装置,具备:第1布线11;第2布线12,不与第1布线11连接,并且为了传递与第1布线11相同的信号电平而设置;以及其他布线,是与第1布线11及第2布线12不同的布线;在布线层内,第1布线11与第2布线12的距离a比第1布线11与其他布线的距离大,并且比第2布线12与其他布线的距离大。

[0174]

由此,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。这是因为,在混入了与布线间距离相同程度的大小的异物的情况下,相比于第1布线与第2布线的短路,更容易发生第1布线或第2布线与其他布线的短路。结果,抑制了无法检测到的短路的发生,换言之,抑制了冗余布线对的短路的发生。

[0175]

这里,可以是,第1布线11和第2布线12具有在布线层内并行配置的并行区间,在并行区间中夹着其他布线。

[0176]

这里,可以是,其他布线包含在布线层内从该其他布线的主体部分延伸的延伸部分e1,延伸部分e1在布线层内的并行区间内夹在第1布线11与第2布线12之间。

[0177]

这里,可以是,其他布线包含从与该其他布线的主体部分连接的通孔延伸的延伸部分e1,延伸部分e1在布线层内的并行区间内夹在第1布线11与第2布线12之间。

[0178]

这里,可以是,其他布线具有在布线层内从该其他布线的主体部分分支而延伸的延伸部分e1,延伸部分e1在布线层内的并行区间内夹在第1布线11与第2布线12之间。

[0179]

这里,可以是,延伸部分e1的端部是在布线层内没有被连接的开放端。

[0180]

这里,可以是,延伸部分e1~e3在布线层内绕过第1布线11的端部,进而配置在并行区间内。

[0181]

这里,可以是,半导体装置还具备:第3布线;以及第4布线,不与第1布线11连接,并且为了传递与第3布线相同的信号电平而设置;其他布线是第3布线。

[0182]

这里,可以是,第1布线11至第4布线的一部分在布线层内以第1布线11、第3布线、第2布线12、第4布线的顺序排列。

[0183]

由此,以第1冗余对的一方的布线、第2冗余对的一方的布线、第1冗余对的另一方的布线、第2冗余对的另一方的布线的顺序排列,所以能够防止或减轻冗余对的短路。

[0184]

这里,可以是,通孔将延伸部分和与上述的布线层不同的布线层中的其他布线21、22的主体部分连接。

[0185]

这里,可以是,延伸部分的长度比半导体装置的设计规则的最小尺寸大。

[0186]

这里,可以是,第1布线11和第2布线12包括在布线层内以夹着其他布线21、22和再其他布线的方式并行配置的区间,区间内的其他布线21、22与再其他布线的距离d1比第1布线11与第2布线12的距离小。

[0187]

这里,第1布线11及第2布线12可以构成dice(dual interlocked storage cell)锁存电路。

[0188]

这里,第1布线11及第2布线12可以构成biser(built in soft error resiliency)触发器电路。

[0189]

此外,可以是,实施方式的半导体装置具备:多个布线层;第1布线11;以及第2布线12,不与第1布线11连接,并且为了传递与第1布线11相同的信号电平而设置;第1布线11和第2布线12属于不同的布线层;第1布线11与第2布线12的距离a1比相邻的布线层的层间距离c大。

[0190]

由此,能够减轻由冗余布线对的短路引起的软错误耐性的劣化。这是因为,在混入了与布线间的距离相同程度的大小的异物的情况下,不易发生第1布线与第2布线的短路。换言之,抑制了冗余布线对的短路的发生。

[0191]

这里,可以是,在半导体装置的平面视图中第1布线11和第2布线12具有重叠的部分,重叠的部分的第1布线11与第2布线12的距离为层间距离c的2倍以上。

[0192]

这里,可以是,在半导体装置的平面视图中第1布线11和第2布线12在重叠的部分交叉;第2布线12具有:第1部分布线12b,与重叠的部分对应;第2部分布线12a,与第1部分布线12b的一端连接;以及第3部分布线12c,与第1部分布线12b的另一端连接;第1部分布线12b属于第1布线层m1;第2部分布线12a及第3部分布线12c属于与第1布线层m1不同的第2布线层m2,经由通孔接触部v1、v2而与第1部分布线12b连接;第1布线11属于距第1布线层m1比第2布线层m2更远的第3布线层m3。

[0193]

这里,可以是,第2布线12以将第1布线11的端部绕过的方式配置,以使得在半导体集成电路的平面视图中第1布线11和第2布线12不重叠。

[0194]

这里,可以是,半导体装置还具备与第1布线11及第2布线12的至少一方在布线层间或布线层内对置的第3布线31;第3布线31具有从通孔接触部v1延伸的延伸部分e1。

[0195]

这里,可以是,延伸部分e1的长度比半导体装置的设计规则的最小尺寸大。

[0196]

以上,基于实施方式对一个或多个技术方案的半导体装置进行了说明,但本发明并不限定于该实施方式。只要不脱离本发明的主旨,对本实施方式施以了本领域技术人员想到的各种变形后的形态、或将不同实施方式的构成要素组合而构建的形态也可以也包含在一个或多个技术方案的范围内。

[0197]

产业上的可利用性

[0198]

本发明能够用于具备锁存电路或触发器电路的半导体装置。

[0199]

标号说明

[0200]

11、12、21、22 布线

[0201]

e1~e3 延伸部分

[0202]

g1~g4 栅极

[0203]

i1 第1翻转电路

[0204]

i2 第2翻转电路

[0205]

i3 第3翻转电路

[0206]

i4 第4翻转电路

[0207]

nt1~nt4 nmos晶体管

[0208]

o1~o4 输出节点

[0209]

pt1~pt4 pmos晶体管

[0210]

v1~v3 通孔

[0211]

w11、w12、w21、w22 布线

[0212]

cm 主c元件

[0213]

cs 副c元件

[0214]

l1 锁存电路

[0215]

m1~m3 布线层

[0216]

ml0、ml1 主锁存器

[0217]

sl0、sl1 副锁存器

[0218]

wm 主弱保持电路

[0219]

ws 副弱保持电路

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。