1.本发明涉及磁检测装置以及磁检测信号放大用半导体集成电路,特别涉及有效用于磁检测装置中的交流磁场输入的消除技术。

背景技术:

2.近年来,在各种领域使用检测有无磁和磁强度的磁检测传感器。例如,存在如下的磁检测装置:为了检测致动器的工作状态,在致动器的可动部件设置磁铁,检测该磁铁的磁并进行放大。若该磁检测装置配设在交流电源装置或交流输电线等附近,则有可能在磁检测传感器输入作为噪声的交流磁场而引起误检测。

3.目前,作为去除磁检测装置中的噪声的发明,例如有专利文献1~3所记载的发明。

4.现有技术文献

5.专利文献

6.专利文献1:日本特开2002-296332号公报

7.专利文献2:日本特开2014-16229号公报

8.专利文献3:日本特开2015-152505号公报

技术实现要素:

9.发明所要解决的课题

10.专利文献1记载的磁检测装置提取由传感器的输出信号所感应的噪声成分,对传感器的输出信号加上或者减去该提取出的噪声成分从而抵消并去除输出信号中包含的噪声成分,并且在传感器待机中进行对传感器输出信号加上或减去的噪声成分的电平调整。但是,该发明的磁检测装置存在电路复杂且占有面积大的课题。

11.专利文献2记载的磁检测装置在经由第一电容器取出从磁传感器输出的信号的高频成分并进行放大的放大电路中设置有噪声消除电路,该噪声消除电路设置与第一电容器接近并以大致相同的姿势表面安装的第二电容器,基于从第二电容器得到的信号,将在第一电容器中产生的噪声相当量从放大信号中去除。但是,该发明的磁检测装置由于使用陶瓷电容器这样的部件,因此存在不适于形成为半导体集成电路的课题。

12.在专利文献3记载的磁检测装置中,对来自磁传感器的输出信号进行处理的检测电路部设置有平均化处理部,该平均化处理部在重复频率附近的噪声成为混叠信号并且频率比重复频率低的情况下,在重复频率的周期内设置平均化区间,在该平均化区间中进行平均化处理,使得该低频的噪声的振幅成为一半以下。但是,该发明的磁检测装置以去除混叠噪声为目的,与去除由交流磁场输入引起的噪声的本发明相比,课题以及解决课题的手段都不同。

13.本发明的目的在于,在具备对磁传感器的检测信号进行放大的放大电路的磁检测装置中,无需使用电容器、电阻等外置部件而能够去除由交流磁场输入引起的噪声。

14.另外,本发明的目的在于提供一种能够在交流磁场强度高的环境中使用并且适合

于半导体集成电路化的磁检测装置。

15.本发明的另一目的在于提供一种能够改变想要作为噪声去除的交流磁场的频率的磁检测装置以及磁检测信号放大用半导体集成电路。

16.用于解决课题的手段

17.为了实现上述目的,本发明构成为

18.磁检测装置具备对来自检测交流磁场的磁传感器的检测信号进行放大的放大电路,该磁检测装置中具备:

19.计时器电路,其根据所述放大电路的输出的变化而启动,当计时了预定时间时输出发生变化;

20.逻辑电路,其以所述计时器电路的输出为输入;以及

21.振荡电路,其用于生成所述计时器电路的动作时钟信号,

22.所述计时器电路在所述预定时间的计时完成之前所述放大电路的输出被复位,由此禁止比所述预定时间短的交流磁场引起的所述逻辑电路的输出变化。

23.根据上述结构,无需使用电容器、电阻等外置部件而能够去除由交流磁场输入引起的噪声。另外,能够在交流磁场强度高的环境中使用,并且不需要陶瓷电容器那样的部件,因此适合于半导体集成电路化。

24.在此,所述放大电路的输出变化为第一电平和第二电平,所述计时器电路具备:第一计时器,其根据所述放大电路的输出从第一电平变化为第二电平而启动,并进行预定时间的计时;以及第二计时器,其根据所述放大电路的输出从第二电平变化为第一电平而启动,并进行预定时间的计时,

25.所述第一计时器和第二计时器分别根据所述放大电路的输出变化为与启动时不同的方向而被复位。

26.根据上述结构,在逻辑电路的输出上升到有效电平(磁检测电平)之前,能够通过第一计时器的复位来防止由预定频率以下的交流磁场引起的逻辑电路的误动作,在逻辑电路的输出上升到有效电平之后,能够通过第二计时器的复位来防止由预定频率以下的交流磁场引起的逻辑电路的误动作。

27.此外,逻辑电路具备触发器电路,

28.所述触发器电路构成为根据所述第一计时器的输出变化,所述触发器电路的输出变化为高电平或低电平,根据所述第二计时器的输出变化,所述触发器电路的输出变化为低电平或高电平。

29.根据该结构,能够用比较简单的电路构成逻辑电路,并从逻辑电路输出表示是否检测出监视对象的磁场的信号。

30.并且,所述第一定时器和所述第二定时器构成为根据所述放大电路的输出状态使任意一方成为动作状态,使另一方成为非动作状态。

31.根据这样的结构,能够降低电路的功耗。

32.并且,构成为具备寄存器,该寄存器用于从外部设定所述第一定时器和/或所述第二定时器计时的预定时间。

33.根据该结构,通过改变向寄存器的设定值,能够改变想要作为噪声去除的交流磁场的频率。

34.本技术的另一发明在磁检测信号放大用半导体集成电路中,在1个半导体基板上作为半导体集成电路形成了上述结构的磁检测装置,所述寄存器构成为能够从设置在所述半导体集成电路的外部端子输入作为串行数据的设定值。

35.根据具有上述结构的半导体集成电路,无需大幅增加外部端子的数量而能够向寄存器输入设定值。

36.发明效果

37.根据本发明,在具备对磁传感器的检测信号进行放大的放大电路的磁检测装置中,无需在电路的外部使用电容器、电阻等部件而能够去除由交流磁场输入引起的噪声。另外,能够实现一种可在交流磁场强度高的环境中使用,并且适合于半导体集成电路化的磁检测装置。并且,根据本发明,具有如下效果:能够提供一种可改变想要作为噪声去除的交流磁场的频率的磁检测装置以及磁检测信号放大用半导体集成电路。

附图说明

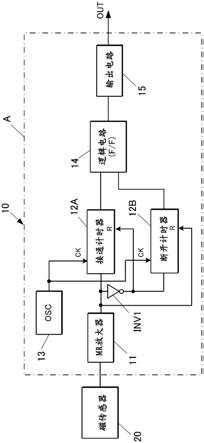

38.图1是表示本发明的磁检测装置的一实施方式的电路结构图。

39.图2中的a~e是表示实施方式的磁检测装置中的作为噪声的交流磁场、检测对象的磁场、磁传感器的输出以及放大器的输出、电路输出的变化的时序图,图2中的f是表示未设置计时器电路的磁检测装置中的电路输出的变化的时序图。

40.图3是表示本发明的磁检测装置的第二实施例的电路结构图。

41.图4是表示现有的磁检测装置的例子的电路结构图。

具体实施方式

42.以下,参照附图对本发明的实施方式进行详细说明。

43.图1是表示本发明一实施方式的磁检测装置的电路图。在图1的磁检测装置10中没有特别限定,由单点划线a包围的范围的电路元件在1个半导体基板(半导体芯片)上形成为半导体集成电路(磁检测用ic)。另外,构成磁传感器20的元件可以与构成检测电路的元件一起形成在1个半导体芯片。作为磁传感器20,例如能够使用霍尔元件、磁阻元件等。

44.本实施方式的磁检测装置10具备:放大电路(mr放大器)11,其对磁传感器20的检测信号进行放大;接通计时器电路12a,其与放大电路11的输出信号的上升同步地进行预定的设定时间的计时;断开计时器电路12b,其与放大电路11的输出信号的下降同步地进行预定的设定时间的计时;以及振荡电路(osc)13,其生成计时器电路12a、12b的动作时钟信号ck。计时器电路12a、12b能够由计数器电路构成。

45.另外,磁检测装置10具备:逻辑电路14,其将计时器电路12a、12b的输出信号作为输入;以及输出驱动器电路15,其接受逻辑电路14的输出信号来生成向芯片外部输出的信号out(磁检测输出)。

46.接通计时器电路12a与放大电路11的输出信号的上升同步地开始计时动作,当计时了预定时间时输出变化为高电平,根据由反相器inv1使放大电路11的输出信号反转后的信号变化为高电平而被复位,接通计时器电路12a的输出变化为低电平。另一方面,断开计时器电路12b根据由反相器inv1使放大电路11的输出信号反转后的信号,与放大电路11的输出信号的下降同步地开始计时动作,当计时了预定时间时输出变化为高电平,根据放大

电路11的输出信号变换为高电平而被复位,断开计时器电路12b的输出变化为低电平。

47.放大电路11例如由输出根据输入的电位而变化的放大器、将该放大器的输出与预定的电压进行比较的比较器等构成。振荡电路13能够由环形振荡器等构成。

48.逻辑电路14能够由rs触发器构成,当接通计时器电路12a的输出变化为高电平时,逻辑电路14的输出变化为高电平并保持该输出状态。另外,当断开计时器电路12b的输出变化为高电平时,逻辑电路14的输出变化为低电平并保持该输出状态。

49.接着,使用图2的时序图对上述磁检测装置10的功能进行说明。

50.在不具有图1所示的磁检测装置10中的计时器电路12a、12b以及逻辑电路14的图4所示的现有检测电路的情况下,在图2的(a)所示的具有交流磁场的环境中放置了磁传感器20的状况下,当图2的(b)所示那样的检测对象的磁场进入磁传感器20时,磁传感器20的输出如图2的(c)所示那样变化,放大电路11的输出如图2的(d)所示那样变化。于是,如图2的(f)所示,从输出驱动器电路15输出的信号out成为包含由交流磁场引起的噪声的信号。

51.与此相对,在上述实施方式的磁检测装置10中,在放大电路11的输出如图2的(d)所示那样变化的情况下,接通计时器电路12a在放大电路11的输出信号的上升定时t1、t2、t3开始计时动作,但当计时了预定时间之前放大电路11的输出信号下降时施加复位,如图2的(e)所示,从输出信号out去除噪声。然后,在由于本来的检测对象的磁场发生了变化而从放大电路11的输出信号已上升的定时t4开始计时了预定时间的定时t5,输出信号out变为高电平。

52.另外,在输出信号out上升后,在放大电路11的输出如图2的(d)所示那样变化的情况下,断开计时器电路12b在放大电路11的输出信号的下降定时t6、t7、t8开始计时动作,但当计时了预定时间之前放大电路11的输出信号上升时施加复位,如图2的(e)所示,从输出信号out去除噪声。然后,在由于本来的检测对象的磁场发生了变化而从放大电路11的输出信号的已下降的定时t9开始计时了预定时间的定时t10,输出信号out变为低电平。

53.因此,上述实施方式的磁检测装置10通过适当设定可变式的计时器电路12a、12b的计时时间,能够去除由预定频率以下的交流磁场引起的噪声。另外,无需设置电容器、电阻等外置部件而能够去除由交流磁场引起的噪声。例如,通过将计时器电路12a、12b的计时时间设为10ms,能够去除50hz以下的噪声。

54.接着,使用图3对上述实施方式的磁检测装置10的第二实施例进行说明。

55.如图3所示,第二实施例的磁检测装置设置有能够从外部设定计时器电路12a、12b所计时的预定时间的寄存器16以及用于输入设定值的外部端子p1。

56.根据上述结构,通过改变在寄存器16中设定的值,能够任意地设定想要去除的交流磁场的频率。为了减少端子数,寄存器16可以使用能够从外部串行输入数据的移位寄存器。另外,也可以构成为设置2个寄存器16,能够分别设定接通计时器电路12a计时的时间和断开计时器电路12b计时的时间。

57.并且,在图3的实施例的磁检测装置中,设置使逻辑电路14的输出反转的反相器inv2,将由反相器inv2反转后的信号作为允许接通计时器电路12a的计时动作的使能信号en1提供给接通计时器电路12a,并且将逻辑电路14的输出信号作为允许断开计时器电路12b的计时动作的使能信号en2提供给断开计时器电路12b。

58.根据具有上述结构的磁检测装置,具有如下优点:在接通计时器电路12a进行计时

动作的期间,能够使断开计时器电路12b的计时动作停止,在断开计时器电路12b进行计时动作的期间,能够使接通计时器电路12a的计时动作停止,由此能够降低电路的功耗。

59.以上,对本发明的实施方式进行了说明,但本发明并不限于上述实施方式。例如,在上述实施方式中,说明了作为放大电路11,由输出根据输入的电位而变化的放大器以及将该放大器的输出与预定的电压进行比较的比较器构成,但也可以是由放大器和施密特触发电路构成的放大器、具有输出变化为高电平和低电平的特性的放大器。

60.另外,在上述实施方式中,在芯片内部设置了生成用于使计时器电路12a、12b进行计时动作的时钟信号的振荡电路13,但也可以构成为设置用于从外部输入时钟信号的外部端子而省略振荡电路13。

61.工业上的应用

62.本发明并不限于致动器的工作状态检测的用途,还能够广泛应用于检测电动机的转子位置,对设置在交流磁场有可能作为噪声而进入的位置的用于检测监视对象的磁场的磁传感器的输出信号进行放大的磁检测装置。

63.附图标记的说明

64.10...磁检测装置、11...放大电路、12a...接通计时器电路(第一计时器)、12b...断开计时器电路(第二计时器)、13...振荡电路、14...逻辑电路、15...输出驱动器电路、16...寄存器、20...磁传感器、out...磁检测输出。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。