1.本发明涉及一种解码电路,尤其涉及一种解码电路模块、存储器控制电路单元及存储器存储装置。

背景技术:

::2.数码相机、移动电话与mp3播放器在这几年来的成长十分迅速,使得消费者对存储媒体的需求也急速增加。由于可复写式非易失性存储器模块(rewritablenon-volatilememorymodule)(例如,快闪存储器)具有数据非易失性、省电、体积小,以及无机械结构等特性,所以非常适合内建于上述所举例的各种可携式多媒体装置中。3.许多存储器控制器配置有解码电路,以对从可复写式非易失性存储器模块中读取出的数据进行错误检查与更正。然而,现有的解码电路主要都是以采用的解码流程来进行设计,在使用上较无弹性。例如,在同时包含初阶解码电路与进阶解码电路的电路架构中,从可复写式非易失性存储器模块中读取的数据必须先经过初阶解码电路处理。若初阶解码电路无法成功解码此数据,则初阶解码电路可接续将此数据送到进阶解码电路进行进阶解码。但是,在此电路架构下,一旦进阶解码电路处于忙碌状态,则初阶解码电路需要等到进阶解码电路结束工作后才能处理下一笔数据。若进阶解码电路经常处于忙碌状态,则初阶解码电路处于闲置状态的时间也会增加,造成系统资源浪费。技术实现要素:4.本发明提供一种解码电路模块、存储器控制电路单元及存储器存储装置,可提升解码电路模块中不同类型的解码电路的工作效率。5.本发明的范例实施例提供一种解码电路模块,其用以解码从可复写式非易失性存储器模块读取的数据。所述解码电路模块包括第一缓冲器、第二缓冲器、第一解码电路及第二解码电路。所述第一缓冲器连接至所述可复写式非易失性存储器模块。所述第二缓冲器连接至所述第一缓冲器。所述第一解码电路连接至所述第一缓冲器与所述第二缓冲器。所述第二解码电路连接至所述第二缓冲器。所述第一解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第一缓冲器中的第一数据。所述第二解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第二缓冲器中的第二数据。所述第一解码电路的数据解码能力不同于所述第二解码电路的数据解码能力。所述第二数据经过所述第一缓冲器而存储于所述第二缓冲器中且未经所述第一解码电路处理。6.在本发明的一范例实施例中,所述第一解码电路更用以将经解码的所述第一数据传送至所述第二缓冲器。7.在本发明的一范例实施例中,所述第二解码电路更用以将经解码的所述第二数据传送至所述第二缓冲器。8.在本发明的一范例实施例中,所述的解码电路模块还包括第一处理电路,其连接至所述第二解码电路。所述第一处理电路用以产生对应于所述第二数据的可靠度数据。所述第二解码电路更用以根据所述可靠度数据解码所述第二数据。9.在本发明的一范例实施例中,所述的解码电路模块还包括第二处理电路,其连接至所述第一处理电路。所述第二处理电路用以根据从所述可复写式非易失性存储器模块读取的第三数据产生软比特数据。所述第一处理电路更用以根据所述软比特数据产生所述可靠度数据。10.在本发明的一范例实施例中,所述第一解码电路用以实现比特翻转算法。11.在本发明的一范例实施例中,所述第二解码电路用以实现总和-乘积算法与最小-总和算法的至少其中之一。12.在本发明的一范例实施例中,所述第一缓冲器专用以缓存从所述可复写式非易失性存储器模块读取的数据。13.在本发明的一范例实施例中,所述解码电路模块还包括第一电路模块与第二电路模块。所述第一解码电路与所述第一缓冲器设置于所述第一电路模块中。所述第二解码电路设置于所述第二电路模块中。所述第二缓冲器连接至所述第一电路模块与所述第二电路模块。14.在本发明的一范例实施例中,所述第一缓冲器中的数据仅供所述第一电路模块中的电路使用。所述第二缓冲器中的数据可供所述第一电路模块与所述第二电路模块中的电路使用。15.本发明的范例实施例另提供一种存储器控制电路单元,其用以控制可复写式非易失性存储器模块。所述存储器控制电路单元包括主机接口、存储器接口、解码电路模块及存储器管理电路。所述主机接口用以连接至主机系统。所述存储器接口用以连接至所述可复写式非易失性存储器模块。所述解码电路模块连接至所述可复写式非易失性存储器模块并用以解码从所述可复写式非易失性存储器模块读取的数据。所述存储器管理电路连接至所述主机接口、存储器接口及解码电路模块。所述解码电路模块包括第一缓冲器、第二缓冲器、第一解码电路及第二解码电路。所述第一缓冲器连接至所述可复写式非易失性存储器模块。所述第二缓冲器连接至所述第一缓冲器。所述第一解码电路连接至所述第一缓冲器与所述第二缓冲器。所述第二解码电路连接至所述第二缓冲器。所述第一解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第一缓冲器中的第一数据。所述第二解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第二缓冲器中的第二数据。所述第一解码电路的数据解码能力不同于所述第二解码电路的数据解码能力。所述第二数据经过所述第一缓冲器而存储于所述第二缓冲器中且未经所述第一解码电路处理。16.本发明的范例实施例另提供一种存储器存储装置,其包括连接接口单元、可复写式非易失性存储器模块及存储器控制电路单元。所述连接接口单元用以连接至主机系统。所述存储器控制电路单元连接至所述连接接口单元与所述可复写式非易失性存储器模块。所述存储器控制电路单元包括解码电路模块。所述解码电路模块包括第一缓冲器、第二缓冲器、第一解码电路及第二解码电路。所述第一缓冲器连接至所述可复写式非易失性存储器模块。所述第二缓冲器连接至所述第一缓冲器。所述第一解码电路连接至所述第一缓冲器与所述第二缓冲器。所述第二解码电路连接至所述第二缓冲器。所述第一解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第一缓冲器中的第一数据。所述第二解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第二缓冲器中的第二数据。所述第一解码电路的数据解码能力不同于所述第二解码电路的数据解码能力。所述第二数据经过所述第一缓冲器而存储于所述第二缓冲器中且未经所述第一解码电路处理。17.基于上述,解码电路模块可包括具有不同数据解码能力的第一解码电路与第二解码电路。第一解码电路可用以解码从可复写式非易失性存储器模块读取且存储于第一缓冲器中的第一数据。第二解码电路可用以解码从可复写式非易失性存储器模块读取且存储于第二缓冲器中的第二数据。特别是,所述第二数据可经过第一缓冲器而存储于第二缓冲器中且未经第一解码电路处理。藉此,可提升解码电路模块中不同类型的解码电路的工作效率。附图说明18.图1是根据本发明的范例实施例所示出的主机系统、存储器存储装置及输入/输出(i/o)装置的示意图;19.图2是根据本发明的范例实施例所示出的主机系统、存储器存储装置及i/o装置的示意图;20.图3是根据本发明的范例实施例所示出的主机系统与存储器存储装置的示意图;21.图4是根据本发明的范例实施例所示出的存储器存储装置的示意图;22.图5是根据本发明的范例实施例所示出的存储器控制电路单元的示意图;23.图6是根据本发明的范例实施例所示出的管理可复写式非易失性存储器模块的示意图;24.图7是根据本发明的范例实施例所示出的解码电路模块的示意图;25.图8是根据本发明的范例实施例所示出的由第一解码电路解码第一数据的示意图;26.图9是根据本发明的范例实施例所示出的由第二解码电路解码第二数据的示意图。具体实施方式27.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。28.一般而言,存储器存储装置(亦称,存储器存储系统)包括可复写式非易失性存储器模块(rewritablenon-volatilememorymodule)与控制器(亦称,控制电路)。存储器存储装置可与主机系统一起使用,以使主机系统可将数据写入至存储器存储装置或从存储器存储装置中读取数据。29.图1是根据本发明的范例实施例所示出的主机系统、存储器存储装置及输入/输出(i/o)装置的示意图。图2是根据本发明的范例实施例所示出的主机系统、存储器存储装置及i/o装置的示意图。30.请参照图1与图2,主机系统11可包括处理器111、随机存取存储器(randomaccessmemory,ram)112、只读存储器(readonlymemory,rom)113及数据传输接口114。处理器111、随机存取存储器112、只读存储器113及数据传输接口114可连接至系统总线(systembus)110。31.在一范例实施例中,主机系统11可通过数据传输接口114与存储器存储装置10连接。例如,主机系统11可经由数据传输接口114将数据存储至存储器存储装置10或从存储器存储装置10中读取数据。此外,主机系统11可通过系统总线110与i/o装置12连接。例如,主机系统11可经由系统总线110将输出信号传送至i/o装置12或从i/o装置12接收输入信号。32.在一范例实施例中,处理器111、随机存取存储器112、只读存储器113及数据传输接口114可设置在主机系统11的主机板20上。数据传输接口114的数目可以是一或多个。通过数据传输接口114,主机板20可以经由有线或无线方式连接至存储器存储装置10。33.在一范例实施例中,存储器存储装置10可例如是u盘201、存储卡202、固态硬盘(solidstatedrive,ssd)203或无线存储器存储装置204。无线存储器存储装置204可例如是近场通信(nearfieldcommunication,nfc)存储器存储装置、无线保真(wifi)存储器存储装置、蓝牙(bluetooth)存储器存储装置或低功耗蓝牙存储器存储装置(例如,ibeacon)等以各式无线通信技术为基础的存储器存储装置。此外,主机板20也可以通过系统总线110连接至全球定位系统(globalpositioningsystem,gps)模块205、网络接口卡206、无线传输装置207、键盘208、屏幕209、喇叭210等各式i/o装置。例如,在一范例实施例中,主机板20可通过无线传输装置207存取无线存储器存储装置204。34.在一范例实施例中,主机系统11为计算机系统。在一范例实施例中,主机系统11可为可实质地与存储器存储装置配合以存储数据的任意系统。在一范例实施例中,存储器存储装置10与主机系统11可分别包括图3的存储器存储装置30与主机系统31。35.图3是根据本发明的范例实施例所示出的主机系统与存储器存储装置的示意图。请参照图3,存储器存储装置30可与主机系统31搭配使用以存储数据。例如,主机系统31可以是数码相机、摄像机、通信装置、音频播放器、视频播放器或平板计算机等系统。例如,存储器存储装置30可为主机系统31所使用的安全数字(securedigital,sd)卡32、小型快闪(compactflash,cf)卡33或嵌入式存储装置34等各式非易失性存储器存储装置。嵌入式存储装置34包括嵌入式多媒体卡(embeddedmultimediacard,emmc)341和/或嵌入式多芯片封装(embeddedmultichippackage,emcp)存储装置342等各类型将存储器模块直接连接于主机系统的基板上的嵌入式存储装置。36.图4是根据本发明的范例实施例所示出的存储器存储装置的示意图。请参照图4,存储器存储装置10包括连接接口单元41、存储器控制电路单元42与可复写式非易失性存储器模块43。37.连接接口单元41用以将存储器存储装置10连接主机系统11。存储器存储装置10可经由连接接口单元41与主机系统11通信。在一范例实施例中,连接接口单元41是相容于高速周边零件连接接口(peripheralcomponentinterconnectexpress,pciexpress)标准。然而,必须了解的是,本发明不限于此,连接接口单元41亦可以是符合串行高级技术附件(serialadvancedtechnologyattachment,sata)标准、并行高级技术附件(paralleladvancedtechnologyattachment,pata)标准、电气和电子工程师协会(instituteofelectricalandelectronicengineers,ieee)1394标准、通用串行总线(universalserialbus,usb)标准、sd接口标准、超高速一代(ultrahighspeed-i,uhs-i)接口标准、超高速二代(ultrahighspeed-ii,uhs-ii)接口标准、存储棒(memorystick,ms)接口标准、mcp接口标准、mmc接口标准、emmc接口标准、通用快闪存储器(universalflashstorage,ufs)接口标准、emcp接口标准、cf接口标准、整合式驱动电子接口(integrateddeviceelectronics,ide)标准或其他适合的标准。连接接口单元41可与存储器控制电路单元42封装在一个芯片中,或者连接接口单元41是布设于一包含存储器控制电路单元42的芯片外。38.存储器控制电路单元42连接至连接接口单元41与可复写式非易失性存储器模块43。存储器控制电路单元42用以执行以硬件型式或固件型式实作的多个逻辑门或控制指令并且根据主机系统11的指令在可复写式非易失性存储器模块43中进行数据的写入、读取与抹除等运作。39.可复写式非易失性存储器模块43用以存储主机系统11所写入的数据。可复写式非易失性存储器模块43可包括单阶存储单元(singlelevelcell,slc)nand型快闪存储器模块(即,一个存储单元中可存储1个比特的快闪存储器模块)、二阶存储单元(multilevelcell,mlc)nand型快闪存储器模块(即,一个存储单元中可存储2个比特的快闪存储器模块)、三阶存储单元(triplelevelcell,tlc)nand型快闪存储器模块(即,一个存储单元中可存储3个比特的快闪存储器模块)、四阶存储单元(quadlevelcell,qlc)nand型快闪存储器模块(即,一个存储单元中可存储4个比特的快闪存储器模块)、其他快闪存储器模块或其他具有相同特性的存储器模块。40.可复写式非易失性存储器模块43中的每一个存储单元是以电压(以下亦称为临界电压)的改变来存储一或多个比特。具体来说,每一个存储单元的控制门(controlgate)与通道之间有一个电荷捕捉层。通过施予一写入电压至控制门,可以改变电荷补捉层的电子量,进而改变存储单元的临界电压。此改变存储单元的临界电压的操作亦称为“把数据写入至存储单元”或“程序化(programming)存储单元”。随着临界电压的改变,可复写式非易失性存储器模块43中的每一个存储单元具有多个存储状态。通过施予读取电压可以判断一个存储单元是属于哪一个存储状态,藉此取得此存储单元所存储的一或多个比特。41.在一范例实施例中,可复写式非易失性存储器模块43的存储单元可构成多个实体程序化单元,并且此些实体程序化单元可构成多个实体抹除单元。具体来说,同一条字线上的存储单元可组成一或多个实体程序化单元。若每一个存储单元可存储2个以上的比特,则同一条字线上的实体程序化单元可至少可被分类为下实体程序化单元与上实体程序化单元。例如,一存储单元的最低有效比特(leastsignificantbit,lsb)是属于下实体程序化单元,并且一存储单元的最高有效比特(mostsignificantbit,msb)是属于上实体程序化单元。一般来说,在mlcnand型快闪存储器中,下实体程序化单元的写入速度会大于上实体程序化单元的写入速度,和/或下实体程序化单元的可靠度是高于上实体程序化单元的可靠度。42.在一范例实施例中,实体程序化单元为程序化的最小单元。即,实体程序化单元为写入数据的最小单元。例如,实体程序化单元可为实体页(page)或是实体扇(sector)。若实体程序化单元为实体页,则此些实体程序化单元可包括数据比特区与冗余(redundancy)比特区。数据比特区包含多个实体扇,用以存储用户数据,而冗余比特区用以存储系统数据(例如,错误更正码等管理数据)。在一范例实施例中,数据比特区包含32个实体扇,且一个实体扇的大小为512字节(byte,b)。然而,在其他范例实施例中,数据比特区中也可包含8个、16个或数目更多或更少的实体扇,并且每一个实体扇的大小也可以是更大或更小。另一方面,实体抹除单元为抹除的最小单位。亦即,每一实体抹除单元含有最小数目的一并被抹除的存储单元。例如,实体抹除单元为实体区块(block)。43.图5是根据本发明的范例实施例所示出的存储器控制电路单元的示意图。请参照图5,存储器控制电路单元42包括存储器管理电路51、主机接口52、存储器接口53及解码电路模块54。44.存储器管理电路51用以控制存储器控制电路单元42的整体运作。具体来说,存储器管理电路51具有多个控制指令,并且在存储器存储装置10运作时,此些控制指令会被执行以进行数据的写入、读取与抹除等运作。以下说明存储器管理电路51的操作时,等同于说明存储器控制电路单元42的操作。45.在一范例实施例中,存储器管理电路51的控制指令是以固件型式来实作。例如,存储器管理电路51具有微处理器单元(未示出)与只读存储器(未示出),并且此些控制指令是被烧录至此只读存储器中。当存储器存储装置10运作时,此些控制指令会由微处理器单元来执行以进行数据的写入、读取与抹除等运作。46.在一范例实施例中,存储器管理电路51的控制指令亦可以程序码型式存储于可复写式非易失性存储器模块43的特定区域(例如,存储器模块中专用于存放系统数据的系统区)中。此外,存储器管理电路51具有微处理器单元(未示出)、只读存储器(未示出)及随机存取存储器(未示出)。特别是,此只读存储器具有开机码(bootcode),并且当存储器控制电路单元42被致能时,微处理器单元会先执行此开机码来将存储于可复写式非易失性存储器模块43中的控制指令载入至存储器管理电路51的随机存取存储器中。之后,微处理器单元会运转此些控制指令以进行数据的写入、读取与抹除等运作。47.在一范例实施例中,存储器管理电路51的控制指令亦可以一硬件型式来实作。例如,存储器管理电路51包括微控制器、存储单元管理电路、存储器写入电路、存储器读取电路、存储器抹除电路与数据处理电路。存储单元管理电路、存储器写入电路、存储器读取电路、存储器抹除电路与数据处理电路是连接至微控制器。存储单元管理电路用以管理可复写式非易失性存储器模块43的存储单元或存储单元群组。存储器写入电路用以对可复写式非易失性存储器模块43下达写入指令序列以将数据写入至可复写式非易失性存储器模块43中。存储器读取电路用以对可复写式非易失性存储器模块43下达读取指令序列以从可复写式非易失性存储器模块43中读取数据。存储器抹除电路用以对可复写式非易失性存储器模块43下达抹除指令序列以将数据从可复写式非易失性存储器模块43中抹除。数据处理电路用以处理欲写入至可复写式非易失性存储器模块43的数据以及从可复写式非易失性存储器模块43中读取的数据。写入指令序列、读取指令序列及抹除指令序列可各别包括一或多个程序码或指令码并且用以指示可复写式非易失性存储器模块43执行相对应的写入、读取及抹除等操作。在一范例实施例中,存储器管理电路51还可以下达其他类型的指令序列给可复写式非易失性存储器模块43以指示执行相对应的操作。48.主机接口52是连接至存储器管理电路51。存储器管理电路51可通过主机接口52与主机系统11通信。主机接口52可用以接收与识别主机系统11所传送的指令与数据。例如,主机系统11所传送的指令与数据可通过主机接口52来传送至存储器管理电路51。此外,存储器管理电路51可通过主机接口52将数据传送至主机系统11。在本范例实施例中,主机接口52是相容于pciexpress标准。然而,必须了解的是本发明不限于此,主机接口52亦可以是相容于sata标准、pata标准、ieee1394标准、usb标准、sd标准、uhs-i标准、uhs-ii标准、ms标准、mmc标准、emmc标准、ufs标准、cf标准、ide标准或其他适合的数据传输标准。49.存储器接口53是连接至存储器管理电路51并且用以存取可复写式非易失性存储器模块43。例如,存储器管理电路51可通过存储器接口53存取可复写式非易失性存储器模块43。也就是说,欲写入至可复写式非易失性存储器模块43的数据会经由存储器接口53转换为可复写式非易失性存储器模块43所能接受的格式。具体来说,若存储器管理电路51要存取可复写式非易失性存储器模块43,存储器接口53会传送对应的指令序列。例如,这些指令序列可包括指示写入数据的写入指令序列、指示读取数据的读取指令序列、指示抹除数据的抹除指令序列、以及用以指示各种存储器操作(例如,改变读取电压电平或执行垃圾回收操作等等)的相对应的指令序列。这些指令序列例如是由存储器管理电路51产生并且通过存储器接口53传送至可复写式非易失性存储器模块43。这些指令序列可包括一或多个信号,或是在总线上的数据。这些信号或数据可包括指令码或程序码。例如,在读取指令序列中,会包括读取的识别码、存储器地址等信息。50.解码电路模块(亦称为错误检查与校正电路)54是连接至存储器管理电路51并且用以执行错误检查与校正操作以确保数据的正确性。具体来说,当存储器管理电路51从主机系统11中接收到写入指令时,解码电路模块54会为对应此写入指令的数据产生对应的错误更正码(errorcorrectingcode,ecc)和/或错误检查码(errordetectingcode,edc),并且存储器管理电路51会将对应此写入指令的数据与对应的错误更正码和/或错误检查码写入至可复写式非易失性存储器模块43中。之后,当存储器管理电路51从可复写式非易失性存储器模块43中读取数据时会同时读取此数据对应的错误更正码和/或错误检查码,并且解码电路模块54会依据此错误更正码和/或错误检查码对所读取的数据执行错误检查与校正操作。51.在一范例实施例中,存储器控制电路单元42还包括缓冲存储器55与电源管理电路56。缓冲存储器55是连接至存储器管理电路51并且用以缓存数据。电源管理电路56是连接至存储器管理电路51并且用以控制存储器存储装置10的电源。52.在一范例实施例中,图4的可复写式非易失性存储器模块43可包括快闪存储器模块。在一范例实施例中,图4的存储器控制电路单元42可包括快闪存储器控制器。在一范例实施例中,图5的存储器管理电路51可包括快闪存储器管理电路。53.图6是根据本发明的范例实施例所示出的管理可复写式非易失性存储器模块的示意图。请参照图6,存储器管理电路51可将可复写式非易失性存储器模块43中的实体单元610(0)~610(b)逻辑地分组至存储区601与闲置(spare)区602。54.在一范例实施例中,一个实体单元是指一个实体地址或一个实体程序化单元。在一范例实施例中,一个实体单元亦可以是由多个连续或不连续的实体地址组成。在一范例实施例中,一个实体单元亦可以是指一个虚拟区块(vb)。一个虚拟区块可包括多个实体地址或多个实体程序化单元。55.存储区601中的实体单元610(0)~610(a)用以存储用户数据(例如来自图1的主机系统11的用户数据)。例如,存储区601中的实体单元610(0)~610(a)可存储有效(valid)数据与无效(invalid)数据。闲置区602中的实体单元610(a 1)~610(b)未存储数据(例如有效数据)。例如,若某一个实体单元未存储有效数据,则此实体单元可被关联(或加入)至闲置区602。此外,闲置区602中的实体单元(或未存储有效数据的实体单元)可被抹除。在写入新数据时,一或多个实体单元可被从闲置区602中提取以存储此新数据。在一范例实施例中,闲置区602亦称为闲置池(freepool)。56.存储器管理电路51可配置逻辑单元612(0)~612(c)以映射存储区601中的实体单元610(0)~610(a)。在一范例实施例中,每一个逻辑单元对应一个逻辑地址。例如,一个逻辑地址可包括一或多个逻辑区块地址(logicalblockaddress,lba)或其他的逻辑管理单元。在一范例实施例中,一个逻辑单元也可对应一个逻辑程序化单元或者由多个连续或不连续的逻辑地址组成。57.须注意的是,一个逻辑单元可被映射至一或多个实体单元。若某一实体单元当前有被某一逻辑单元映射,则表示此实体单元当前存储的数据包括有效数据。反之,若某一实体单元当前未被任一逻辑单元映射,则表示此实体单元当前存储的数据为无效数据。58.存储器管理电路51可将描述逻辑单元与实体单元之间的映射关系的管理数据(亦称为逻辑至实体映射信息)记录于至少一逻辑至实体映射表。当主机系统11欲从存储器存储装置10读取数据或写入数据至存储器存储装置10时,存储器管理电路51可根据此逻辑至实体映射表中的信息来存取可复写式非易失性存储器模块43。59.图7是根据本发明的范例实施例所示出的解码电路模块的示意图。请参照图7,解码电路模块54包括缓冲器(亦称为第一缓冲器或内部缓冲器)711、缓冲器(亦称为第二缓冲器或系统缓冲器)73、解码电路(亦称为第一解码电路)712及解码电路(亦称为第二解码电路)721。缓冲器711连接至可复写式非易失性存储器模块43与解码电路712。缓冲器73连接至缓冲器711、解码电路712及解码电路721。缓冲器711与73皆用以缓存(或缓存)数据。解码电路711与721皆用以解码从可复写式非易失性存储器模块43读取的数据。60.解码电路712的数据解码能力不同于解码电路721的数据解码能力。例如,解码电路721的数据解码能力可高于解码电路712的数据解码能力。例如,相较于解码电路712,解码电路721可更正数据中较多的错误比特。但是,相较于解码电路721,解码电路712可较快完成解码操作,无论解码成功与否。61.在一范例实施例中,解码电路721的电路复杂度可高于解码电路712的电路复杂度。在一范例实施例中,解码电路721所执行的解码操作的复杂度可高于解码电路712所执行的解码操作的复杂度。62.在一范例实施例中,解码电路712可用以实现比特翻转(bitflipping)算法。在一范例实施例中,解码电路721可用以实现总和-乘积(sum-product)算法与最小-总和(min-sum)算法的至少其中之一。须注意的是,解码电路712与721皆可用以实现其他类型的数据编/解码算法,本发明不加以限制。63.在一范例实施例中,缓冲器711专用以缓存从可复写式非易失性存储器模块43读取的数据,例如从可复写式非易失性存储器模块43读取且待解码的数据。特别是,缓冲器711可不属于图5的缓冲存储器55。在一范例实施例中,相较于缓冲器711,缓冲器73可视为缓冲存储器55的一部分。藉此,解码电路模块54可经由缓冲器73与图5的存储器控制电路单元42中的其他电路沟通。例如,解码电路模块54可将经解码的数据传送至缓冲器73中,以供存储器管理电路51存取或者经由主机接口52传送给图1的主机系统11。64.图8是根据本发明的范例实施例所示出的由第一解码电路解码第一数据的示意图。请参照图8,解码电路712可用以解码缓冲器711中的特定数据(亦称为第一数据)d1。例如,数据d1可从可复写式非易失性存储器模块43读取并存储于缓冲器711中。解码电路712可将经解码的数据d1传送至缓冲器73。65.图9是根据本发明的范例实施例所示出的由第二解码电路解码第二数据的示意图。请参照图9,解码电路721可用以解码缓冲器73中的特定数据(亦称为第二数据)d2。例如,数据d2可从可复写式非易失性存储器模块43读取并经由缓冲器711缓存后存储至缓冲器73中。解码电路721可将经解码的数据d2回传至缓冲器73。66.在一范例实施例中,响应于解码电路712对从某一实体单元(亦称为第一实体单元)读取的数据d1的解码失败,数据d2可从同一个实体单元(即第一实体单元)读取出来并由解码能力较强的解码电路721进行解码。特别是,在解码电路721解码数据d2的过程中,解码电路712可接续解码下一笔数据,而不需等待解码电路721解除忙碌状态。67.从另一角度而言,在图8与图9的范例实施例中,解码电路712与721所执行的解码操作彼此可不互相干涉和/或解码电路712与721所执行的解码操作可不需相互等待。例如,在解码电路712解码缓冲器711中的数据d1(如图8所示)时,解码电路721可同步解码缓冲器73中的数据d2(如图9所示)。藉此,即便解码电路721持续处于忙碌状态,解码电路712仍可同步执行对其他数据的解码。相较于传统上解码电路712需要等待解码电路721完成解码操作后才能处理新数据,解码电路712的工作效能可被提升。68.在一范例实施例中,解码电路模块54可包括电路模块(亦称为第一电路模块)71与电路模块(亦称为第二电路模块)72。解码电路712与缓冲器711可设置于电路模块71中。解码电路721可设置于电路模块72中。例如,电路模块71可设置于某一电路板(亦称为第一电路板)中,且电路模块72可设置于另一电路板(亦称为第二电路板)中。或者,电路模块71与72亦可设置于同一电路板中的不同区域。缓冲器73可连接至电路模块71与72。69.在一范例实施例中,缓冲器711中的数据仅供电路模块71中的电路(例如解码电路712)使用。在一范例实施例中,缓冲器73中的数据可供电路模块71与72中的电路(例如解码电路712与721)使用。70.在一范例实施例中,数据d1与d2皆可包括硬比特数据。硬比特数据是指使用单一个读取电压电平从可复写式非易失性存储器模块43中的单一存储单元读取的数据。在硬比特解码模式中,解码电路712可对缓冲器711中的硬比特数据进行解码和/或解码电路721可对缓冲器73中的硬比特数据进行解码。此外,在硬比特解码模式中,用来读取特定存储单元(或实体单元)的读取电压电平可被调整,以尝试降低读取到错误比特的机率。71.相较于硬比特数据,软比特数据是指使用多个读取电压电平重复读取可复写式非易失性存储器模块43中的单一存储单元所获得的数据。相较于硬比特数据,软比特数据可带有更多可辅助对此存储单元所存储的数据进行解码的信息。在软比特解码模式中,对应于数据d2的可靠度数据可根据软比特数据产生,且解码电路721可根据所述可靠度数据对数据d2进行解码,以提高数据d2的解码成功率。72.在一范例实施例中,解码电路模块54还包括处理电路(亦称为第一处理电路)722。处理电路722可连接至缓冲器73与解码电路721。例如,处理电路722可设置于电路模块72中。在图9的范例实施例中,处理电路722可用以产生对应于数据d2的可靠度数据。例如,所述可靠度信息可缓存于缓冲器73中或者不经由缓冲器73直接提供给解码电路721使用。解码电路721可根据所述可靠度数据来解码数据d2。例如,所述可靠度数据可包括对数相似性比值(log-likelihoodratio,llr)等可用以在解码过程中辅助判断数据d2中的特定比特应该被解码为比特“1”或“0”的辅助数据。73.在一范例实施例中,解码电路模块54还包括处理电路(亦称为第二处理电路)723。处理电路723可连接至缓冲器73与处理电路722。例如,处理电路723可设置于电路模块72中。在图9的范例实施例中,处理电路723可根据从可复写式非易失性存储器模块43读取的数据(亦称为第三数据)产生软比特数据。例如,所述软比特数据可缓存于缓冲器73中或者不经由缓冲器73直接提供给处理电路722使用。处理电路722可根据所述软比特数据产生对应于数据d2的可靠度数据。例如,处理电路722可根据所述软比特数据查询对数相似性比值映射表,以获得对应于数据d2的可靠度数据(例如llr数值)。然后,处理电路722可提供所述可靠度数据给解码电路721以解码数据d2。74.须注意的是,在图7至图9的范例实施例中,更多具有特定功能的电路可以被加入至电路模块71和/或72中,本发明不加以限制。此外,图7至图9的范例实施例中至少部分电路的连接关系也可以被调整,本发明不加以限制。75.综上所述,本发明的范例实施例通过特殊的电路布局,使解码电路模块中不同类型(例如具有不同解码能力)的解码电路皆可独立运作且运作上不须相互等待。藉此,可提升解码电路模块整体的工作效率。76.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。当前第1页12当前第1页12

背景技术:

::2.数码相机、移动电话与mp3播放器在这几年来的成长十分迅速,使得消费者对存储媒体的需求也急速增加。由于可复写式非易失性存储器模块(rewritablenon-volatilememorymodule)(例如,快闪存储器)具有数据非易失性、省电、体积小,以及无机械结构等特性,所以非常适合内建于上述所举例的各种可携式多媒体装置中。3.许多存储器控制器配置有解码电路,以对从可复写式非易失性存储器模块中读取出的数据进行错误检查与更正。然而,现有的解码电路主要都是以采用的解码流程来进行设计,在使用上较无弹性。例如,在同时包含初阶解码电路与进阶解码电路的电路架构中,从可复写式非易失性存储器模块中读取的数据必须先经过初阶解码电路处理。若初阶解码电路无法成功解码此数据,则初阶解码电路可接续将此数据送到进阶解码电路进行进阶解码。但是,在此电路架构下,一旦进阶解码电路处于忙碌状态,则初阶解码电路需要等到进阶解码电路结束工作后才能处理下一笔数据。若进阶解码电路经常处于忙碌状态,则初阶解码电路处于闲置状态的时间也会增加,造成系统资源浪费。技术实现要素:4.本发明提供一种解码电路模块、存储器控制电路单元及存储器存储装置,可提升解码电路模块中不同类型的解码电路的工作效率。5.本发明的范例实施例提供一种解码电路模块,其用以解码从可复写式非易失性存储器模块读取的数据。所述解码电路模块包括第一缓冲器、第二缓冲器、第一解码电路及第二解码电路。所述第一缓冲器连接至所述可复写式非易失性存储器模块。所述第二缓冲器连接至所述第一缓冲器。所述第一解码电路连接至所述第一缓冲器与所述第二缓冲器。所述第二解码电路连接至所述第二缓冲器。所述第一解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第一缓冲器中的第一数据。所述第二解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第二缓冲器中的第二数据。所述第一解码电路的数据解码能力不同于所述第二解码电路的数据解码能力。所述第二数据经过所述第一缓冲器而存储于所述第二缓冲器中且未经所述第一解码电路处理。6.在本发明的一范例实施例中,所述第一解码电路更用以将经解码的所述第一数据传送至所述第二缓冲器。7.在本发明的一范例实施例中,所述第二解码电路更用以将经解码的所述第二数据传送至所述第二缓冲器。8.在本发明的一范例实施例中,所述的解码电路模块还包括第一处理电路,其连接至所述第二解码电路。所述第一处理电路用以产生对应于所述第二数据的可靠度数据。所述第二解码电路更用以根据所述可靠度数据解码所述第二数据。9.在本发明的一范例实施例中,所述的解码电路模块还包括第二处理电路,其连接至所述第一处理电路。所述第二处理电路用以根据从所述可复写式非易失性存储器模块读取的第三数据产生软比特数据。所述第一处理电路更用以根据所述软比特数据产生所述可靠度数据。10.在本发明的一范例实施例中,所述第一解码电路用以实现比特翻转算法。11.在本发明的一范例实施例中,所述第二解码电路用以实现总和-乘积算法与最小-总和算法的至少其中之一。12.在本发明的一范例实施例中,所述第一缓冲器专用以缓存从所述可复写式非易失性存储器模块读取的数据。13.在本发明的一范例实施例中,所述解码电路模块还包括第一电路模块与第二电路模块。所述第一解码电路与所述第一缓冲器设置于所述第一电路模块中。所述第二解码电路设置于所述第二电路模块中。所述第二缓冲器连接至所述第一电路模块与所述第二电路模块。14.在本发明的一范例实施例中,所述第一缓冲器中的数据仅供所述第一电路模块中的电路使用。所述第二缓冲器中的数据可供所述第一电路模块与所述第二电路模块中的电路使用。15.本发明的范例实施例另提供一种存储器控制电路单元,其用以控制可复写式非易失性存储器模块。所述存储器控制电路单元包括主机接口、存储器接口、解码电路模块及存储器管理电路。所述主机接口用以连接至主机系统。所述存储器接口用以连接至所述可复写式非易失性存储器模块。所述解码电路模块连接至所述可复写式非易失性存储器模块并用以解码从所述可复写式非易失性存储器模块读取的数据。所述存储器管理电路连接至所述主机接口、存储器接口及解码电路模块。所述解码电路模块包括第一缓冲器、第二缓冲器、第一解码电路及第二解码电路。所述第一缓冲器连接至所述可复写式非易失性存储器模块。所述第二缓冲器连接至所述第一缓冲器。所述第一解码电路连接至所述第一缓冲器与所述第二缓冲器。所述第二解码电路连接至所述第二缓冲器。所述第一解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第一缓冲器中的第一数据。所述第二解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第二缓冲器中的第二数据。所述第一解码电路的数据解码能力不同于所述第二解码电路的数据解码能力。所述第二数据经过所述第一缓冲器而存储于所述第二缓冲器中且未经所述第一解码电路处理。16.本发明的范例实施例另提供一种存储器存储装置,其包括连接接口单元、可复写式非易失性存储器模块及存储器控制电路单元。所述连接接口单元用以连接至主机系统。所述存储器控制电路单元连接至所述连接接口单元与所述可复写式非易失性存储器模块。所述存储器控制电路单元包括解码电路模块。所述解码电路模块包括第一缓冲器、第二缓冲器、第一解码电路及第二解码电路。所述第一缓冲器连接至所述可复写式非易失性存储器模块。所述第二缓冲器连接至所述第一缓冲器。所述第一解码电路连接至所述第一缓冲器与所述第二缓冲器。所述第二解码电路连接至所述第二缓冲器。所述第一解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第一缓冲器中的第一数据。所述第二解码电路用以解码从所述可复写式非易失性存储器模块读取且存储于所述第二缓冲器中的第二数据。所述第一解码电路的数据解码能力不同于所述第二解码电路的数据解码能力。所述第二数据经过所述第一缓冲器而存储于所述第二缓冲器中且未经所述第一解码电路处理。17.基于上述,解码电路模块可包括具有不同数据解码能力的第一解码电路与第二解码电路。第一解码电路可用以解码从可复写式非易失性存储器模块读取且存储于第一缓冲器中的第一数据。第二解码电路可用以解码从可复写式非易失性存储器模块读取且存储于第二缓冲器中的第二数据。特别是,所述第二数据可经过第一缓冲器而存储于第二缓冲器中且未经第一解码电路处理。藉此,可提升解码电路模块中不同类型的解码电路的工作效率。附图说明18.图1是根据本发明的范例实施例所示出的主机系统、存储器存储装置及输入/输出(i/o)装置的示意图;19.图2是根据本发明的范例实施例所示出的主机系统、存储器存储装置及i/o装置的示意图;20.图3是根据本发明的范例实施例所示出的主机系统与存储器存储装置的示意图;21.图4是根据本发明的范例实施例所示出的存储器存储装置的示意图;22.图5是根据本发明的范例实施例所示出的存储器控制电路单元的示意图;23.图6是根据本发明的范例实施例所示出的管理可复写式非易失性存储器模块的示意图;24.图7是根据本发明的范例实施例所示出的解码电路模块的示意图;25.图8是根据本发明的范例实施例所示出的由第一解码电路解码第一数据的示意图;26.图9是根据本发明的范例实施例所示出的由第二解码电路解码第二数据的示意图。具体实施方式27.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。28.一般而言,存储器存储装置(亦称,存储器存储系统)包括可复写式非易失性存储器模块(rewritablenon-volatilememorymodule)与控制器(亦称,控制电路)。存储器存储装置可与主机系统一起使用,以使主机系统可将数据写入至存储器存储装置或从存储器存储装置中读取数据。29.图1是根据本发明的范例实施例所示出的主机系统、存储器存储装置及输入/输出(i/o)装置的示意图。图2是根据本发明的范例实施例所示出的主机系统、存储器存储装置及i/o装置的示意图。30.请参照图1与图2,主机系统11可包括处理器111、随机存取存储器(randomaccessmemory,ram)112、只读存储器(readonlymemory,rom)113及数据传输接口114。处理器111、随机存取存储器112、只读存储器113及数据传输接口114可连接至系统总线(systembus)110。31.在一范例实施例中,主机系统11可通过数据传输接口114与存储器存储装置10连接。例如,主机系统11可经由数据传输接口114将数据存储至存储器存储装置10或从存储器存储装置10中读取数据。此外,主机系统11可通过系统总线110与i/o装置12连接。例如,主机系统11可经由系统总线110将输出信号传送至i/o装置12或从i/o装置12接收输入信号。32.在一范例实施例中,处理器111、随机存取存储器112、只读存储器113及数据传输接口114可设置在主机系统11的主机板20上。数据传输接口114的数目可以是一或多个。通过数据传输接口114,主机板20可以经由有线或无线方式连接至存储器存储装置10。33.在一范例实施例中,存储器存储装置10可例如是u盘201、存储卡202、固态硬盘(solidstatedrive,ssd)203或无线存储器存储装置204。无线存储器存储装置204可例如是近场通信(nearfieldcommunication,nfc)存储器存储装置、无线保真(wifi)存储器存储装置、蓝牙(bluetooth)存储器存储装置或低功耗蓝牙存储器存储装置(例如,ibeacon)等以各式无线通信技术为基础的存储器存储装置。此外,主机板20也可以通过系统总线110连接至全球定位系统(globalpositioningsystem,gps)模块205、网络接口卡206、无线传输装置207、键盘208、屏幕209、喇叭210等各式i/o装置。例如,在一范例实施例中,主机板20可通过无线传输装置207存取无线存储器存储装置204。34.在一范例实施例中,主机系统11为计算机系统。在一范例实施例中,主机系统11可为可实质地与存储器存储装置配合以存储数据的任意系统。在一范例实施例中,存储器存储装置10与主机系统11可分别包括图3的存储器存储装置30与主机系统31。35.图3是根据本发明的范例实施例所示出的主机系统与存储器存储装置的示意图。请参照图3,存储器存储装置30可与主机系统31搭配使用以存储数据。例如,主机系统31可以是数码相机、摄像机、通信装置、音频播放器、视频播放器或平板计算机等系统。例如,存储器存储装置30可为主机系统31所使用的安全数字(securedigital,sd)卡32、小型快闪(compactflash,cf)卡33或嵌入式存储装置34等各式非易失性存储器存储装置。嵌入式存储装置34包括嵌入式多媒体卡(embeddedmultimediacard,emmc)341和/或嵌入式多芯片封装(embeddedmultichippackage,emcp)存储装置342等各类型将存储器模块直接连接于主机系统的基板上的嵌入式存储装置。36.图4是根据本发明的范例实施例所示出的存储器存储装置的示意图。请参照图4,存储器存储装置10包括连接接口单元41、存储器控制电路单元42与可复写式非易失性存储器模块43。37.连接接口单元41用以将存储器存储装置10连接主机系统11。存储器存储装置10可经由连接接口单元41与主机系统11通信。在一范例实施例中,连接接口单元41是相容于高速周边零件连接接口(peripheralcomponentinterconnectexpress,pciexpress)标准。然而,必须了解的是,本发明不限于此,连接接口单元41亦可以是符合串行高级技术附件(serialadvancedtechnologyattachment,sata)标准、并行高级技术附件(paralleladvancedtechnologyattachment,pata)标准、电气和电子工程师协会(instituteofelectricalandelectronicengineers,ieee)1394标准、通用串行总线(universalserialbus,usb)标准、sd接口标准、超高速一代(ultrahighspeed-i,uhs-i)接口标准、超高速二代(ultrahighspeed-ii,uhs-ii)接口标准、存储棒(memorystick,ms)接口标准、mcp接口标准、mmc接口标准、emmc接口标准、通用快闪存储器(universalflashstorage,ufs)接口标准、emcp接口标准、cf接口标准、整合式驱动电子接口(integrateddeviceelectronics,ide)标准或其他适合的标准。连接接口单元41可与存储器控制电路单元42封装在一个芯片中,或者连接接口单元41是布设于一包含存储器控制电路单元42的芯片外。38.存储器控制电路单元42连接至连接接口单元41与可复写式非易失性存储器模块43。存储器控制电路单元42用以执行以硬件型式或固件型式实作的多个逻辑门或控制指令并且根据主机系统11的指令在可复写式非易失性存储器模块43中进行数据的写入、读取与抹除等运作。39.可复写式非易失性存储器模块43用以存储主机系统11所写入的数据。可复写式非易失性存储器模块43可包括单阶存储单元(singlelevelcell,slc)nand型快闪存储器模块(即,一个存储单元中可存储1个比特的快闪存储器模块)、二阶存储单元(multilevelcell,mlc)nand型快闪存储器模块(即,一个存储单元中可存储2个比特的快闪存储器模块)、三阶存储单元(triplelevelcell,tlc)nand型快闪存储器模块(即,一个存储单元中可存储3个比特的快闪存储器模块)、四阶存储单元(quadlevelcell,qlc)nand型快闪存储器模块(即,一个存储单元中可存储4个比特的快闪存储器模块)、其他快闪存储器模块或其他具有相同特性的存储器模块。40.可复写式非易失性存储器模块43中的每一个存储单元是以电压(以下亦称为临界电压)的改变来存储一或多个比特。具体来说,每一个存储单元的控制门(controlgate)与通道之间有一个电荷捕捉层。通过施予一写入电压至控制门,可以改变电荷补捉层的电子量,进而改变存储单元的临界电压。此改变存储单元的临界电压的操作亦称为“把数据写入至存储单元”或“程序化(programming)存储单元”。随着临界电压的改变,可复写式非易失性存储器模块43中的每一个存储单元具有多个存储状态。通过施予读取电压可以判断一个存储单元是属于哪一个存储状态,藉此取得此存储单元所存储的一或多个比特。41.在一范例实施例中,可复写式非易失性存储器模块43的存储单元可构成多个实体程序化单元,并且此些实体程序化单元可构成多个实体抹除单元。具体来说,同一条字线上的存储单元可组成一或多个实体程序化单元。若每一个存储单元可存储2个以上的比特,则同一条字线上的实体程序化单元可至少可被分类为下实体程序化单元与上实体程序化单元。例如,一存储单元的最低有效比特(leastsignificantbit,lsb)是属于下实体程序化单元,并且一存储单元的最高有效比特(mostsignificantbit,msb)是属于上实体程序化单元。一般来说,在mlcnand型快闪存储器中,下实体程序化单元的写入速度会大于上实体程序化单元的写入速度,和/或下实体程序化单元的可靠度是高于上实体程序化单元的可靠度。42.在一范例实施例中,实体程序化单元为程序化的最小单元。即,实体程序化单元为写入数据的最小单元。例如,实体程序化单元可为实体页(page)或是实体扇(sector)。若实体程序化单元为实体页,则此些实体程序化单元可包括数据比特区与冗余(redundancy)比特区。数据比特区包含多个实体扇,用以存储用户数据,而冗余比特区用以存储系统数据(例如,错误更正码等管理数据)。在一范例实施例中,数据比特区包含32个实体扇,且一个实体扇的大小为512字节(byte,b)。然而,在其他范例实施例中,数据比特区中也可包含8个、16个或数目更多或更少的实体扇,并且每一个实体扇的大小也可以是更大或更小。另一方面,实体抹除单元为抹除的最小单位。亦即,每一实体抹除单元含有最小数目的一并被抹除的存储单元。例如,实体抹除单元为实体区块(block)。43.图5是根据本发明的范例实施例所示出的存储器控制电路单元的示意图。请参照图5,存储器控制电路单元42包括存储器管理电路51、主机接口52、存储器接口53及解码电路模块54。44.存储器管理电路51用以控制存储器控制电路单元42的整体运作。具体来说,存储器管理电路51具有多个控制指令,并且在存储器存储装置10运作时,此些控制指令会被执行以进行数据的写入、读取与抹除等运作。以下说明存储器管理电路51的操作时,等同于说明存储器控制电路单元42的操作。45.在一范例实施例中,存储器管理电路51的控制指令是以固件型式来实作。例如,存储器管理电路51具有微处理器单元(未示出)与只读存储器(未示出),并且此些控制指令是被烧录至此只读存储器中。当存储器存储装置10运作时,此些控制指令会由微处理器单元来执行以进行数据的写入、读取与抹除等运作。46.在一范例实施例中,存储器管理电路51的控制指令亦可以程序码型式存储于可复写式非易失性存储器模块43的特定区域(例如,存储器模块中专用于存放系统数据的系统区)中。此外,存储器管理电路51具有微处理器单元(未示出)、只读存储器(未示出)及随机存取存储器(未示出)。特别是,此只读存储器具有开机码(bootcode),并且当存储器控制电路单元42被致能时,微处理器单元会先执行此开机码来将存储于可复写式非易失性存储器模块43中的控制指令载入至存储器管理电路51的随机存取存储器中。之后,微处理器单元会运转此些控制指令以进行数据的写入、读取与抹除等运作。47.在一范例实施例中,存储器管理电路51的控制指令亦可以一硬件型式来实作。例如,存储器管理电路51包括微控制器、存储单元管理电路、存储器写入电路、存储器读取电路、存储器抹除电路与数据处理电路。存储单元管理电路、存储器写入电路、存储器读取电路、存储器抹除电路与数据处理电路是连接至微控制器。存储单元管理电路用以管理可复写式非易失性存储器模块43的存储单元或存储单元群组。存储器写入电路用以对可复写式非易失性存储器模块43下达写入指令序列以将数据写入至可复写式非易失性存储器模块43中。存储器读取电路用以对可复写式非易失性存储器模块43下达读取指令序列以从可复写式非易失性存储器模块43中读取数据。存储器抹除电路用以对可复写式非易失性存储器模块43下达抹除指令序列以将数据从可复写式非易失性存储器模块43中抹除。数据处理电路用以处理欲写入至可复写式非易失性存储器模块43的数据以及从可复写式非易失性存储器模块43中读取的数据。写入指令序列、读取指令序列及抹除指令序列可各别包括一或多个程序码或指令码并且用以指示可复写式非易失性存储器模块43执行相对应的写入、读取及抹除等操作。在一范例实施例中,存储器管理电路51还可以下达其他类型的指令序列给可复写式非易失性存储器模块43以指示执行相对应的操作。48.主机接口52是连接至存储器管理电路51。存储器管理电路51可通过主机接口52与主机系统11通信。主机接口52可用以接收与识别主机系统11所传送的指令与数据。例如,主机系统11所传送的指令与数据可通过主机接口52来传送至存储器管理电路51。此外,存储器管理电路51可通过主机接口52将数据传送至主机系统11。在本范例实施例中,主机接口52是相容于pciexpress标准。然而,必须了解的是本发明不限于此,主机接口52亦可以是相容于sata标准、pata标准、ieee1394标准、usb标准、sd标准、uhs-i标准、uhs-ii标准、ms标准、mmc标准、emmc标准、ufs标准、cf标准、ide标准或其他适合的数据传输标准。49.存储器接口53是连接至存储器管理电路51并且用以存取可复写式非易失性存储器模块43。例如,存储器管理电路51可通过存储器接口53存取可复写式非易失性存储器模块43。也就是说,欲写入至可复写式非易失性存储器模块43的数据会经由存储器接口53转换为可复写式非易失性存储器模块43所能接受的格式。具体来说,若存储器管理电路51要存取可复写式非易失性存储器模块43,存储器接口53会传送对应的指令序列。例如,这些指令序列可包括指示写入数据的写入指令序列、指示读取数据的读取指令序列、指示抹除数据的抹除指令序列、以及用以指示各种存储器操作(例如,改变读取电压电平或执行垃圾回收操作等等)的相对应的指令序列。这些指令序列例如是由存储器管理电路51产生并且通过存储器接口53传送至可复写式非易失性存储器模块43。这些指令序列可包括一或多个信号,或是在总线上的数据。这些信号或数据可包括指令码或程序码。例如,在读取指令序列中,会包括读取的识别码、存储器地址等信息。50.解码电路模块(亦称为错误检查与校正电路)54是连接至存储器管理电路51并且用以执行错误检查与校正操作以确保数据的正确性。具体来说,当存储器管理电路51从主机系统11中接收到写入指令时,解码电路模块54会为对应此写入指令的数据产生对应的错误更正码(errorcorrectingcode,ecc)和/或错误检查码(errordetectingcode,edc),并且存储器管理电路51会将对应此写入指令的数据与对应的错误更正码和/或错误检查码写入至可复写式非易失性存储器模块43中。之后,当存储器管理电路51从可复写式非易失性存储器模块43中读取数据时会同时读取此数据对应的错误更正码和/或错误检查码,并且解码电路模块54会依据此错误更正码和/或错误检查码对所读取的数据执行错误检查与校正操作。51.在一范例实施例中,存储器控制电路单元42还包括缓冲存储器55与电源管理电路56。缓冲存储器55是连接至存储器管理电路51并且用以缓存数据。电源管理电路56是连接至存储器管理电路51并且用以控制存储器存储装置10的电源。52.在一范例实施例中,图4的可复写式非易失性存储器模块43可包括快闪存储器模块。在一范例实施例中,图4的存储器控制电路单元42可包括快闪存储器控制器。在一范例实施例中,图5的存储器管理电路51可包括快闪存储器管理电路。53.图6是根据本发明的范例实施例所示出的管理可复写式非易失性存储器模块的示意图。请参照图6,存储器管理电路51可将可复写式非易失性存储器模块43中的实体单元610(0)~610(b)逻辑地分组至存储区601与闲置(spare)区602。54.在一范例实施例中,一个实体单元是指一个实体地址或一个实体程序化单元。在一范例实施例中,一个实体单元亦可以是由多个连续或不连续的实体地址组成。在一范例实施例中,一个实体单元亦可以是指一个虚拟区块(vb)。一个虚拟区块可包括多个实体地址或多个实体程序化单元。55.存储区601中的实体单元610(0)~610(a)用以存储用户数据(例如来自图1的主机系统11的用户数据)。例如,存储区601中的实体单元610(0)~610(a)可存储有效(valid)数据与无效(invalid)数据。闲置区602中的实体单元610(a 1)~610(b)未存储数据(例如有效数据)。例如,若某一个实体单元未存储有效数据,则此实体单元可被关联(或加入)至闲置区602。此外,闲置区602中的实体单元(或未存储有效数据的实体单元)可被抹除。在写入新数据时,一或多个实体单元可被从闲置区602中提取以存储此新数据。在一范例实施例中,闲置区602亦称为闲置池(freepool)。56.存储器管理电路51可配置逻辑单元612(0)~612(c)以映射存储区601中的实体单元610(0)~610(a)。在一范例实施例中,每一个逻辑单元对应一个逻辑地址。例如,一个逻辑地址可包括一或多个逻辑区块地址(logicalblockaddress,lba)或其他的逻辑管理单元。在一范例实施例中,一个逻辑单元也可对应一个逻辑程序化单元或者由多个连续或不连续的逻辑地址组成。57.须注意的是,一个逻辑单元可被映射至一或多个实体单元。若某一实体单元当前有被某一逻辑单元映射,则表示此实体单元当前存储的数据包括有效数据。反之,若某一实体单元当前未被任一逻辑单元映射,则表示此实体单元当前存储的数据为无效数据。58.存储器管理电路51可将描述逻辑单元与实体单元之间的映射关系的管理数据(亦称为逻辑至实体映射信息)记录于至少一逻辑至实体映射表。当主机系统11欲从存储器存储装置10读取数据或写入数据至存储器存储装置10时,存储器管理电路51可根据此逻辑至实体映射表中的信息来存取可复写式非易失性存储器模块43。59.图7是根据本发明的范例实施例所示出的解码电路模块的示意图。请参照图7,解码电路模块54包括缓冲器(亦称为第一缓冲器或内部缓冲器)711、缓冲器(亦称为第二缓冲器或系统缓冲器)73、解码电路(亦称为第一解码电路)712及解码电路(亦称为第二解码电路)721。缓冲器711连接至可复写式非易失性存储器模块43与解码电路712。缓冲器73连接至缓冲器711、解码电路712及解码电路721。缓冲器711与73皆用以缓存(或缓存)数据。解码电路711与721皆用以解码从可复写式非易失性存储器模块43读取的数据。60.解码电路712的数据解码能力不同于解码电路721的数据解码能力。例如,解码电路721的数据解码能力可高于解码电路712的数据解码能力。例如,相较于解码电路712,解码电路721可更正数据中较多的错误比特。但是,相较于解码电路721,解码电路712可较快完成解码操作,无论解码成功与否。61.在一范例实施例中,解码电路721的电路复杂度可高于解码电路712的电路复杂度。在一范例实施例中,解码电路721所执行的解码操作的复杂度可高于解码电路712所执行的解码操作的复杂度。62.在一范例实施例中,解码电路712可用以实现比特翻转(bitflipping)算法。在一范例实施例中,解码电路721可用以实现总和-乘积(sum-product)算法与最小-总和(min-sum)算法的至少其中之一。须注意的是,解码电路712与721皆可用以实现其他类型的数据编/解码算法,本发明不加以限制。63.在一范例实施例中,缓冲器711专用以缓存从可复写式非易失性存储器模块43读取的数据,例如从可复写式非易失性存储器模块43读取且待解码的数据。特别是,缓冲器711可不属于图5的缓冲存储器55。在一范例实施例中,相较于缓冲器711,缓冲器73可视为缓冲存储器55的一部分。藉此,解码电路模块54可经由缓冲器73与图5的存储器控制电路单元42中的其他电路沟通。例如,解码电路模块54可将经解码的数据传送至缓冲器73中,以供存储器管理电路51存取或者经由主机接口52传送给图1的主机系统11。64.图8是根据本发明的范例实施例所示出的由第一解码电路解码第一数据的示意图。请参照图8,解码电路712可用以解码缓冲器711中的特定数据(亦称为第一数据)d1。例如,数据d1可从可复写式非易失性存储器模块43读取并存储于缓冲器711中。解码电路712可将经解码的数据d1传送至缓冲器73。65.图9是根据本发明的范例实施例所示出的由第二解码电路解码第二数据的示意图。请参照图9,解码电路721可用以解码缓冲器73中的特定数据(亦称为第二数据)d2。例如,数据d2可从可复写式非易失性存储器模块43读取并经由缓冲器711缓存后存储至缓冲器73中。解码电路721可将经解码的数据d2回传至缓冲器73。66.在一范例实施例中,响应于解码电路712对从某一实体单元(亦称为第一实体单元)读取的数据d1的解码失败,数据d2可从同一个实体单元(即第一实体单元)读取出来并由解码能力较强的解码电路721进行解码。特别是,在解码电路721解码数据d2的过程中,解码电路712可接续解码下一笔数据,而不需等待解码电路721解除忙碌状态。67.从另一角度而言,在图8与图9的范例实施例中,解码电路712与721所执行的解码操作彼此可不互相干涉和/或解码电路712与721所执行的解码操作可不需相互等待。例如,在解码电路712解码缓冲器711中的数据d1(如图8所示)时,解码电路721可同步解码缓冲器73中的数据d2(如图9所示)。藉此,即便解码电路721持续处于忙碌状态,解码电路712仍可同步执行对其他数据的解码。相较于传统上解码电路712需要等待解码电路721完成解码操作后才能处理新数据,解码电路712的工作效能可被提升。68.在一范例实施例中,解码电路模块54可包括电路模块(亦称为第一电路模块)71与电路模块(亦称为第二电路模块)72。解码电路712与缓冲器711可设置于电路模块71中。解码电路721可设置于电路模块72中。例如,电路模块71可设置于某一电路板(亦称为第一电路板)中,且电路模块72可设置于另一电路板(亦称为第二电路板)中。或者,电路模块71与72亦可设置于同一电路板中的不同区域。缓冲器73可连接至电路模块71与72。69.在一范例实施例中,缓冲器711中的数据仅供电路模块71中的电路(例如解码电路712)使用。在一范例实施例中,缓冲器73中的数据可供电路模块71与72中的电路(例如解码电路712与721)使用。70.在一范例实施例中,数据d1与d2皆可包括硬比特数据。硬比特数据是指使用单一个读取电压电平从可复写式非易失性存储器模块43中的单一存储单元读取的数据。在硬比特解码模式中,解码电路712可对缓冲器711中的硬比特数据进行解码和/或解码电路721可对缓冲器73中的硬比特数据进行解码。此外,在硬比特解码模式中,用来读取特定存储单元(或实体单元)的读取电压电平可被调整,以尝试降低读取到错误比特的机率。71.相较于硬比特数据,软比特数据是指使用多个读取电压电平重复读取可复写式非易失性存储器模块43中的单一存储单元所获得的数据。相较于硬比特数据,软比特数据可带有更多可辅助对此存储单元所存储的数据进行解码的信息。在软比特解码模式中,对应于数据d2的可靠度数据可根据软比特数据产生,且解码电路721可根据所述可靠度数据对数据d2进行解码,以提高数据d2的解码成功率。72.在一范例实施例中,解码电路模块54还包括处理电路(亦称为第一处理电路)722。处理电路722可连接至缓冲器73与解码电路721。例如,处理电路722可设置于电路模块72中。在图9的范例实施例中,处理电路722可用以产生对应于数据d2的可靠度数据。例如,所述可靠度信息可缓存于缓冲器73中或者不经由缓冲器73直接提供给解码电路721使用。解码电路721可根据所述可靠度数据来解码数据d2。例如,所述可靠度数据可包括对数相似性比值(log-likelihoodratio,llr)等可用以在解码过程中辅助判断数据d2中的特定比特应该被解码为比特“1”或“0”的辅助数据。73.在一范例实施例中,解码电路模块54还包括处理电路(亦称为第二处理电路)723。处理电路723可连接至缓冲器73与处理电路722。例如,处理电路723可设置于电路模块72中。在图9的范例实施例中,处理电路723可根据从可复写式非易失性存储器模块43读取的数据(亦称为第三数据)产生软比特数据。例如,所述软比特数据可缓存于缓冲器73中或者不经由缓冲器73直接提供给处理电路722使用。处理电路722可根据所述软比特数据产生对应于数据d2的可靠度数据。例如,处理电路722可根据所述软比特数据查询对数相似性比值映射表,以获得对应于数据d2的可靠度数据(例如llr数值)。然后,处理电路722可提供所述可靠度数据给解码电路721以解码数据d2。74.须注意的是,在图7至图9的范例实施例中,更多具有特定功能的电路可以被加入至电路模块71和/或72中,本发明不加以限制。此外,图7至图9的范例实施例中至少部分电路的连接关系也可以被调整,本发明不加以限制。75.综上所述,本发明的范例实施例通过特殊的电路布局,使解码电路模块中不同类型(例如具有不同解码能力)的解码电路皆可独立运作且运作上不须相互等待。藉此,可提升解码电路模块整体的工作效率。76.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。当前第1页12当前第1页12

再多了解一些

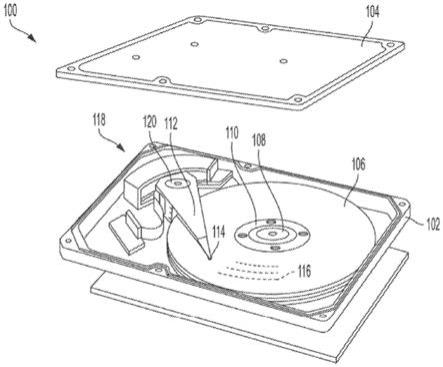

本文用于企业家、创业者技术爱好者查询,结果仅供参考。