1.本技术实施例涉及集成电路技术领域,具体涉及一种存储单元的抗老化方法、装置和相关设备。

背景技术:

2.bti(bias temperature instability,偏压温度不稳定性)效应是近年来严重影响存储单元可靠性的老化效应之一。bti效应是指在晶体管的栅极施加偏置电压时,晶体管的电学特性发生阈值电压漂移、饱和电流及跨导减小等退化,并且与温度呈正相关的效应。基于此,如何降低bti效应对存储单元的老化影响,已经成为本领域技术人员亟待解决的问题之一。

技术实现要素:

3.有鉴于此,本发明实施例提供一种存储单元的抗老化方法、装置和相关设备,以降低bti效应对存储单元的老化影响。

4.为解决上述问题,本发明实施例提供如下技术方案:

5.本发明第一方面提供了一种存储单元的抗老化方法,包括:

6.确定目标存储单元;

7.生成针对所述目标存储单元的交换指令;

8.根据所述交换指令,控制所述目标存储单元与其他存储单元进行存储数据的交换,以实现所述目标存储单元的抗老化。

9.本发明第二方面提供了一种存储单元的抗老化装置,包括:

10.老化确定模块,用于确定目标存储单元;

11.指令生成模块,用于生成针对所述目标存储单元的交换指令;

12.控制模块,用于根据所述交换指令,控制所述目标存储单元与其他存储单元进行存储数据的交换,以实现所述目标存储单元的抗老化。

13.本发明第三方面提供了一种计算机设备,包括:

14.存储器,存储至少一组指令;

15.处理器,执行所述至少一组指令执行如上任一项所述的存储单元的抗老化方法。

16.本发明第四方面提供了一种可读存储介质,所述可读存储介质存储至少一组指令,所述至少一组指令用于使处理器执行如上任一项所述的存储单元的抗老化方法。

17.本发明实施例提供的存储单元的抗老化方法、装置和相关设备,确定目标存储单元之后,生成针对目标存储单元的交换指令,并根据交换指令,控制目标存储单元与其他存储单元进行存储数据的交换,以通过不同存储单元之间存储数据的交换,实现目标存储单元存储数据的翻转,实现目标存储单元的抗老化。

附图说明

18.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

19.图1示例性的示出了一种存储器的存储阵列结构示意图;

20.图2示例性的示出了一种存储单元的结构示意图;

21.图3为本发明一个实施例提供的存储单元的抗老化方法的流程图;

22.图4为本发明一个实施例提供的目标存储阵列进行存储数据交换的流程图;

23.图5为本发明一个实施例提供的目标存储阵列和冗余存储阵列的结构示意图;

24.图6为本发明一个实施例提供的存储单元的抗老化装置的结构示意图;

25.图7为本发明一个实施例提供的目标存储阵列所在的存储器与抗老化装置的连接关系示意图。

具体实施方式

26.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的内容。

27.图1示例性的示出了一种存储器的存储阵列结构示意图,该存储阵列包括多个阵列排布的存储单元。每一行存储单元都与一条字线wl相连,每一列存储单元都与两条互补位线blt和blc相连。通过选中相应的字线和相应的位线,即可选中与该字线和该位线相连的一个存储单元,即可对该存储单元进行读写操作。例如,通过选中字线wl1和位线blt1和blc1,即可选中第一行第一列的存储单元,即可对该存储单元进行读写操作。

28.图2示例性的示出了一种存储单元的结构示意图,该存储单元包括nmos晶体管n1和n2、pmos晶体管p1和p2。其中,nmos晶体管n1和pmos晶体管p1构成一个反相器,nmos晶体管n2和pmos晶体管p2构成另一个反相器,这两个反相器背对背设置,构成对数据进行锁存的锁存结构。并且,通过字线wl可以控制nmos晶体管n3和n4的通断。在nmos晶体管n3和n4导通的状态下,可以通过互补位线blt和blc实现对锁存结构存储的数据的读写。

29.但是,对于长期存储同一数据的存储单元而言,由于存储单元中晶体管的偏置状态保持不变,因此,pmos晶体管p1和p2中,总会有一个pmos晶体管长期遭受nbti(negative bias temperature instability,负偏压温度不稳定性)效应,nmos晶体管n1和n2中,总会一个nmos晶体管长期遭受pbti(positive bias temperature instability,正偏压温度不稳定性)效应。其中,nbti效应和pbti效应都属于bti效应。

30.例如,若存储单元长期存储的数据为1,则q’=0,q=1,晶体管n1的栅极接vdd,晶体管n1的源极和漏极接地,晶体管n1长期遭受pbti效应,晶体管p2的栅极接地,晶体管p2的源极和漏极接vdd,晶体管p2长期遭受nbti效应。

31.由于bti效应会导致存储单元中的晶体管发生阈值电压漂移、饱和电流及跨导减小等老化现象,而老化后的存储单元的抗干扰能力较差,因此,会导致存储单元的存储数据

容易受其他存储单元读写操作的干扰而发生翻转,造成存储数据的丢失。由此可知,bti效应会严重影响存储单元乃至整个存储阵列的可靠性。

32.发明人研究发现,对晶体管的栅极施加适当的反向电压,可以修复bti效应造成的晶体管老化。其中,可以通过翻转存储单元存储的数据,如将存储数据即q节点的数据由1翻转为0,或由0翻转为1,来向存储单元中的晶体管的栅极施加反向电压。也就是说,相比于存储数据经常翻转的存储单元而言,存储数据长期不翻转的存储单元,受bti效应的影响更加严重。

33.基于此,本发明实施例提供了一种存储单元的抗老化方案,通过交换不同的存储单元的存储数据,实现存储单元中存储数据的翻转,实现存储单元中晶体管的栅极电压的翻转,以降低bti效应对存储单元的老化影响,实现存储单元的抗老化。

34.作为本发明实施例公开内容的一种可选实现,本发明实施例提供了一种存储单元的抗老化方法,应用于存储器件,用于降低bti效应对存储器件中的存储单元的老化影响。其中,该存储器件包括但并不仅限于静态随机存取存储器(sram)等。

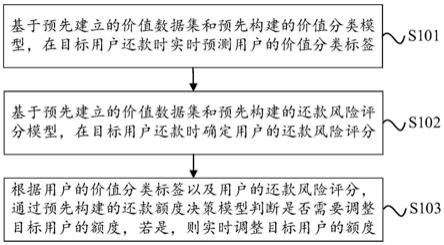

35.如图3所示,图3为本发明一个实施例提供的存储单元的抗老化方法的流程图,该抗老化方法包括:

36.s301:确定目标存储单元;

37.本发明实施例中,目标存储单元可以是存储器件中已经老化的存储单元,即可以是因存储数据长期不翻转导致晶体管长期遭受bti效应而出现老化的存储单元,也可以是尚未老化的存储单元。但是,无论是已经老化还是尚未老化的存储单元,都可以通过本发明中的抗老化方案,增加存储单元的存储数据的翻转次数,避免存储单元老化。

38.本发明一些可选示例中,可以根据芯片设计的读写策略,确定芯片中存储器中的目标存储单元。例如,若芯片设计的读写策略是经常对低位地址的存储单元进行读写操作,那么,高位地址的存储单元大概率会长期存储同一数据,即高位地址的存储单元老化的概率比较大,此时,可以将高位地址的存储单元确定为目标存储单元。若芯片设计的读写策略是经常对高位地址的存储单元进行读写操作,那么,低位地址的存储单元大概率会长期存储同一数据,即低位地址的存储单元老化的概率比较大,此时,可以将低位地址的存储单元确定为目标存储单元。

39.当然,本发明并不仅限于此,在另一些可选示例中,也可以在每隔一段时间之后,将存储器件中的至少部分存储单元确定为目标存储单元,无论存储单元是否老化,都对其实施抗老化方案。

40.s302:生成针对目标存储单元的交换指令;

41.确定目标存储单元之后,如确定存储数据长期不翻转的存储单元之后,即可确定目标存储单元的数据交换策略,进而根据交换策略生成交换指令。例如,可以确定令高位地址的存储单元与低位地址的存储单元进行存储数据交换的交换策略,可以确定令目标存储单元和与其不同行的存储单元进行存储数据交换的交换策略,并生成对应的不同行交换指令;也可以确定令目标存储单元和与其不同列的存储单元进行存储数据交换的交换策略,并生成对应的不同列交换指令;也可以确定令目标存储单元和其不同行的存储单元和不同列的存储单元都进行存储数据交换的交换策略,并生成对应的不同行交换指令和不同列交换指令。

42.s303:根据交换指令,控制目标存储单元与其他存储单元进行存储数据的交换,以实现目标存储单元的抗老化。

43.生成针对目标存储单元的交换指令之后,根据交换指令,控制目标存储单元与其他存储单元进行存储数据的交换。如根据不同行交换指令,控制目标存储单元和与其位于不同行的存储单元进行存储数据的交换,或者,控制目标存储单元所在行和其他行的存储单元进行存储数据的交换;根据不同列交换指令,控制目标存储单元和与其位于不同列的存储单元进行存储数据的交换,或者,控制目标存储单元所在列和其他列的存储单元进行存储数据的交换。

44.需要说明的是,若能够确定目标存储单元和与其交换的存储单元的存储数据相反,如一个存储数据为0、另一个存储数据为1,则令目标存储单元与一个存储单元进行存储数据的交换即可。但是,若不能确定目标存储单元和与其交换的存储单元的存储数据是否相反,则可以令目标存储单元与多个存储单元进行存储数据的交换。

45.由于存储单元中的存储数据不是0就是1,因此,多个存储单元中必然会存在与目标存储单元存储数据相反的存储单元,控制目标存储单元与多个存储单元进行存储数据的交换之后,必然存在与目标存储单元存储数据相反的存储单元和目标存储单元交换了存储数据,必然实现了目标存储单元存储数据的翻转,如从0翻转为1、从1翻转为0,从而必然实现了目标存储单元的晶体管的栅极电压的翻转,如晶体管的栅极电压由正向偏置翻转为负向偏置、负向偏置翻转为正向偏置,进而可以降低bti效应对目标存储单元的老化影响,实现目标存储单元的抗老化,减小因老化而导致的存储单元失配,提高存储器件的寿命。

46.需要说明的是,在目标存储单元交换存储数据之后,为了保证能够根据外部输入的指令正确地读写数据,本发明一些实施例中的存储单元的抗老化方法还包括:控制目标存储单元和与其进行存储数据交换的存储单元进行地址的交换。

47.例如,可以将目标存储单元和与其进行存储数据交换的存储单元进行物理地址或虚拟地址的交换。将物理地址或虚拟地址交换之后,虚拟地址与存储数据的实际存储单元的地址的对应关系发生了交换。若外部输入的读指令为读取目标存储单元的存储数据的指令,对指令进行解析获得目标存储单元的虚拟地址之后,由于虚拟地址与存储数据的实际存储单元的对应关系发生了交换,因此,该虚拟地址对应的是与目标存储单元进行存储数据交换的存储单元的地址,也就是说,根据解析后的虚拟地址能够从与目标存储单元进行存储数据交换的存储单元中,得到之前位于目标存储单元中的存储数据。

48.本发明一些实施例中,若存在多个目标存储单元,为了提高交换效率,则确定目标存储单元之后,还可以确定多个目标存储单元所在的目标存储阵列,该目标存储阵列中的存储单元阵列排布,并令目标存储阵列中的存储单元相互交换存储数据,实现目标存储阵列的抗老化。

49.需要说明的是,多个目标存储单元所在的目标存储阵列可以是多个目标存储单元所在存储器的整个存储阵列,也可以是所在存储器的部分存储阵列,在此不再赘述。其中,在对存储器的部分存储阵列进行存储数据交换,并不会影响存储器其他部分存储阵列的正常工作,并且,本发明中的抗老化方案不受掉电或上电的影响,因此,本发明中的抗老化方案的可行性较高,复杂度较低,尤其对面积不大的存储器而言,更有实现抗老化的价值。

50.还需要说明的是,若多个目标存储单元阵列排布,则目标存储阵列中的每个存储

单元都为目标存储单元;若多个目标存储单元非阵列排布,则目标存储阵列中部分存储单元为目标存储单元,则在对目标存储阵列中的存储单元进行存储数据的交换时,不仅对目标存储单元进行了抗老化,也对其他存储单元进行了抗老化。

51.本发明一些实施例中,可以通过对存储器件中的多个存储单元进行老化检测,来确定多个目标存储单元及其所在的存储阵列。也就是说,确定多个目标存储单元所在的目标存储阵列确定目标存储单元包括:对多个存储单元进行老化检测,确定多个老化的存储单元及其所在的存储阵列;将老化的存储单元所在的存储阵列,确定为目标存储单元阵列。其中,可以通过复制存储单元,并根据复制单元电流的变化侧面实现老化的检测,当然,也可以使用其他手段实现老化检测,在此不再赘述。

52.在确定多个目标存储单元所在的目标存储阵列之后,可以生成针对目标存储阵列的交换指令,并根据交换指令控制目标存储阵列中的存储单元相互交换存储数据。也就是说,本发明一些实施例中,生成针对目标存储单元的交换指令包括:生成针对目标存储阵列的交换指令;控制目标存储单元与其他存储单元进行存储数据的交换包括:控制目标存储阵列中所有的存储单元相互交换存储数据。

53.由于目标存储阵列中必然存在存储数据相反的两个存储单元,因此,控制目标存储阵列中所有的存储单元相互交换存储数据之后,必然会存在与目标存储单元存储数据相反的存储单元和目标存储单元交换了存储数据,而多个目标存储单元大概率会全部实现存储数据的翻转,进而可以降低bti效应对大部分目标存储单元的老化影响,实现大部分目标存储单元的抗老化。当然,在实际应用中,也可以通过控制目标存储阵列进行多次不同方式的存储数据的交换,来提高目标存储阵列存储数据的翻转概率。

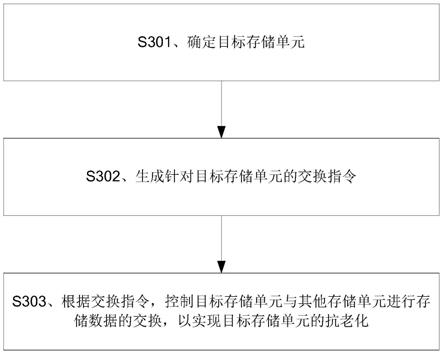

54.需要说明的是,可以通过控制目标存储阵列中的目标存储单元两两交换存储数据的交换方式,控制目标存储阵列中的存储单元相互交换存储数据;也可以将目标存储阵列分成多个子存储阵列,并通过控制目标存储阵列中的子存储阵列相互交换存储数据的交换方式,控制目标存储阵列中的存储单元相互交换存储数据;也可以通过控制目标存储阵列中任意两行目标存储单元交换存储数据的交换方式,控制目标存储阵列中的存储单元相互交换存储数据;也可以通过控制目标存储阵列中任意两列目标存储单元交换存储数据的交换方式,控制目标存储阵列中的存储单元相互交换存储数据;也可以通过上述交换方式中的至少两种交换方式,控制目标存储阵列中的存储单元相互交换存储数据,在此不再赘述。

55.本发明一些实施例中,控制目标存储阵列中所有的存储单元相互交换存储数据包括:控制目标存储阵列中的每一行存储单元都与其他行存储单元进行存储数据的交换。

56.在此基础上,若目标存储阵列包括m行存储单元,m为大于或等于2的自然数,则控制目标存储阵列中的每一行存储单元都与其他行存储单元进行存储数据的交换包括:控制第i行存储单元与第m-i 1行存储单元进行存储数据的交换,i为1至m/2之间的任一自然数。

57.也就是说,在控制目标存储阵列中的每一行存储单元都与其他行存储单元进行存储数据的交换时,可以控制第1行存储单元与第m行存储单元进行存储数据的交换,控制第2行存储单元与第m-1行存储单元进行存储数据的交换,控制第3行存储单元与第m-2行存储单元进行存储数据的交换,依次类推。基于此,只需遍历m/2行就可实现m行存储单元的存储数据的交换。

58.本发明一些实施例中,控制两行存储单元进行存储数据的交换时,可以将一行存

储单元的存储数据读出后缓存到暂存单元中,待将另一行的存储单元的存储数据写入该行存储单元之后,再将暂存单元的数据写入另一行存储单元,实现这两行存储数据的交换。

59.也就是说,本发明一些实施例中,如图4所示,图4为本发明一个实施例提供的目标存储阵列进行存储数据交换的流程图,其中,控制目标存储阵列中的每一行存储单元都与其他行存储单元进行存储数据的交换包括:

60.s401:读出目标存储阵列中的任一行存储单元的存储数据,并将任一行存储单元的存储数据保存到暂存单元中;

61.s402:读出要与任一行存储单元进行存储数据交换的其他行存储单元的存储数据,并将其他行存储单元的存储数据写入任一行存储单元中;

62.s403:将暂存单元中的任一行存储单元的存储数据写入其他行存储单元中。

63.以第1行存储单元和第m行存储单元进行存储数据的交换为例,将第1行存储单元的存储数据读出之后,将该存储数据缓存到暂存单元中,然后将第m行存储单元的存储数据读出并写入到第1行存储单元中,之后再将暂存单元中的存储数据写入第1行存储单元。当然,本发明并不仅限于此,也可以先将第m行存储单元的存储数据读出并写入到暂存单元中,在此不再赘述。

64.由于目标存储阵列中行与行之间的存储单元的数量是相同的,因此,两行存储单元进行存储数据的交换后,每行存储单元中的每个存储单元都进行了存储数据的交换。此外,还可以采用暂存单元实现两列存储单元的存储数据的交换以及两个存储单元的存储数据的交换,在此不再赘述。

65.需要说明的是,若m为偶数,则每一行存储单元都有对应的一行存储单元,但是,若m为奇数,则第(m 1)/2行存储单元没有对应的一行存储单元。基于此,若m为奇数,第(m 1)/2行存储单元可以与其他任一行存储单元进行存储数据的交换。

66.还需要说明的是,暂存单元可以是冗余存储单元、冗余存储阵列、由晶体管搭建的锁存结构以及其他有存储功能的结构。

67.本发明一些实施例中,暂存单元为冗余存储阵列,冗余存储阵列中的冗余存储单元阵列排布,且冗余存储阵列与目标存储阵列位于同一存储器件中。如图5所示,图5为本发明一个实施例提供的目标存储阵列和冗余存储阵列的结构示意图,其中,冗余存储阵列可以位于目标存储阵列的一侧或两侧,冗余存储阵列中的冗余存储单元用于替代目标存储阵列中错误或损坏的存储单元。

68.基于此,将任一行存储单元的存储数据保存到暂存单元中包括:将任一行存储单元的存储数据存储到一行冗余存储单元中。当然,本发明并不仅限于此,在另一些实施例中,也可以通过冗余存储阵列实现目标存储阵列中列与列存储单元存储数据的交换,即,可以将一列存储单元的存储数据存储到一列冗余存储单元中,实现存储数据的缓存。

69.此外,在上述任一实施例中,都可以采用存储器内建自测试(mbist)算法对多个目标存储单元所在的目标存储阵列进行存储数据的交换,即基于mbist算法生成对目标存储阵列进行存储数据交换的交换指令。

70.由于mbist算法是针对存储器中的存储阵列进行故障检测的算法,因此,本发明一些实施例中,基于mbist算法生成对目标存储阵列进行存储数据交换的交换指令,仅需要在执行mbist算法的mbist模块中增加少量的控制逻辑即可,从而不必在存储器中增加大量的

控制逻辑,进而不必增大存储器的整体面积。

71.当然,本发明实施例中的mbist模块还可以基于mbist算法生成针对目标存储阵列所在存储器件的故障检测指令,以根据故障检测指令对目标存储阵列中故障的存储单元进行检测。其中,mbist模块可以在不同的模式下生成不同的指令,如在测试(test)模式下,生成故障检测指令,在翻转(shift)模式下,生成交换指令。

72.本发明实施例中,在对目标存储单元或目标存储阵列进行存储数据交换之前,需保证目标存储单元或目标存储阵列并未进行读写等工作。也就是说,本发明实施例中对目标存储单元或目标存储阵列进行存储数据交换的方案,都是在目标存储单元或目标存储阵列空闲的时段进行的,以避免对存储数据的交换,影响目标存储单元或目标存储阵列的正常工作。

73.基于此,本发明一些实施例中,确定目标存储单元或确定目标存储阵列之后,还包括:确定是否具有使目标存储单元或目标存储阵列工作的使能信号;若否,执行生成针对目标存储单元或目标存储阵列的交换指令以及之后的步骤;若是,直接结束流程,不再执行任何抗老化的步骤。

74.在此基础上,为了避免存储数据交换的过程中接收到使能信号,本发明一些实施例中,生成针对目标存储单元或目标存储阵列的交换指令之前,还包括:对目标存储单元或目标存储阵列进行隔离处理,以隔离使目标存储单元或目标存储阵列工作的使能信号。

75.其中,可以把目标存储单元或目标存储阵列所在的存储器内部的读写使能信号全部拉低,使其在执行抗老化步骤时保持低电平,同时把读出的数据做隔离操作,使得存储数据交换期间读出的数据不能真正读出去。

76.需要说明的是,在对目标存储单元或目标存储阵列进行存储数据和地址的交换后,需及时释放该目标存储单元或目标存储阵列,恢复该目标存储单元或目标存储阵列的使能信号以及读出的数据,使该目标存储单元或目标存储阵列恢复正常工作。

77.作为本发明实施例公开内容的另一种可选实现,本发明实施例提供了一种存储单元的抗老化装置,应用于存储器件,用于降低bti效应对存储器件中的存储单元的老化影响。其中,该存储器件包括但并不仅限于静态随机存取存储器(sram)等。

78.如图6所示,图6为本发明一个实施例提供的存储单元的抗老化装置的结构示意图,该抗老化装置包括:

79.老化确定模块61,用于确定目标存储单元;

80.指令生成模块62,用于生成针对目标存储单元的交换指令;

81.控制模块63,用于根据交换指令,控制目标存储单元与其他存储单元进行存储数据的交换,以实现目标存储单元的抗老化。

82.本发明实施例中,老化确定模块61确定目标存储单元之后,指令生成模块62生成针对目标存储单元的交换指令,控制模块63根据交换指令,控制目标存储单元与其他存储单元进行存储数据的交换,以通过不同存储单元之间存储数据的交换,实现目标存储单元存储数据的翻转,实现目标存储单元的抗老化。

83.本发明一些实施例中,老化确定模块61确定目标存储单元之后,还用于确定多个目标存储单元所在的目标存储阵列,目标存储阵列中的存储单元阵列排布;指令生成模块62生成针对目标存储单元的交换指令包括:生成针对目标存储阵列的交换指令;控制模块

63控制目标存储单元与其他存储单元进行存储数据的交换包括:控制目标存储阵列中所有的存储单元相互交换存储数据。

84.如图7所示,图7为本发明一个实施例提供的目标存储阵列所在的存储器与老化装置的连接关系示意图,目标存储阵列所在的存储器的电路结构包括存储阵列、地址译码器、灵敏放大器、控制电路、输入输出端口等。其中,控制模块63还具有除交换存储数据之外的其他功能,如控制存储单元进行读写操作等,在此不再赘述。

85.其中,cpu等通过地址信号选中存储阵列,对存储阵列进行数据的读写。读出的数据以及写入的数据通过输入输出端口以及灵敏放大器进出存储阵列。地址译码器对外部输入的指令中的地址进行译码,如根据交换指令等指令中的虚拟地址确定物理地址,然后根据物理地址找到对应的存储单元。

86.本发明一些实施例中,指令生成模块62还用于基于存储器内建自测试算法生成针对目标存储阵列的交换指令,以及基于存储器内建自测试算法生成针对目标存储阵列所在存储器件的故障检测指令,以根据故障检测指令对目标存储阵列中故障的存储单元进行检测。其中,指令生成模块62即为mbsit模块。

87.本发明一些实施例中,控制模块63还用于控制目标存储单元和与其进行存储数据交换的存储单元进行地址的交换。

88.本发明一些实施例中,控制模块63控制目标存储阵列中所有的存储单元相互交换存储数据包括:

89.控制目标存储阵列中的每一行存储单元都与其他行存储单元进行存储数据的交换。

90.在上述实施例的基础上,本发明一些实施例中,目标存储阵列包括m行存储单元,m为大于或等于2的自然数,则控制模块63控制目标存储阵列中的每一行存储单元都与其他行存储单元进行存储数据的交换包括:

91.控制第i行存储单元与第m-i 1行存储单元进行存储数据的交换,i为1至m/2之间的任一自然数;

92.并且,若m为奇数,第(m 1)/2行存储单元与其他任一行存储单元进行存储数据的交换。

93.本发明一些实施例中,控制模块63控制目标存储阵列中的每一行存储单元都与其他行存储单元进行存储数据的交换包括:

94.读出目标存储阵列中的任一行存储单元的存储数据,并将任一行存储单元的存储数据保存到暂存单元中;

95.读出要与任一行存储单元进行存储数据交换的其他行存储单元的存储数据,并将其他行存储单元的存储数据写入任一行存储单元中;

96.将暂存单元中的任一行存储单元的存储数据写入其他行存储单元中。

97.在上述实施例的基础上,本发明一些实施例中,暂存单元包括冗余存储阵列,冗余存储阵列中的冗余存储单元阵列排布,且冗余存储阵列与目标存储阵列位于同一存储器件中;

98.将任一行存储单元的存储数据保存到暂存单元中包括:将任一行存储单元的存储数据存储到一行冗余存储单元中。

99.本发明一些实施例中,控制模块63还用于控制目标存储单元和与其进行存储数据交换的存储单元进行地址的交换。

100.本发明一些实施例中,老化确定模块61确定多个目标存储单元所在的目标存储阵列包括:

101.对多个存储单元进行老化检测,确定多个老化的存储单元及其所在的存储阵列;

102.将老化的存储单元所在的存储阵列,确定为目标存储阵列。

103.本发明一些实施例中,老化确定模块61确定目标存储单元或确定目标存储阵列之后,控制模块63还用于确定是否具有使目标存储单元或目标存储阵列工作的使能信号;若否,执行生成针对目标存储单元或目标存储阵列的交换指令以及之后的步骤。

104.本发明一些实施例中,指令生成模块62生成针对目标存储单元或目标存储阵列的交换指令之前,控制模块63还用于对目标存储单元或目标存储阵列进行隔离处理,以隔离使目标存储单元或目标存储阵列工作的使能信号。

105.图7所示的虚线框内的区域即为需要隔离的区域,在数据交换的过程中,通过使得使能信号为低电平,对需要隔离的区域做隔离处理,使得没有写入数据和读出数据,没有新的外部输入的地址信号,仅有电源信号和时钟信号,存储器的工作状态为待机状态。

106.作为本发明实施例公开内容的另一种可选实现,本发明实施例提供了一种计算机设备,包括:存储器,存储至少一组指令;处理器,执行至少一组指令执行如任一实施例提供的存储单元的抗老化方法。

107.作为本发明实施例公开内容的另一种可选实现,本发明实施例提供了一种可读存储介质,可读存储介质存储至少一组指令,至少一组指令用于使处理器执行如上任一实施例提供的存储单元的抗老化方法。

108.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

109.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。