1.本实用新型涉及一种高压集成电路及半导体电路,属于半导体电路应用技术领域。

背景技术:

2.半导体电路是一种将电力电子和集成电路技术结合的功率驱动类产品。高压集成电路,即hvic,是半导体电路中的主要组成部分。hcic是一种把mcu信号转换成驱动igbt信号的集成电路产品。hvic把pmos管、nmos管、三极管、二极管、稳压管、电阻、电容集成在一起,形成斯密特、低压levelshift、高压levelshift、脉冲发生电路、死区电路、互锁电路、延时电路、滤波电路、过电流保护电路和过热保护电路、欠压保护电路等电路。hvic一方面接收mcu的控制信号,驱动后续igbt或mos工作,另一方面将系统的状态检测信号送回mcu。是ipm内部的关键芯片。

3.在实现过程中,发明人发现传统技术中至少存在如下问题:hvic通常在低压和高压之间的隔离由结终端进行横向耐压,由高压岛与低压衬底进行纵向耐压。目前,hvic中,在高压岛和低压区(包括低压衬底)之间的esd能力完全靠结终端以及高压岛与衬底形成的pn结来释放,当高esd电压形成大电流,容易使高压区和低压区之间的结终端或pn结击穿。

技术实现要素:

4.基于此,有必要针对传统的设计、制备及应用高压集成电路过程中,hvic在高压岛和低压区(包括低压衬底)之间的esd能力完全靠结终端以及高压岛与衬底形成的pn结来释放,当高esd电压形成大电流,容易使高压区和低压区之间的结终端或pn结击穿的问题。提供一种高压集成电路及半导体电路。

5.具体地,本实用新型公开一种高压集成电路,包括:

6.p型衬底,p型衬底上设置有n外延层,n外延层包括n型高压区;n型高压区内设置有第一n 区;p型衬底内设置有第二n 区和p 区,第二n 区与p 区电性相连,且第二n 区用于连接地线;

7.hvjt终结端,hvjt终结端设置在n外延层上;

8.hvnmos管,hvnmos管包括多晶硅栅、漏区、源区和体区;多晶硅栅设置在hvjt终结端的外侧,且与hvjt终结端电性连接;第一n 区形成漏区,第二n 区形成源区,p 区形成体区。

9.可选地,第一n 区靠近hvjt终结端的内侧设置,hvjt终结端的内侧与hvjt终结端的外侧相对。

10.可选地,n外延层还包括n外延区;n外延区上设置有p-top区,p-top区上设置有从hvjt终结端的内侧至hvjt终结端的外侧排列的多个多晶硅场板;

11.多个多晶硅场板、p-top区和n外延区组成hvjt终结端。

12.可选地,多个多晶硅场板的电位从hvjt终结端的内侧与hvjt终结端的外侧依次降

低;多晶硅栅与靠近hvjt终结端的外侧的多晶硅场板电性连接。

13.本实用新型还公开一种高压集成电路,包括:

14.p型衬底,p型衬底上设置有n外延层,n外延层包括n型高压区;n型高压区内设置有n 区和第一p 区,且n 区与第一p 区电性相连;p型衬底内设置有第二p 区和第三p 区,第二p 区和第三p 区电性相连,且第三p 区用于连接地线;

15.hvjt终结端,hvjt终结端设置在n外延层上;

16.hvpmos管,hvpmos管包括多晶硅栅、漏区、源区和体区;多晶硅栅设置在hvjt终结端的内侧,且与hvjt终结端电性连接;第二p 区形成漏区,第一p 区形成源区,n 区形成体区。

17.可选地,第二p 区靠近hvjt终结端的外侧设置,hvjt终结端的外侧与hvjt终结端的内侧相对。

18.可选地,n外延层还包括n外延区;n外延区上设置有p-top区,p-top区上设置有从hvjt终结端的内侧与hvjt终结端的外侧排列的多个多晶硅场板;

19.多个多晶硅场板、p-top区和n外延区组成hvjt终结端。

20.可选地,多个多晶硅场板的电位从hvjt终结端的内侧与hvjt终结端的外侧依次降低;多晶硅栅与靠近hvjt终结端的内侧的多晶硅场板电性连接。

21.本实用新型还公开一种半导体电路,包括:

22.电路基板,电路基板上设有绝缘层;

23.电路层,电路层设置在绝缘层上;

24.多个引脚,多个引脚的第一端分别与电路层电性连接;

25.密封本体,密封本体包裹电路基板、以及连接有各引脚的电路层;

26.其中,各引脚的第二端分别从密封本体的第一侧面引出;电路层包括桥臂模块,以及上述任意一项的高压集成电路;桥臂模块耦合连接高压集成电路。

27.上述技术方案中的一个技术方案具有如下优点和有益效果:

28.上述的高压集成电路的实施例中,通过在p型衬底上设置有n外延层,n外延层包括n型高压区;n型高压区内设置有第一n 区;p型衬底内设置有第二n 区和p 区,且第二n 区与p 区电性相连;hvjt终结端设置在n外延层上;hvnmos管包括多晶硅栅、漏区、源区和体区;多晶硅栅设置在hvjt终结端的外侧,且与hvjt终结端电性连接;第一n 区形成漏区,第二n 区形成源区,p 区形成体区。当hvjt终结端处的静电电流达到阈值时,会向hvnmos管的多晶硅栅输出一定电平,当该电平高于hvnmos管的阈值电压时,hvnmos管开始导通,静电电流从hvnmos管释放到地,从而明显提高了hvic在高压岛和低压区(包括低压衬底)之间的esd(静电放电)能力,避免了静电加载到高压端口和低压端口之间而造成hvjt终结端的击穿。

附图说明

29.图1为传统的高压集成电路的等效电路应用示意图;

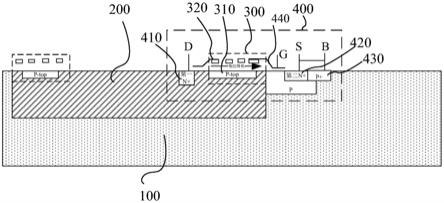

30.图2为本实用新型实施例的高压集成电路的第一结构示意图;

31.图3为本实用新型实施例的高压集成电路的第一等效电路示意图;

32.图4为本实用新型实施例的高压集成电路的第一等效电路应用示意图;

33.图5为本实用新型实施例的高压集成电路的第二结构示意图;

34.图6为本实用新型实施例的高压集成电路的第二等效电路示意图;

35.图7为本实用新型实施例的高压集成电路的第二等效电路应用示意图。

36.附图标记:

37.p型衬底100,n外延层200,hvjt终结端300,p-top区310,多晶硅场板320,hvnmos管400,第一n 区410,第二n 区420,p 区430,多晶硅栅440,hvpmos管500,n 区510,第一p 区520,第二p 区530,第三p 区540。

具体实施方式

38.为了使本技术领域的人员更好地理解本技术方案,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分的实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本技术保护的范围。

39.需要说明的是,在结构或功能不冲突的情况下,本实用新型中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本实用新型。

40.传统的hvic一般低压和高压的隔离由结终端进行横向耐压,由高压岛与低压衬底进行纵向耐压。目前传统的hvic的高压岛和低压区(包括低压衬底)之间没有esd结构,因此高压跟低压之间的esd能力完全靠结终端以及高压岛与衬底形成的pn结来释放。目前的hvic高压跟低压之间的esd能力比较难释放,高esd电压形成大电流,容易使高压区和低压区之间的hvjt结终端或pn结击穿,例如,目前很多高压bcd工艺高低压之间都无法承受2000v以上电压。如图1中,传统的hvic中,全部静电放电电流只能通过hvjt终结端反向释放,容易使高压区和低压区之间的hvjt结终端或pn结击穿。

41.本实用新型提到的高压集成电路,即hvic,是把pmos管、nmos管、三极管、二极管、稳压管、电阻、电容集成在一起,形成斯密特电路、低压levelshift(电平位移)电路、高压levelshift(电平位移)电路、脉冲发生电路、死区及互锁电路、延时电路、滤波电路、过电流保护电路和过热保护电路、欠压保护电路等的电路。在本实用新型的以下实施例中,统一称为hvic。

42.本实用新型提到的半导体电路,是一种将功率开关器件和高压驱动电路等集成在一起,并在外表进行密封封装的一种电路模块,在电力电子领域应用广泛,如驱动电机的变频器、各种逆变电压、变频调速、冶金机械、电力牵引、变频家电等领域应用。这里的半导体电路还有多种其他的名称,如模块化智能功率系统(modular intelligent power system,mips)、智能功率模块(intelligent power module,ipm),或者称为混合集成电路、功率半导体模块、功率模块等名称。在本实用新型的以下实施例中,统一称为半导体电路。

43.在一个实施例中,如图2所示,本实用新型提出一种高压集成电路,该高压集成电路包括p型衬底100、hvjt终结端300和hvnmos管400。p型衬底100上设置有n外延层200,n外延层200包括n型高压区;n型高压区内设置有第一n 区410;p型衬底100内设置有第二n 区420和p 区430,第二n 区420与p 区430电性相连,且第二n 区420用于连接地线;hvjt终结端300设置在n外延层200上;hvnmos管400包括多晶硅栅440、漏区、源区和体区;多晶硅栅

440设置在hvjt终结端300的外侧,且与hvjt终结端300电性连接;第一n 区410形成漏区,第二n 区420形成源区,p 区430形成体区。

44.其中,p型衬底100指的是用来形成高压集成电路有源区的半导体部,p型衬底100可由适合于高压集成电路的任何半导体材料(例如硅、碳化硅、锗化硅等)制成,例如p型衬底100可以是硅衬底。p型衬底100也可以是绝缘体上硅(soi)、绝缘体上锗硅等各种复合衬底。hvjt终结端300指的是高压终结端,hvjt终结端300具有围绕并界定高压侧区的环形顶部布局。此外,hvjt器件将高压侧区与低压区分离并且具有高压金属氧化物半导体器件,如本实施例中的hvnmos管400。p型衬底100上设置有n外延层200,在一个示例中,n外延层200从p型衬底100的上表面向下延伸形成,且n外延层200的厚度小于p型衬底100的厚度。n外延层200的掺杂浓度小于p型衬底100的掺杂浓度。n外延层200可用半导体材料制成,例如,n外延层200可以是碳化硅n外延层200。hvnmos管400指的是高压功率n型mos管。hvnmos管400包括漏极(d极)、源极(s极)、栅极(g极)和体极(b极)。其中,hvnmos管400的d极对应hvnmos管400的漏区;hvnmos管400的s极对应hvnmos管400的源区;hvnmos管400的g极对应hvnmos管400的多晶硅栅440;hvnmos管400的b极对应hvnmos管400的体区。

45.具体地,在p型衬底100上设置n外延层200,n外延层200从p型衬底100的上表面向下延伸得到;n外延层200上设置有hvjt终结端300。n外延层200划分有n型高压区,在n型高压区内设置有第一n 区410,例如第一n 区410的掺杂浓度为1e15cm-2。p型衬底100内设置有第二n 区420和p 区430,例如可在p型衬底100内设置第二n 区420,其中第二n 区420的掺杂浓度可以是1e15cm-2;然后在第二n 区420的一侧设置p 区430,p 区430的掺杂浓度可以是1e15cm-2。即第一n 区410的掺杂浓度、第二n 区420的掺杂浓度和p 区430的掺杂浓度可相等。其中,第二n 区420与p 区430电性相连,且第二n 区420连接地线,使得第二n 区420与p 区430相连接地。

46.hvjt终结端300可包括多个多晶硅场板320,多个多晶硅场板320的电位从高压区向低压区逐级降低。hvnmos管400的多晶硅栅440设置在hvjt终结端300的外侧,即hvnmos管400的多晶硅栅440靠近hvjt终结端300的低压区设置,且与hvjt终结端300的多晶硅场板320电性连接。上述设置得到的第一n 区410形成hvnmos管400的漏区,第二n 区420形成hvnmos管400的源区,p 区430形成hvnmos管400的体区。

47.上述的实施例中,通过在p型衬底100上设置有n外延层200,n外延层200包括n型高压区;n型高压区内设置有第一n 区410;p型衬底100内设置有第二n 区420和p 区430,且第二n 区420与p 区430电性相连;hvjt终结端300设置在n外延层200上;hvnmos管400包括多晶硅栅440、漏区、源区和体区;多晶硅栅440设置在hvjt终结端300的外侧,且与hvjt终结端300电性连接;第一n 区410形成漏区,第二n 区420形成源区,p 区430形成体区。当hvjt终结端300处的静电电流达到阈值时,会向hvnmos管400的多晶硅栅440输出一定电平,当该电平高于hvnmos管400的阈值电压时,hvnmos管400开始导通,静电电流从hvnmos管400释放到地,从而明显提高了hvic在高压岛和低压区(包括低压衬底)之间的esd(静电放电)能力,避免了静电加载到高压端口和低压端口之间而造成hvjt终结端300的击穿。

48.在一个示例中,第一n 区410靠近hvjt终结端300的内侧设置,hvjt终结端300的内侧与hvjt终结端300的外侧相对。

49.其中,hvjt终结端300的内侧指的是靠近多晶硅场板320的高压区的一侧。hvjt终

结端300的外侧指的是靠近多晶硅场板320的低压区的一侧。

50.示例性的,通过将第一n 区410靠近hvjt终结端300的内侧设置,将hvnmos管400的多晶硅栅440设置在hvjt终结端300的外侧,将第二n 区420设置在p型衬底100上,且第二n 区420靠近多晶硅栅440;p 区430紧贴第二n 区420设置,进而第一n 区410形成hvnmos管400的漏区,第二n 区420形成hvnmos管400的源区,p 区430形成hvnmos管400的体区。当hvjt终结端300处的静电电流达到阈值时,会向hvnmos管400的多晶硅栅440输出一定电平,当该电平高于hvnmos管400的阈值电压时,hvnmos管400开始导通,静电电流从hvnmos管400释放到地,从而明显提高了hvic在高压岛和低压区(包括低压衬底)之间的esd(静电放电)能力,避免了静电加载到高压端口和低压端口之间而造成hvjt终结端300的击穿。

51.在一个示例中,n外延层200还包括n外延区;n外延区上设置有p-top区310,p-top区310上设置有从hvjt终结端300的内侧至hvjt终结端300的外侧排列的多个多晶硅场板320;多个多晶硅场板320、p-top区310和n外延区组成hvjt终结端300。

52.其中,n外延层200还划分有n外延区,n外延区可用半导体材料制成,例如,n外延区可以是碳化硅n外延区。n外延区上设置有p-top区310,在一个示例中,p-top区310可由n外延区的上表面向下延伸得到,其中p-top区310的厚度小于n外延区的厚度。在p-top区310上设置有多个多晶硅场板320,其中多个多晶硅场板320从hvjt终结端300的内侧至hvjt终结端300的外侧排列,使得多个多晶硅场板320的电位从高压区向低压区逐级降低,即多个多晶硅场板320的电位从hvjt终结端300的内侧与hvjt终结端300的外侧依次降低,且多晶硅栅440与靠近hvjt终结端300的外侧的多晶硅场板320电性连接。示例性的,p-top区310的掺杂浓度大于n外延区的掺杂浓度。

53.示例性的,hvjt结终端由多个多晶硅场板320、p-top区310、n外延区组成,多个多晶硅场板320的电位从高压区向低压区逐级降低。p-top区310的掺杂浓度大于n外延区的掺杂浓度。在n型高压区制作了第一n 区410,参杂浓度为1e15cm-2;在p型衬底100上采用双扩散工艺制作了第二n 区420和p区,n 参杂浓度为1e15cm-2,p区参杂浓度为1e13cm-2。需要说明的是,双扩散工艺是在相同的源/漏区域注入两次,一次注入浓度较大(例如,典型注入剂量1e15cm-2)的砷(as);另一次注入浓度较小(例如,典型注入剂量1e13cm-2)的硼(b)。注入之后再进行一个高温推进过程,由于硼扩散比砷快,所以在栅极边界下会沿着横向扩散更远(图中p区),形成一个有浓度梯度的沟道,它的沟道长度由这两次横向扩散的距离之差决定。双扩散后再在第二n 区420旁边再制作p 区430,其中p 区430的参杂浓度为1e15cm-2。n型高压区内的第一n 区410形成hvnmos管400的漏区(d),多晶硅栅440(g)在hvjt终结端300的外侧,第二n 区420形成hvnmos管400的源区(s),p 区430形成hvnmos管400的体区(b)。第一n 漏区(d)、第二n 源区(s)、p 体区(b)表面淀积金属铝形成欧姆接触,多晶硅栅440(g)通过通孔连接到金属层;源区通过金属层连接到体区,进而在hvjt结终端侧形成hvnmos管400,从而当hvjt终结端300处的静电电流达到阈值时,会向hvnmos管400的多晶硅栅440输出一定电平,当该电平高于hvnmos管400的阈值电压时,hvnmos管400开始导通,静电电流从hvnmos管400释放到地,明显提高了hvic在高压岛和低压区(包括低压衬底)之间的esd(静电放电)能力,避免了静电加载到高压端口和低压端口之间而造成hvjt终结端300的击穿。需要说明的是,可使用双扩散工艺制作hvnmos管400,调整注入浓度。可采用double resurf工艺制作hvjt结构,调整p-top区310的掺杂浓度。

54.在一个示例中,如图3所示,为对应图2中的高压集成电路的第一等效电路示意图。其中hvjt终结端300是一个高压的pn结,将hvjt终结端300等效为反向二极管来表征它的特性。hvnmos管400并联到hvjt终结端300的两端,hvnmos管400的漏极(d)与hvjt终结端300的阴极(c)相连接,hvnmos管400的源极(s)与hvjt终结端300的阳极(a)相连接。hvnmos管400的栅极(g)连接到分压电阻r1、r2中间,hvnmos管400的体极(b)与hvnmos管400的源极(s)连接并接到地。当静电电流达到某个值时,分压电阻(r1、r2)向hvnmos管400的栅极(g)输出一定电平,电平高于hvnmos管400的阈值电压时,hvnmos管400开始导通,静电电流从hvnmos管400释放到地,从而明显提高了hvic在高压岛和低压区(包括低压衬底)之间的esd(静电放电)能力,避免了静电加载到高压端口和低压端口之间而造成hvjt终结端300的击穿。

55.需要说明的是,在一个示例中,通过设计r1和r2电阻的分压比例,使静电电流约800a的时候达到hvnmos管400的阈值电压,使hvnmos管400开启。

56.在一个示例中,如图1中,传统的高压集成电路的等效电路应用示意图。传统的无静电释放电路时,全部静电放电电流只能通过hvjt终结端反向释放,由于hvjt终结端反向击穿电压有600v以上,而释放能量等于释放电压释放电流,在半导体电路里面释放能量是转换成热量耗散的,同样面积的半导体电路能耗散的能量是一定的,因此释放能量一定的情况下,释放电压越高,可以释放的电流就越小,也就是静电等级越低。而采用本技术高压集成电路的hvnmos管400来释放的时,如图4所示,hvnmos管400的导通电压很低,只有几伏,约为hvjt终结端300反向击穿电压的1/100,因此hvnmos管400的释放电流是hvjt终结端300的100倍。图4中,由于hvnmos管400导通电阻小,因此大部分电流通过hvnmos管400来流通,只有很小部分电路通过电阻和hvjt终结端300流通,因此大大提高了静电的释放能力。

57.示例性的,该高压集成电路的验证过程为:对hvjt终结端300的结构、hvnmos管400结构和掺杂浓度进行拉偏,在保证hvjt终结端300耐压能达到650v以上情况下,选择静电释放能力较好同时耐压较好的方案。进行125℃以上温度的高温反偏试验,测试高温下hvjt终结端300的高温漏电流,不允许出现漏电流明显增大现象。

58.在一个实施例中,如图5所示还提供一种高压集成电路,该高压集成电路包括p型衬底100、hvjt终结端300和hvpmos管500。p型衬底100上设置有n外延层200,n外延层200包括n型高压区;n型高压区内设置有n 区510和第一p 区520,且n 区510与第一p 区520电性相连;p型衬底100内设置有第二p 区530和第三p 区540,第二p 区530和第三p 区540电性相连,且第三p 区540用于连接地线;hvjt终结端300设置在n外延层200上;hvpmos管500包括多晶硅栅、漏区、源区和体区;多晶硅栅设置在hvjt终结端300的内侧,且与hvjt终结端300电性连接;第二p 区530形成漏区,第一p 区520形成源区,n 区510形成体区。

59.其中,p型衬底100指的是用来形成高压集成电路有源区的半导体部,p型衬底100可由适合于高压集成电路的任何半导体材料(例如硅、碳化硅、锗化硅等)制成,例如p型衬底100可以是硅衬底。p型衬底100也可以是绝缘体上硅(soi)、绝缘体上锗硅等各种复合衬底。hvjt终结端300指的是高压终结端,hvjt终结端300具有围绕并界定高压侧区的环形顶部布局。此外,hvjt器件将高压侧区与低压区分离并且具有高压金属氧化物半导体器件,如本实施例中的hvpmos管500。p型衬底100上设置有n外延层200,在一个示例中,n外延层200从p型衬底100的上表面向下延伸形成,且n外延层200的厚度小于p型衬底100的厚度。n外延层200的掺杂浓度小于p型衬底100的掺杂浓度。n外延层200可用半导体材料制成,例如,n外

延层200可以是碳化硅n外延层200。hvpmos管500指的是高压功率p型mos管。hvpmos管500包括漏极(d极)、源极(s极)、栅极(g极)和体极(b极)。其中,hvpmos管500的d极对应hvpmos管500的漏区;hvpmos管500的s极对应hvpmos管500的源区;hvpmos管500的g极对应hvpmos管500的多晶硅栅;hvpmos管500的b极对应hvnmos管的体区。

60.具体地,在p型衬底100上设置n外延层200,n外延层200从p型衬底100的上表面向下延伸得到;n外延层200上设置有hvjt终结端300。n外延层200划分有n型高压区,在n型高压区内设置有n 区510和第一p 区520,例如可在n型高压区内设置n 区510,其中n 区的掺杂浓度可以是1e15cm-2;然后在n 区510的一侧设置第一p 区520,第一p 区520的掺杂浓度可以是1e15cm-2。在p型衬底100内设置有第二p 区530和第三p 区540,例如n 区510的掺杂浓度为1e15cm-2,即n 区510的掺杂浓度、第一p 区520的掺杂浓度和第二p 区530的掺杂浓度可相等。其中,n 区510与第一p 区520电性相连,第二p 区530和第三p 区540电性相连,且第三p 区540用于连接地线,使得第二p 区530连接地线。

61.hvjt终结端300可包括多个多晶硅场板320,多个多晶硅场板320的电位从高压区向低压区逐级降低。hvpmos管500的多晶硅栅设置在hvjt终结端300的内侧,即hvpmos管500的多晶硅栅靠近hvjt终结端300的高压区设置,且与hvjt终结端300的多晶硅场板320电性连接。上述设置得到的n 区510形成hvpmos管500的体区,第一p 区520形成hvpmos管500的源区,第二p 区530形成hvpmos管500的漏区。

62.上述的实施例中,通过在p型衬底100上设置有n外延层200,n外延层200包括n型高压区;n型高压区内设置有n 区510和第一p 区520;p型衬底100内设置有第二p 区530和第三p 区540,且n 区510与第一p 区520电性相连,第二p 区530与第三p 区540相连接地;hvjt终结端300设置在n外延层200上;hvpmos管500包括多晶硅栅、漏区、源区和体区;多晶硅栅设置在hvjt终结端300的内侧,且与hvjt终结端300电性连接;n 区510形成体区,第一p 区520形成源区,第二p 区530形成漏区。当hvjt终结端300处的静电电流达到阈值时,会向hvpmos管500的多晶硅栅输出一定电平,当该电平高于hvpmos管500的阈值电压时,hvpmos管500开始导通,静电电流从hvpmos管500释放到地,从而明显提高了hvic在高压岛和低压区(包括低压衬底)之间的esd(静电放电)能力,避免了静电加载到高压端口和低压端口之间而造成hvjt终结端300的击穿。

63.在一个示例中,第二p 区530靠近hvjt终结端300的外侧设置,hvjt终结端300的外侧与hvjt终结端300的内侧相对。

64.其中,hvjt终结端300的内侧指的是靠近多晶硅场板320的高压区的一侧。hvjt终结端300的外侧指的是靠近多晶硅场板320的低压区的一侧。

65.示例性的,通过将第二p 区530靠近hvjt终结端300的外侧设置,将hvnmos管的多晶硅栅设置在hvjt终结端300的内侧,将第一p 区520设置在n型高压区上,且第一p 区520靠近多晶硅栅;n 区510紧贴第一p 区520设置,进而n 区510形成hvpmos管500的体区,第一p 区520形成hvpmos管500的源区,第二p 区530形成hvpmos管500的漏区。当hvjt终结端300处的静电电流达到阈值时,会向hvpmos管500的多晶硅栅输出一定电平,当该电平高于hvpmos管500的阈值电压时,hvpmos管500开始导通,静电电流从hvpmos管500释放到地,从而明显提高了hvic在高压岛和低压区(包括低压衬底)之间的esd(静电放电)能力,避免了静电加载到高压端口和低压端口之间而造成hvjt终结端300的击穿。

66.在一个示例中,n外延层200还包括n外延区;n外延区上设置有p-top区310,p-top区310上设置有从hvjt终结端300的内侧与hvjt终结端300的外侧排列的多个多晶硅场板320;多个多晶硅场板320、p-top区310和n外延区组成hvjt终结端300。

67.其中,n外延层200还划分有n外延区,n外延区可用半导体材料制成,例如,n外延区可以是碳化硅n外延区。n外延区上设置有p-top区310,在一个示例中,p-top区310可由n外延区的上表面向下延伸得到,其中p-top区310的厚度小于n外延区的厚度。在p-top区310上设置有多个多晶硅场板320,其中多个多晶硅场板320从hvjt终结端300的内侧至hvjt终结端300的外侧排列,使得多个多晶硅场板320的电位从高压区向低压区逐级降低,即多个多晶硅场板320的电位从hvjt终结端300的内侧与hvjt终结端300的外侧依次降低,且多晶硅栅与靠近hvjt终结端300的内侧的多晶硅场板320电性连接。示例性的,p-top区310的掺杂浓度大于n外延区的掺杂浓度。

68.示例性的,hvjt结终端由多个多晶硅场板320、p-top区310、n外延区组成,多个多晶硅场板320的电位从高压区向低压区逐级降低。p-top区310的掺杂浓度大于n外延区的掺杂浓度。在n外延区以外p型衬底100上制作第二p 区530和第三p 区540,其中第二p 区530的掺杂浓度为1e15cm-2;在n外延区上采用双扩散工艺制作了第一p 区520和n区,第一p 区520的掺杂浓度为1e15cm-2,n区的掺杂浓度为1e13cm-2。双扩散后再在n外延区内部的第一p 区520旁边再制作n 区510,其中n 区510的掺杂浓度为1e15cm-2。n型高压区内的n 区510形成hvnmos管的体区(b),第一p 区520形成hvnmos管的源区(s),多晶硅栅(g)在hvjt终结端300的内侧,p型衬底100内的第二p 区530形成hvnmos管的漏区(d)。n 体区(b)、第一p 源区(s)、第二p 漏区(d)表面淀积金属铝形成欧姆接触,多晶硅栅(g)通过通孔连接到金属层;源区通过金属层连接到体区,进而在hvjt结终端侧形成hvpmos管500,从而当hvjt终结端300处的静电电流达到阈值时,会向hvpmos管500的多晶硅栅输出一定电平,当该电平高于hvpmos管500的阈值电压时,hvpmos管500开始导通,静电电流从hvpmos管500释放到地,明显提高了hvic在高压岛和低压区(包括低压衬底)之间的esd(静电放电)能力,避免了静电加载到高压端口和低压端口之间而造成hvjt终结端300的击穿。需要说明的是,可使用双扩散工艺制作hvpmos管500,调整注入浓度。可采用double resurf工艺制作hvjt结构,调整p-top区310的掺杂浓度。

69.在一个示例中,如图6所示,为对应图5中的高压集成电路的第二等效电路示意图。其中hvjt终结端300是一个高压的pn结,将hvjt终结端300等效为反向二极管来表征它的特性。hvpmos管500并联到hvjt终结端300的两端,hvpmos管500的源极(s)与hvjt终结端300的阴极(c)相连接,hvpmos管500的漏极(d)与hvjt终结端300的阳极(a)相连接。hvpmos管500的栅极(g)连接到分压电阻r1、r2中间,hvpmos管500的体极(b)与hvpmos管500的源极(s)连接并接到地。当静电电流达到某个值时,分压电阻(r1、r2)向hvpmos管500的栅极(g)输出一定电平,gs电压高于hvpmos管500的阈值电压时,hvpmos管500开始导通,静电电流从hvpmos管500释放到地,从而明显提高了hvic在高压岛和低压区(包括低压衬底)之间的esd(静电放电)能力,避免了静电加载到高压端口和低压端口之间而造成hvjt终结端300的击穿。

70.需要说明的是,在一个示例中,通过设计r1和r2电阻的分压比例,使静电电流约800a的时候达到hvpmos管500的阈值电压,使hvpmos管500开启。

71.在一个示例中,如图1中,传统的高压集成电路的等效电路应用示意图。传统的无

静电释放电路时,全部静电放电电流只能通过hvjt终结端反向释放,由于hvjt终结端反向击穿电压有600v以上,而释放能量等于释放电压释放电流,在半导体电路里面释放能量是转换成热量耗散的,同样面积的半导体电路能耗散的能量是一定的,因此释放能量一定的情况下,释放电压越高,可以释放的电流就越小,也就是静电等级越低。而采用本技术高压集成电路的hvpmos管500来释放的时,如图7所示,hvpmos管500的导通电压很低,只有几伏,约为hvjt终结端300反向击穿电压的1/100,因此hvpmos管500的释放电流是hvjt终结端300的100倍。图7中,由于hvpmos管500导通电阻小,因此大部分电流通过hvpmos管500来流通,只有很小部分电路通过电阻和hvjt终结端300流通,因此大大提高了静电的释放能力。

72.示例性的,该高压集成电路的验证过程为:对hvjt终结端300的结构、hvpmos管500结构和掺杂浓度进行拉偏,在保证hvjt终结端300耐压能达到650v以上情况下,选择静电释放能力较好同时耐压较好的方案。进行125℃以上温度的高温反偏试验,测试高温下hvjt终结端300的高温漏电流,不允许出现漏电流明显增大现象。

73.在一个实施例中,还提供一种半导体电路,包括电路基板、电路层、多个引脚和密封本体。电路基板上设有绝缘层;电路层设置在绝缘层上;多个引脚的第一端分别与电路层电性连接;密封本体包裹电路基板、以及连接有各引脚的电路层;其中,各引脚的第二端分别从密封本体的第一侧面引出;电路层包括桥臂模块,以及上述任意一项的高压集成电路;桥臂模块耦合连接高压集成电路。

74.其中,高压集成电路的具体描述内容可参照上述实施例对高压集成电路的描述,在此不再赘述。

75.电路基板可用于承载整个半导体电路的电路及相应的元器件。电路基板可由金属材料制成,如1100、5052等材质的铝构成的矩形板材,其厚度相对其它层厚很多,一般为0.8mm至2mm,常用的厚度为1.5mm,主要实现导热和散热作用。又如,电路基板还可以是其它的导热性良好的金属材料制成,例如,可以是铜材质的矩形板材。需要说明的是,本技术的电路基板形状不限定于是矩形形状,还可以是圆形或梯形等形状。

76.绝缘层可用来防止电路层与电路基板进行导电。绝缘层设置于电路基板的表面,其厚度相对电路基板较薄,一般在50um至150um,常用为110um。在绝缘层上设置电路层,使得电路层与电路基板之间绝缘,电路层上设有高压集成电路、桥臂模块等内部电路。高压集成电路、桥臂模块之间通过金属线电性连接。

77.其中,引脚可用来传输信号至电路层上的相应内部电路,还可用来将电路层上的相应内部电路输出的信号传输给外部模块。多个引脚中的部分引脚可用于传输低压逻辑控制信号,多个引脚中的另一部分引脚还可用于传输高压功率输出信号,多个引脚设置在电路基板的至少一侧边缘处,且引脚与电路基板上的电路层电性连接;多个引脚通过焊接如锡膏焊的方式焊接到电路基板上的电路层的焊盘,以此实现与电路基板上的电路层电性连接,以此实现与电路基板上的电路层电性连接。

78.引脚的材质可采用c194(-1/2h)板料(化学成分:cu(≧97.0)、fe:2.4、p:0.03、zn:0.12)或kfc(-1/2h)板料(化学成分:cu(≧99.6)、fe:0.1(0.05~0.15)、p:0.03(0.025~0.04)),通过冲压或蚀刻工艺对0.5mm的c194或kfc板料进行加工,再对表面进行先镀镍厚度0.1-0.5um,再镀锡厚度2-5um;通过特定设备将引脚320多余的连筋切除并整形成所需形状。

79.需要说明的是,各引脚从密封本体的第一侧面穿出后,通过折弯工艺,将各引脚折弯,得到第一折弯端,然而再对第一折弯端的末端折弯,得到第二折弯端。其中第一折弯端可平行于电路基板。

80.桥臂模块可包括高压侧桥臂(即上桥臂模块)和/或低压侧桥臂(即下桥臂模块),桥臂模块可包括igbt和快恢复二极管,igbt和快恢复二极管分别采用银胶或焊锡粘接到电路基板上;igbt和快恢复二极管分别采用金、铜或铝等键合线连接在电路层上。高压集成电路采用银胶或焊锡粘接到电路基板上,高压集成电路可通过采用金、铜或铝等键合线连接在电路层上,且可采用金、铜或铝等键合线分别与mos管、igbt连接。

81.密封本体可用来对电性连接有多个引脚和电路层的电路基板进行塑封,使得将电路基板、以及连接有各引脚、桥臂模块的电路层包裹在密封本体内,起到保护内部的线路,以及绝缘耐压的作用。密封本体在制备过程中,可通过塑封工艺,采用塑封模具将电性连接有多个引脚、桥臂模块的电路基板塑封在密封本体内。密封本体的材料可以是热固性高分子,如环氧树脂、酚醛树脂、硅胶、氨基、不饱和树脂;为了提高散热能力,密封本体可以为含有金属、陶瓷、氧化硅、石墨烯等粉末或纤维的复合材料。在一个示例中,密封本体采用的材料可以是以环氧树脂为基体树脂,以高性能酚醛树脂为固化剂,加入硅微粉等为填料,以及添加多种助剂混配而成的模塑料。

82.可根据不同的设计要求,设计不同形状的塑封模具,进而可塑封得到不同形状结构的密封本体。例如,密封本体可以是长方体结构。通过使用热塑性树脂的注入模模制方式或使用热硬性树脂的传递模模制方式,将电路基板、以及连接有各引脚、桥臂模块、高压集成电路(包括hvjt终结端、hvnmos管或hvnmos管)的电路层包裹起来起到保护作用。

83.在一个示例中,电路层包括电路布线层(未示出),以及配置于电路布线层上的电路元件;电路布线层设于绝缘层上。电路元件包括桥臂模块相应的电路元件(如igbt和快恢复二极管)、高压集成电路(包括hvjt终结端、hvnmos管或hvnmos管)等)相应的电路元件。

84.其中,电路布线层由铜等金属构成且和电路基板绝缘,电路布线层包括由蚀刻的铜箔构成电路线路,线路层厚度也较薄,如70um左右。在一个示例中,电路布线层还包括靠近电路基板的侧边位置设置的焊盘,可以采用2盎司铜箔形成上述的电路布线层。最后在电路布线层上还可以涂覆一层较薄的绿油层,以起到线路隔离作用,隔断电路线路与电路线路之间的电连接。多个电路元件设在电路布线层上,多个电路元件之间或者电路元件与电路布线层之间可通过金属线电连接;电路元件可通过焊接的方式与电路布线层固定。

85.在一个示例中,绝缘层覆盖电路基板至少一个表面形成。且形成密封层的环氧树脂等树脂材料内可高浓度填充氧化铝、碳化硅铝等填料提高热导率,为了提高热导率,填料可采用角形,为了规避填料损坏电路元件表面的风险,填料可采用球形。引脚一般采用铜等金属制成,铜表面通过化学镀和电镀形成一层镍锡合金层,合金层的厚度一般为5μm,镀层可保护铜不被腐蚀氧化,并可提高可焊接性。

86.在一个示例中,电路层包括高压集成电路(包括hvjt终结端、hvnmos管或hvnmos管)、桥臂模块,通过刷锡膏或点银胶分别将高压集成电路(包括hvjt终结端、hvnmos管或hvnmos管)、桥臂模块相应的器件芯片贴装到电路层相应的元器件安装位上,通过自动贴片smt设备分别将高压集成电路(包括hvjt终结端、hvnmos管或hvnmos管)、桥臂模块相应的阻件、容件贴装到电路层相应的元器件安装位上;然后将整个半成品过回流炉将所有的元器

件焊接到对应安装位上,通过视觉检查aoi设备对元器件焊接质量进行检测;通过喷淋、超声等清洗方式,清除残留在电路基板上的助焊剂和铝屑等异物,通过键合线,使高压集成电路(包括hvjt终结端、hvnmos管或hvnmos管)、桥臂模块和电路布线间形成连接,实现对高压集成电路、桥臂模块的安装,进而实现集成高压集成电路、桥臂模块的半导体电路。

87.上述的实施例中,基于本技术的半导体电路设置了上述实施例中的高压集成电路,当hvjt终结端处的静电电流达到阈值时,会向hvnmos管(或hvnmos管)的多晶硅栅输出一定电平,当该电平高于hvnmos管(或hvnmos管)的阈值电压时,hvnmos管(或hvnmos管)开始导通,静电电流从hvnmos管(或hvnmos管)释放到地,从而明显提高了hvic在高压岛和低压区(包括低压衬底)之间的esd(静电放电)能力,即提高了半导体电路的静电放电能力,避免了静电加载到高压端口和低压端口之间而造成hvjt终结端的击穿。

88.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本实用新型的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

89.在本实用新型的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”、“顺时针”、“逆时针”、“轴向”、“径向”、“周向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。

90.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本实用新型的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

91.在本实用新型中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系,除非另有明确的限定。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本实用新型中的具体含义。

92.在本实用新型中,除非另有明确的规定和限定,第一特征在第二特征“上”或“下”可以是第一和第二特征直接接触,或第一和第二特征通过中间媒介间接接触。而且,第一特征在第二特征“之上”、“上方”和“上面”可是第一特征在第二特征正上方或斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”可以是第一特征在第二特征正下方或斜下方,或仅仅表示第一特征水平高度小于第二特征。

93.尽管上面已经示出和描述了本实用新型的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本实用新型的限制,本领域的普通技术人员在本实用新型的范围内可以对上述实施例进行变化、修改、替换和变型。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。