1.本案是与显示装置有关,且特别是有关于一种应用于有机发光二极管显示器的栅极驱动装置。

背景技术:

2.有机发光二极管(organic light-emitting diode,oled)显示器具有高对比、高色彩饱和度和发光效率佳等优点,使其成为下一世代热门技术之一。传统的栅极驱动装置需要具备顺向或反向传输功能,其内部节点漏电流会影响输出,且电路内的薄膜晶体管若老化会导致阈值电压(threshold voltage,vth)变异影响输出。故,如何提供高显示品质的有机发光二极管驱动装置与显示器,实为业界有待解决的技术问题。

技术实现要素:

3.发明内容旨在提供本揭示内容的简化摘要,以使阅读者对本揭示内容具备基本的理解。此发明内容并非本揭示内容的完整概述,且其用意并非在指出本案实施例的重要/关键元件或界定本案的范围。

4.本案内容的一技术态样是关于一种驱动装置。此驱动装置包含第n级电路与第n 1级电路。第n级电路用以根据第一选择信号或第二选择信号以决定是否提供第一稳压信号、第二稳压信号或第三稳压信号,第n级电路用以根据第一稳压信号或第二稳压信号以决定是否提供第一栅极信号。第n 1级电路用以根据第一选择信号或第二选择信号以决定是否提供下级第一稳压信号、下级第二稳压信号或下级第三稳压信号,第n 1级电路用以根据下级第一稳压信号与下级第三稳压信号以决定是否输出下级第二栅极信号。第一栅极信号与下级第二栅极信号在同时序互为相同脉冲宽度的反相信号。第一稳压信号、第二稳压信号、第三稳压信号、第一栅极信号、下级第一稳压信号、该下级第二稳压信号、下级第三稳压信号与下级第二栅极信号对应第1级至第n级信号,n为大于1的正整数。

5.因此,根据本案的技术内容,本案实施例所示的驱动装置得以同时提供顺向或反向产生的脉冲信号,适用于高显示品质的有机发光二极管驱动装置。此外,本案的驱动装置得以防止内部节点电压在输出信号时受漏电流影响输出,因此,可以改善显示器亮度显示不均的问题。

附图说明

6.为让本案的上述和其他目的、特征、优点与实施例能更明显易懂,所附图式的说明如下:

7.图1是依照本案一实施例绘示一种驱动装置与显示面板的示意图。

8.图2是依照本案一实施例绘示一种驱动电路的详细电路图。

9.图3是依照本案一实施例绘示一种驱动电路的详细电路图。

10.图4是依照本案一实施例绘示多种控制信号位准的波形示意图。

11.图5至图12是依照本案一实施例绘示如图2中所示的驱动电路的操作示意图。

12.根据惯常的作业方式,图中各种特征与元件并未依比例绘制,其绘制方式是为了以最佳的方式呈现与本案相关的具体特征与元件。此外,在不同图式间,以相同或相似的元件符号来指称相似的元件/部件。

13.其中,附图标记说明如下:

14.200、200a:驱动电路

15.201、201a:启动电路

16.202、202a:第一稳压电路

17.203、203a:第一输出电路

18.204、204a:第二稳压电路

19.205、205a:第二输出电路

20.q[n]:第一稳压信号

[0021]

p[n]:第二稳压信号

[0022]

g[n]:第一栅极信号

[0023]

k[n]:第三稳压信号

[0024]

gb[n]:第二栅极信号

[0025]

u2d:第一选择信号

[0026]

d2u:第二选择信号

[0027]

ck2:第一时钟信号

[0028]

ck4:第二时钟信号

[0029]

g[n-1]:第三栅极信号

[0030]

g[n 1]:第四栅极信号

[0031]

vgh:上拉信号

[0032]

vgl:下拉信号

[0033]

c1:第一电容

[0034]

c2:第二电容

[0035]

xck1:反时钟信号

[0036]

xck2:下级反时钟信号

[0037]

t1~t2_2:晶体管

[0038]

q[n 1]:下级第一稳压信号

[0039]

p[n 1]:下级第二稳压信号

[0040]

k[n 1]:下级第三稳压信号

[0041]

gb[n 1]:下级第二栅极信号

[0042]

p1~p8:第一阶段~第八阶段

具体实施方式

[0043]

为了使本揭示内容的叙述更加详尽与完备,下文针对本案的实施态样与具体实施例提出了说明性的描述;但这并非实施或运用本案具体实施例的唯一形式。实施方式中涵盖了多个具体实施例的特征以及用以建构与操作这些具体实施例的方法步骤与其顺序。然

而,亦可利用其他具体实施例来达成相同或均等的功能与步骤顺序。

[0044]

除非本说明书另有定义,此处所用的科学与技术词汇的含义与本案所属技术领域中具有通常知识者所理解与惯用的意义相同。此外,在不和上下文冲突的情形下,本说明书所用的单数名词涵盖该名词的复数型;而所用的复数名词时亦涵盖该名词的单数型。

[0045]

另外,关于本文中所使用的「耦接」或「连接」,可指二或多个元件相互直接作实体或电性接触,或是相互间接作实体或电性接触,亦可指二或多个元件相互操作或动作。

[0046]

在本文中,用语『电路』泛指由一或多个晶体管与/或一或多个主被动元件按一定方式连接以处理信号的物件。

[0047]

在说明书及权利要求书中使用了某些词汇来指称特定的元件。然而,所属技术领域中具有通常知识者应可理解,同样的元件可能会用不同的名词来称呼。说明书及权利要求书并不以名称的差异做为区分元件的方式,而是以元件在功能上的差异来做为区分的基准。在说明书及权利要求书所提及的「包含」为开放式的用语,故应解释成「包含但不限定于」。

[0048]

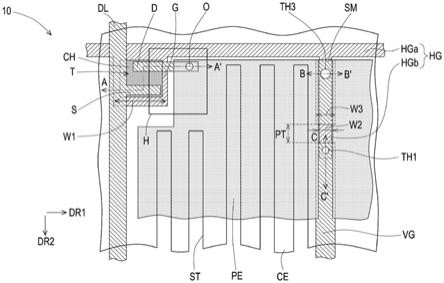

图1是依照本揭露一实施例绘示一种驱动装置100与显示面板的示意图。请同时参照图2,如图所示,驱动装置100包含n个驱动电路,驱动装置100包含第n级电路与第n 1级电路。于连接关系上,第n级电路耦接于第n 1级电路。

[0049]

为提供高显示品质的有机发光二极管驱动电路技术,本案提供如图2所示的驱动电路200,其相关操作详细说明如后。

[0050]

在一实施例中,第n级电路200用以根据第一选择信号或第二选择信号以决定是否提供第一稳压信号、第二稳压信号或第三稳压信号,第n级电路用以根据第一稳压信号或第二稳压信号以决定是否提供第一栅极信号。第n 1级电路200a用以根据第一选择信号或第二选择信号以决定是否提供下级第一稳压信号、下级第二稳压信号或下级第三稳压信号,第n 1级电路用以根据下级第一稳压信号与下级第三稳压信号以决定是否输出下级第二栅极信号。第一栅极信号与下级第二栅极信号在同时序互为相同脉冲宽度的反相信号。第一稳压信号、第二稳压信号、第三稳压信号、第一栅极信号、下级第一稳压信号、该下级第二稳压信号、下级第三稳压信号与下级第二栅极信号对应第1级至第n级信号,n为大于1的正整数。

[0051]

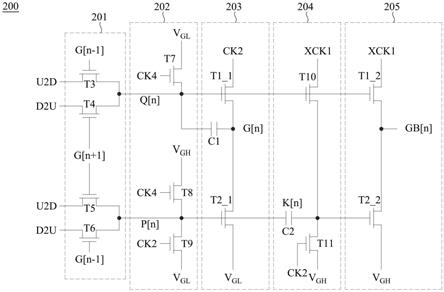

为使驱动电路200的上述操作易于理解,请一并参阅图2至图4,图2是依照本案一实施例绘示一种驱动电路的详细电路图,图3是依照本案一实施例绘示一种驱动电路的详细电路图,图4是依照本案一实施例绘示多种控制信号位准的波形示意图。

[0052]

如图2至图4所示,第n级电路200用以根据第一选择信号u2d或第二选择信号d2u以决定是否提供第一稳压信号q[n]、第二稳压信号p[n]或第三稳压信号k[n],第n级电路200用以根据第一稳压信号q[n]或第二稳压信号p[n]以决定是否提供第一栅极信号g[n]。第一稳压信号q[n]、第二稳压信号p[n]、第三稳压信号k[n]与第一栅极信号g[n]对应第1级至第n级信号,n为大于1的正整数。举例而言,第n级电路200通过提供第一稳压信号q[n]至晶体管t1_1的栅极,或通过提供第二稳压信号p[n]至晶体管t2_1的栅极,借此控制是否提供第一栅极信号g[n]。此外,第一栅极信号g[n]可以为脉冲宽度调制(pulse width modulation,pwm)信号,晶体管t1_1与晶体管t2_1可以是低温多晶硅(low temperature poly-silicon,ltps)薄膜晶体管。

[0053]

随后,第n 1级电路200a用以根据第一选择信号u2d或第二选择信号d2u以决定是否提供下级第一稳压信号q[n 1]、下级第二稳压信号p[n 1]或下级第三稳压信号k[n 1],第n 1级电路200a用以根据下级第一稳压信号q[n 1]与下级第三稳压信号k[n 1]以决定是否输出下级第二栅极信号gb[n 1]。下级第一稳压信号q[n 1]、下级第二稳压信号p[n 1]、下级第三稳压信号k[n 1]与下级第二栅极信号gb[n 1]对应第1级至第n级信号,n为大于1的正整数。举例而言,第n 1级电路200a通过提供下级第一稳压信号q[n 1]至晶体管t1_2的栅极,或通过提供下级第三稳压信号k[n 1]至晶体管t2_2的栅极,借此控制是否提供下级第二栅极信号gb[n 1]。此外,下级第二栅极信号gb[n 1]可以为脉冲宽度调制(pulse width modulation,pwm)信号,晶体管t1_2与晶体管t2_2可以是低温多晶硅(low temperature poly-silicon,ltps)薄膜晶体管。

[0054]

第一栅极信号g[n]与下级第二栅极信号gb[n 1]在同时序互为相同脉冲宽度的反相信号。举例而言,当在第一时序时,第一栅极信号g[n]为高电位,则下级第二栅极信号gb[n 1]为低电位,当在第二时序时,第一栅极信号g[n]为低电位,则下级第二栅极信号gb[n 1]为高电位。此外,晶体管t3~t11可以是氧化铟镓锌(indium gallium zinc oxide,igzo)薄膜晶体管。

[0055]

请一并参照图2与图4,在一实施例中,第n级电路200包含启动电路201、第一稳压电路202、第一输出电路203、第二稳压电路204与第二输出电路205。启动电路203用以根据第三栅极信号g[n-1]与第四栅极信号g[n 1]以决定是否提供第一选择信号u2d或第二选择信号d2u。第一稳压电路202用以根据第一时钟信号ck2与第二时钟信号ck4以决定是否提供第一稳压信号q[n]或第二稳压信号p[n]。第一输出电路203用以根据第一稳压信号q[n]或第二稳压信号p[n]以决定是否提供第一栅极信号g[n]。第二稳压电路204用以根据第一稳压信号p[n]与第一时钟信号ck2以决定是否输出第三稳压信号k[n]。第二输出电路205用以根据第一稳压信号q[n]与第三稳压信号k[n]以决定是否输出第二栅极信号gb[n]。上述第三栅极信号g[n-1]、第四栅极信号g[n 1]、第一稳压信号q[n]、第二稳压信号p[n]、第三稳压信号k[n]、第一栅极信号g[n]与第二栅极信号gb[n]对应第1级至第n级信号,n为大于1的正整数。

[0056]

请一并参照图3与图4,在另一实施例中,第n 1级电路200a包含启动电路201a、第一稳压电路202a、第一输出电路203a、第二稳压电路204a与第二输出电路205a。启动电路201a用以根据第一栅极信号g[n]与第五栅极信号g[n 2]以决定是否提供第一选择信号u2d或第二选择信号d2u。第一稳压电路202a用以根据第三时钟信号ck1与第四时钟信号ck3以决定是否提供下级第一稳压信号q[n 1]或下级第二稳压信号p[n 1]。第一输出电路203a用以根据下级第一稳压信号q[n 1]或下级第二稳压信号p[n 1]以决定是否提供第四栅极信号g[n 1]。第二稳压电路204a用以根据下级第一稳压信号q[n 1]与第四时钟信号ck3以决定是否输出下级第三稳压信号k[n 1]。第二输出电路205a用以根据下级第一稳压信号q[n 1]与下级第三稳压信号k[n 1]以决定是否输出下级第二栅极信号gb[n 1]。上述第一栅极信号g[n]、第五栅极信号g[n 2]、下级第一稳压信号q[n 1]、下级第二稳压信号p[n 1]、下级第三稳压信号k[n 1]、第四栅极信号g[n 1]与下级第二栅极信号gb[n 1]对应第1级至第n级信号,n为大于1的正整数。

[0057]

请一并参照图4与图5,在一实施例中,第一稳压电路202包含第一储存电容c1,且

第二稳压电路204包含第二储存电容c2。在第一阶段p1时,第一储存电容c1根据第三栅极信号g[n-1]而于第一端及第二端分别储存第一选择信号u2d与第一时钟信号ck2。第一输出电路203根据第一稳压信号q[n]提供第一时钟信号ck2。第二储存电容c2根据第三栅极信号g[n-1]而于第三端及第四端分别储存第二选择信号d2u与反时钟信号xck1。第二输出电路205根据第一稳压信号q[n]提供反时钟信号xck1。举例而言,第一选择信号u2d流经晶体管t3,第一选择信号u2d的电压为vgh,故储存于第一电容c1的第一端的电压值为vgh-vth_t3,第一稳压信号q[n]的电压值同样为vgh-vth_t3,晶体管t1_1根据第一稳压信号q[n]开启,第一电容的第二端储存第一时钟信号ck2的电压值vgl,第一栅极信号g[n]的电压值同样为vgl。再者,晶体管t6根据第三栅极信号g[n-1]开启,第二电容的第三端储存第二选择信号d2u的电压值vgl,第二稳压信号p[n]的电压值同样为vgl,晶体管t10根据第一稳压信号q[n]开启,第二电容的第四端储存反时钟信号xck1的电压值vgl,第三稳压信号k[n]的电压值同样为vgl。最后,晶体管t1_2根据第一稳压信号q[n]开启,输出的第二栅极信号gb[n]为反时钟信号xck1的电压值vgl。

[0058]

请一并参照图4与图6,在第二阶段p2时,第一储存电容c1根据第一稳压信号q[n]储存第一时钟信号ck2。第一输出电路202根据第一稳压信号q[n]提供第一时钟信号ck2。第二储存电容根据第一时钟信号ck2与第一稳压信号q[n]而于第三端及第四端分别储存下拉信号vgl与上拉信号vgh。第二输出电路205根据第一稳压信号q[n]提供反时钟信号xck1。举例而言,晶体管t1_1根据第一稳压信号q[n]开启,第一电容c1的第二端储存第一时钟信号ck2的电压值vgh,第一栅极信号g[n]的电压值同样为vgh,第一稳压信号q[n]经由第一电容c1同步升压为vq,电压值vq大于vgh vth_ltps。再者,晶体管t9根据第一时钟信号ck2开启,第二电容的第三端储存下拉信号vgl,第二稳压信号p[n]的电压值同样为vgl,晶体管t10根据第第一稳压信号q[n]开启,晶体管t11根据第一时钟信号ck2开启,第二电容的第四端储存反时钟信号xck1的电压值vgh与上拉信号vgh,第三稳压信号k[n]的电压值同样为vgh。最后,晶体管t1_2根据第一稳压信号q[n]开启,输出的第二栅极信号gb[n]为反时钟信号xck1的电压值vgh。

[0059]

请一并参照图4与图7,在第三阶段p3时,第一储存电容c1根据第四栅极信号g[n 1]而于第一端及第二端分别储存第二选择信号d2u与下拉信号vgl。第一输出电路203根据第二稳压信号p[n]提供下拉信号vgl。第二储存电容c2根据第四栅极信号g[n 1]而储存第一选择信号u2d。第二输出电路根据第三稳压信号k[n]提供上拉信号vgh。举例而言,晶体管t4根据第四栅极信号g[n 1]开启,第一电容的第一端储存第二选择信号d2u的电压值vgl,晶体管t2_1根据第二稳压信号p[n]开启,第一电容c1的第二端储存下拉信号vgl。再者,晶体管t5根据第四栅极信号g[n 1]开启,第一选择信号u2d流经晶体管t5,第一选择信号u2d的电压为vgh,故储存于第二电容c2的第一端的电压值为vgh-vth_t5,第二稳压信号p[n]的电压值同样为vgh-vth_t5,第三稳压信号q[n]经由第二电容c2同步升压为vk,电压值vk大于vgh vth_ltps。最后,晶体管t2_2根据第三稳压信号k[n]开启,输出的第二栅极信号gb[n]为上拉信号vgh。

[0060]

请一并参照图4与图8,在第四阶段p4时,第一储存电容c1根据第二时钟信号ck4与第二稳压信号p[n]而储存下拉信号vgl。第一输出电路203根据第二稳压信号p[n]而提供下拉信号vgl。第二储存电容c2根据第二时钟信号ck4而储存上拉信号vgh。第二输出电路205

根据第三稳压信号k[n]提供上拉信号vgh。举例而言,晶体管t7根据第二时钟信号ck4开启,第一电容c1的第一端储存上拉信号vgh,第一稳压信号q[n]的电压值同样为vgh,晶体管t2_1根据第二稳压信号p[n]开启,第一电容c1的第二端储存下拉信号vgl,第一栅极信号g[n]的电压值同样为vgl。再者,晶体管t8根据第二时钟信号ck4开启,上拉信号vgh流经晶体管t8,故储存于第二电容c2的第三端的电压值为vgh-vth_t8,第一稳压信号p[n]的电压值同样为vgh-vth_t8,第三稳压信号k[n]经由第二电容c2同步升压为vk,电压值vk大于vgh vth_ltps。最后,晶体管t2_2根据第三稳压信号k[n]开启,输出的第二栅极信号gb[n]为上拉信号vgh。

[0061]

请一并参照图4与图9,在第五阶段p5时,第一储存电容c1根据第二稳压信号p[n]而储存下拉信号vgl。第一输出电路203根据第二稳压信号p[n]而提供下拉信号vgl。第二储存电容c2维持第四阶段p4储存的上拉信号vgh。第二输出电路205根据第三稳压信号k[n]提供上拉信号vgh。举例而言,晶体管t2_1根据第二稳压信号p[n]开启,第一电容c1的第二端储存下拉信号vgl,第一栅极信号g[n]的电压值同样为vgl,经由第一电容c1降第一稳压信号q[n]电压值为vgl。再者,第二储存电容c2维持第四阶段p4的储存状态,第二储存电容c2的第三端储存电压值为vgh-vth_t8,第二稳压信号p[n]的电压值同样为vgh-vth_t8,第二储存电容c2的第四端储存电压值为vk,电压值vk大于vgh vth_ltps,第三稳压信号k[n]的电压值同样为vk。最后,晶体管t2_2根据第三稳压信号k[n]开启,输出的第二栅极信号gb[n]为上拉信号vgh。

[0062]

请一并参照图4图10,在第六阶段p6时,第一储存电容c1维持第五阶段p5储存下拉信号vgl。第一输出电路203维持第五阶段p5而提供下拉信号vgl。第二储存电容c2根据第一时钟信号ck2而于第三端及第四端分别储存下拉信号vgl与上拉信号vgh。第二输出电路维持第五阶段p5而提供上拉信号vgh。举例而言,第一储存电容c1维持第五阶段p5的储存状态,第一储存电容c1的第一端与第二端储存电压值皆为vgl,第一稳压信号q[n]与第一栅极信号g[n]的电压值同样为vgl。再者,晶体管t9根据第一时钟信号ck2开启,第二电容的第三端储存下拉信号vgl,第二稳压信号p[n]的电压值同样为vgl,晶体管t11根据第一时钟信号ck2开启,第一时钟信号ck2流经晶体管t11,第一时钟信号ck2的电压值为vgh,故储存于第二电容c2的第四端的电压值为vgh-vth_t11,第三稳压信号k[n]的电压值同样为vgh-vth_t11。最后,第二栅极信号gb[n]维持第五阶段p5的输出状态,输出的第二栅极信号gb[n]为上拉信号vgh。

[0063]

请一并参照图4与图11,在第七阶段p7时,第一储存电容c1维持第五阶段p5储存下拉信号vgl。第一输出电路203维持第五阶段p5而提供下拉信号vgl。第二储存电容c2维持第六阶段p6而于第三端及第四端分别储存下拉信号vgl与上拉信号vgh。第二输出电路205维持第五阶段p5而提供上拉信号。举例而言,第一储存电容c1维持第五阶段p5的储存状态,第一储存电容c1的第一端与第二端储存电压值皆为vgl,第一稳压信号q[n]与第一栅极信号g[n]的电压值同样为vgl。再者,第二储存电容c2维持第六阶段p6的储存状态,第二电容的第三端储存下拉信号vgl,第二稳压信号p[n]的电压值同样为vgl,储存于第二电容c2的第四端的电压值为vgh-vth_t11,第三稳压信号k[n]的电压值同样为vgh-vth_t11。最后,第二栅极信号gb[n]维持第五阶段p5的输出状态,输出的第二栅极信号gb[n]为上拉信号vgh。

[0064]

请一并参照图4与图12,在第八阶段p8时,第一储存电容c1根据第二时钟信号ck4

与第二稳压信号p[n]储存下拉信号vgl。第一输出电路202根据第二稳压信号p[n]而提供下拉信号vgl。第二储存电容c2根据第二时钟信号ck4而储存上拉信号vgh。第二输出电路203根据第三稳压信号k[n]而提供上拉信号vgh。举例而言,晶体管t7根据第二时钟信号ck4开启,第一电容c1的第一端储存上拉信号vgh,第一稳压信号q[n]的电压值同样为vgh,晶体管t2_1根据第二稳压信号p[n]开启,第一电容c1的第二端储存下拉信号vgl,第一栅极信号g[n]的电压值同样为vgl。再者,晶体管t8根据第二时钟信号ck4开启,上拉信号vgh流经晶体管t8,故储存于第二电容c2的第三端的电压值为vgh-vth_t8,第一稳压信号p[n]的电压值同样为vgh-vth_t8,第三稳压信号k[n]经由第二电容c2同步升压为vk,电压值vk大于vgh vth_ltps。最后,晶体管t2_2根据第三稳压信号k[n]开启,输出的第二栅极信号gb[n]为上拉信号vgh。

[0065]

在另一实施例中,在第八阶段p8后可接续第五阶段p5操作,驱动装置100借此达到同时提供顺向或反向产生的脉冲信号的功效。

[0066]

由上述本案实施方式可知,应用本案具有下列优点。本案实施例所示的驱动装置100得以适用于高显示品质与可同时提供顺向或反向产生的脉冲信号。此外,本案的驱动装置100得以防止内部节点电压在输出信号时受漏电流影响输出,因此,可以改善显示器亮度显示不均的问题。

[0067]

在参阅下文实施方式后,本案所属技术领域中具有通常知识者当可轻易了解本案的基本精神及其他目的,以及本案所采用的技术手段与实施态样。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。