1.本实用新型涉及电子技术领域,更具体的说,本实用新型涉及一种多相位本地震荡信号产生器。

背景技术:

2.在本地振荡器的一些应用中,从锁相环(phase-locked loop,pll)输出的时钟信号被建议由具有奇数因子的分频器来分频。这种类型的本地振荡器存在以下几个方面的不足,一,分频器是奇数的分频因子,不是偶数;二、可产生的相位较少(仅四相位);三、需要数字控制信号调整延迟链,增加设计复杂度;四、4.延迟链过多,导致面积电流过大。

技术实现要素:

3.为了克服现有技术的不足,本实用新型提供一种多相位本地震荡信号产生器,可产生的相位较多,并通过全模拟方式实现,不需要数字电路辅助设计,降低设计复杂度。

4.本实用新型解决其技术问题所采用的技术方案是:一种多相位本地震荡信号产生器,其改进之处在于,包括分频器、延迟链数组以及校准电路;

5.所述的延迟链数组连接在分频器上,该分频器用于接收输入信号,将输入信号进行分频成多个分频输入信号并穿入延迟链数组;所述的延迟链数组包括有与分频输入信号数量相同的延迟链,用于产生多个输出信号;

6.所述的校准电路包括电性连接的逻辑电路和运算放大器,逻辑电路连接至延迟链数组上,用于接收输出信号;运算放大器连接至延迟链数组上,该运算放大器用于产生控制信号,并将控制信号回传至延迟链数组,以控制延迟链的延迟量。

7.在上述的结构中,所述的分频器连接于锁相环pll上,输入信号由第一输入信号v

inp

和第二输入信号v

inn

组成。

8.在上述的结构中,所述的分频器中分频因子为n,分频器将第一输入信号v

inp

和第二输入信号v

inn

分频产生2n个分频输入信号。

9.在上述的结构中,所述延迟链的数量为2n个,且每个延迟链均包括有多个相串联的延迟单元。

10.在上述的结构中,所述的校准电路还包括低通滤波器,且低通滤波器设置在逻辑电路和运算放大器之间,逻辑电路用于接收多个延迟链内的信号;

11.所述低通滤波器用于对滤波电路的输出进行滤波,以产生滤波信号;

12.所述运算放大器用于比较滤波信号,以产生控制信号。

13.本实用新型的有益效果是:分频器可以是偶数的分频因子;采用全模拟方式实现,不需要数字电路辅助设计,降低设计复杂度。

附图说明

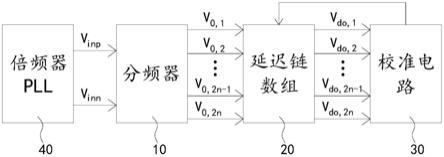

14.图1为本实用新型的多相位本地震荡信号产生器的原理框图。

15.图2为本实用新型的多相位本地震荡信号产生器的第一实施例图。

16.图3为本实用新型的正交信号、反相同相信号以及反相正交信号的相位图。

17.图4为本实用新型的校准电路的实施例图。

18.图5为完整的四相位本地震荡信号产生器结构图。

19.图6为本实用新型的多相位本地震荡信号产生器的第二实施例图。

20.图7为本实用新型的正交信号、反相同相信号以及反相正交信号的相位图。

21.图8为本实用新型的校准电路的实施例图。

22.图9为完整的八相位本地震荡信号产生器结构图。

具体实施方式

23.下面结合附图和实施例对本实用新型进一步说明。

24.以下将结合实施例和附图对本实用新型的构思、具体结构及产生的技术效果进行清楚、完整地描述,以充分地理解本实用新型的目的、特征和效果。显然,所描述的实施例只是本实用新型的一部分实施例,而不是全部实施例,基于本实用新型的实施例,本领域的技术人员在不付出创造性劳动的前提下所获得的其他实施例,均属于本实用新型保护的范围。另外,专利中涉及到的所有联接/连接关系,并非单指构件直接相接,而是指可根据具体实施情况,通过添加或减少联接辅件,来组成更优的联接结构。本实用新型创造中的各个技术特征,在不互相矛盾冲突的前提下可以交互组合。

25.参照图1所示,本实用新型揭示了一种多相位本地震荡信号产生器,具体的,包括分频器10、延迟链数组20以及校准电路30;所述的延迟链数组20连接在分频器10上,该分频器10用于接收输入信号,将输入信号进行分频成多个分频输入信号并穿入延迟链数组20;本实施例中,所述的分频器10连接于锁相环pll40上,输入信号由第一输入信号v

inp

和第二输入信号v

inn

组成。并且,所述的分频器10中分频因子为n,分频器10将第一输入信号v

inp

和第二输入信号v

inn

分频产生2n个分频输入信号。

26.进一步的,所述的延迟链数组20包括有与分频输入信号数量相同的延迟链,用于产生多个输出信号;因此本实施例中,所述延迟链的数量为2n个,延迟链数组20包括第一延迟链,第二延迟链,

…

,到第2n延迟链;用于接收2n个分频输入信号,产生2n个输出信号。结合图1所示,其输入信号是v

o,1

,v

o,2

,

…

,v

o,2n

,输出信号是v

do,1

,v

do,2

,

…

,v

do,2n

。并且,每个延迟链均包括有多个相串联的延迟单元,即,所述第一延迟链,包括多个串联联接的第一延迟单元,用于接收第一个分频输入信号;所述第二延迟链,包括多个串联联接的第二延迟单元,用于接收第二个分频输入信号;所述第2n延迟链,包括多个串联联接的第2n延迟单元,用于接收第2n个分频输入信号。

27.对于所述的校准电路30,本实用新型提供了一具体实施例,校准电路30包括电性连接的逻辑电路和运算放大器,逻辑电路连接至延迟链数组20上,用于接收输出信号;运算放大器连接至延迟链数组20上,该运算放大器用于产生控制信号,并将控制信号回传至延迟链数组20,以控制延迟链的延迟量。本实施例中,所述的校准电路30还包括低通滤波器,且低通滤波器设置在逻辑电路和运算放大器之间,逻辑电路用于接收多个延迟链内的信号;所述低通滤波器用于对滤波电路的输出进行滤波,以产生滤波信号;所述运算放大器用于比较滤波信号,以产生控制信号。其中,延迟链数组20的输入信号v

o,1

,v

o,2

,

…

,v

o,2n

和输

出信号v

do,1

,v

do,2

,

…

,v

do,2n

可作为4n个多相位输出信号,且各相位差为0,360/4n,360*2/4n,

…

,360*(4n-1)/4n。

28.通过上述的结构,本实用新型的分频器10可以是偶数的分频因子;输入信号如有2n个,可以产生4n个相位,故不限于只能产生四相位;并且,采用全模拟方式实现,不需要数字电路辅助设计,降低设计复杂度。另外本实用新型减少了所需的延迟单元,可以缩减面积电流。

29.结合图2所示,为本实用新型提供的一具体实施例,当n=1时,分频器10的输出为两个相位,延迟链需两组。延迟链由反向器组成,反向器的延迟由i

b1

的大小决定,i

b1

的大小由i_ctrl所控制。

30.如图2所示,i是同相信号,q是正交信号,ib是反相同相信号,qb是反相正交信号。其中i即是锁相环输出的同相信号,ib是锁相环输出的反相同相信号;q和qb经由延迟链产生得到。

31.如图3(a)所示,如果延迟链的延迟恰好使得q和i相差90度,qb和ib也相差90度,那如图2的延迟链数组20等校可以得到正交相位(i,q,ib,qb),也就是输入两个相位,输出四个相位。如图3(b)所示,如果延迟链的延迟过多,使得q和i相差超过90度,假设是相差95度,同理qb和ib也会相差95度。(因为q/qb和i在此不是正交关系,所以用q’/qb’表示)。

32.如图4所示为校准电路30的实现方式,用与门和低通滤波器去取出这个相位差的关系。假设q和i相差超过90度,那也代表qb和i相差小于90度,故可以把i和q通过一个与门,后面接一个低通滤波器,得到一个控制信号up_dc;再把i和qb通过一个与门,后面接一个低通滤波器,得到一个控制信号dn_dc。如果dn_dc》up_dc,代表延迟时间过长,需要把延迟链的延迟缩短,才可以得到准确的正交信号。

33.完整的四相位本地震荡信号产生器如图5所示,如上所述,使用不同与门将i/q和ib/qb本来应该互为领先(q领先i;qb领先ib)的电压信号做逻辑运算,通过低通滤波器得到up_dc;再使用不同与门将i/qb和ib/q本来应该互为落后(qb落后i;q落后ib)的电压信号做逻辑运算,通过低通滤波器得到dn_dc,通过op1和低通滤波器得到v1信号,v1信号和参考电压vref做通过op2,即可产生ib1的控制电压i_ctrl,去调整延迟链数组20的延迟时间,使得延迟链数组20的延迟时间能准确的让q和i相差90度,完成正交信号产生的目的。

34.结合图6所示,为本实用新型提供的一种八相位产生器的结构示意图,假设分频器10是除二电路,即n=2,输出为四相位,固延迟链需要四组。延迟链由反向器组成,反向器的延迟由i

b1

的大小决定,i

b1

的大小由i_ctrl所控制。

35.如图6所示,i是同相信号,q是正交信号,ib是反相同相信号,qb是反相正交信号,hq是45度信号,hqb是135度信号,hqq是225度信号,hqqb是315度信号。其中i即是除二分频器10输出的同相信号,ib是除二分频器10输出的反相同相信号,q是除二分频器10输出的正交信号,qb是除二分频器10输出的反相正交信号;hq,hqb,hqq和hqqb经由延迟链产生得到。

36.如图7(a)所示,如果延迟链的延迟恰好使得hq和i相差45度,hqb和ib也相差45度,hqq和q相差45度,hqqb和qb也相差45度,那如图7的延迟链数组20等校可以得到八相位(i,q,ib,qb,hq,hqb,hqq,hqqb),也就是输入四个相位,输出八个相位。如图8(b)所示,如果延迟链的延迟过多,使得hq和i相差超过45度,假设是相差48度,同理hqq和q也会相差48度。(因为hq/hqqb和i在此不是相差45度的关系,所以用hq’/hqqb’表示)。

37.如图8所示为校准电路30的实现方式,用与门和低通滤波器去取出这个相位差的关系。假设hq和i相差超过45度,那也代表hqqb和i相差小于45度,故我们可以把i和hq通过一个与门,后面接一个低通滤波器,得到一个控制信号up_dc;再把i和hqqb通过一个与门,后面接一个低通滤波器,得到一个控制信号dn_dc。如果dn_dc》up_dc,代表延迟时间过长,需要把延迟链的延迟缩短,才可以得到准确的正交信号。

38.完整的八相位本地震荡信号产生器如图9所示,如上所述,我们使用不同与门将i/hq,ib/hqb,q/hqq,qb/hqqb,本来应该互为领先(hq领先i;hqb领先ib,hqq领先q;hqqb领先qb)的电压信号做逻辑运算,通过低通滤波器得到up_dc;再使用不同与门将i/hqqb,ib/hqq,q/hq,qb/hqb,本来应该互为落后(hqqb落后i;hqq落后ib;hq落后q;hqb落后qb)的电压信号做逻辑运算,通过低通滤波器得到dn_dc,通过op1和低通滤波器得到v1信号,v1信号和参考电压vref通过op2,即可产生ib1的控制电压i_ctrl,去调整延迟链数组20的延迟时间,使得延迟链数组20的延迟时间能准确的让q和i相差90度,完成八相位信号产生的目的。

39.以上是对本实用新型的较佳实施进行了具体说明,但本实用新型创造并不限于所述实施例,熟悉本领域的技术人员在不违背本实用新型精神的前提下还可做出种种的等同变形或替换,这些等同的变形或替换均包含在本技术权利要求所限定的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。