1.本发明涉及噪声非相干时钟源电路领域,更具体涉及一种数字阵列雷达噪声非相干时钟源。

背景技术:

2.相控阵雷达技术在经历了无源相控阵、有源相控阵两个阶段后,迎来了数字阵列雷达时代,该项技术以数字t/r组件和数字波束形成(dbf)为典型特征,通过相位补偿在数字域实现多通道矢量合成,数字阵列雷达在低副瓣,抗干扰、处理灵活等方面具有明显优势。

3.随着对数字阵列雷达技术的不断深入研究,雷达的合成信噪比得益越来越受到关注,经过多年探索研究,时钟源的相噪特性、抖动特性、噪声非相干特性成为非常重要的制约因素。长期以来,相控阵雷达中采用的是集中式时钟源产生方式,实践表明,在这种方式下相干噪声占时钟源组合噪声中的主导因素,大阵面数字阵列雷达在进行多通道合成时无法得到预期的信噪比得益。

4.专利公开号cn1196608(cn1105420c),公开了同步数字微波设备的数字处理锁相环,数字处理锁相环,通过分散相位控制周期使网络稳定地开始同步,包括:基准时钟接收单元,接收作为基准时钟的8千赫信号;相位比较器,比较基准时钟与自同步反馈时钟;相位控制单元,作相位控制,输入相位检测信息,并进行环通滤波以抑制抖动,输出16位数据;信号转换器,将16位数据转换成模拟信号;vco(压控振荡器),输入模拟信号工作;分频器,划分vco输出频率,反馈分频频率,向相位比较器输出8千赫的自同步信号。该专利申请目的是通过将相位控制的周期分散开来提供网络起始同步装置结构稳定的一种数字处理锁相环,提供一种在定时状态和基准交换状态下供相位校准用的数字处理锁相环,并不涉及相干噪声的处理。

技术实现要素:

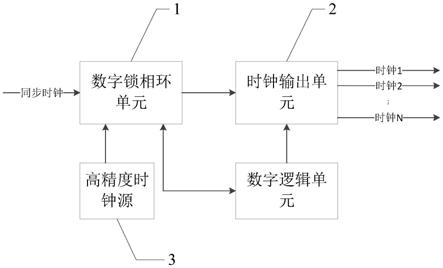

5.本发明所要解决的技术问题在于现有技术时钟源的相干噪声占时钟源组合噪声中的主导因素,大阵面数字阵列雷达在进行多通道合成时无法得到预期的信噪比得益。

6.本发明通过以下技术手段实现解决上述技术问题的:一种数字阵列雷达噪声非相干时钟源,包括数字锁相环单元(1)、时钟输出单元(2)及高精度时钟源(3),所述数字锁相环单元(1)将同步时钟与输出端反馈回来的时钟比较得到相位差以后转换为时钟补偿信号,将该时钟补偿信号与高精度时钟源(3)输出的高精度时钟叠加输出给时钟输出单元(2),时钟输出单元(2)接收数字锁相环单元(1)输出的时钟信号并进行分频处理,输出多路时钟,高精度时钟源(3)为数字锁相环单元(1)提供采样时钟。

7.本发明时钟输出与同步时钟有耦合关系,同步时钟发生变化,输出时钟也有一定的变化,将同步时钟与输出端反馈回来的时钟比较得到相位差以后转换为时钟补偿信号,将该时钟补偿信号与高精度时钟源(3)输出的高精度时钟叠加输出给时钟输出单元(2),输

出时钟的频率与同步时钟相关,而输出噪声与输入噪声非相关,应该本发明的噪声源将改变组合噪声比例,使时钟信号输出的非相干噪声占主导因素,以此为基础,经过数字域合成处理,将大幅提高大型数字阵列雷达的合成信噪比得益,提升其战技术性能,应用前景十分广阔。

8.进一步地,所述数字锁相环单元包括相差检测子单元(11)、数字环路滤波器(12)、反馈除法器(13)、钳位记录电路(14)、数字逻辑单元以及信号转换子单元(15),所述相差检测子单元(11)检测反馈除法器(13)与同步时钟之间的绝对时间差,将绝对时间差映射为相位差,数字环路滤波器(12)接收相位差并滤除干扰,钳位记录电路(14)保持记录数字环路滤波器(12)的历史输出并将相位差转换为相位码或者频率码作为时钟补偿信号输出给数字逻辑单元,所述数字逻辑单元将高精度时钟源(3)输出的高精度时钟与时钟补偿信号叠加得到逻辑计算结果,信号转换子单元(15)将逻辑计算结果转化为模拟信号以后输出时钟给时钟输出单元(2)并将输出时钟反馈给反馈除法器(13),反馈除法器(13)将输出时钟按照预设比例调整为低频信号后反馈给相差检测子单元(11)。

9.更进一步地,所述相差检测子单元(11)包括时间数字化器和相位频率检测器,所述时间数字化器检测反馈除法器(13)与同步时钟之间的绝对时间差转换为数字信号输出给相位频率检测器,相位频率检测器将数字信号的绝对时间差转换为相位差。

10.更进一步地,所述信号转换子单元(15)包括直接数字合成器和数模转换器,直接数字合成器接收数字逻辑单元的逻辑计算结果转换为数字信号波形,数模转换器将数字信号波形转化为模拟信号波形以后输出时钟给时钟输出单元(2)并将输出时钟反馈给反馈除法器(13)

11.更进一步地,所述数字锁相环单元(1)还包括保持逻辑电路(16),所述保持逻辑电路(16)判断数字环路滤波器(12)输出的相位差是否超出门限,如果超过门限则控制钳位记录电路(14)开启,将相位差转换为相位码或者频率码输出给信号转换子单元(15)。

12.更进一步地,所述数字锁相环单元(1)还包括相位控制器(17),所述相位控制器(17)对钳位记录电路(14)输出的相位差进行比例调整,从而对信号转换子单元(15)输出时钟微调。

13.更进一步地,所述相差检测子单元(11)包括时序产生器(111)、门控环路振荡器(112)、状态寄存器(113)、测量单元(114)及加法器(115),所述时序产生器(111)产生使能信号控制门控环路振荡器(112)的启停并输出时钟给状态寄存器(113)、测量单元(114)以及加法器(115),门控环路振荡器(112)接收同步时钟以及反馈除法器(13)反馈的信号后与基准时钟进行比较,分别计算同步时钟相比基准时钟在一个时间间隔内跳转次数a1,计算反馈除法器(13)反馈的信号相比基准时钟在一个时间间隔内跳转次数a2,状态寄存器(113)存储门控环路振荡器(112)的比较和计数结果,测量单元(114)将状态寄存器(113)存储的同一时间间隔内跳转次数a1与跳转次数a2相减然后乘以每个跳转次数对应的时间得到同一时间间隔内反馈除法器(13)与同步时钟之间的时间差,加法器(115)将测量单元(114)计算的所有单个时间间隔内的时间差叠加得到反馈除法器(13)与同步时钟之间的绝对时间差,相位频率检测器将绝对时间差映射为相位差后输出给数字环路滤波器(12)。

14.本发明的优点在于:本发明时钟输出与同步时钟有耦合关系,同步时钟发生变化,输出时钟也有一定的变化,将同步时钟与输出端反馈回来的时钟比较得到相位差以后转换

为时钟补偿信号,将该时钟补偿信号与高精度时钟源(3)输出的高精度时钟叠加输出给时钟输出单元(2),输出时钟的频率与同步时钟相关,而输出噪声与输入噪声非相关,应该本发明的噪声源将改变组合噪声比例,使时钟信号输出的非相干噪声占主导因素,以此为基础,经过数字域合成处理,将大幅提高大型数字阵列雷达的合成信噪比得益,提升其战技术性能,应用前景十分广阔。

附图说明

15.图1为本发明实施例所公开的一种数字阵列雷达噪声非相干时钟源的结构框图;

16.图2为本发明实施例所公开的一种数字阵列雷达噪声非相干时钟源中数字锁相环单元的结构示意图;

17.图3为本发明实施例所公开的一种数字阵列雷达噪声非相干时钟源中相差检测子单元的结构示意图。

具体实施方式

18.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

19.如图1所示,一种数字阵列雷达噪声非相干时钟源,包括数字锁相环单元1、时钟输出单元2及高精度时钟源3,所述数字锁相环单元1将同步时钟与输出端反馈回来的时钟比较得到相位差以后转换为时钟补偿信号,将该时钟补偿信号与高精度时钟源3输出的高精度时钟叠加输出给时钟输出单元2,时钟输出单元2接收数字锁相环单元1输出的时钟信号并进行分频处理,输出多路时钟,高精度时钟源3为数字锁相环单元1提供采样时钟。

20.如图2所示,所述数字锁相环单元1包括相差检测子单元11、数字环路滤波器12、反馈除法器13、钳位记录电路14、数字逻辑单元以及信号转换子单元15,所述相差检测子单元11检测反馈除法器13与同步时钟之间的绝对时间差,将绝对时间差映射为相位差,数字环路滤波器12接收相位差并滤除干扰,数字环路滤波器12是一个三级无限长滤波器,钳位记录电路14保持记录数字环路滤波器12的历史输出并将相位差转换为相位码或者频率码作为时钟补偿信号输出给数字逻辑单元,所述数字逻辑单元将高精度时钟源3输出的高精度时钟与时钟补偿信号叠加得到逻辑计算结果,信号转换子单元15将逻辑计算结果转化为模拟信号以后输出时钟给时钟输出单元2并将输出时钟反馈给反馈除法器13,反馈除法器13将输出时钟按照预设比例调整为低频信号后反馈给相差检测子单元11。

21.所述相差检测子单元11包括时间数字化器和相位频率检测器,所述时间数字化器检测反馈除法器13与同步时钟之间的绝对时间差转换为数字信号输出给相位频率检测器,相位频率检测器将数字信号的绝对时间差转换为相位差。

22.所述信号转换子单元15包括直接数字合成器和数模转换器,直接数字合成器接收数字逻辑单元的逻辑计算结果转换为数字信号波形,数模转换器将数字信号波形转化为模拟信号波形以后输出时钟给时钟输出单元2并将输出时钟反馈给反馈除法器13

23.继续参阅图2,所述数字锁相环单元1还包括保持逻辑电路16,所述保持逻辑电路

16判断数字环路滤波器12输出的相位差是否超出门限,如果超过门限则控制钳位记录电路14开启,将相位差转换为相位码或者频率码输出给信号转换子单元15。

24.继续参阅图2,所述数字锁相环单元1还包括相位控制器17,所述相位控制器17对钳位记录电路14输出的相位差进行比例调整,从而对信号转换子单元15输出时钟微调。

25.如图3所示,所述相差检测子单元11包括时序产生器111、门控环路振荡器112、状态寄存器113、测量单元114及加法器115,所述时序产生器111产生使能信号控制门控环路振荡器112的启停并输出时钟给状态寄存器113、测量单元114以及加法器115,门控环路振荡器112接收同步时钟以及反馈除法器13反馈的信号后与基准时钟进行比较,分别计算同步时钟相比基准时钟在一个时间间隔内跳转次数a1,计算反馈除法器13反馈的信号相比基准时钟在一个时间间隔内跳转次数a2,状态寄存器113存储门控环路振荡器112的比较和计数结果,测量单元114将状态寄存器113存储的同一时间间隔内跳转次数a1与跳转次数a2相减然后乘以每个跳转次数对应的时间得到同一时间间隔内反馈除法器13与同步时钟之间的时间差,加法器115将测量单元114计算的所有单个时间间隔内(图3中开始信号与停止信号之间的所有时间间隔)的时间差叠加得到反馈除法器13与同步时钟之间的绝对时间差,相位频率检测器将绝对时间差映射为相位差后输出给数字环路滤波器12。

26.通过以上技术方案,本发明时钟输出与同步时钟有耦合关系,同步时钟发生变化,输出时钟也有一定的变化,将同步时钟与输出端反馈回来的时钟比较得到相位差以后转换为时钟补偿信号,将该时钟补偿信号与高精度时钟源3输出的高精度时钟叠加输出给时钟输出单元2,输出时钟的频率与同步时钟相关,而输出噪声与输入噪声非相关,应该本发明的噪声源将改变组合噪声比例,使时钟信号输出的非相干噪声占主导因素,以此为基础,经过数字域合成处理,将大幅提高大型数字阵列雷达的合成信噪比得益,提升其战技术性能,应用前景十分广阔。

27.以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。