技术特征:

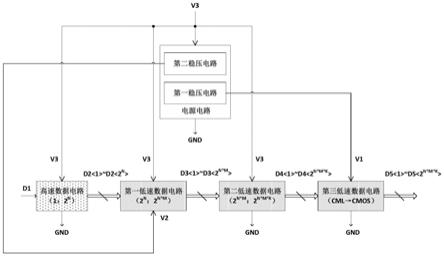

1.一种异质集成串并转换电路,其特征在于,所述异质集成串并转换电路包括:高速数据电路、第一低速数据电路和电源电路,所述高速数据电路由电子迁移率高于预定阈值的半导体材料制成,所述第一低速数据电路基于硅基深阱工艺制成;所述高速数据电路的工作电压为v3,所述高速数据电路的供电电压连接电压源,所述电压源的电压值为v3,所述高速数据电路的衬底电压连接参考地电位,所述高速数据电路用于将高速串行数据转换为多路中低速并行数据输出;所述第一低速数据电路的工作电压为v1,所述第一低速数据电路的供电电压连接所述电压源,所述电源电路连接所述电压源并给所述第一低速数据电路提供电压值为v2的衬底电压,v3=v1 v2;所述第一低速数据电路用于将所述高速数据电路输出的每路中低速并行数据转换为多路低速并行数据输出;其中,高速串行数据、中低速并行数据、低速并行数据的数据传输速率依次降低。2.根据权利要求1所述的异质集成串并转换电路,其特征在于,所述高速数据电路和所述第一低速数据电路均采用电流模式逻辑cml传输数据,所述第一低速数据电路输出的低速并行数据与接收到的中低速并行数据的摆幅和共模电平分别相等。3.根据权利要求1所述的异质集成串并转换电路,其特征在于,所述异质集成串并转换电路还包括基于硅基工艺制成的第二低速数据电路,所述第二低速数据电路的工作电压为v3,所述第二低速数据电路的供电电压连接所述电压源,所述第二低速数据电路的衬底电压连接参考地电位;所述第二低速数据电路也采用电流模式逻辑cml传输数据,所述第二低速数据电路用于将所述第一低速数据电路输出的每路低速并行数据转换为多路差分并行数据,输出的差分并行数据的数据传输速率低于接收到的低速并行数据,且输出的差分并行数据与接收到的低速并行数据的摆幅和共模电平分别相等。4.根据权利要求3所述的异质集成串并转换电路,其特征在于,所述异质集成串并转换电路还包括基于硅基工艺制成的第三低速数据电路,所述第三低速数据电路用于将所述第二低速数据电路输出的电流模式逻辑cml的每路差分并行数据转换为一路单端cmos电平模式的输出数据。5.根据权利要求4所述的异质集成串并转换电路,其特征在于,所述第三低速数据电路的工作电压为v1,所述电源电路给所述第三低速数据电路提供电压值为v1的供电电压,所述第三低速数据电路的衬底电压连接参考地电位,所述第三低速数据电路输出的输出数据摆幅为v1。6.根据权利要求5所述的异质集成串并转换电路,其特征在于,所述电源电路包括第一稳压电路和第二稳压电路,所述第二稳压电路用于将所述电压源提供的v3转换为v2并提供给所述第一低速数据电路的衬底电压,所述第一稳压电路用于将所述电压源提供的v3转换为v1并提供给所述第三低速数据电路的供电电压。7.根据权利要求6所述的异质集成串并转换电路,其特征在于,在所述第二稳压电路中,第一偏置电流ibias1的正极连接所述电压源提供的电压值v3,所述第一偏置电流ibias1的负极连接pmos管p1的源极和pmos管p2的源极,p1的漏极连接nmos管n1的漏极、n1的栅极以及nmos管n2的栅极,n1的源极接地,n2的源极接地;p2的漏极连接n2的漏极,p2的栅极连接第二参考电压vref2;p2和n2的公共端依次通过第一电阻r1和第一电容c1连接nmos管n3的漏极,n3的源极接

地,n3的栅极连接n2的漏极;pmos管p3的源极连接所述电压源提供的电压值v3,p3的漏极连接n3的漏极并输出电压值v2,p3的漏极还连接p1的栅极,p3的栅极连接使能端en。8.根据权利要求4所述的异质集成串并转换电路,其特征在于,所述第一低速数据电路、第二低速数据电路和第三低速数据电路中分别包括受控于复位信号的复位电路,以调节相连的两个数据电路之间的传输的差分电平模式数据的数据起点。9.根据权利要求8所述的异质集成串并转换电路,其特征在于,所述第一低速数据电路包括第一差分单元和受控于第一复位信号rst1的第一复位电路;在所述第一差分单元中:nmos管n7的漏极通过电阻r14连接所述第一低速数据电路的供电电压,nmos管n8的漏极通过电阻r15连接所述第一低速数据电路的供电电压,n7的源极和n8的源极相连并连接nmos管n9的漏极,n7的栅极和n8的栅极作为一对差分对连接所述高速数据电路,n7的栅极还通过电阻r13连接所述第一低速数据电路的供电电压,n8的栅极还通过电阻r12连接所述第一低速数据电路的供电电压;n7的漏极和n8的漏极作为一对差分对连接所述第二低速数据电路,n7的漏极还连接nmos管n10的漏极以及nmos管n11的栅极,n8的漏极连接n10的栅极和n11的漏极,n10的源极和n11的源极相连并连接nmos管n12的漏极;n9的栅极和n12的栅极连接一对差分时钟,n9的栅极还通过电阻r11连接所述第一低速数据电路的供电电压,n12的栅极还通过电阻r10连接所述第一低速数据电路的供电电压;n12的源极和n9的源极相连并连接第三偏置电流ibias3的正极,所述第三偏置电流ibias3的负极连接所述第一低速数据电路的衬底电压;所述第一复位电路包括第一反相器inv1、pmos管p7、pmos管p8、nmos管n13和nmos管n14,第一复位信号rst1通过所述第一反相器inv1连接p7的栅极,p7的源极、p8的源极和p8的栅极分别连接所述第一低速数据电路的供电电压,p7的漏极连接n7的漏极,p8的漏极连接n8的漏极;n13的漏极连接n7的漏极,n14的漏极连接n8的漏极,n14的栅极连接所述第一复位信号rst1,n13的源极、n13的栅极和n14的源极相连并连接所述第三偏置电流ibias3的正极。10.根据权利要求8所述的异质集成串并转换电路,其特征在于,所述第二低速数据电路和所述第三低速数据电路的电路结构相同,所述第二低速数据电路和所述第三低速数据电路中的任意一个低速数据电路包括第二差分单元和受控于所述低速数据电路的复位信号rst2的第二复位电路:在所述第二差分单元中,nmos管n15的漏极通过电阻r16连接所述低速数据电路的供电电压,nmos管n16的漏极通过电阻r17连接所述低速数据电路的供电电压;n15的源极和n16的源极相连并连接nmos管n17的漏极;n15的栅极和n16的栅极作为一对差分对获取输入的数据,n15的漏极和n16的漏极作为一对差分对输出数据;n15的漏极连接nmos管n18的漏极和nmos管n19的栅极,n16的漏极连接n18的栅极和n19的漏极,n18的源极和n19的源极相连并连接nmos管n20的漏极,n20的源极和n17的源极相连并连接第四偏置电流ibias4的正极,所述第四偏置电流ibias4的负极连接所述低速数据电路的衬底电压;n17的栅极和n20的栅极连接一对差分时钟;所述第二复位电路包括第二反相器inv2、第三pmos管p9、pmos管p10、nmos管n21和nmos管n22,第二复位信号rst2通过所述第二反相器inv2连接p9的栅极,p9的源极、p10的栅极和

p10的源极分别连接所述低速数据电路的供电电压,p9的漏极连接n15的漏极,p10的漏极连接n16的漏极;n21的漏极连接n15的漏极,n22的漏极连接n16的漏极,n22的栅极连接所述第二复位信号rst2,n21的源极、n21的栅极和n22的源极相连并连接所述第四偏置电流ibias4的正极。

技术总结

本发明公开了一种异质集成串并转换电路,涉及串并转换电路领域,该异质集成串并转换电路将不同工艺区间的电路集成在一起并解决了互相之间的电平转换难题,可以将一路高速串行数据转换为多路低速的并行数据,该电路由高速数据电路实现高速数据的传输与处理,低速数据电路实现多通道、中低速率的数据传输与处理,使得该异质集成电路可以实现接口处的高速数据传输,同时又可以降低整个系统的成本与功耗。耗。耗。

技术研发人员:涂波 杨煜 王澧 李成

受保护的技术使用者:中国电子科技集团公司第五十八研究所

技术研发日:2021.12.17

技术公布日:2022/4/1

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。