1.本发明涉及生产由氮化物(n)制成的台面,该氮化物优选地从选自镓(ga)、铟(in)和铝(al)中的至少一种材料获得。本发明的一个示例性应用是在包括多个微型发光二极管(led)的光电器件的领域,该微型发光二极管一般称为micro-led。在这个领域中,本发明的一个特别有利的用途是生产一般被称为微型显示器的小型显示器。

现有技术

2.基于micro-led的光电器件包括由彼此间隔开的多个micro-led叠覆的基板。这些光电器件通常是通过执行下面简要描述的步骤来形成的,并在图1a和图1b中示意性地例示。

[0003]-第一步骤在于获得氮化物层500,通常是氮化镓(gan)层。这种类型的氮化物通常是通过从结晶层300外延生长来获得的。这个步骤在图1a中示出。

[0004]-第二步骤在于在结晶层300上的全晶圆外延生长氮化物层500中对台面550a-550e进行空间界定。这种空间界定是例如通过rie(反应性离子蚀刻)10来执行的。这些台面550a-550e中的每一者用于形成micro-led 570a-570d。为此目的,例如可以在台面550a-550e中的每一者中产生量子阱590,以形成micro-led 570a-570d。

[0005]

这些光电器件的一个缺点是,这些micro-led的外量子效率高度依赖于micro-led的大小。这清楚地示出在图2a的图表中。该图表清楚地示出,随着micro-led大小的减小,外量子效率也减小。这种效率下降对于侧向尺寸小于50μm(10-6

米)的micro-led来说尤其明显,该侧向尺寸是指具有方形或矩形顶面的micro-led的两侧长度。因此,micro-led的顶面的两侧长度决定了该顶面的周长。

[0006]

图2b是侧向尺寸为7μm的micro-led在室温下记录的阴极发光图像。该图清楚地示出,micro-led的这种效率下降与led边缘的发光降低有关。图2c是比较300k(开尔文)和8k温度下的阴极发光曲线的图。该图清楚地示出,随着温度的升高,在micro-led边缘处,处于低温的激子向非辐射复合中心离域(delocalised)。

[0007]

随着与micro-led大小的倒数近似成比例的周长面积比(perimeter-to-area ratio)增加,这种边缘效应变得更加重要。这从图2d中很明显。该图示出了肖克莱-雷德-霍尔(srh)复合参数a根据该周长面积比的变化。

[0008]

这种边缘效应很可能与蚀刻10留下的缺陷有关,该蚀刻意在于其基板300上的全晶圆外延生长层500中对各个台面550a-550e进行空间界定。更具体地,蚀刻10,例如rie类型的蚀刻,改变了意在形成每个micro-led 570a、570b的台面550a-550e的周缘。这些改变区域在图1c中被给出附图标记520a、520b,该图1c是图1b中参考的区域a的放大图。在micro-led 570a-570d中形成的量子阱590处,这些非辐射缺陷捕获了载流子,阻止载流子进行辐射复合,这降低了micro-led 570a-570d的效率。

[0009]

为解决这个问题,已经提出了几个解决方案。

[0010]

第一种可能的解决方案在于,通过生产具有接近像素间距的表面积并具有使p/s

比最小化的几何形状的的micro-led来优化像素的可用表面积,p是像素间距,以及s是与像素相关的micro-led的表面积。这种解决方案的一个缺点是,像素的接近增加了像素之间的所谓串扰效应。

[0011]

第二种解决方案在于,强制将载流子注入micro-led的中心,使得载流子不能扩散到micro-led的边缘。为此目的,可以提供p型接触件,使其不占据gan的形成micro-led的整个表面积。这要求gan中载流子的扩散长度小于p型接触部的边缘与像素边缘之间的距离。因此,载流子不会到达像素的边缘。然而,这种解决方案的缺点是造成发射表面积的明显损失,尤其是在micro-led的情况下。对于相同的表面积,具有这些micro-led的显示器将因此具有较低的光强度。

[0012]

通常,已知蚀刻技术会引起问题。其不利影响涉及多个方面:表面粗糙化、与所用气体的化学性质有关的化学污染、与氮空位有关的水平等等。特别地,已经示出了p-掺杂(mg)gan表面受到icp蚀刻(电感耦合等离子体蚀刻)的影响,这使得靠近表面的区域中受体的浓度明显下降。这在由cao等人发表在appl.phys.lett.75,2569,(1999)上的题为“electrical effect of plasma damage in p-gan induced by reactive ion etching”的出版物中得到了特别的解释。

[0013]

也有研究示出,rie或icp蚀刻会在gan间隙中引起陷阱能级。这在pss.a 2017,1700633的kodera等人发表“impact of plasma damaged layer removal on gan hemt devices”的出版物中得到了特别的说明。在受干法蚀刻影响的区域中,氧浓度也增加了3倍,这可能是由于表面层的氧化,与氮亚化学计量的出现有关。此外,表面区域在几纳米(10-9

米)范围内变成非晶态。kodera等人发表的同一出版物示出,适当的蚀刻后化学处理减少了蚀刻的负面影响。然而,sims分析(二次离子质谱法)示出,对由蚀刻引起的表面杂质的移除并不完全。

[0014]

还研究了rie的影响,以确定是否可以重新加工蚀刻表面上的接触件。在蚀刻的表面上似乎不可能获得电阻与应用兼容的p型接触件。rta(快速热退火)改善了接触,然而并没有恢复欧姆接触。在j.of the electrochemical society 149no.7(g367-g369)2002的chang等人发表的“the variation of ohmic contacts and surface characteristics”的出版物中尤其示出了这点。

[0015]

为了克服micro-led的这些问题,可以实施对蚀刻的侧壁进行钝化的方法。这些方法在于,在蚀刻的侧壁上沉积sio2型层,以防止在台面550a-550e的边缘上发生任何非辐射复合。除了这应该与消除(仅部分地消除)缺陷区域的初步化学处理有关的事实外,这增加了难以控制的额外技术步骤。这趋于大大增加生产micro-led的复杂性和成本。

[0016]

如上所述,用于形成由优选地从选自镓(ga)、铟(in)和铝(al)中的至少一种材料获得的氮化物(n)制成的台面的已知解决方案在这些台面被用来形成micro-led时会产生许多问题。当这些台面被用于生产功率电子器件诸如功率晶体管、例如hemt(高电子迁移率晶体管)时,这些已知的解决方案进一步产生了问题。实际上,用于生产台面的这些已知解决方案使得hemt的电气性能水平相对较低。

[0017]

因此,有必要限制或甚至消除已知解决方案的缺点。本发明的目的特别是为这个问题提供解决方案。

[0018]

本发明的另一目的是提供一种用于在基板表面上获得多个亮度提高和/或分辨率

非常高的micro-led的解决方案。

[0019]

本发明的另一目的是提供一种用于提高功率器件例如hemt的电气性能水平的解决方案。

[0020]

本发明的其他目的、特点和优点将在阅读以下描述和附图后显现。可以理解的是,其他优点也可以结合在其中。

技术实现要素:

[0021]

为了达到这个目的,根据一个实施方式,本发明提供了一种用于获得多个台面的方法,每个台面意在形成电子或光电器件。每个台面至少部分由氮化物(n)制成,该氮化物优选地从选自镓(ga)、铟(in)和铝(al)的至少一种材料获得。

[0022]

该方法包括以下连续步骤:

[0023]-提供叠置件,该叠置件包括基板和从基板起连续地布置的至少以下各层:

[0024]

■

第一层,该第一层称为流变层,该流变层由具有玻璃化转变温度的材料制成,该流变层具有玻璃化转变温度t

玻璃化转变

,

[0025]

■

第二结晶层,被称为结晶层,其与流变层不同,

[0026]-通过对至少结晶层以及流变层的至少一部分进行蚀刻来形成垫,使得:

[0027]

○

每个垫包括至少:

[0028]

■

第一部分,该第一部分称为流变部分,由流变层的至少一部分形成,

[0029]

■

第二结晶部分,称为结晶部分,由结晶层形成并叠覆在流变部分上,

[0030]

○

垫分布在基板上,以形成多组垫,

[0031]-使位于所述垫的至少一些垫上的微晶进行外延生长,并且:

[0032]

■

继续微晶的外延生长,直到同一组的相邻垫所承载的微晶聚结以在每组上形成氮化物台面,

[0033]

■

在属于两个单独组的微晶开始聚结之前,中断微晶的外延生长,使得每组的台面彼此分开。

[0034]

因此,所提出的方法提供了用于在叠置件中蚀刻的成组的垫上产生氮化物(例如gan)台面,该叠置件包括流变层和意在用于氮化物外延生长的结晶层。在氮化物的外延生长期间,在同一组垫的垫顶部处形成的微晶聚集在一起以形成台面,台面中的每个台面意在形成光电器件诸如例如micro-led,或形成电子器件诸如功率晶体管,例如hemt类型的功率晶体管。

[0035]

如下文将详细描述的,使用这些垫阵列允许外延形成具有几乎没有位错或无位错的氮化物台面。更具体地,使用成组垫使得可以从某些垫材料在外延温度下的流变特性中获益,以便使通过悬空外延从相邻的垫上生长的氮化物微晶对准以形成台面,而不形成聚结缺陷。

[0036]

更具体地,在外延期间,垫的由流变部分形成的部分达到(或超过)其玻璃化转变温度或非常接近该玻璃化转变温度的温度。在机械应力的作用下,垫的这部分可以因此变形。因此,当由同一组垫支撑的两个微晶接触并聚结时,由这种接触产生的机械应力会转移到垫,并因此转移到流变部分。该流变部分变形,从而吸收了部分或全部的机械应力。因此,可以大大减少或者甚至防止在形成氮化物台面的微晶之间的聚结边界处的位错的发生和

传播。

[0037]

特别地,如果微晶在基板主要所在的平面内相对于彼此错取向(称为“扭转”)或在该平面外相对于彼此错取向(称为“倾斜”),微晶之间的错位取向会使得在聚结期间产生晶界。这种晶界是高能的,因为晶界是由构成晶界的缺陷的应力场的叠加而成的。如果微晶生长在所述方法允许的可以变形的垫上,那么相邻的微晶就会变成在平面内或平面外取向,从而使系统的总能量最小化而不会形成晶界。相反,如果微晶生长在不能变形的垫上(如悬空外延或elog(外延侧向过生长)类型的现有技术方法的情况),则会形成晶界并出现位错。

[0038]

因此,所描述的方法提供了一种解决方案,该解决方案显然与上文介绍的所有现有技术解决方案相反,现有技术解决方案提供了通过蚀刻从通过外延获得的初始公共层中界定台面。所提出的方法使得可以完全省去用于界定台面的任何蚀刻步骤。此外,如上所述,这种蚀刻步骤大大阻碍了micro-led的效率。此外,为减少但不是消除这种蚀刻的缺点而开发的解决方案使方法相当复杂,并造成了其他缺点。因此,在本发明范围内提出的解决方案是基于一种简单且容易再现的方法,这使得可以获得没有被蚀刻方法改变并且没有或很少有与聚结边界有关的缺陷的台面。因此,本发明使得可以相当大地增加从这些台面获得的micro-led的效率。

[0039]

因此,这种解决方案允许提高由这些micro-led产生的高分辨率显示器的亮度。更具体地,它允许获得具有非常小尺寸的micro-led。台面的尺寸是由垫阵列决定的。使用这种方法可以生产出几μm到几百μm(10-6

米)的台面。

[0040]

这些gan台面的位错密度小于或约为1至2 10e8/cm2。量子阱的辐射效率非常高。

[0041]

为生产垫阵列而实施的方法的精度将至少部分地决定micro-led的最小可能尺寸,并因此决定包括这些micro-led的显示器的分辨率。例如,对于通过纳米压印和电子束光刻生产的垫阵列,可以实现50nm的垫大小以及150-200nm的周期。因此,可以获得1μm至2μm的台面大小。这与高分辨率微显示器(通常称为μ显示器)所寻求的像素大小相对应。

[0042]

此外,这种方法允许直接生产micro-led,每个micro-led的大小与台面的初始大小相对应,特别是如果在这些氮化物台面上构建了量子阱异质结构,每个micro-led的大小与台面的初始大小相对应。

[0043]

因此,所提出的方法允许获得大小非常小且亮度高的micro-led。因此,这种方法对于生产高分辨率、高亮度的显示器特别有利。

[0044]

还可以实施所提出的方法以获得用于制造功率电子器件的台面,诸如例如hemt类型的晶体管。所获得的台面具有较低的位错率和改进的结晶质量,从而提高了功率器件的电气性能水平。

[0045]

因此,本发明允许从选自镓(ga)、铟(in)和铝(al)的至少一种材料获得的氮化物(n)层,其位错密度明显降低。

[0046]

因此,根据本发明的方法为与聚结引起的缺陷的产生有关的问题提供了特别有效的解决方案。这种方法,特别是当应用于在soi(绝缘体上的硅)类型的基板上生产的、具有纳米级尺寸的微晶时,会使聚结引起的缺陷的密度非常明显地降低,允许生产出具有非常低的位错密度的伪基板。

[0047]

本发明的另一方面涉及一种用于形成多个发光二极管(led)的方法,该方法至少包括以下连续的步骤:

[0048]-形成多个台面,每个台面用于形成led,多个台面是通过实施上文所述的方法获得的,

[0049]-在台面中产生以下中的至少一者:

[0050]

○

至少一个p/n结,

[0051]

○

至少一个量子阱。

[0052]

本发明的另一方面涉及一种微电子器件,该器件包括由多个台面叠覆的基板,每个台面由氮化物(n)制成,该氮化物优选地从选自镓(ga)、铟(in)和铝(al)的至少一种材料获得。该器件还包括多个垫,该垫在基板和多个台面之间延伸,每个台面由所述多个垫中的成组的垫完全支撑。

[0053]

每个垫至少包括:

[0054]-第一部分,该第一部分被称为流变部分,具有玻璃化转变温度t

玻璃化转变

,

[0055]-第二部分,该第二部分称为结晶部分,由结晶材料形成,流变部分和结晶部分从基板连续地布置。

[0056]

选择流变部分的材料以及制成台面的所述氮化物,使得:

[0057]

t

外延

≥k1

×

t

玻璃化转变

,其中k1=0.8,

[0058]

t

外延

是指对于制成台面的所述氮化物进行外延成形而言的最低温度。

[0059]

因此,每个台面包括连续的氮化物(n)层或由连续的氮化物层形成,该氮化物优选地从选自镓(ga)、铟(in)和铝(al)的至少一种材料获得。在外延生长期间,即在台面的形成期间,每个台面都由垫完全支撑。

[0060]

本发明的另一方面涉及一种光电系统,该光电系统包括上文所述的微电子器件,其中,至少一些台面并且优选地每个台面部分地形成至少一个发光二极管(led)。

[0061]

本发明的另一方面涉及一种包括上述微电子器件的系统,其中,至少一些台面并且优选地每个台面部分地形成至少一个晶体管,优选地晶体管为高电子迁移率晶体管(hemt)。

附图说明

[0062]

在阅读本发明的一个实施方式给出的详细描述后将更好地理解本发明的目标、目的、特点和优点,实施方式借助于以下附图进行说明,其中:

[0063]

图1a至图1c示出了用于生产micro-led的现有技术方法的步骤。

[0064]

图1a示出了包括连续氮化物层的起始叠置件。

[0065]

图1b示出了用于以连续层构造独立的台面的蚀刻步骤。

[0066]

图1c是图1a的放大图,其示出由蚀刻产生的缺陷区域。

[0067]

图2a至图2c示出了使用现有技术解决方案获得的micro-led解决方案的缺点。

[0068]

图2a是示出了led根据led大小变化的量子效率的图表。

[0069]

图2b是micro-led的阴极发光图像,其清楚地示出,这些led的效率下降与led边缘的较少发光有关。

[0070]

图2c是对两个不同温度下的阴极发光曲线进行比较的图表。

[0071]

图2d是示出肖克莱-雷德-霍尔(srh)复合参数a随micro-led的周长面积比变化的图表。

[0072]

图3a至图3f示出了根据基于本发明方法的非限制性示例的方法的步骤。

[0073]

图3a示出了叠置件的一个示例,根据本发明的示例性方法可以通过叠置件的示例来实现。

[0074]

图3b示出了图3a中的叠置件,在该叠置件上形成有种子层。

[0075]

图3c示出了根据图3a中的叠置件或根据图3b中的叠置件形成成组的垫的步骤的结果。

[0076]

图3d示出了微晶在垫顶部上外延生长的阶段,该生长阶段是不完整的。

[0077]

图3e示出了微晶外延生长的结果,在同一组的垫所承载的微晶聚结后,同一组的垫所承载的微晶由此形成氮化物台面。

[0078]

图3f示出了在每个氮化物台面内产生多量子阱的可选步骤。

[0079]

图4a是通过扫描电子显微镜(sem)获得的照片,其示出了对使用根据本发明的方法获得的多个台面进行支撑的基板。

[0080]

图4b至图4d是通过扫描电子显微镜(sem)获得的照片,其放大倍数比图4中的放大倍数高,并且示出了使用根据本发明的方法获得的不同大小的台面。

[0081]

图5a从俯视角度示意性地示出了在常规的悬空外延方法的范围内两个微晶的聚结。

[0082]

图5b从俯视角度示意性地示出了在根据本发明的示例性方法的范围内两个微晶的聚结。

[0083]

图5c和图5d从侧面角度示意性地示出了根据本发明的示例性方法的范围内两个微晶的聚结过程。

[0084]

图5c示出了在两个微晶聚结之前发生的第一阶段。

[0085]

图5d示出了在两个微晶聚结期间或之后发生的第二阶段。

[0086]

图6是通过sem获得的照片,其示出了通过实施根据本发明的示例性方法获得的由微晶叠覆的垫。

[0087]

图7a和图7b是通过sem获得的照片,其示出了在实施根据本发明的方法后通过外延获得的氮化物台面。

[0088]

图8a至图8c是通过sem获得的照片,其示出了根据本发明的方法的范围内微晶的形成。

[0089]

图9是通过透射电子显微镜(tem)获得的照片,其示出了由聚结形成的台面的截面图。

[0090]

图10是使用根据本发明的方法聚结的微晶的照片,该照片通过sem在“阴极发光”(cl)模式下从俯视角度获得。

[0091]

图11a和图11b是通过扫描电子显微镜(sem)获得的照片以及示出已知方法结果的图,其中,成核层中的缺陷穿过整个最终层。

[0092]

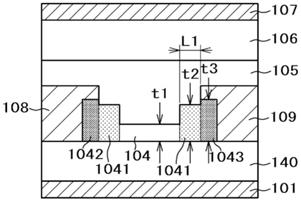

图12a至图12o示出了用于从由垫支撑的氮化物台面上生产led的示例性方法中的步骤,通常是生产micro-led的示例性方法中的步骤。

[0093]

图13a至图13c示意性地示出了通过实施上文所述方法的原理获得的微电子器件的若干示例,例如hemt类型的竖向晶体管。

[0094]

图14a至图14b示意性地示出了在相同晶圆上从由垫支撑的氮化物台面上生产的

晶体管的示例。

[0095]

图15a至图15d示意性地示出了用于在晶圆上从用垫支撑的氮化物台面上生产晶体管的示例性方法中的步骤,该晶体管例如为hemt类型的竖向晶体管。

[0096]

图16a示出了承载晶体管的图15d中晶圆的俯视图。

[0097]

图16b示出了在用于对源极、漏极和栅极进行连接的电气轨道制作完成后承载晶体管的图15d中的晶圆的俯视图。

[0098]

图17示出了根据图15d和图16a所示的替代性实施方式的承载晶体管的晶圆的俯视图。

[0099]

图18a至图18c示意性地示出了步骤3d至步骤3f的替代性步骤。图18a至图18c示出了一个实施方式,其中,垫的流变部分在微晶生长之前被减薄。

[0100]

这些图是以示例的方式提供的,并不意在限制本发明的范围。附图是意在便于理解本发明的示意图,因此不一定符合实际应用的比例尺。特别地,不同层、部分、微晶和台面的相对厚度并不表示实际情况。

具体实施方式

[0101]

在对本发明的实施方式进行详细评述之前,下面列出了可选的特征,这些特征可以相互结合使用或相互替代。

[0102]

根据一个示例,同一组的两个相邻垫之间的距离d小于两个不同组的两个相邻垫之间的距离w1。w1》d,并且优选地w1≥2

×

d。

[0103]

优选地w1≥k4

×

d,其中k4=1.5,并且优选地k4=2。这样允许小的像素尺寸以及高的集成密度。优选地k4=5。w1可以等于1.5微米。

[0104]

根据一个示例,每个垫的截面具有被包括在10nm至500nm(10-9

米)之间的最大尺寸d

垫

,该最大尺寸d

垫

是在与基板顶面主要延伸所沿的平面(xy)平行的平面中测量的,优选地20nm≤d

垫

≤200nm,并且优选地50nm≤d

垫

≤100nm。

[0105]

根据一个示例,每个台面的截面的最大尺寸d

台面

被包括在0.5至20μm(10-6

米)之间,最大尺寸d

台面

是在与基板顶面主要延伸所沿的平面(xy)平行的平面中测量的,优选地0.8μm≤d

台面

≤3μm,并且优选地1μm≤d

台面

≤2μm。因此,最大尺寸d

台面

对应于台面在与xy-平面平行的平面中的投影的最大尺寸,其中,基板的顶面主要在xy-平面中延伸。

[0106]

根据一个示例,同一组的垫根据周期p

垫

周期性地分布在基板上,其中200nm≤p

垫

≤3000nm,并且优选地其中200nm≤p

垫

≤2000nm,并且优选地200nm≤p

垫

≤500nm。周期p

垫

是在与基板顶面主要延伸所沿的平面(xy)平行的平面中测量的。

[0107]

由于w2是两个相邻的台面550a、550b之间的距离(见图3d中的w2),w2必须非零以使两个相邻的台面550a、550b不互相接触。因此,w2》0。

[0108]

理论上,如果在台面的边缘没有侧向再生长,为了使这两个相邻的台面550a、550b不相互接触(非零w2),w1必须严格大于2(p

垫-d

垫

)/2,即大于p

垫-d

垫

。

[0109]

根据一个示例,w1≥k5

×

w2,其中

[0110]-w1是属于两个独立的组的两个相邻垫之间的距离,

[0111]-w2是两个相邻的台面之间的距离,w2》0。

[0112]

其中k5=1.2,优选地k5=1.5,优选地k5=2。

[0113]

可替代地,同一组的垫以非周期性的方式分布在基板上。可选地但有利地,台面以周期性的方式分布在基板上。

[0114]

根据一个示例,流变层由粘性材料制成。流变层具有粘塑性转变。优选地,该材料选自:

[0115]-氧化硅sixoy,其中x和y是整数,并且优选地流变层由sio2制成,

[0116]-玻璃,

[0117]-硼硅玻璃,

[0118]-硼磷硅玻璃(bpsg)。

[0119]

可选地,外延生长是在温度t

外延

下进行的,使得:t

外延

≥k1

×

t

玻璃化转变

,其中k1≥0.8。

[0120]

根据一个示例,k1=1,并且优选地k1=1.5。根据一个示例性实施方式,k1=0.87或k1=0.9。根据一个特别有利的示例,k1=0.92。因此,在流变部分由sio2形成的情况下,t

外延

≥1104℃,因为sio2的t

玻璃化转变

等于1200℃。根据甚至更优选的示例性实施方式,k1=0.95。根据甚至更优选的示例性实施方式,k1=1,并且优选地k1=1.5。

[0121]

根据一个示例,t

外延

≤k2

×

t

最低熔融

,t

最低熔融

是形成垫的各部分的熔融温度中的最低熔融温度,其中k2≤0.9,并且优选地k2≤0.8。根据示例性实施方式,k2=0.9。这防止了具有最低熔融温度的材料物质扩散。因此,在垫由sio2流变部分和硅微晶部分形成的情况下,t

外延

≤1296℃。更具体地,t

最低熔融

等于硅的熔融温度,因为硅的熔融温度等于1440℃,并且sio2的熔融温度等于1970℃。优选地,k2=0.8。

[0122]

根据一个示例,垫包括叠覆在结晶层上的至少一个缓冲层,至少一个缓冲层由与氮化物台面不同的材料制成。根据该示例,氮化物台面由氮化镓(gan)制成,以及缓冲层由氮化铝(aln)制成。这防止了由镓和硅之间非常高的反应性产生的回熔蚀刻现象。

[0123]

根据一个示例,在通过蚀刻形成垫的步骤之前,通过在结晶层的顶部上进行外延沉积来形成缓冲层。因此,在氮化物台面的外延生长步骤之前,该叠置件至少包括所述缓冲层。在通过于结晶层顶部上形成缓冲层之后通过蚀刻形成多个垫,可以防止缓冲层在垫之间沉积,通常是防止在流变层的底部上沉积,或者可以防止缓冲层在由结晶层形成的各部分的壁上沉积,如果形成缓冲层的该步骤是在蚀刻叠置件以形成垫之后执行的话就会发生这种情况。这防止了氮化物台面从流变层外延生长。当然,当意在形成每个台面的氮化物层的生长是通过选择性外延来进行时,就能观察到这种优势。更具体地,这种生长发生在缓冲层的材料上,而不是流变部分的材料上。当流变部分由sio2制成、缓冲层由aln制成、以及通过外延例如通过movpe(金属有机气相外延)形成的氮化物台面由gan制成时就是这种情况。作为结果,流变部分没有沉积在垫的基部处。

[0124]

根据一个示例,在使氮化物台面进行外延生长的步骤之前,垫包括叠覆在所述缓冲层之上的并由氮化镓(gan)制成的至少一个种子层。

[0125]

根据一个示例,在所述通过蚀刻形成垫的步骤之前,叠置件包括叠覆所述结晶层的至少一个种子层,该种子层由与氮化物台面相同的材料制成。因此,在一个实施方式中,其中氮化物台面是由gan制成,种子层也是由gan制成。有利地,该种子层促进恢复外延生长以形成微晶。当垫顶部的表面积较小时,这个特点尤其有利。

[0126]

根据一个示例,每个垫具有顶面,并且微晶的外延生长至少部分地发生在所述顶面,并且优选地只发生在所述顶面。优选地,缓冲层被设置为直接与微晶部分的顶面接触,

或者与由种子层形成的部分的顶面接触。

[0127]

如果垫的顶部,即垫的未经覆盖的顶面,是由结晶部分形成的,那么微晶被外延生长为直接与结晶层接触。如果垫的顶部是由种子层形成,那么微晶被外延生长为直接与种子层接触。如果垫的顶部是由缓冲层形成,那么微晶被外延生长为直接与缓冲层接触。优选地,种子层被设置为直接与结晶部分的顶面接触。

[0128]

根据一个示例,在外延生长步骤期间,缓冲层和种子层中的至少一者保持恒定的厚度。

[0129]

根据一个示例,提供所述叠置件包括提供绝缘体上硅(soi)类型的精细基板,该基板包括基部基板,在基部基板上由形成所述流变层的氧化物层和形成所述结晶层的半导体层依次叠覆。

[0130]

根据一个示例,流变部分具有高度e

220

,使得e

220

≥0.1

×d垫

,其中d

垫

是垫的直径,或更普遍地是在流变部分处并沿与基板顶面主要延伸所沿的平面(xy)平行的方向测量的垫的边缘到边缘距离,优选地e

220

≥1

×d垫

。这些值促成足够的变形,以减少晶界处的应力。

[0131]

根据一个示例,垫具有高度h

垫

,并且两个相邻的垫以距离d分开,使得:

[0132]h垫

/d《2,并且优选地h

垫

/d≤1。

[0133]

根据一个示例,结晶层是硅基的,并且优选地结晶层是由硅制成。

[0134]

结晶层也可以具有由与si不同的材料制成的基部,并且该材料允许氮化物材料的外延。例如,结晶层可以是sic基或al2o3基。这些材料也可以以sicoi(绝缘体上sic)或sos(蓝宝石上硅)的形式使用。

[0135]

根据一个示例性实施方式,结晶层是单晶层。

[0136]

根据一个示例性实施方式,流变层与基板直接接触。流变层与结晶层直接接触。根据一个示例性实施方式,形成通过微晶聚结制成的每个台面的氮化物层与结晶层直接接触。根据另一实施方式,在结晶层和氮化物层之间设置有至少一个中间层,该中间层是由微晶聚结产生的,并形成台面。该中间层通常形成缓冲层。

[0137]

因此,流变层和结晶层是不同的。流变层具有玻璃化转变温度。因此,流变层是由玻璃化转变材料制成,并呈现出玻璃化转变材料的性能。因此,流变层不是结晶。流变层是由粘性材料或玻璃质材料制成,例如氧化物。流变层和结晶层不是由相同材料制成。

[0138]

根据一个示例性实施方式,流变层的厚度e

220

小于500nm(10-9

米)。该厚度优选地被包括在50nm至500nm之间,并且优选地在100nm至150nm之间。

[0139]

根据一个示例性实施方式,结晶层的厚度被包括在2nm(10-9

米)至10μm(10-6

米)之间,并且优选地在5nm至500nm之间,并且优选地在10nm至50nm之间。

[0140]

根据一个示例性实施方式,晶体在所有所述垫上外延生长。

[0141]

根据一个示例性实施方式,所述材料在外延沉积反应器中的通量(例如以sccm为单位测量的通量)的v/iii比约为2000,该材料包括氮化物(n)和选自镓(ga)、铟(in)和铝(al)的至少一种材料。

[0142]

根据一个示例性实施方式,台面的氮化物是氮化镓(gan)。根据另一实施方式,台面的氮化物是氮化镓(gan)基,并且还包括铝(al)和/或铟(in)。

[0143]

根据另一实施方式,形成台面的氮化物(n)的材料是选自以下的任何材料:氮化镓(gan)、氮化铟(inn)、氮化铝(aln)、氮化铝镓(algan)、氮化铟镓(ingan)、氮化铝镓铟

(algainn)、氮化铝铟(alinn)和氮化铝铟镓(alingan)。

[0144]

根据一个示例,形成垫的步骤包括蚀刻结晶层并仅蚀刻流变层的一部分,以便在垫之间保留流变层的一部分。

[0145]

根据一个示例,形成垫的步骤是这样进行的:d

微晶

/d

垫

≥k3,其中k3=3,d

垫

是垫截面在与基板顶面主要延伸所沿的平面(xy)平行的方向上测量的最大尺寸(垫或更一般地垫的边缘到边缘距离,即垫的最大尺寸,无论其截面形状如何),d

微晶

对应于在微晶聚结时在与d

垫

相同的方向上测量的微晶的尺寸。

[0146]

对于k3=3,获得了特别有效的结果。根据一个示例,100≥k3≥3。优选地,50≥k3≥3。优选地,5≥k3≥3。

[0147]

这个特点允许流变部分变形,使得流变部分在吸收两个相邻微晶开始聚结时产生的机械应力方面特别有效。因此,这个特点有效地减少最终获得的氮化物台面中的缺陷密度。

[0148]

优选地,p

垫

/d

垫

≥4,并且优选地p

垫

/d

垫

≥5。根据给出特别定性结果的一个示例,p

垫

/d

垫

=5。

[0149]

优选地,h/d

垫

≥2。该比例允许通过使垫破裂来发生应力松弛机制。

[0150]

根据一个示例,在所述垫形成之后,并在微晶的所述外延生长之前,执行使流变部分减薄的步骤。该减薄步骤包括至少相对于结晶部分选择性地蚀刻流变部分。因此,在该减薄步骤结束时,流变部分的截面减小。然而,流变部分的剩余截面足以支撑结晶部分、以及由缓冲层和种子层形成的任何部分、和将通过外延形成的微晶。该可选的实施方式允许在形成垫期间释放该方法中的应力,而同时在微晶的聚结期间引起垫的流动变形。

[0151]

根据一个示例,该方法包括在氮化物台面上形成阻挡层的步骤,接着是在阻挡层上形成至少一个源极、漏极和栅极的步骤。这样允许从每个台面上形成竖向晶体管,优选地为hemt类型的竖向晶体管。这种晶体管的、通常由gan制成的氮化物层可以具有较大的厚度和较低的位错率,并且不会引起基板的变形。

[0152]

优选地,阻挡层由algan制成或是algan基的。优选地,阻挡层是通过外延形成的。晶体管可以包括氮化物层与阻挡层之间的其他层。

[0153]

术语“micro-led”是指led所具有的、在与对micro-led进行支撑的基板延伸所沿的主平面(即图中给出的正交坐标系的xy平面)平行的平面中测量的至少一个尺寸是微米级的,即严格小于1mm(10-3

米)。在本发明的范围内,micro-led投影在与micro-led主面平行的主延伸平面中,即投影在与基板顶面平行的主延伸平面中的最大尺寸在该平面中为微米级大小。优选地,这些最大尺寸小于几百微米。优选地,这些最大尺寸小于500μm。

[0154]

在本发明中,“hemt类型的晶体管”(高电子迁移率晶体管)被理解为高电子迁移率场效应晶体管,有时也被称为异质结构场效应晶体管。这种晶体管包括具有不同带隙的两个半导体层的叠覆,在带隙之间的界面处形成量子阱。电子被限制在该量子阱中,以形成二维的电子气。由于与耐高压和耐高温有关的原因,选择这些晶体管的材料以使其具有宽带隙(wide band gap)。

[0155]

在下文的描述中,术语晶体和微晶将被认为是等效的。

[0156]

需要说明的是,在本发明的范围内,术语“在...上”、“叠覆”、“覆盖”或“之下”或其等效词并不意味着“接触”。因此,例如,“第一层在第二层上的沉积”并不一定意味着这两层

直接相互接触,而是意味着第一层至少部分地覆盖第二层,要么同时直接与第二层接触,要么同时被至少一个其他层或包括空气的至少一个其他元件分开。类似地,“叠覆在第一层之上的垫”并不意味着该垫一定与该第一层接触,而是指该垫要么与该第一层接触,要么与设置在第一层与垫之间的一个或更多个层接触。

[0157]

用于形成不同层和区域的步骤应从广义上理解:各步骤可以在不一定严格地连续进行的几个子步骤中执行。

[0158]

在下面的描述中,厚度或高度是在与不同层的主面垂直的方向上测量的。在图中,厚度或高度是沿图3a所示正交坐标系的竖向轴线或z轴线测量的。

[0159]

类似地,当元件被指示为与另一元件位于一条线上时,这意味着这两个元件都位于与基板的主平面垂直的相同线上,即在图中相同的竖向定向线(z轴线)上。

[0160]

材料m“基”的基板、层或器件被理解为是指仅包括该材料m的基板、层或器件,或者包括该材料m和可选的其他材料例如合金元素、杂质或掺杂元素的基板、层或器件。

[0161]

术语“基本上”、“大约”和“约”是指“在10%以内”,或者在提到角度定向时为“在10

°

以内”。因此,基本上法向于平面的方向是指相对于该平面具有90

±

10

°

角的方向。

[0162]

现在将参照图3a至图3f来描述根据本发明形成多个台面的一个示例性方法。

[0163]

如图3a所示,叠置件被设置为包括至少一个基板100,该基板由流变层200和结晶层300连续地叠覆。因此,流变层200被设置在基板100和结晶层300之间。

[0164]

根据一个示例性实施方式,基板100是非晶硅基或结晶硅基的。这实现了叠置件的机械强度。

[0165]

结晶层300具有顶面和面向流变层200的底面,该顶面被设计为用作用于使最终要获得的台面550a、550b的氮化物外延生长的基部层。例如,最终要获得的层是氮化镓gan层。根据一个示例性实施方式,结晶层300是单晶硅基。可替代地,结晶层300可以是sic基或al2o3基。

[0166]

优选地,流变层200由粘性材料制成。流变层200具有玻璃化转变温度。因此,流变层具有玻璃转变点,并呈现出玻璃化转变材料的性能。像所有具有玻璃化转变温度的材料一样,流变层200在温度上升的作用下变形而不会断裂,并且也不会在温度下降后恢复到其原始位置。相反地,结晶层300显然没有玻璃化转变点。结晶层变形,然后错取向,并可能断裂。因此,流变层200和结晶层300是不同的。流变层200不是结晶。

[0167]

流变层200由非晶材料诸如氧化物制成,优选地硅氧化物sixoy,诸如sio2。该层的作用将在下文的描述中解释。

[0168]

有利地,但以非限制性方式,包括基板100、流变层200和结晶层300的这种叠置件构成了绝缘体上半导体类型的基板,优选地为绝缘体上硅(soi)类型的基板。在这种情况下,流变层200由soi基板的隐埋氧化物(box)层形成。

[0169]

根据图3a所示的一个有利的示例性实施方式,通过在结晶层300的顶面上进行外延而沉积缓冲层400。当最终要获得的台面550a、550b是由gan形成并且结晶层300是硅基层时,该缓冲层400通常由氮化铝(aln)制成。这防止了所谓的“回熔蚀刻”现象,这种现象是通过硅与镓在通常的外延温度(1000/1100℃)下的非常高反应性而产生的,并使得gan台面550a、550b的降解非常强烈。

[0170]

通常地,aln层的厚度被包括在10纳米至200纳米(10-9

米)之间。

[0171]

如图3b所示,还可以在缓冲层400的顶面上外延沉积种子层500。该种子层500的功能是为了促进微晶510在接下来的步骤中恢复生长。在这种情况下,微晶510a1-510b4的外延生长的至少一部分是从种子层500的顶面发生的,这些微晶在图3d中示出。该种子层500优选地由与最终要获得的台面550a、550b相同的材料制成。通常地,当台面550a、550b的材料是氮化镓gan时,种子层500也是由gan制成。该种子层500通常具有被包括在50纳米至200纳米之间的厚度。

[0172]

为了简洁明了起见,图中仅示出了四个垫1000a1-1000a4以支撑台面550a。不言而喻,台面550a可以形成在更多数量的垫上。如下文将描述的,垫的数量及其周期将适应于micro-led的所需大小。

[0173]

应该注意的是,层400和500仅仅是可选的。因此,根据图3a至图3f中未示出的实施方式,可以仅设置缓冲层400或仅设置种子层500,或者可以不设置这两层400和500。

[0174]

如图3c所示,随后根据叠置件形成垫1000a1-1000b4。这些垫是通过将叠置件蚀刻到流变层200中来获得的,其中至少部分蚀刻剂延伸到流变层200中。

[0175]

为了通过蚀刻形成垫,可以使用本领域技术人员已知的许多蚀刻技术。特别地,可以使用常规的光刻技术,诸如包括形成掩模(mask)的光蚀刻技术,该掩模例如由树脂制成,随后将掩模的图案转移到叠置件中。也可以使用电子束光刻技术或纳米压印技术。

[0176]

这些垫1000a1-1000b4的尺寸很小,并且可以描述为纳米垫。通常地,在垫截面的与正交xyz坐标系的xy平面平行的或者与基板100的顶面101的平面平行的平面中测量的最大尺寸被包括在几十到几百纳米之间。更具体地,d

垫

被包括在10至500nm之间,并且优选地在20至150nm之间,并且优选地在50至100nm之间,例如约为50nm或100nm。在图3c中,垫的该最大截面尺寸被赋予了附图标记d

垫

。如果垫具有圆形截面,该最大尺寸d

垫

对应于垫的直径。如果垫具有六边形截面,该最大尺寸d

垫

对应于对角线或经过六边形的各角的圆的直径。如果这些垫具有长方形或正方形截面,该最大尺寸d

垫

对应于最大的对角线。

[0177]

垫1000a1-1000b4并非全部均匀地分布在基板100的表面上。垫1000a1-1000b4形成垫组1000a、1000b,每组包括多个垫。形成同一组1000a的垫1000a1-1000a4形成与形成另一组1000b的垫1000b1-1000b4的阵列间隔开的垫的阵列。

[0178]

因此,同一组1000a的相邻垫1000a1-1000a4以距离d分开。属于两个单独的组1000a、1000b的相邻垫1000a4-1000b1以距离w1分开。距离d和w1是在平行于xy平面的平面中测量的,并且如图3c所示。如下文将解释的,同一组1000a的垫1000a1-1000a4意在支撑单个台面550a,该台面将与由另一组1000b的垫1000b1-1000b4支撑的另一台面550b间隔开。

[0179]

应注意的是,对于相同的台面,d可以变化。因此,相同台面550a的垫1000a1-1000a4可以以非周期性的方式分布。因此,垫的分布方式可以适于促进台面的生长。例如,如果台面550a的垫1000a1-1000a4的布置不是周期性的,则可以存在对于这些垫1000a1-1000a4而言相对于平均值以正负20或正负10%的方式变化的距离d,例如以正负10nm的方式变化。根据一个示例,对于相同的台面,d可以具有以下值:100nm、90nm、85nm、107nm。

[0180]

在不以周期性方式分布的成组垫1000a、1000b上形成的台面550a、550b可以周期性地设置在基板上。这促进了微显示器的生产。

[0181]

根据一个示例性实施方式,垫1000a1-1000b4的在流变层200中形成的部分具有高度e

220

,并且在同一组中,两个相邻的垫1000a1、1000a2间隔开距离d,使得:

[0182]e220

/d《1,并且优选地e

220

/d《1.5。优选地e

220

/d《2。

[0183]

根据一个示例性实施方式,垫具有高度h

垫

,并且两个相邻的垫以距离d分开,使得:

[0184]h垫

/d《2,并且优选地h

垫

/d《1.5。优选地h

垫

/d≤1。

[0185]h垫

和e

220

是在z方向上测量的。d是平行于xy平面测量的。

[0186]

如图3c所示,垫被蚀刻穿过整个种子层500、整个缓冲层400(如果存在这些层)和整个结晶层300。优选地,流变层200的仅一部分220被蚀刻。该实施方式的优点是,它可以防止在外延期间台面550a、550b的氮化物在流变部分220上生长。当被外延生长的氮化物台面550a、550b由gan制成而流变部分由sio2制成时,这种外延选择性尤其明显。相反地,如果使用这些相同的材料,流变层200被蚀刻穿过其整个厚度,那么在外延期间,台面550a、550b的氮化物从通常由硅制成的基板100的顶面生长。这种情况显然是不理想的。

[0187]

此外,保持流变层200的非蚀刻部分210被视为促进部分220的流动,特别是当微晶因扭转而错取向(misoriented)时,即在要获得的台面550a、550b的主要延伸平面中错取向时。台面550a、550b的这些主要延伸平面与xyz坐标系的xy平面平行。

[0188]

优选地,由此形成流变部分220的高度的蚀刻厚度e

220

等于流变层200的厚度的一半。这在形成晶界期间促成了非常好的微晶重新定向。

[0189]

图3d示出了通过从种子层500(或在没有层400和500时从结晶层300的顶面)外延生长来形成微晶510a1-510b4。

[0190]

如该图3d所示,垫1000a1-1000b4各自支撑由叠置的部分400a1-400b4、300a1-300b4、220a1-220b4承载的微晶510a1-510b4。这些部分在垫的主要延伸方向上延伸,即在图3a至图3f中的竖向(z)方向上延伸。

[0191]

如果垫的截面主要是圆形的,那么这些部分形成圆形柱体。如果垫1000a1-1000b4的截面是多边形的,例如六边形的,那么这些部分形成具有六边形截面的柱体。优选地,这些部分是实心的。垫的截面是平行于xy平面测量的,即与流变层220和结晶层300主要延伸所沿的平面平行的平面测量的。

[0192]

无论选择哪种实施方式,即具有或没有种子层400以及具有或没有缓冲层500,微晶510a1-510b4的外延生长至少部分地或完全地发生在垫1000a1-1000b4的顶面1001。因此,该顶面1001要么由结晶部分300a1-300b4形成,要么通过由种子层400a1-400b4形成的部分形成,要么通过由缓冲层形成的部分形成。特别地,这允许快速获得具有明显厚度的微晶510a1-510b4。

[0193]

应注意的是,缓冲层400的顶面和种子层500的顶面,即面向待生长的台面550a、550b的各面,具有镓(ga)型极性,而不是氮(n),这相当大地促进了高质量外延生长的氮化物台面550a、550b的生产。

[0194]

微晶510a1-510b4的生长是持续的,并侧向延伸,特别是在平行于xy面的平面中延伸。来自同一组1000a的垫1000a1-1000a4的微晶510a1-510b4生长,直到它们聚结并形成块或台面550a、550b,如图3e所示。

[0195]

换句话说,并如图所示,每个台面550a、550b在多个垫1000a1-1000a4之间延伸。每个台面550a、550b形成连续层。

[0196]

微晶510a1-510b4的这种生长并不向下延伸。此外,这种生长是有选择性的,因为它不会发生在通常由氧化物制成的流变层200上。在这个意义上,微晶510a1-510b4的生长

是根据悬空外延的原理发生的。

[0197]

应注意的是,在缓冲层400的外延形成和种子层500(如果存在这些层)的外延形成之后,特别有利地蚀刻垫1000a1-1000b4。更具体地,如果这些层400、500中的一层在蚀刻后被沉积,该层将至少部分地形成在流变层200的顶面上的垫1000a1-1000b4之间。在外延生长的氮化物是gan而流变层200由sio2制成的情况下,那么在外延沉积温度下,氮化物台面550a、550b的外延生长将不是选择性的,而是也会发生在垫1000a1-1000b4之间,这当然是不理想的。

[0198]

以一种特别有利的方式,进行外延的温度t

外延

大于或约为流变层200的玻璃化转变温度t

玻璃化转变

。因此,在外延期间,流变部分220a1-220a4被加热到允许它们变形的温度。

[0199]

作为结果,如果由两个相邻的垫1000a1-1000a2承载的微晶510a11-510a12相对于彼此错取向,在这两个微晶聚结后,在微晶之间的界面处形成的、通常被称为晶界或聚结边界的边界560将形成而不发生位错,以校正这些错取向。因此,流变部分220的变形允许这些错取向得到校正,并获得在聚结边界处没有或很少有位错的台面550a、550b。该现象将在下文中参照图5a至图5d详细描述。

[0200]

因此,在步骤3e结束时,获得多个台面550a、550b,每个台面550a由相同垫组1000a的垫1000a1-1000a4支撑。两个相邻的台面550a、550b以距离w2分开,其中w2是在这两个台面之间测量的最短距离。w2是在xy平面中测量的。

[0201]

w2取决于w1、外延生长的持续时间和速度。w2是非零的。w2《w1。

[0202]

台面的平行于xy平面测量的最大尺寸被赋予附图标记d

台面

。因此,d

台面

对应于台面投影在与xy平面平行的平面中的最大尺寸。优选地0.8μm≤d

台面

≤3μm,并且优选地1μm≤d

台面

≤2μm。d

台面

取决于外延生长的速度和持续时间,以及取决于同一组中垫的数量、尺寸和间距p

垫

。

[0203]

用于生产台面550a、550b的方法可以在图3e结束时停止。可替代地,可以继续该方法以从台面550a、550b中的每一者形成micro-led。

[0204]

图3f示出了非限制性实施方式,其中,量子阱590是在每个台面550a、550b内产生的。该实施方式有利地允许直接生产出尺寸与台面的初始尺寸相对应的micro-led。为了在每个台面550a、550b内产生量子阱590,本领域技术人员可以实施现有技术中已知的解决方案。因此,在微晶510已经聚结后,采用与常规二维生长相同的生长条件来制造阱。

[0205]

micro-led的最小可能尺寸取决于所选择的结构化方法的最终分辨率:例如,对于通过纳米压印制成的阵列,可以实现50nm的垫大小和150至200nm的周期p

垫

。这意味着获得了1至2μm的台面尺寸d

台面

。因此,这是在高分辨率μ显示器所需的像素大小范围内。

[0206]

图4a是通过扫描电子显微镜(sem)获得的照片,示出了对使用上文所述方法获得的多个台面550a、550b进行支撑的基板。

[0207]

图4b是通过扫描电子显微镜(sem)获得的照片,放大倍数比图4中的放大倍数高,并示出了台面550a。在该图4b中,台面的顶面在形状上是方形的。每条边是300μm长。垫的截面可以被比作边长为200nm的方形。

[0208]

图4c是另一台面550a的照片。该台面的顶面当投影在xy平面上时具有六边形或基本矩形的形状。考虑到该形状是矩形的,两个相邻边的长度是40μm和50μm。因此,该台面的面积为40μm

×

50μm。

[0209]

图4d是另一台面550a的照片。该台面的顶面当投影在xy平面上时具有六边形或基本矩形的形状。考虑到该形状是矩形的,两个相邻边的长度是3μm和4μm。因此,该台面的面积为3μm

×

4μm。

[0210]

这些示例涉及从蚀刻到soi上gan叠置件的垫阵列中获得的gan台面。

[0211]

图4a至图4d示出,通过实施上文所述的方法可以生产出测量为几十至几百μm的台面550a。这些gan台面中的位错密度约为1至2 10e8/cm2。量子阱的辐射效率非常好。包括由这些台面形成的多个led的显示器具有很高的分辨率和亮度。

[0212]

对在台面内在几乎没有位错或无位错的情况下的聚结原理进行建模和解释

[0213]

如上文参照图3e所示,如果由两个相邻的垫1000a1-1000a2承载的微晶510a11-510a12相对于彼此错取向,在这两个微晶聚结后,在微晶之间的界面处形成的边界560将通过校正这些错取向来形成而不存在位错。因此,本发明提出的流变部分220的变形使得能够校正这些错取向。该原理将在下面的段落中说明。

[0214]

如图5a和图5b所示,两个相邻的微晶510a1-510a12的错取向可以由被称为扭转的面内错取向(即相对于被包含在图3a-图3f的平面内的轴线)造成。

[0215]

示出了微晶510a1-510a2的俯视图的图5a例示了这种类型的未对准,其中微晶之间存在角度α。图5a示意性地示出,使用用于外延形成氮化物层的常规方法,在聚结期间形成的边界560会产生错取向561以校正未对准。

[0216]

在用于生产氮化物层的已知方法中,存在位错的原因有几个。

[0217]

第一个原因是,氮化物层的外延生长是在异质基板上进行的,即在基板的材料和晶格参数与待外延生长的氮化物层的材料和晶格参数不同的该基板上进行。

[0218]

存在位错的第二个原因是,外延生长是柱状的。这主要与生长期间异质基板表面上物质的低扩散性有关,这造成了小晶粒的形成。在聚结期间,这些晶粒连结在一起,在晶粒之间的界面处,即在聚结边界处,形成位错,然后穿过整个外延生长的结构。

[0219]

由于涉及成本和可用性以及符合工业限制的尺寸方面的原因,不能使用与待外延生长的层相同性质的基板(同质基板)。

[0220]

因此,工业解决方案是基于使用异质基板的。然而,当使用异质基板时,在外延层中会产生许多位错,并且这些缺陷会传播到器件的有源区中。

[0221]

减少位错密度的一个解决方案是使用所谓的“外延侧向过生长”(elog)方法。这种方法的原理是基于以下事实:在外延生长的某个阶段中,沉积了具有开口的掩模。种子在开口中生长,然后通过侧向再生长超过掩模。侧向再生长的结果是使种子的位错弯曲,从而防止其竖向传播。因此,这种类型的方法通过弯曲消除了大量的位错,然而在聚结期间也会产生位错。更具体地,当来自两个相邻开口的两个微晶在掩模上方连结时,会形成聚结边界,并且位错可以到达表面。

[0222]

实际上,虽然很明显的是,掩模下的位错被有效地阻挡,但设法穿过掩模上的开口传播的位错会传播到外延层中,并可以到达表面。

[0223]

不言而喻,与“自然”聚结相比,聚结产生的穿透性位错的密度大大降低,因为“晶粒”的尺寸较大(通常与掩模中的开口的周期相近)。然而,这些位错是不均匀分布的,这可能会在器件制造期间造成问题,因为它是由竖向于这些区域的非发光材料带的形成造成的。

[0224]

另一种解决方案在于在该材料的预先存在的垫上进行材料的外延生长:这种方法被称为悬空外延方法,它免除了在掩模上重新生长的需要。另一方面,已知的悬空外延解决方案并不能消除或显著减少由相邻种子聚结产生的缺陷的出现。

[0225]

图5b非常示意地示出了使用上文所述的方法来形成聚结边界560。图5b示出了流变部分的扭转变形ta1、ta2(相对于z轴线),允许在没有位错的情况下形成聚结边界560。在这种情况下,由流变部分220a-220b对这种变形的校正使得流变部分220a1-220a2相对于其主轴线扭转。如图5b中右视图所示,每个部分沿相反的方向旋转。

[0226]

如图5c和图5d所示,两个相邻的微晶510a1、510a2的错取向还可以造成平面外的未对准(即相对于与xyz坐标系的y轴线或x轴线平行的轴线),被称为倾斜。在这种情况下,通过流变部分220a1-220a2对这种变形的校正造成了垫的倾斜。

[0227]

图5c示出了微晶510a1和510a2在聚结前的微晶平面之间的角度错取向,由角度β表示。图5d非常示意性地示出了流变部分220的变形,允许在没有位错的情况下形成聚结边界560。在此图中可以认为,错取向在两个微晶510a1和510a2之间平均分布,即由β/2表示。该图也适用于结晶错取向在两个相邻的微晶中具有不同角度且角度总和等于β的情况。

[0228]

图5a至图5d并不意在成为流变部分的变形的真实视觉表现。这些图意在提供示意性视图,以便于理解在边界560处无位错的情况下的微晶聚结的原理。以下段落意在对该原理作进一步的解释和说明。

[0229]

下文的段落旨在更详细地解释允许获得无位错或极少位错的外延生长层或台面550a、550b的现象。

[0230]

当两个晶粒或微晶被刚性地键合在晶粒或微晶所沉积的基板上,并且相对于彼此稍有错取向时,它们的聚结边界的形成能量很高(它可以很容易地计算出来,因为它是界面位错阵列的第一近似值。在这方面,可以参考以下出版物:j.p.hirth和j.lothe“theory of dislocations”,john wiley and sons(1982)。

[0231]

然而,如果微晶510a1-510a4搁置在垫1000a1-1000a4上,就像悬空外延的情况一样,并且这些垫1000a1-1000a4可以变形,无论是扭转变形还是倾斜变形,微晶(例如gan)相对于彼此的错取向被“传输”到承载这些微晶的垫。在简单扭转的情况下,如图5b所示,该现象可以通过以下方式来模拟:使得微晶旋转连结并形成“内部”表面的吸引力在纳米垫1000a1-1000a4处产生扭转转矩。垫1000a1-1000a4的大小与微晶的大小之间的比越小,该扭转转矩将越大。如果垫1000a1-1000a4的变形很容易,那么聚结边界560简单地成为将形成“完美”原子键的内部表面。就能量而言,只有在聚结期间由“内部表面”的形成所释放的能量大于垫1000a1-1000a4本身变形以吸收相邻微晶510a1-510a2之间的初始错取向所需的能量时,这才有可能。底层垫是sio2基座的事实是有益的,因为sio2在生长温度下会流变。sio2是一种实际上非常适合这种方法的材料,但这并不排除使用其他材料,诸如可以在同等或更低温度下流动的玻璃,诸如也用于制造soi的硼硅玻璃或硼磷硅玻璃(bpsg)。

[0232]

在假设边长为500nm的立方gan微晶由具有直径测量为100nm的圆形截面的垫承载的情况下,聚结期间释放的能量可以表示为内部键能和将要接触的两个表面的表面能量之间的差异。表面能量值约在0.1至0.2(在这方面可以参考以下出版物:c.e.dreyer、a.janotti和c.g.van de walle“absolute surface energies of polar and nonpolar planes of gan”,physical review b 89,081305(r)2014)。键能约为11ev(ga-n

键)。

[0233]

作为第一近似值,从六边形表面(0001型)开始,获得每个晶胞的值36ev(每个晶胞有三个ga-n键),即对于所考虑的六边形晶胞(表面积为26a2),获得与表面积有关的键能为1.35ev/angstrom2。这种方法通过考虑接触c型(0001)表面而得到简化,但是与这些表面的晶体取向有关的校正(每晶胞的键数和表面能量)是二阶的,并只对该数值评估稍有修改。

[0234]

因此,通过形成1.35-0.3=1.05的共价键,在接触处观察到能量“释放”(最终状态-初始状态),即每约1ev。这显然与将要接触的微晶510a1、510a2之间的错取向无关。如果考虑边长为500nm的立方体形状的微晶(为了简化估计,如图2b中的图表),会观察到25 10

e6×

1.6 10

e-19的能量释放,即约4 10

e-12焦耳。这必须与使sio2垫1000a1-1000a4在微晶下变形所需的能量进行比较,如下文详细描述的。

[0235]

在gan的外延温度(约1100℃)下,氧化硅展现出粘塑性性能,其粘度取决于材料所承受的温度和机械应力两者。

[0236]

随着温度的升高,sio2的粘度降低,就像具有玻璃转化点的任何材料一样。在一定的应力值以上,sio2的粘度也随着机械应力的增加而降低。换句话说,与塑性应变率同剪切应力成比例(与应力无关的粘度)的常规流变体不同的是,在超过被称为失效应力的阈值时,sio2的应变率随着应力的增加呈指数增加。实际上,在1100℃时,sio2的失效应力约为500mpa:因此在这个温度下,sio2的粘度在最多达500mpa的应力范围内与应力无关。超过这个值,粘度会下降几个数量级,并且非常快的塑性应变会留下接近失效应力的余留应力。然后,该余留应力通过常规流变(几分钟到几小时)缓慢地减少。

[0237]

在对准之前,gan微晶510a1-510a4示出了相对于彼此的错取向,平均等于1至6

°

。在相邻的微晶聚集到一起以形成共价原子键之前,作用在微晶之间的原子间力是范德华力(van der waals force),在非常短的范围内具有吸引力。这使得在接触点处施加旋转转矩,以使微晶对准。在非常小的旋转几分之一度之后,在垫1000a1-1000a4下的流变部分220a1-220b4中达到500mpa的失效应力。因此,流变在氧化物中几乎成为瞬时的,并且在对准阶段结束期间,旋转所需的旋转转矩是恒定的。

[0238]

使用图5b所示的几何形状,即以具有圆形截面且边长为100nm的较小垫为中心的、边长为500nm的立方体微晶510,微晶510a1-510a4的完全聚结通常在几百秒内实现。如果1s被认为是使微晶510接触的特征时间,数值模型示出的是,为了在约一秒钟内使垫旋转2

°

,考虑到氧化物在高温下的失效,需要约0.5

e-20至1

e-20焦耳的机械功。因此,使两个表面接触所释放的能量在约10

e-11至10

e-13焦耳,远远大于底层垫1000a1-1000a4的机械变形能量。该能量也比在微晶510a1-510a4的外延生长温度附近将以下垫进行对准所需的能量低几个数量级:构建在块状硅上的垫;或由没有玻璃转变相的材料形成的垫。

[0239]

上述段落的考虑示出的是,为了实现无位错的微晶聚结,可以调整以下参数:

[0240]-在相对较低的500mpa的应力下形成高温流变部分的材料的“机械失效”特性。

[0241]-与同一组1000a的垫之间的距离d相比,支撑垫1000a1-1000a4的大小足够小,允许在流变部分中产生应力,对于给定的旋转转矩,该应力大于失效应力。

[0242]

此外,如上文所述,应注意确保外延温度t

外延

允许流变部分220流变。实际上,t

外延

≥600℃(在分子束外延的情况下),t

外延

≥900℃,并且优选地t

外延

≥1000℃,并且优选地t

外延

≥1100℃。当流变层由sio2制成时,这些数值对减少外延生长层或台面中的缺陷特别有效。实

际上,t

外延

≤1500℃。

[0243]

为了便于在无位错的情况下的聚结边界560的形成,应采用以下条件:

[0244]

t

外延

≥k1

×

t

玻璃化转变

,其中k1=0.8,优选地k1=1,并且优选地k1=1.5。

[0245]

根据一个示例性实施方式,t

外延

≤k2

×

t

最低熔融

,t

最低熔融

是形成垫的各部分的熔融温度中的最低熔融温度。这主要涉及结晶部分和流变部分。根据示例性实施方式,k2=0.9。这防止了具有最低熔融温度的材料种类的扩散。

[0246]

因此,在垫由sio2流变部分和硅结晶部分形成的情况下,t

外延

≤1296℃。更具体地,t

最低熔融

等于硅的熔融温度,因为硅的熔融温度等于1440℃,并且sio2的熔融温度等于1970℃。

[0247]

根据一个示例性实施方式,流变部分的高度e

220

使得e

220

≥0.1d

垫

。优选地,e

220

≥1d

垫

。这些值促成足够的变形,以减少晶界处的应力。

[0248]

垫1000a1-1000a4具有高度h

垫

,并且两个相邻的垫1000a1-1000a2以距离d分开,使得:h

垫

/d《2,并且优选地h

垫

/d≤1。

[0249]

有利地,执行形成垫1000a1-1000a4的步骤使得d

微晶

/d

垫

≥k3,其中d

垫

是垫1000a1-1000a4的截面在与基板100的顶面110延伸所沿的平面平行的方向上测量的最大尺寸。因此,d

垫

对应于垫投影在xy平面上的最大尺寸。d

微晶

对应于微晶510a1-510b4聚结时在与d

垫

相同的方向上测量的微晶尺寸。d

微晶

的尺寸在图3e中被引用。

[0250]

根据一个示例,100≥k3≥1.1。优选地,50≥k3≥1.5。优选地,5≥k3≥2。

[0251]

根据一个示例,k3≥3,优选地100≥k3≥3。优选地,50≥k3≥3。优选地,5≥k3≥3。

[0252]

这个特点允许流变部分变形,因此流变部分在吸收两个相邻微晶开始聚结时产生的机械应力方面特别有效。因此,该特点有效地减少最终获得的氮化物台面550a、550b中的缺陷密度。

[0253]

图18a至图18c的实施方式

[0254]

现在将参照图18a至图18c描述替代性实施方式。图18a所示步骤之前的步骤可以与图3a至图3c所示步骤相同。因此,参照这些图3a至图3c提到的所有特点、步骤和技术效果都完全适用于该替代性实施方式。

[0255]

在图3c中所示的步骤结束时,执行使流变部分220减薄的步骤。该步骤使得流变部分220的截面减少。

[0256]

在减薄之前,流变部分220的截面对应于d

垫

,如图3c和图18a中所示。在减薄后,流变部分220的截面对应于d

220a

,如图18a所示。如图18a所示,减薄后的厚度被赋予附图标记ea。

[0257]

为了实现这种减薄,提供了蚀刻,相对于结晶部分300的材料,以及如果存在缓冲层400和种子层500的话相对于分别由缓冲层和种子层形成的部分,选择性地蚀刻流变部分220的材料。例如,可以用氢氟酸(hf)溶液进行湿式蚀刻。当流变层200由氧化物制成而结晶层300是硅基时,这种蚀刻特别有效且是选择性的。

[0258]

在图18a所示的示例中,虚线对应于蚀刻之前流变层200的轮廓。在图18a所示的非限制性示例中,流变层200的部分210被完全移除。基板100因此被暴露。应注意的是,尽管如此该部分210的一部分优选地被保留。因此,优选地,部分210的一部分覆盖基板100。这增进了流变部分220在流变期间的变形。

[0259]

步骤18b对应于垫1000上微晶开始外延生长。该步骤18b对应于步骤3d。

[0260]

步骤18c对应于垫1000上的微晶聚结,直到在每个垫组1000a、1000b上形成台面550a、550b。该步骤18c对应于步骤3e。

[0261]

因此,参照图3d和图3e提到的所有特点、步骤和技术效果都完全适用于图18a至图18c所示的该替代性实施方式。

[0262]

在要生产led的非限制性情况下,步骤18c可以通过应用参照图3f描述的特点和步骤继续进行。

[0263]

提供了对流变部分进行减薄的该实施方式具有几个优点。

[0264]

特别地,它允许在微晶的外延生长之前生产具有截面减小的流变部分的垫。这促进了在流变期间由在外延生长期间施加的温度引起的垫变形。该实施方式还减少了微晶聚结期间的应力,并因此降低了出现缺陷和位错的风险。

[0265]

因此,本实施方式允许形成垫1000,具有:

[0266]-微晶部分,或如果存在缓冲层400和种子层500的话,甚至具有由缓冲层和种子层形成的具有相对较大尺寸的部分(这些尺寸是在与基板100的主要面平行的xy平面中测量的)。这减少了在生产垫1000时对该方法的压力。这允许尺寸大于上文所述的尺寸d

垫

。

[0267]-具有较小截面的流变部分220,该截面有利于微晶在流变期间的变形和正确定向。可以为流变部分220的截面提供尺寸d

220a

,该尺寸对应于上文提到的d

垫

的数值。

[0268]

因此,该方法减少了关于该方法的应力,同时提高了所产生的氮化物台面550a、550b的质量。

[0269]

例如:

[0270]-在微晶部分处,d

垫

≥100nm,并且优选地d

垫

≥200nm,甚至更优选地d

垫

≥500nm,并且优选地d

垫

≥1000nm。

[0271]-在流变部分220处,20nm≤d

220a

≤200nm,并且优选地50nm≤d

220a

≤100nm。

[0272]

示例性实施方式

[0273]

现在将参照图6至图10描述台面的几个示例性实施方式。

[0274]

图6是用扫描电子显微镜(sem)拍摄的照片。它示出了依次包括以下的叠置件:基板100、非蚀刻流变层的部分210、流变部分220、结晶层300以及在这种情况下由gan制成的微晶510。由于形成棱锥刻面的半极性平面的生长速度较低,该微晶510在形状上呈棱锥形。在该示例中,垫的直径为100nm。

[0275]

在流变部分220的两侧上可以看到空的空间230。

[0276]

为了确保棱锥形微晶的聚结并获得二维生长,可以有利地执行以下步骤。在第一步骤中,使用给定的生长条件在每个纳米垫上产生棱锥直到棱锥彼此相邻。在第二步骤中,修改这些生长条件以诱导侧向生长。例如,这两步骤生长过程在以下出版物中有所描述:shields et al.2011,nanopendeo coalescence overgrowth of gan on etched nanorod array phys.status solidi c 8,no.7

–

8,2334

–

2336(2011)。

[0277]

图7a和图7b示出了由通过该方法获得的氮化物层形成的台面550的示例,用于197

×

300垫阵列。在该示例中,垫大小为200nm,并且其间距为1μm。该垫尺寸允许出现在垫微晶上的位错数量非常明显地减少。此外,该垫大小优化了聚结期间的变形和转矩传输。

[0278]

以一种特别有利的方式,很明显的是,形成台面550的氮化物层已经与底层基板

100分离。因此,最终待获得的台面550的脱层特别容易。该自动脱层可以是完全的或部分的。下文将更详细地进行描述。

[0279]

因此,可以生产出自支撑的gan台面,在本示例中大小为300

×

300μm。

[0280]

图8a至图8c是以不同的放大率水平和观察角度示出在垫上生长后得到的棱锥形gan微晶510的阵列580的照片。图8a是示出整个阵列580的立体图的照片。该阵列580是方形的,并且表面积为40

×

40μm2。图8b是示出了阵列580的一部分的俯视图的照片。图8c是示出了阵列580的一部分的立体图的照片,清楚地示出了由形成在基板100上的垫1000支撑的微晶510。如从图8c清楚看到的,微晶510形成具有六边形截面的棱锥。垫是通过电子束光刻技术从包括以下各层的叠置件中产生:

[0281]-流变层200:sio2

[0282]-结晶层300:si

[0283]-缓冲层400:aln

[0284]-种子层500:gan

[0285]

在图8a至图8c所示的示例中,垫可以例如具有200nm的直径,并间隔开1μm。

[0286]

聚结缺陷的特征

[0287]

图9是聚结的gan晶体510的截面的透射电子显微镜(tem)照片。该图首先示出的是,在生长开始时,来自再生长的大部分位错560在生长平面中对准。

[0288]

此外,很明显的是,发生来自相邻垫的微晶510的聚结,其中在聚结边界560处的聚结缺陷非常少。这必须与常规方法相比较,在常规方法中,聚结会产生穿透性缺陷。这些常规方法可以基于侧向再生长,如图11a和图11b所示,并如e.byakimov和a.ypolyakov,2015ebic investigation of dislocations in elog gan,phys.status solidi的出版物中所述。这些图11a和图11b清楚地示出的是,使用这种方法,成核层的缺陷903通过掩模901中的开口902穿过整个最终层。

[0289]

这些常规的方法也可以基于从一维结构的悬空型再生长,如shieldsshields et al.2011,nanopendeo coalescence overgrowth of gan on etched nanorod array phys.status solidi c 8,no.7

–

8,2334

–

2336(2011)的上述出版物中所述。

[0290]

图9还示出的是,垫1000a1、1000a2沿其高度的一半被分割,这允许垫1000a1-1000a2的阵列580上的外延生长的台面550容易脱层。

[0291]

在理想的是台面在转移后容易分离以形成micro-led的情况下,该特征是非常有利的。

[0292]

图10使用阴极发光技术证实了在例如棱锥形的两个微晶之间不存在聚结引起的缺陷。该技术允许对在考虑生产的材料的光子发射进行空间映射。图10中的全色阴极发光图像示出的是,除了从不同的面(或边缘)提取光引起的发射变化外,在两个微晶之间的交界处没有非辐射复合,这表明在聚结边界的区域中没有任何结构缺陷。

[0293]

用于由多个台面生产micro-led的方法

[0294]

现在将参照图12a至图12o描述用于生产micro-led 570a、570b的一个示例性方法。

[0295]

第一步骤在于提供一种包括多个氮化物台面550a、550b的器件。该器件可以与图3f中所示的器件相同。例如,器件是通过实施参照图3a至图3f所描述的方法来获得的。因

此,氮化物台面中的每个氮化物台面550a、550b都由搁置在基板100上的垫支撑。优选地,量子阱590形成在每个台面中。

[0296]

优选地,执行保护台面550a、550b的步骤,特别是保护台面550a、550b的侧壁552a、552b。例如,该步骤包括沉积保护层以覆盖台面550a、550b,该保护层也被称为钝化层。例如,该沉积是ald(原子层沉积)类型的。这允许该保护层形成在台面550a、550b的所有表面上,特别地保护层形成在台面550a、550b的侧壁552a、552b和顶面551a、551b上。该保护层还可以覆盖垫的侧壁。

[0297]

为清晰起见,该保护层在图12a中没有示出。该保护层优选地为介电层。例如,保护层是由以下材料之一制成或具有由以下材料之一形成的基部:sio2、al2o3、si3n4、hfo2。该保护层的厚度优选地被包括在10nm至1μm之间。

[0298]

如图12a所示,沉积了介电层600以覆盖台面550a、550b。该介电层600是通过全晶圆沉积来沉积的。介电层填充了空间630的位于台面550a、550b之间的部分。该层覆盖台面550a、550b的顶面551a、551b。该介电层600例如是由以下材料之一制成或具有由以下材料之一形成的基板:sio2、sin。

[0299]

如图12b所示,然后对介电层600进行减薄,以提供通向台面550a、550b的顶面551a、551b的入口。这可以通过平面化化学机械抛光(cmp)来实现。该cmp步骤优选地使用止动件在p-掺杂台面550a、550b的顶面551a、551b上执行。

[0300]

如图12c所示,下一步骤包括与p-掺杂台面550a、550b的顶面551a、551b产生电接触件700。该电接触件是以导电层的形式产生的。例如,它是铝基或银基。在图12c中,由基板100、垫、台面550a、550b和接触件700形成的叠置件被赋予附图标记2000。

[0301]

与上述步骤并行或在上述步骤之后,产生互补器件3000,诸如寻址电路或互连网络。例如,该器件3000包括由介电层3200和导电区域3300叠覆的基板3100,在该示例中,每个导电区域意在形成电极和阳极。这样的器件3000在图12d中示出。例如,互补器件是由cmos技术制成的。

[0302]

如图12e和图12f所示,执行步骤,从而为叠置件2000和器件3000的键合(bonding)做准备。

[0303]

根据第一实施方式,该键合准备步骤包括在叠置件2000的电接触件700上沉积键合层2100和/或在导电区域3300上沉积键合层3400。这些键合层2100、3400是导电的。例如,这些键合层2100、3400形成以下材料对中之一:tin/al、tin/w、tin/ti。

[0304]

根据替代性实施方式,叠置件2000的电接触件700与器件3000的导电区域3300的键合是直接键合型的。在准备这种直接键合时,可以在这两层700、3300中的至少一层上执行cmp。

[0305]

图12g示出了叠置件2000在器件3000上的键合结果。因此,导电区域3300与电接触件700电连接。得到的结构被赋予附图标记4000。

[0306]

在包括沉积键合层2100、3400的实施方式中,接触件700和导电区域3300之间的电传导是经由这些键合层2100、3400发生的。优选地,键合方法包括热压。在包括直接键合的实施方式中,承载电接触件的台面550a、550b被设置为直接与由器件3000承载的电极接触。

[0307]

图12h示出了支撑基板100的移除情况。例如,该移除通过对基板100的厚度的一部分进行研磨来进行。例如,基板100的厚度在研磨后可以保留为约40μm。然后可以通过湿法

或干法蚀刻来蚀刻余留的基板材料。作为提醒,该基板100例如是由硅制成的,或者是硅基的。在这个步骤结束时,流变层200被暴露。

[0308]

图12i示出了流变层200的移除情况。作为提醒,在台面550a、550b形成在soi型基板上的情况下,该流变层有利地是埋置的氧化层(box)。消除流变层200的这个步骤留下了介电层600的部分610,这些部分610位于台面550a、550b之间。在消除流变层200的这个步骤期间,可以消耗掉层600的部分厚度。在这两层200、600是由相同的材料(通常是sio2)制成的情况下,当层200和600的蚀刻的选择性较低或为零时,这种情况尤其明显。

[0309]

在这个步骤结束时,垫的一部分被暴露。特别地,微晶部分和可选的缓冲部分在这个阶段是存在的。实际上,已经观察到缓冲部分被gan台面封装。

[0310]

如图12j所示,随后消除垫1000a1-1000b4的余留部分。这个步骤例如通过化学-机械抛光来进行。在这个步骤结束时,检查台面550a、550b的面553a、553b是否已经可访问。还检查叠置件4000是否具有良好的平面度。

[0311]

如图12k所示,下一步骤在于界定micro-led 570a、570b。为了这个目的,在每个台面550a、550b之间进行蚀刻。这种蚀刻在于通过介电层的整个厚度移除介电层600的部分610,以使器件3000的介电层3200暴露。这种蚀刻因此移除了micro-led 570a、570b之间的键合层2100、3400和接触层700。该蚀刻在电子层3200上停止,以保持其功能。在该蚀刻之前进行光刻步骤,以便在台面550a、550b的侧壁552a、552b上保留介电层600的部分620。因此,这些侧壁552a、552b被介电材料完全覆盖。

[0312]

如图12l所示,micro-led 570a、570b中的开口630的侧壁由介电膜640保护。优选地,该介电膜是通过介电层的全晶圆沉积,随后进行各向异性蚀刻来产生的,其优选方向与台面550a、550b的面553a、553b垂直。该各向异性蚀刻因此将介电层蚀刻在水平表面上,并将该介电层640保留在开口630的侧壁上。

[0313]

如图12m所示,仅移除650台面550a、550b的侧壁552a、552b上膜640的一部分和介电层600的部分620的一部分。因此,台面550a、550b的侧壁552a、552b的一部分552'a、552'b未覆盖,而不会使量子阱590未覆盖。因此,部分620的沿z轴测量的蚀刻厚度被控制为使得量子阱590在侧壁552a、552b处仍然被介电层600的部分620和膜640覆盖。

[0314]

如图12n所示,随后通过全晶圆沉积来沉积导体层800,填充台面550a、550b之间的空间630,并覆盖该两个台面。优选地,该沉积是通过电解(ecd)来进行的。导体层800优选地是金属层,诸如铜层。可选地,可以事先沉积种子层以促进金属层的键合。

[0315]

如图12o所示,随后移除导体层800以提供对台面550a、550b的面553a、553b的访问。

[0316]

随后可以在这些面553a、553b上沉积介电层,然后可以制作接触件来连接由此产生的micro-led 570a、570b。

[0317]

使用台面制造的功率晶体管的示例性实施方式

[0318]

在上文的描述中指出,所提出的方法的原理允许以有效的方式生产高性能的led。该方法还允许以特别有利的方式生产其他器件。这就是功率器件诸如功率晶体管的情况。下图描述了这种器件的某些示例以及用于生产这种器件的步骤。下文描述的示例更具体地与hemt型晶体管有关,然而并不限于此。

[0319]

图13a示出了通过实施上文所述的方法来获得的结构,例如参照图3a至图3e或图

3a至图18c。它示出了基板100、流变部分200、微晶部分300、由缓冲层400形成的可选部分、和由种子层500形成的可选部分。由种子层500形成的可选部分在附图中没有示出。

[0320]

图13a所示的该结构具有氮化物台面550,优选地由gan或gan基制成。优选地,这个台面不是有意掺杂的并且可以归类为uid,即无意掺杂的首字母缩写。该结构还具有叠覆在台面550之上的层740。该层740是氮化物基的。它优选地从台面550外延形成。在hemt的情况下,如果台面550是由gan制成,那么层740可以由algan制成。

[0321]

在hemt的情况下,台面550是通道的座部,以及层740是阻挡层。

[0322]

通常地,氮化物台面550具有与基板100的顶面垂直测量的厚度,约为10μm。通常地,阻挡层740的厚度约为25nm。

[0323]

图13b示出了形成在相同基板100的表面处并搁置在垫上的多个这种类型的结构。不言而喻,这些结构可以使用上文所述的任何方法来形成。

[0324]

图13c示出了图13a中所示结构的替代性结构。在图13c所示的、也可用于形成hemt的结构中,台面550搁置在垫上,并被以下连续的层叠覆,这些层从台面550的顶面551堆叠:

[0325]-背面阻挡层710(通常称为背面阻挡)。例如,该层是由algan/pgan制成。层的厚度可以被包括在50-100nm之间。该层是可选的。该层提高了二维电子气的限域性(confinement)。

[0326]-层720,用于形成晶体管的通道。该层优选地由gan制成或是gan基。例如,层的厚度被包括在100纳米至300纳米之间。

[0327]-间隔层730。该层优选地由aln制成或是aln基。例如,间隔层的厚度约为1纳米。该层是可选的。该层提高了限域性,并因此增加了电荷载流子的迁移性。

[0328]-层740,用于形成用于晶体管的阻挡层。该层优选地由algan制成或是algan基。例如,层的厚度被包括在10至25纳米之间。

[0329]-钝化层750。该层优选地由氮化物制成,例如sin。例如,层的厚度被包括在2至50纳米之间。该层是可选的。该层可以防止电荷滞留在表面处。

[0330]

氮化物台面550的厚度可以约为10微米。

[0331]

优选地,层710、720、730、740是外延形成的,优选地由氮化物台面550形成。该层750可以通过cvd(化学气相沉积)或mocvd(金属有机化学气相沉积)来沉积。

[0332]

图13a和图13c中的结构可以经过附加的步骤,特别是用于移除垫。

[0333]

所提出的方法的一个相当大的优点是,它允许生产具有很少或没有断裂、位错并且具有很少或没有晶圆变形的大厚度台面550,台面的厚度通常大于5微米,优选地约为10微米。该大厚度氮化物层减少了竖向泄漏并增加了击穿电压。因此,所提出的方法相当大地提高了功率晶体管诸如hemt的性能水平。

[0334]

图14a示出了基板100,在该基板上搁置有多个器件,每个器件意在形成hemt 554。每个晶体管554具有源极760、漏极770和栅极180。这个实施方式的优点是特别容易实施。

[0335]

图14b示出了替代性实施方式,其中介电层将不同的晶体管554分离。例如,该介电层910是通过离心法沉积的,并且可以是sog(旋涂式玻璃)类型。该介电层910在机械上稳定了台面550。

[0336]

该介电层910还可以电隔离不同的晶体管554,特别是在晶体管处于运行中时将不同的晶体管电隔离。如图14b所示,介电层910的一部分911有效地分离了相邻的晶体管554。

例如,这可以防止在彼此面对的源极760之间或彼此面对的漏极770之间短路,如图14a所示。更具体地,两个相邻的晶体管554的源极和漏极优选地对称设置。如下文参照图16a至图17所看到的,这促进源极760和漏极770的后续连接。特别地,这允许高电压和低电压处于相同位置处。

[0337]

现在将参照图15a至图15d来描述晶体管554的一个示例性实施方式。该晶体管可以与图14b中所示的晶体管相同。

[0338]

图15a示出了由垫200、300、400叠覆的基板100,这些垫支撑台面550和至少阻挡层740。不言而喻,可以存在至少一个并优选地存在多个前述层710、720、730、750。优选地,如参考图14b所述,介电层910被沉积。该介电层910覆盖结构554中每一者的自由面。随后将操作基板920附接到介电层910的自由面。

[0339]

如图15b所示,基板100和垫随后被移除。例如,这可以通过蚀刻、研磨或化学机械抛光(cmp)来发生。该移除是持续的,直到氮化物台面550的一个面被制成为可访问。优选地,在通过减薄来进行该移除之前,叠置件将已被翻转。

[0340]

如图15c所示,随后将附加的基板930附接到氮化物台面550的可访问面。然后,移除操作基板920。保留附加的基板930。这可以是最终的基板。

[0341]

随后,移除保护性介电层910以使阻挡层740可访问。

[0342]

随后可以形成源极760、漏极770和栅极780,以最终确定晶体管554。

[0343]

优选地,介电层910的位于两个晶体管554之间的部分被保留。

[0344]

图16a示出了图15d所示的结构的俯视图。

[0345]

该图16a还强调了属于两个相邻晶体管554的源极760、漏极770和栅极780的对称设置。

[0346]

因此,轴线x1是用于设置属于两个相邻晶体管554的源极760、漏极770和栅极780的对称轴线,而轴线x2是属于用于设置另外两个相邻晶体管554的源极760、漏极770和栅极780的对称轴线。

[0347]

如图16b所示,其他两个相邻的晶体管554之间的这种对称性促进了:

[0348]-源极760与公共电接触点760'的连接,

[0349]-漏极770与公共电接触点770'的连接,

[0350]-栅极780与公共电接触点780'的连接。

[0351]

图17示出了图15d和图16a中所示结构的替代性结构的俯视图。在该替代性结构中,每个晶体管554具有中央漏极770、以及源极760、和两个栅极780。源极760被设置在漏极770的两侧。栅极780也被设置在漏极770的两侧。

[0352]

从上述描述中很明显的是,本发明提出了一种用于获得多个外延生长台面的特别有效的解决方案,每个台面意在形成使缺陷密度相当大地降低的micro-led。

[0353]

本发明并不局限于上文所述的实施方式,并且还包括权利要求书中所涵盖的所有实施方式。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。