1.本发明涉及计算机领域,尤其涉及一种缓冲器、存储器设备和内存总线信号处理方法。

背景技术:

2.双倍速率同步动态随机存储存储器(double data rate synchronous dynamic random access memory,ddr sdram)是电子系统中常用的内存系统解决方案。自2014年联合电子设备工程委员会(joint electron device engineering council,jedec)正式推出ddr4以来,被广泛应用到电子产品中,如个人电脑、服务器、嵌入式系统、消费类电子产品。

3.为了得到更好的性能,jedec在2020年发布了ddr5标准。ddr5是新技术,ddr5内存颗粒初期有成本高、产能低和质量有风险等问题。

技术实现要素:

4.本技术公开了一种缓冲器、存储器设备、计算机系统和信号处理方法,存储器设备包括内存颗粒和缓冲器,通过缓冲器将处理器侧的第一内存总线上的信号转换成内存颗粒相匹配的第二内存总线上的信号。使用支持旧标准的内存颗粒实现新标准存储器设备的性能,解决新标准内存颗粒初期成本高、产能低和质量有风险的问题。

5.第一方面,本技术提供了一种缓冲器,用于以第一内存总线连接到处理器和以第二内存总线连接到内存颗粒;第一内存总线和第二内存总线遵循不同的标准。通过该方案,可以使遵循不同内存标准的处理器和内存颗粒进行匹配和正常工作,例如,支持ddr5标准的处理器和支持ddr4的内存颗粒进行匹配和正常工作,实现ddr5标准的性能。

6.一种可能的实施方式中,第一内存总线和第二内存总线遵循不同的标准包括:第一内存总线的信号线数量和第二内存总线的信号线数量不同。

7.一种可能的实施方式中,缓冲器还用于将第一内存总线上的信号转换成第二内存总线上的信号。通过该技术方案,可以让第一内存总线上的信号和第二内存总线上的信号匹配。

8.一种可能的实施方式中,第二内存总线包括多个子总线。利用多个子总线连接到不同的内存颗粒上,实现总线整体带宽的增加。

9.一种可能的实施方式中,多个子总线中的至少任意两个用于连接不同内存颗粒。

10.一种可能的实施方式中,第一内存总线上信号的数据率和第二内存总线上信号的数据率不同。

11.一种可能的实施方式中,第一内存总线为ddr5总线或一种内存标准总线。

12.一种可能的实施方式中,第二内存总线为ddr4总线。

13.一种可能的实施方式中,缓冲器是数据缓冲器和/或寄存器时钟驱动器。

14.第二方面,本技术提供了一种内存总线信号处理的方法,包括:获取第一内存总线上的信号,将第一内存总线上的信号转换成第二内存总线上的信号;通过该技术方案,可以

让第一内存总线上的信号和第二内存总线上的信号匹配。

15.第一内存总线上的信号和第二内存总线上的信号遵循不同的协议。

16.一种可能的实施方式中,第一内存总线上信号的数据率和第二内存总线上信号的数据率不同。

17.一种可能的实施方式中,第一内存总线为ddr5总线或一种内存标准总线。

18.一种可能的实施方式中,第二内存总线为ddr4总线。

19.一种可能的实施方式中,信号包括:数据信号和控制信号。

20.第三方面,本技术提供一种存储器设备,包括缓冲器和多个内存颗粒,缓冲器是第一方面中任一种可能的实施方式中任一缓冲器。

21.第四方面,本技术提供了一种计算机系统包括存储器设备和处理器,存储器设备是第三方面中的存储器设备。

附图说明

22.图1a:ddr4标准的存储器设备的结构示意图;

23.图1b:ddr5标准的存储器设备的结构示意图;

24.图2a:本技术实施例提供的一种存储器设备的结构示意图;

25.图2b:本技术实施例提供的一种rcd转换控制信号的示意图;

26.图2c:本技术实施例提供的一种db转换数据信号的示意图;

27.图3a:本技术实施例提供的另一种rcd转换控制信号的示意图;

28.图3b:本技术实施例提供的另一种db转换数据信号的示意图;

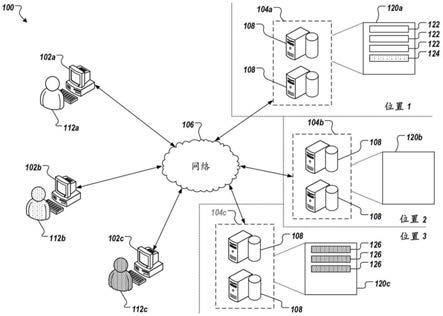

29.图4:本技术实施例提供的一种计算机系统结构示意图。

具体实施方式

30.图1a所示为ddr4标准的存储器设备100的结构示意图,存储器设备100包括电路板102,多颗ddr4内存颗粒104,至少一颗数据缓冲器(data buffer,db)114,至少一颗寄存器时钟驱动器(register clock driver,rcd)112,连接部108。各个db 114通过数据信号总线106连接到各个ddr4内存颗粒104,rcd112通过控制信号总线110连接到各个ddr4内存颗粒104。控制信号总线118连接rcd 112和处理器,数据信号总线116连接各个db 114和处理器。数据信号总线116上信号的数据率和数据信号总线106上信号的数据率是相同的,例如都是3200兆次数据传输每秒(mega-transfer per second,mt/s),对应的,控制信号总线118上信号的数据率是1600mt/s,控制信号总线110上信号的数据率也是1600mt/s。

31.图1b所示为ddr5标准的存储器设备120的结构示意图,存储器设备120包括电路板122,多颗ddr5内存颗粒130,至少一颗db 132,至少一颗rcd 136,连接部134。各个db 132通过数据信号总线128连接到各个ddr5内存颗粒130,rcd 136通过控制信号总线124连接到各个ddr5内存颗粒130。控制信号总线140连接rcd 136和处理器,数据信号总线140连接各个db 132和处理器。根据ddr5标准,存储器设备120拥有两个内存通道,如图1b所示,存储器设备120拥有通道138和通道126,而作为对比图1a所示符合ddr4标准的存储器设备100只有一个通道。因此存储器设备120的通道138中的内存颗粒的控制信号总线上的信号和通道126中的内存颗粒的控制信号总线上的信号可以是不同的。按ddr5标准的存储器设备120,其中

数据信号总线140和128上信号的数据率最高可以达到6400mt/s,对应的控制信号总线142上信号的数据率最高可以到6400mt/s,而控制信号总线124上信号的数据率最高可以到3200mt/s。

32.ddr5内存颗粒的失效率高,成本高,而ddr4内存颗粒的失效率低,质量好,成本低。因此,本技术实施例提供一种技术方案,使用ddr4颗粒,替换ddr5内存颗粒,达到和ddr5标准下的存储器设备120相同的性能。

33.如图2a所示为本技术实施例提供的存储器设备200的结构示意图,在该实施例中,存储器设备200包括:电路板202,多颗ddr4内存颗粒,至少一颗db211,至少一个rcd 214和连接部212。各个db 211通过数据信号总线206连接到各个ddr4内存颗粒210,rcd 214通过控制信号总线216连接到各个ddr4内存颗粒210。控制信号总线220连接rcd 214和处理器,数据信号总线218连接各个db 211和处理器。其中,数据信号总线206和控制信号总线216遵循ddr4标准的数据信号总线和控制信号总线,另外数据信号总线218和控制信号总线220遵循ddr5标准的数据信号总线和控制总线。上述连接部可以是金手指,也可以是其他连接形态的结构。存储器设备可以是内存条或者别的结构形态的存储器设备。

34.该存储器设备200也拥有两个通道,分别是通道204和通道222,其中通道204和通道222的控制信号总线上的信号可以是不同的。

35.连接部212遵循ddr5标准定义的数字信号总线和控制信号总线,具体的,在一种可行的方式中,每个db上的数字信号总线包括1组8根数据信号线通过连接部212连接到处理器,每个rcd上的控制信号总线包括2组7根控制信号线通过连接部212连接到处理器。

36.在图2a所示的结构的存储器设备200基础上,提出一种信号转换的方案,如图2b所示,数据信号总线218和控制信号总线220上的信号在本技术实施例遵循ddr4协议,具体的,数据信号总线218上收发的是经过编码的ddr4协议的数据信号,而控制信号总线220上收发的是经过编码的ddr4协议的控制信号。可选的,该编码过程经过处理器处理,由处理器完成。

37.具体的,控制信号总线220上的信号经过rcd 214转换成控制信号总线208上的信号,其中可以看到控制总线220上信号的数据率是控制信号总线208上信号的数据率的4倍。例如控制总线220上遵循ddr4协议的信号的数据率是6400mt/s,总线位宽和ddr5标准的控制总线位宽一样,都是2组,每组7bit,则经过rcd 214转换后,在控制信号总线208上得到遵循ddr4协议的信号,数据率是1600mt/s,而位宽是2组,每组24bit。容易理解,rcd 214将ddr5标准的总线上收发的ddr4协议的控制信号转换成ddr4标准的总线上收发的ddr4协议的控制信号。将控制信号总线220上两个周期内的信号[d1:d24]转换成控制信号总线208上一个周期内的信号[d1:d24]。

[0038]

同样的道理,如图2c所示,数据信号总线218上的信号经过db 211后转换成数字信号总线206上的信号。数据信号总线218上的信号的数据率是数据信号总线206上的2倍,例如数据信号总线218上的信号的数据率是6400mt/s,位宽为1组,每组8bit,而数据信号总线206上的信号的数据率是3200mt/s,位宽为2组,每组8bit。同样容易理解,db 211将ddr5标准的总线上收发的ddr4协议的数据信号转换成ddr4标准的总线上收发的ddr4协议的信号。将数据信号总线218上遵循该内存标准的8bit位宽的数据信号[d1,d2

…

d2n]转换成数据信号总线206上2组,每组8bit数据信号,一组取数据信号的奇数序号的数据信号[d1,d3

…d(2n 1)],另一组取数据信号的偶数序号的数据信号[d2,d4

…

d(2n)]。其中,数据信号总线206上的每组8bit位宽的数据信号是遵循ddr4协议的数据信号。

[0039]

在图2a所示的结构的存储器设备200基础上,提出另外一种信号转换的方案,,如图3a所示,控制信号总线220上遵循ddr5协议的信号经过rcd 302后的转换成控制信号总线208上遵循ddr4协议的信号,例如,两个周期内4组ddr5协议的控制信号[c1_1:c7_1],[c1_2:c7_2],[c1_3:c7_3],[c1_4:c7_4],经过rcd302转换成一个周期内遵循ddr4协议的信号[d1:d24]。总结为rcd 302将ddr5标准的总线上收发的ddr5协议的控制信号转换成ddr4标准的总线上收发的ddr4协议的控制信号。控制总线220上是ddr5协议的信号的数据率是6400mt/s,总线位宽按照ddr5标准是2组,每组7bit,则经过rcd 302转换后,得到控制信号总线208,遵循ddr4协议的控制信号,数据率是1600mt/s,而位宽是2组,每组24bit。控制总线220上信号的数据率是控制总线208上信号的数据率的4倍

[0040]

同理在图3b所示,数据信号总线218上遵循ddr5协议的数据信号经过db304后转换成数字信号总线206上遵循ddr4协议的数据信号。例如将数据信号总线218上遵循ddr5协议的8bit位宽的数据信号[d1,d2

…

d2n]转换成数据信号总线206上2组,每组8bit数据信号,一组取数据信号的奇数序号的数据信号[d1,d3

…

d(2n 1)],另一组取数据信号的偶数序号的数据信号[d2,d4

…

d(2n)]。其中,数据信号总线206上的每组8bit位宽的数据信号是遵循ddr4协议的数据信号。

[0041]

db 304将ddr5标准的总线上收发的ddr5协议的数据信号转换成ddr4标准的总线上收发的ddr4协议的数据信号。数据信号总线218上的信号的数据率是6400mt/s,位宽为1组,每组8bit,经过db 304转换后,数据信号总线211上的信号的数据率是3200mt/s位宽为2组,每组8bit。数据信号总线218上的信号的数据率是数据信号总线211上的2倍

[0042]

在本技术实施例中,单个rcd或db上的各总线具体位宽和数据率只是举例说明,并不对此进行限制。例如数据率可以是从支持4800mt/s的内存总线上的信号转换成支持2400mt/s的drr4内存总线上的信号等等情况。内存总线包括数据信号总线和控制信号总线。另外,ddr4标准和ddr5标准只是本技术一种实施例的具体举例,本技术不对内存总线遵循的标准做具体限定,例如,还可以将ddr4标准的内存总线上的信号通过缓冲器转换成ddr3标准的内存总线上的信号等等涉及不同内存标准之间进行转换的技术方案都是本技术所要保护的范围。另外,上述遵循ddr4协议包括总线上信号的报文格式遵循ddr4协议,遵循ddr5协议包括总线上信号的报文格式遵循ddr5协议。

[0043]

本发明实施例提供一种如图4所示的计算机系统400,该计算机系统400包括本技术实施例所描述的存储器设备。如图4所示,计算机系统400包括处理器402、通信接口406、总线708和存储器设备410。其中,处理器402、和通信接口406通过总线408实现彼此之间的通信连接。

[0044]

处理器402是计算机系统400的控制中心,可以采用通用的中央处理器,微处理器,专用集成电路,或者一个或多个集成电路,用于执行相关程序,以实现本发明实施例所提供的技术方案。

[0045]

通信接口406使用例如但不限于收发器一类的收发装置,来实现装置400与其他设备或通信网络之间的通信。

[0046]

总线408可包括一个线路或多个线路,在装置400各个部件(例如处理器402、存储

器设备410和通信接口406)之间传送信息。

[0047]

应注意,尽管图4所示的计算机系统400仅仅示出了处理器402、通信接口406、总线408和存储器设备410,但是在具体实现过程中,本领域的技术人员应当明白,计算机系统400还包含实现正常运行所必须的其他器件。同时,根据具体需要,本领域的技术人员应当明白,计算机系统400还可包含实现其他附加功能的硬件器件。此外,本领域的技术人员应当明白,计算机系统400也可仅仅包含实现本发明实施例所必须的器件,而不必包含图4中所示的全部器件。

[0048]

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案脱离权利要求的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。