1.本发明系有关于半导体结构,且特别有关于存储器结构。

背景技术:

2.动态随机存取存储器(dynamic random access memories;drams)已广泛地使用于计算机系统的主存储器(main memory)。然而,随着存储器技术逐渐接近物理极限,传统的dram,例如1晶体管1电容(1t1c)dram,正面临许多严峻的挑战,例如高漏电流(leakage current)使存储器结构的可靠度(reliability)下降、随着存储器结构愈来愈小而益发复杂的工艺与高昂生产成本、dram的「动态」特性导致耗电量大、以及由于复杂的控制电路使存储器结构的可扩展性(scalability)不佳等问题。

3.因此,为了满足市场需求,缩小存储器结构的尺寸且同时维持存储器结构的性能表现系为重要的。

技术实现要素:

4.本发明系有关于存储器结构。

5.根据一实施例,存储器结构包含第一通道本体、第一源极区、第一漏极区、第一栅极结构与第二栅极结构。第一源极区具有第一导电类型且连接至第一通道本体的第一端。第一漏极区具有第二导电类型且连接至第一通道本体的第二端,第二端和第一端分离。第一栅极结构设置为相邻于第一通道本体且介于第一端与第二端之间。第二栅极结构设置为相邻于第一通道本体且介于第一端与第二端之间。

6.为了对本发明的上述及其他方面有更好的了解,下文特举实施例,并配合所附附图详细说明如下。

附图说明

7.图1a系绘示根据本发明的一实施例的存储器结构的示意立体图;

8.图1b系为沿着图1a所示的aa

′

剖面线延伸画出的根据本发明的一实施例的存储器结构的示意剖面图;

9.图2系绘示根据本发明的一实施例的存储器结构在多种操作模式下的测试结果;

10.图3a-图3f系绘示根据本发明的一实施例的存储器结构的载流子能量分布图;

11.图4系绘示根据本发明的一实施例的存储器结构的测试结果;

12.图5系绘示根据本发明的一实施例的存储器结构的示意剖面图;

13.图6系绘示根据本发明的一实施例的存储器结构的示意剖面图;

14.图7系绘示根据本发明的一实施例的存储器结构的示意剖面图;

15.图8a-图8f系绘示根据本发明的一实施例的存储器结构的载流子能量分布图;

16.图9系绘示根据本发明的一实施例的存储器结构的测试结果;

17.图10系绘示根据本发明的一实施例的存储器结构的示意剖面图;

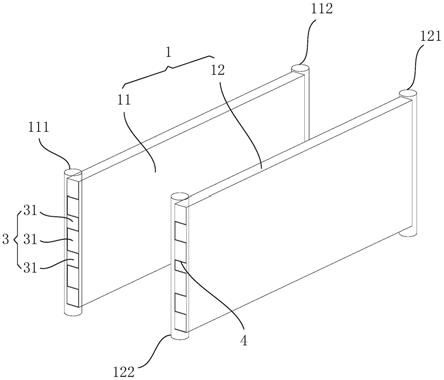

18.图11a系绘示根据本发明的一实施例的存储器结构的示意立体图;

19.图11b系为沿着图11a所示的bb

′

剖面线延伸画出的根据本发明的一实施例的存储器结构的示意剖面图;

20.图11c系为沿着图11a所示的cc

′

剖面线延伸画出的根据本发明的一实施例的存储器结构的示意剖面图;

21.图12系绘示根据本发明的一实施例的存储器结构的测试结果;

22.图13a系绘示根据本发明的一实施例的存储器结构的示意立体图;

23.图13b系为沿着图13a所示的dd

′

剖面线延伸画出的根据本发明的一实施例的存储器结构的示意剖面图;

24.图14a系绘示根据本发明的一实施例的存储器结构的示意立体图;

25.图14b系为沿着图14a所示的ee

′

剖面线延伸画出的根据本发明的一实施例的存储器结构的示意剖面图;

26.图14c系为沿着图14a所示的ff

′

剖面线延伸画出的根据本发明的一实施例的存储器结构的示意剖面图;及

27.图15系绘示根据本发明的一实施例的存储器结构的示意性电路图。

28.【符号说明】

29.10,11,13,14,50,70,70a:存储器结构

30.14t1,14t2,14t3,14t4,14t5,14t6,14t7,14t8:晶体管

31.100,700,1100,1400:通道本体

32.100a,700a,1100a,1400a:第一端

33.100b,700b,1100b,1400b:第二端

34.100n,100p,700n,700p:区域

35.101,701,1101,1401:源极区

36.102,702,1102,1402:漏极区

37.103,703,1003,1103,1303,1403:第一栅极结构

38.104,704,1004,1104,1305,1404:第二栅极结构

39.107,720:衬底

40.108,708:第一栅极介电层

41.109,709,1009:第一栅电极

42.110,710:第二栅极介电层

43.111,711,1011:第二栅电极

44.143,144:漏极连接部

45.145,146:源极连接部

46.512,612:连接区

47.705,1005,1304,1405:第三栅极结构

48.712:第三栅极介电层

49.713,1013:第三栅电极

50.1020,1460:介电膜

51.1103a,1303b,1304b,1403b:偶数部

52.1103b,1303a,1304a,1403a:奇数部

53.1104a,1305a,1404a,1405a:第一部

54.1104b,1305b,1404b,1405b:第二部

55.1104c,1305e,1404c,1405c:连接部

56.1305c:第三部

57.1305d:第四部

58.141a,141b,141c,142a,142b,142c,1111,1112,1113:柱状体

59.aa

′

,bb

′

,cc

′

,dd

′

,ee

′

,ff

′

:剖面线

60.bl_0,bl_1:位线

61.blt_0,blt_1:漏极选择线

62.cd1:尺寸

63.d1:第一方向

64.d2:第二方向

65.d3:第三方向

66.g1:间隙

67.sl_0,sl_1:源极线

68.slt_0,slt_1:源极选择线

69.w1,w2:长度

具体实施方式

70.以下系提出相关实施例,配合附图以详细说明本发明所提出的存储器结构。然而,本发明并不以此为限。实施例中的叙述,例如局部结构、制造方法的步骤和材料应用等,仅为举例说明之用,本发明欲保护的范围并非仅限于所述实例。

71.同时,须注意的是,本发明并非显示出所有可能的实施例。相关技术领域者当可在不脱离本发明的精神和范围的前提下,对实施例的结构和制造方法加以变化与修饰,以符合实际应用所需。因此,未于本发明提出的其他实施态样也可能可以应用。再者,附图系简化以利清楚说明实施例的内容,附图上的尺寸比例并非按照实际产品等比例绘制。因此,说明书和附图仅作叙述实施例之用,而非用以限缩本发明保护范围。相同或相似的元件符号用以代表相同或相似的原件。

72.根据本发明的多个实施例,提供存储器结构,其中存储器结构在操作期间像晶体闸流管(thyristor)一样运作,从而可显著改善做为dram的存储器结构的可靠度、信息保存时间(retention time)、耗电量与可扩展性。因此,实施例的设计可提升存储器结构的性能表现,且使存储器结构达成高存储密度(density)。

73.图1a系绘示根据本发明的一实施例的存储器结构的示意立体图,图1b系为沿着图1a所示的aa

′

剖面线延伸画出的存储器结构的示意剖面图。请同时参照图1a-图1b,存储器结构10包含衬底10、通道本体100、源极区101、漏极区102、第一栅极结构103与第二栅极结构104。衬底107可包含半导体衬底,例如块状硅(bulk silicon)衬底、绝缘层上硅(silicon-on-insulator;soi)衬底或薄膜晶体管(thin-film transistor;tft)衬底。源极区101形成于衬底107的上表面上。通道本体100沿着垂直于源极区101的上表面的第一方向

d1(例如是z方向)向上延伸。漏极区102形成于通道本体100上。源极区101、通道本体100与漏极区102沿着第一方向d1配置。

74.具体而言,源极区101连接至通道本体100的第一端100a。漏极区102连接至通道本体100的第二端100b。通道本体100的第二端100b和通道本体100的第一端100a分离,且分别位于通道本体100沿着第一方向d1的两相对端部。在一实施例中,第一端100a可接近衬底107的上表面,而第二端100b远离衬底107的上表面。

75.在此实施例中,通道本体100可分别于第一端100a与第二端100b直接接触源极区101与漏极区102。源极区101具有第一导电类型,漏极区102具有第二导电类型,第二导电类型和第一导电类型不同。源极区101与漏极区102可包含半导体材料,例如硅(silicon)。在一实施例中,第一导电类型可为n型(n-type),第二导电类型可为p型(p-type)。或者,在另一实施例中,第一导电类型可为p型,第二导电类型可为n型。

76.例如,在此实施例中,源极区101可为具有高掺杂浓度的n型(即n ),且漏极区102可为具有高掺杂浓度的p型(即p )。在其他的实施例中,源极区101与漏极区102可具有反向配置,例如,漏极区102可形成于衬底107的上表面上,且连接至通道本体100的第一端100a,源极区101可连接至通道本体100的第二端100b。

77.通道本体100可包含掺杂的半导体材料或未掺杂的半导体材料。通道本体100可包含单晶硅(single-crystal silicon)或多晶硅(polysilicon)。在一实施例中,通道本体100可包含掺杂的硅,具有n型掺杂区位于p型掺杂区上。

78.第一栅极结构103设置为相邻于通道本体100且介于通道本体100的第一端100a与第二端100b之间。第二栅极结构104设置为相邻于通道本体100且介于通道本体100的第一端100a与通道本体100的第二端100b之间。具体而言,第一栅极结构103与第二栅极结构104设置于通道本体100的侧壁上。

79.具体而言,第一栅极结构103与第二栅极结构104可延伸于第二方向d2(例如是y方向)与第三方向d3(例如是x方向)所定义的平面上。第一方向d1、第二方向d2与第三方向d3彼此相互垂直。第一栅极结构103可具有垂直于第一方向d1的上表面。第二栅极结构104可沿着第一方向d1设置于第一栅极结构103的上表面上。在此实施例中,存储器结构10可视为垂直通道型存储器。在一实施例中,第一栅极结构103与第二栅极结构104可至少部分围绕通道本体100。在另一实施例中,通道本体100可被第一栅极结构103与第二栅极结构104包围,以形成栅极环绕式(gate-all-around)存储器结构。

80.第一栅极结构103可包含第一栅电极109与第一栅极介电层108,第一栅极介电层108使第一栅电极109电性绝缘于通道本体100。具体而言,第一栅极介电层108连接至通道本体100,第一栅电极109连接至第一栅极介电层108。第二栅极结构104可包含第二栅电极111与第二栅极介电层110,第二栅极介电层110使第二栅电极111电性绝缘于通道本体100。具体而言,第二栅极介电层110连接至通道本体100,第二栅电极111连接至第二栅极介电层110。第一栅电极109与第二栅电极111可由相同材料形成。类似地,第一栅极介电层108与第二栅极介电层110可由相同材料形成。

81.例如,在一实施例中,第一栅极介电层108与第二栅极介电层110可包含介电材料;介电材料可包含氧化物,例如氧化硅(silicon oxide)。在另一实施例中,第一栅极介电层108与第二栅极介电层110可包含高介电常数(high dielectric constant;high-k)材料。

在又一实施例中,第一栅极介电层108与第二栅极介电层110可包含氧化物-氮化物-氧化物(oxide-nitride-oxide;ono)结构。第一栅电极109与第二栅电极111可包含半导体材料或金属材料。例如,第一栅电极109与第二栅电极111可包含单晶硅或多晶硅。

82.第一栅极结构103可做为存储器结构10的控制栅极(control gate;cg),且第二栅极结构104可做为存储器结构10的辅助栅极(assisting gate;ag),但本发明不限于此。当第一栅极结构103被施加第一电压,且第二栅极结构104被施加第二电压,通道本体100可分为至少两区域100n和100p,区域100n与区域100p具有不同的电荷载流子(charge carriers)密度且分别设置为相邻于第二栅极结构104与第一栅极结构103,电荷载流子例如是空穴(holes)。因此,漏极区102、通道本体100的至少两区域100n和100p、及源极区101可做为晶体闸流管,且第一栅极结构103可用来做为栅极以开启或关闭晶体闸流管。在此实施例中,图1a-图1b所示的存储器结构10可充当2-晶体管(2t)晶体闸流管随机存取存储器(thyristor random access memory;t-ram)。

83.例如,图1a-图1b所示的存储器结构10的操作表现可使用半导体工艺模拟以及器件模拟(technology computer aided design;tcad)工具通过计算机仿真来观察。在模拟期间,列于表1的不同偏压可施加于源极区101、漏极区102、第一栅极结构103、第二栅极结构104与衬底107,以进行不同的操作模式例如是编程(programming)、读取(reading)、维持(hold)或擦除(erasing)操作模式。在此实施例与附图中,

″

write 1

″

表示使存储器结构10的存储单元编程为

″1″

的信息状态(即为逻辑

″1″

)的操作模式;

″

write 0

″

表示使存储器结构10的存储单元编程为

″0″

的信息状态(即为逻辑

″0″

)的操作模式;

″

hold

″

表示用以维持存储器结构10的存储单元的电压信息状态的操作模式(包含

″

hold 1

″

与

″

hold 0

″

),此电压信息状态由先前的

″

write

″

操作模式(

″

write 1

″

或

″

write 0

″

)所决定;

″

read

″

表示读取存储器结构10的存储单元以确认个别存储单元的电压信息状态的操作模式(包含

″

read 1

″

与

″

read 0

″

),此电压信息状态由先前的

″

hold

″

操作模式(

″

hold 1

″

或

″

hold 0

″

)所决定。

84.[表1]

[0085][0086][0087]

图2系绘示存储器结构10在如表1所示的偏压条件下的测试结果,曲线201表示漏极电流(id)-时间,曲线202表示通道本体100中相邻于第一栅极结构103(cg)的下部的空穴密度-时间。图3a-图3f系绘示由tcad工具计算出的存储器结构10的载流子能量分布,此时存储器结构10被施加如表1所示的偏压条件。图3a与图3d分别绘示

″

write 1

″

操作模式与

″

write 0

″

操作模式的结果,图3b与图3e分别绘示

″

hold 1

″

操作模式与

″

hold 0

″

操作模式的结果,图3c与图3f分别绘示

″

read 1

″

操作模式与

″

read 0

″

操作模式的结果。上述操作方案系有关于在表1所示的偏压条件下使空穴移入与移出存储区。在施加另一组偏压条件的情况下,电子亦可以相似的方式移入与移出存储区。

[0088]

请同时参照图2与图3a,在

″

write 1

″

操作模式中,由于施加于第一栅极结构103与第二栅极结构104的电压皆小于施加于漏极区102的电压,空穴从漏极区102移动至通道本体100。请同时参照图2与图3d,在

″

write 0

″

操作模式中,没有阻止空穴的势阱(potential well)形成,从而多数空穴从通道本体100离开。

[0089]

请同时参照图2与图3b,在

″

hold 1

″

操作模式中,第一栅极结构103被施加-1.2伏特(v)的负偏压;且施加于第二栅极结构104的电压提升至1.2v,以使多数空穴聚集于通道本体100中相邻于第一栅极结构103的下部(区域100p)。在此情况下,通道100可分为两区域,例如是区域100n(通道本体100中相邻于第二栅极结构104的上部)和区域100p(通道本体100中相邻于第一栅极结构103的下部),区域100n和区域100p分别具有不同的空穴密度;漏极区102、通道本体100的区域100n和区域100p与源极区101的组合可做为具有p-n-p-n结构的晶体闸流管。因此,从源极区101流出的电子或从漏极区102流出的空穴皆可触发正回馈回路(positive feedback loop),从而导致高id。请同时参照图2与图3e,在

″

hold 0

″

操作模式中,微量的空穴存在通道本体100中,代表存储单元的

″0″

信息状态被维持,且具有少量漏电流。

[0090]

请同时参照图2与图3c,在

″

read 1

″

操作模式中,施加于源极区101的电压降至0v,且存储器结构10处于顺向偏压(forward bias)状态。通道本体100的下部的空穴密度系为高的,且高的传导电流(conduction current)(即id)流动于通道本体100中。请同时参照图2与图3f,在

″

read 0

″

操作模式中,施加于源极区101的电压降至0v,且存储器结构10处于顺向偏压状态。通道本体100的空穴密度系为低的。因此,在

″

read

″

操作模式期间,存储器结构10的能量组态(energy configuration)相似于正向闭锁模式(forward blocking mode)的p-n-p-n闸控晶体闸流管(p-n-p-n gated thyristor),且源极区101与漏极区102之间具有可忽略的微量电流。

[0091]

如图2所示,在

″

read 1

″

操作模式中的id大约1毫安(milliampere;ma),且在

″

read 0

″

操作模式中的id大约0.1皮安培(picoampere;pa)。在

″

read 1

″

操作模式中的id与在

″

read 0

″

操作模式中的id之间的差异系为大的,代表存储器结构10的感测范围(sensing margin)系为大的。

[0092]

图4系绘示本发明提供的存储器结构10的id-保持时间(hold time)曲线,在

″

read 1

″

操作模式与

″

read 0

″

操作模式下。如图4所示,在

″

read 1

″

操作模式中的id与在

″

read 0

″

操作模式中的id之间的差异在10秒(sec)时仍是明显的,代表本发明提供的存储器结构10具有至少10秒的信息保存时间。相较于传统的1t1c dram具有少于100毫秒(milliseconds)的信息保存时间,本发明的存储器结构10具有提高的信息保存时间。

[0093]

此外,本发明的存储器结构10的读取写入时间大约1纳秒(nanoseconds)。本发明的存储器结构10具有改善的读取写入表现。

[0094]

图5系绘示根据本发明的另一实施例的存储器结构50的示意剖面图。存储器结构50的结构相似于图1a-图1b所示的存储器结构10的结构,差异之处在于存储器结构50还包

括设置于漏极区102与通道本体100之间的连接区512。连接区512可使漏极区102连接至通道本体100的第二端100b。连接区512具有第一导电类型。连接区512可包含半导体材料,例如硅。在此实施例中,连接区512可为具有高掺杂浓度的n型(即n )。漏极区102、连接区512、通道本体100与源极区101的组合可做为具有p-n-p-n结构的晶体闸流管,且可结合第一栅极结构103与第二栅极结构104以充当2t t-ram,以进行编程、读取、维持或擦除操作模式。

[0095]

图6系绘示根据本发明的另一实施例的存储器结构60的示意剖面图。存储器结构60的结构相似于图1a-图1b所示的存储器结构10的结构,差异之处在于存储器结构60还包括设置于源极区101与通道本体100之间的连接区612。连接区612可使源极区101连接至该通道本体100的第一端100a。连接区612具有第二导电类型。连接区612可包含半导体材料,例如硅。在此实施例中,连接区612可为具有高掺杂浓度的p型(即p )。漏极区102、通道本体100、连接区612与源极区101的组合可做为具有p-n-p-n结构的晶体闸流管,且可结合第一栅极结构103与第二栅极结构104以充当2t t-ram,以进行编程、读取、维持或擦除操作模式。

[0096]

图7系绘示根据本发明的另一实施例的存储器结构70的示意剖面图。存储器结构70的结构相似于图1a-图1b所示的存储器结构10的结构,差异之处在于存储器结构70比存储器结构10包含更多的栅极结构。请参照图7,存储器结构70包含衬底701、通道本体700、源极区701、漏极区702、第一栅极结构703、第二栅极结构704与第三栅极结构705。

[0097]

第一栅极结构703、第二栅极结构704与第三栅极结构705设置为相邻于通道本体700,且介于通道本体700的第一端700a与第二端700b之间。第一栅极结构703可包含连接至通道本体700的第一栅极介电层708与连接至第一栅极介电层708的第一栅电极709;第二栅极结构704可包含连接至通道本体700的第二栅极介电层710与连接至第二栅极介电层710的第二栅电极711;第三栅极结构705可包含连接至通道本体700的第三栅极介电层712与连接至第三栅极介电层712的第三栅电极713。第一栅极介电层708、第二栅极介电层710与第三栅极介电层712分别使第一栅电极709、第二栅电极711与第三栅电极713电性绝缘于通道本体700。

[0098]

在本发明的一些实施例中,第一栅极介电层708、第二栅极介电层710与第三栅极介电层712可包含相似于第一栅极介电层108及/或第二栅极介电层110的材料。第一栅电极709、第二栅电极711与第三栅电极713可包含相似于第一栅电极109及/或第二栅电极111的材料。

[0099]

在一实施例中,存储器结构70可充当3-晶体管(3t)t-ram,其中第一栅极结构703、第二栅极结构704与第三栅极结构705可做为存储器结构70的字线(wl),例如,第一栅极结构703可做为wl0、第二栅极结构704可做为wl1、且第三栅极结构705可做为wl2。在此实施例中,第一栅极结构703可做为存储器结构70的辅助栅极(ag),且第二栅极结构704可做为存储器结构70的控制栅极(cg)。在一些实施例中,存储器结构70可包含多于三个栅极结构。本发明对此不加局限。

[0100]

例如,图7所示的存储器结构70的操作表现可使用tcad工具通过计算机仿真来观察。在模拟期间,列于表2的不同偏压可施加于源极区701、漏极区702、第一栅极结构703、第二栅极结构704、第三栅极结构705与衬底720,以进行不同的操作模式,例如是编程、读取、维持或擦除操作模式。

n闸控晶体闸流管,且源极区701与漏极区702之间具有可忽略的微量电流、以及高的传导电流(即id)流动于通道本体700中。请参照图8f,在

″

read 0

″

操作模式中,存储器结构70处于顺向偏压状态。通道本体700的空穴密度系为低的。因此,在

″

read

″

操作模式期间,存储器结构70的能量组态相似于正向闭锁模式的p-n-p-n闸控晶体闸流管,且源极区701与漏极区702之间具有可忽略的微量电流。

[0108]

图9系绘示本发明提供的存储器结构70的id-保持时间曲线,在

″

read 1

″

操作模式与

″

read 0

″

操作模式下。如图9所示,在

″

read 1

″

操作模式中的id与在

″

read 0

″

操作模式中的id之间的差异在10秒时仍是明显的,代表本发明提供的存储器结构70具有至少10秒的信息保存时间。相较于传统的1t1c dram具有少于100毫秒的信息保存时间,本发明的存储器结构70具有提高的信息保存时间。

[0109]

应理解的是,虽然在图8a-图8f所示的操作模式中,存储器结构70的第一栅极结构703设计为控制栅极(cg),但存储器结构70的控制栅极(cg)并不限于此种设计。设置于不相邻于源极区701与漏极区702的栅极结构,例如第二栅极结构704,可在其他操作模式中设计为存储器结构70的控制栅极(cg);通过此配置,可进一步降低存储器结构70的漏电流。

[0110]

图10系绘示根据本发明的另一实施例的存储器结构70a的示意剖面图。存储器结构70a的结构相似于图7所示的存储器结构70的结构,差异之处在于存储器结构70a包含设置于通道本体700的侧壁的介电膜1020。介电膜1020沿着第一方向d1延伸。第一栅极结构1003包含第一栅电极1009设置于介电膜1020上、第二栅极结构1004包含第二栅电极1011设置于介电膜1020上、第三栅极结构1005包含第三栅电极1013设置于介电膜1020上。换言之,介电膜1020使第一栅极结构1003、第二栅极结构1004与第三栅极结构1005接触通道本体700。介电膜1020和图7所示的存储器结构70的第一栅极介电层708、第二栅极介电层710与第三栅极介电层712不同之处在于,介电膜1020并未设置于第一栅电极1009、第二栅电极1011与第三栅电极1013沿着第一方向d1的上表面与下表面上。介电膜1020可为电荷捕捉结构,例如是ono结构,ono结构包含沿着第三方向d3依序叠层的第一氧化硅层、氮化硅层、及第二氧化硅层。在一些实施例中,ono结构可还包括浮动栅极层,例如是多晶硅。

[0111]

电荷捕捉结构的特性使得具有电荷捕捉结构的存储器结构70a中的每个存储单元可展现两个以上的可能的信息状态,从而,存储器结构70a中的每个存储单元能够存储一位(bit)以上的信息。换言之,存储器结构70a可做为多层存储(multi-level)存储器装置。

[0112]

图11a系绘示根据本发明的一实施例的存储器结构11的示意立体图。请参照图11a,存储器结构11包含沿着第二方向d2延伸的柱状体1111/1112/1113、沿着第一方向d1延伸的第一栅极结构1103与沿着第一方向d1延伸的第二栅极结构1104。柱状体1111/1112/1113沿着第一方向d1配置,且彼此相互分离。第一栅极结构1103和第二栅极结构1104分离。

[0113]

每一柱状体1111/1112/1113包含通道本体1100、源极区1101与漏极区1102,源极区1101具有第一导电类型且连接至通道本体1100的第一端1100a,漏极区1102具有第二导电类型且连接至通道本体1100的第二端1100b,第一端1100a和第二端1100b分离。第一栅极结构1103与第二栅极结构1104设置为相邻于柱状体1111/1112/1113的通道本体1100,且设置于第一端1100a与第二端1100b之间。

[0114]

具体而言,每一柱状体1111/1112/1113的源极区1101、通道本体1100与漏极区1102系沿着第二方向d2配置,第二方向d2垂直于第一方向d1。第一栅极结构1103与第二栅

极结构1104沿着第二方向d2配置。

[0115]

源极区1101可包含相似于如上所述的源极区101的材料;通道本体1100可包含相似于如上所述的通道本体100的材料;漏极区1102可包含相似于如上所述的漏极区102的材料。第一栅极结构1103与第二栅极结构1104可包含半导体材料或金属材料。在一实施例中,第一导电类型可为n型,第二导电类型可为p型。在此实施例中,源极区1101可为具有高掺杂浓度的n型(即n ),且漏极区1102可为具有高掺杂浓度的p型(即p )。

[0116]

在此实施例中,存储器结构11可被视为具有三维(three-dimensional;3d)垂直栅极的存储器结构。第一栅极结构1103可做为存储器结构11的控制栅极(cg),且第二栅极结构1104可做为存储器结构11的辅助栅极(ag),但本发明对此不加局限。每一源极区1101可电性连接于源极线,且每一漏极区1102可电性连接于位线。根据前述的类似原则,每一柱状体1111/1112/1113可充当晶体闸流管,且可结合第一栅极结构1103与第二栅极结构1104以充当2t t-ram,以进行编程、读取、维持或擦除操作模式。

[0117]

图11b系为沿着图11a所示的bb

′

剖面线延伸画出的存储器结构11的示意剖面图。请同时参照图11a-图11b,第一栅极结构1103可包含偶数部1103a与奇数部1103b,奇数部1103b和偶数部1103a分离。奇数部1103b与偶数部1103a皆沿着第一方向d1延伸,奇数部1103b与偶数部1103a沿着第三方向d3配置且分别设置于柱状体1111/1112/1113的通道本体1100的相对侧。换言之,柱状体1111/1112/1113使奇数部1103b和偶数部1103a分离。在操作期间,通过分别对奇数部1103b与偶数部1103a施加操作电压(例如是编程电压或读取电压),有助于使存储器结构11的电荷存储区和读取路径分开,从而降低存储器结构11的访问时间。

[0118]

请再次参照图11a,第二栅极结构1104可包含第一部1104a、第二部1104b与连接部1104c,连接部1104c使第一部1104a和第二部1104b连接。第一部1104a与第二部1104b皆沿着第一方向d1延伸,第一部1104a与第二部1104b沿着第三方向d3配置且分别设置于柱状体1111/1112/1113的通道本体1100的相对侧。连接部1104c沿着第三方向d3延伸,跨过柱状体1111/1112/1113。

[0119]

图11c系为沿着图11a所示的cc

′

剖面线延伸画出的存储器结构11的示意剖面图。在此实施例中,柱状体1111/1112/1113可具有沿着第三方向d3的一尺寸cd1,尺寸cd1约为30纳米(nanometer;nm);第一栅极结构1103可具有沿着第二方向d2的一长度w2,长度w2约为80纳米;第二栅极结构1104可具有沿着第二方向d2的一长度w1,长度w1约为80纳米;存储器结构11可具有沿着第二方向d2且介于第一栅极结构1103与第二栅极结构1104之间的一间隙g1,间隙g1约为30纳米。尺寸cd1可被视为位线临界尺寸(critical dimension)。在一实施例中,存储器结构11可还包括介电膜(未绘示),介电膜介于第一栅极结构1103与柱状体1111/1112/1113之间,且介于第二栅极结构1104与柱状体1111/1112/1113之间。介电膜可具有约5纳米的一厚度。第一栅极结构1103与第二栅极结构1104可通过介电膜电性绝缘于柱状体1111/1112/1113的通道本体1100。

[0120]

存储器结构11在不同操作模式下的操作表现亦可使用tcad工具通过计算机仿真来观察,测试结果列于图12。如图12所示,在读取/写入时间降低至10纳秒时,在

″

read 1

″

操作模式中的id与在

″

read 0

″

操作模式中的id之间的差异仍是大的,代表存储器结构11的感测范围系为大的。

[0121]

图13a系绘示根据本发明的一实施例的存储器结构13的示意立体图。图13b系为沿着图13a所示的dd

′

剖面线延伸画出的存储器结构13的示意剖面图。存储器结构13的结构相似于图11a-图11c所示的存储器结构11的结构,差异之处在于存储器结构13包含更多的柱状体1111/1112沿着第三方向d3配置。存储器结构13还包括第三栅极结构1304,第三栅极结构1304相邻于第一栅极结构1303。第一栅极结构1303与第三栅极结构1304沿着第三方向d3配置。第三栅极结构1304设置为相邻于柱状体1111/1112的通道本体1100,且沿着第一方向d1延伸。多个柱状体1111中的一者与多个柱状体1112中的一者使第一栅极结构1303和第三栅极结构1304分离,换言之,第一栅极结构1303和第三栅极结构1304分别设置于多个柱状体1111中的该柱状体1111的相对侧、以及多个柱状体1112中的该柱状体1112的相对侧。第二栅极结构1305和图11a所示的第二栅极结构1104不同之处在于,第二栅极结构1305可包含第一部1305a、第二部1305b、第三部1305c、第四部1305d与连接部1305e,连接部1305e使第一部1305a、第二部1305b、第三部1305c和第四部1305d连接。第一部1305a、第二部1305b、第三部1305c和第四部1305d皆沿着第一方向d1延伸。第一部1305a、第二部1305b、第三部1305c和第四部1305d沿着第三方向d3配置,且分别设置于柱状体1111/1112的通道本体1100的相对侧。连接部1305e沿着第三方向d3延伸,跨过柱状体1111/1112。第一栅极结构1303与第二栅极结构1305沿着第二方向d2配置。

[0122]

第一栅极结构1303可包含沿着第三方向d3配置的奇数部1303a与偶数部1303b,且奇数部1303a与偶数部1303b分别设置于柱状体1111/1112的通道本体1100的相对侧;第三栅极结构1304可包含沿着第三方向d3配置的奇数部1304a与偶数部1304b,且奇数部1304a与偶数部1304b分别设置于柱状体1111/1112的通道本体1100的相对侧。换言之,奇数部1303a、偶数部1303b、奇数部1304a与偶数部1304b通过柱状体1111/1112而相互分离。在操作期间,通过分别对奇数部1303a/1304a与偶数部1303b/1304b施加操作电压(例如是编程电压或读取电压),有助于使存储器结构13的电荷存储区和读取路径分开,从而降低存储器结构13的访问时间。

[0123]

在此实施例中,存储器结构13可被视为具有三维垂直栅极的存储器结构。第一栅极结构1303与第三栅极结构1304可做为存储器结构13的控制栅极(cg),且第二栅极结构1305可做为存储器结构13的辅助栅极(ag),但本发明对此不加局限。根据前述的类似原则,每一柱状体1111/1112可做为晶体闸流管,且可结合第一栅极结构1303与第二栅极结构1304以充当2t t-ram,以进行编程、读取、维持或擦除操作模式。为了对存储器结构13进行译码(decoding),每一源极区1101可电性连接于源极线,且每一漏极区1102可电性连接于位线。

[0124]

图14a系绘示根据本发明的一实施例的存储器结构14的示意立体图。请参照图14a,存储器结构14包含柱状体141a、141b和141c、柱状体142a、142b和142c、沿着第一方向d1延伸的第一栅极结构1403、沿着第一方向d1延伸的第二栅极结构1404、以及沿着第一方向d1延伸的第三栅极结构1405;柱状体141a、141b和141c沿着第二方向d2延伸且设置于相同阶层(level);柱状体142a、142b和142c沿着第二方向d2延伸且设置于相同阶层(此阶层位于柱状体141a、141b和141c的阶层的下方)。柱状体141a、141b和141c沿着第三方向d3配置,且第一栅极结构1403、第二栅极结构1404与第三栅极结构1405使柱状体141a、141b和141c相互分离。柱状体142a、142b和142c沿着第三方向d3配置,且第一栅极结构1403、第二

栅极结构1404与第三栅极结构1405使柱状体142a、142b和142c相互分离。在第一方向d1上,柱状体141a、141b和141c设置于柱状体142a、142b和142c上方且和柱状体142a、142b和142c分离。每一柱状体141a、141b、141c、142a、142b和142c包含通道本体1400、源极区1401与漏极区1402,源极区1401具有第一导电类型且连接至通道本体1400的第一端1400a,漏极区1402具有第二导电类型且连接至通道本体1400的第二端1400b,第一端1400a和第二端1400b分离。每一柱状体141a、141b和141c的通道本体1400、源极区1401与漏极区1402沿着第二方向d2配置。每一柱状体142a、142b和142c的通道本体1400、源极区1401与漏极区1402沿着第二方向d2配置。根据前述的类似原则,每一柱状体141a、141b、141c、142a、142b和142c可做为晶体闸流管,且可结合第一栅极结构1403、第二栅极结构1404与第三栅极结构1405以充当2t t-ram,以进行编程、读取、维持或擦除操作模式。

[0125]

存储器结构14还包括沿着第三方向d3延伸的漏极连接部143、漏极连接部144、源极连接部145与源极连接部146。柱状体141a、141b和141c的漏极区1402通过漏极连接部143相互连接;柱状体142a、142b和142c的漏极区1402通过漏极连接部144相互连接;柱状体141a、141b和141c的源极区1401通过源极连接部145相互连接;柱状体142a、142b和142c的源极区1401通过源极连接部146相互连接。漏极连接部143和144可包含相似于漏极区1402的材料;源极连接部145和146可包含相似于源极区1401的材料。

[0126]

在此配置下,设置于第一方向d1上的相同阶层的柱状体141a、141b和141c的源极区1401可通过源极连接部145电性连接至源极线接触结构(contact),且设置于第一方向d1上的相同阶层的柱状体142a、142b和142c的源极区1401可通过源极连接部146电性连接至另一源极线接触结构。设置于第一方向d1上的相同阶层的柱状体141a、141b和141c的漏极区1402可通过漏极连接部143电性连接至位线接触结构,且设置于第一方向d1上的相同阶层的柱状体142a、142b和142c的漏极区1402可通过漏极连接部144电性连接至另一位线接触结构。换言之,仅需要两个接触结构,例如是源极线接触结构与位线接触结构,即可使设置于相同阶层的柱状体141a、141b和141c(或者是柱状体142a、142b和142c)连接至对应的源极线与位线。相较于图13a-图13b所示的存储器结构13,存储器结构14可具有数量减少的用于位线与源极线的接触结构,且可达成具有改善的空间利用效率(area efficiency)与简单的布局(layout)的高度叠层的存储器装置。

[0127]

第一栅极结构1403、第二栅极结构1404与第三栅极结构1405设置为相邻于柱状体141a、141b、141c、142a、142b和142c的通道本体1400,且介于第一端1400a与第二端1400b之间。第一栅极结构1403、第二栅极结构1404与第三栅极结构1405沿着第二方向d2配置且彼此分离,且第一栅极结构1403沿着第二方向d2配置于第二栅极结构1404与第三栅极结构1405之间。

[0128]

第一栅极结构1403可包含奇数部1403a与偶数部1403b。奇数部1403a与偶数部1403b沿着第三方向d3配置,且分别设置于柱状体141a、141b、141c、142a、142b和142c的通道本体1400的相对侧。存储器结构14可包含一个以上的第一栅极结构1403沿着第三方向d3配置,如图14a所示。

[0129]

图14b系为沿着图14a所示的ee

′

剖面线延伸画出的存储器结构14的示意剖面图。请同时参照图14a-图14b,第二栅极结构1404可包含第一部1404a、第二部1404b与连接部1404c,连接部1404c连接第一部1404a与第二部1404b。存储器结构14可包含一个以上的第

二栅极结构1404沿着第三方向d3配置,如图14a-图14b所示。第三栅极结构1405可具有相似于第二栅极结构1404的结构。在一实施例中,第三栅极结构1405亦可包含第一部1405a、第二部1405b与连接部1405c,连接部1405c连接第一部1405a与第二部1405b。

[0130]

图14c系为沿着图14a所示的ff

′

剖面线延伸画出的存储器结构14的示意剖面图。在一实施例中,存储器结构14可还包括介电膜1460位于柱状体的侧壁上,例如是位于柱状体141c的侧壁上,如图14c所示。第一栅极结构1403、第二栅极结构1404与第三栅极结构1405可通过介电膜1460电性绝缘于柱状体141c的通道本体1400。在一实施例中,介电膜可包含高介电常数材料、ono结构、电荷捕捉层或浮动栅极层,例如多晶硅。

[0131]

请参照图14c,在此实施例中,第一栅极结构1403的奇数部1403a结合介电膜1460与柱状体141c的通道本体1400可形成晶体管14t1;第一栅极结构1403的偶数部1403b结合介电膜1460与柱状体141c的通道本体1400可形成晶体管14t2;第二栅极结构1404结合介电膜1460与柱状体141c的通道本体1400可形成晶体管14t3;第三栅极结构1405结合介电膜1460与柱状体141c的通道本体1400可形成晶体管14t4。晶体管14t1、14t2、14t3和14t4形成于相同阶层。

[0132]

相似地,第一栅极结构1403、第二栅极结构1404与第三栅极结构1405分别结合介电膜1460与柱状体142c(位于柱状体141c的下方)的通道本体1400亦可形成多个晶体管,该些晶体管设置于相同阶层,该阶层位于晶体管14t1、14t2、14t3和14t4所在的阶层之下。多个柱状体与栅极结构的组成可形成具有多层存储存储单元(multi-level level cells;mlc)的三维存储阵列。

[0133]

例如,图15系绘示存储器结构14于操作模式中的示意性电路图。在此实施例中,第一栅极结构1403的奇数部1403a结合介电膜1460与柱状体142c的通道本体1400亦可形成晶体管14t5;第一栅极结构1403的偶数部1403b结合介电膜1460与柱状体142c的通道本体1400可形成晶体管14t6;第二栅极结构1404结合介电膜1460与柱状体142c的通道本体1400可形成晶体管14t7;第三栅极结构1405结合介电膜1460与柱状体142c的通道本体1400可形成晶体管14t8。晶体管14t5、14t6、14t7和14t8形成于相同阶层。

[0134]

设置于相同阶层的柱状体141c的源极区1401与柱状体141b的源极区1401可通过源极连接部145连接至源极线sl_1。设置于相同阶层的柱状体142c的源极区1401与柱状体142b的源极区1401可通过源极连接部146连接至源极线sl_0。设置于相同阶层的柱状体141c的源极区1401与柱状体141b的源极区1401可连接至串列选择线;设置于相同阶层的柱状体142c的源极区1401与柱状体142b的源极区1401可连接至另一串列选择线。

[0135]

设置于相同阶层的柱状体141c的漏极区1402与柱状体141b的漏极区1402可通过漏极连接部143连接至位线bl_1。设置于相同阶层的柱状体142c的漏极区1402与柱状体142b的漏极区1402可通过漏极连接部144连接至位线bl_0。

[0136]

晶体管14t4与14t8可连接至源极选择线slt_0且分别充当串列选择晶体管。晶体管14t3与14t7可连接至漏极选择线blt_0且分别充当位线选择晶体管。晶体管14t1、14t2、14t5和14t6可充当存储晶体管(memory transistors)。存储器结构14还可包含更多晶体管连接至其他源极选择线及/或其他漏极选择线,例如源极选择线slt_1及/或漏极选择线blt_1。

[0137]

相较于传统的易失性存储器装置,根据本发明的存储结构可提供低漏电流、高感

测范围、简单的布局、长的信息保存时间、低耗电量与高度可扩展性。因此,本发明可达成具有优化的性能表现的存储器结构。

[0138]

应注意的是,如上所述的附图、结构和步骤,是用以叙述本发明的部分实施例或应用例,本发明并不限制于上述结构和步骤的范围与应用态样。其他不同结构态样的实施例,例如不同内部元件的已知构件都可应用,其示例的结构和步骤可根据实际应用的需求而调整。因此附图的结构仅用以举例说明之,而非用以限制本发明。本领域技术人员当知,应用本发明的相关结构和步骤过程,例如半导体结构中的相关元件和层的排列方式或构型,或制造步骤细节等,都可能依实际应用样态所需而可能有相应的调整和变化。

[0139]

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。