1.本发明涉及一种组合物及使用其的光致抗蚀剂的去除方法,所述组合物用于在下述电路图案形成后将光致抗蚀剂去除,所述光致抗蚀剂用于在至少一部分具有铜布线的绝缘层上形成电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少一种。另外,本发明涉及包括使用前述组合物的将前述光致抗蚀剂去除的工序的、半导体元件搭载用封装基板、半导体元件及半导体封装体的制造方法。

背景技术:

2.近年来,随着电子设备的小型化、轻量化及高功能化,印刷电路板急需铜布线的微细化且高密度化。

3.印刷电路板的制造工序中,在一部分具有铜布线的绝缘层上形成被称作晶种层的金属层,并在其表面形成光致抗蚀层,进行曝光显影从而形成抗蚀图案后,对图案开口部实施镀铜,然后,将光致抗蚀剂及晶种层去除,从而形成成为铜布线的连接端子部的电路图案。

4.作为光致抗蚀剂,大多使用干膜抗蚀剂,通常,使用氢氧化钠及氢氧化钾等无机碱的水溶液将光致抗蚀剂从基板上去除。另外,对于半导体元件搭载用封装基板等具有布线形成的难易度更高的微细布线的印刷电路板,使用组合有胺水溶液、例如胺、季铵盐、极性溶剂及铜防腐剂等的光致抗蚀剂剥离液,将光致抗蚀剂从基板上去除(专利文献1等)。

5.以往,印刷电路板(例如半导体元件搭载用封装基板)与半导体元件等部件的电连接中,在铜布线的连接端子部使用焊锡球,但近年来,随着部件的小型化和布线的高密度化,有将焊锡球替换为镀锡或镀锡合金的趋势。

6.现有技术文献

7.专利文献

8.专利文献1:日本特开2015-46575号公报

技术实现要素:

9.发明要解决的问题

10.印刷电路板的制造工序中,镀锡通常在对绝缘层上的图案开口部实施镀铜后在镀铜上直接实施。此时,在实施镀锡后,将光致抗蚀剂去除时,若使用碱的化学溶液,则镀锡容易受到损伤。另外,半导体元件的制造工序中,在半导体晶圆上形成镀铜、进而对其表面实施镀锡后去除光致抗蚀剂时也会产生同样的问题。使用镀锡合金代替镀锡时,或并用镀锡和镀锡合金时,也同样。

11.在这样的情况下,期望提供:除铜外、还可对锡及锡合金进行防腐,并且可以从印刷电路板或半导体晶圆上将光致抗蚀剂去除的组合物及光致抗蚀剂的去除方法。

12.用于解决问题的方案

13.本发明提供:以下示出的光致抗蚀剂去除用组合物、光致抗蚀剂的去除方法,以及

包括使用前述光致抗蚀剂去除用组合物将光致抗蚀剂去除的工序的、半导体元件搭载用封装基板、半导体元件及半导体封装体的制造方法。

14.[1]一种组合物,其用于在下述电路图案形成后将光致抗蚀剂去除,所述光致抗蚀剂用于在至少一部分具有铜布线的绝缘层上形成电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少一种,

[0015]

该组合物包含烷醇胺(a)、氢氧化季铵(b)、糖醇(c)、极性有机溶剂(d)及水(e),

[0016]

以组合物的总量基准计,烷醇胺(a)的含量为2.5~50质量%,氢氧化季铵(b)的含量为0.5~4质量%,糖醇(c)的含量为0.5~20质量%,

[0017]

极性有机溶剂(d)为选自由乙二醇单乙醚、2-丁氧基乙醇、苯氧乙醇、丙二醇单乙醚、二乙二醇单乙醚、二乙二醇单丁醚及二乙二醇单苯醚组成的组中的1种以上,

[0018]

该组合物实质上不包含唑化合物。

[0019]

[2]根据[1]所述的组合物,其中,选自由锡及锡合金组成的组中的至少1种的50℃下的蚀刻速率为0.1μm/分钟以下。

[0020]

[3]根据[1]或[2]所述的组合物,其中,以组合物的总量基准计,水(e)的含量为40质量%以上。

[0021]

[4]根据[1]~[3]中任一项所述的组合物,其中,以组合物的总量基准计,极性有机溶剂(d)的含量为0.5~10质量%。

[0022]

[5]根据[1]~[4]中任一项所述的组合物,其中,极性有机溶剂(d)为选自由苯氧乙醇及二乙二醇单苯醚组成的组中的1种以上。

[0023]

[6]根据[1]~[5]中任一项所述的组合物,其中,糖醇(c)为选自由山梨糖醇、木糖醇及甘露糖醇组成的组中的1种以上。

[0024]

[7]根据[1]~[6]中任一项所述的组合物,其中,氢氧化季铵(b)为选自由四甲基氢氧化铵、四乙基氢氧化铵及三乙基甲基氢氧化铵组成的组中的1种以上。

[0025]

[8]根据[1]~[7]中任一项所述的组合物,其中,烷醇胺(a)为选自由2-氨基乙醇(单乙醇胺)及1-氨基-2-丙醇组成的组中的1种以上。

[0026]

[9]根据[1]~[8]中任一项所述的组合物,其中,前述连接端子部为印刷电路板中的铜布线的连接端子部。

[0027]

[10]根据[1]~[8]中任一项所述的组合物,其中,前述连接端子部为半导体元件搭载用封装基板或半导体元件中的铜布线的连接端子部。

[0028]

[11]一种光致抗蚀剂的去除方法,其包括使光致抗蚀剂与[1]~[10]中任一项所述的组合物接触的工序,所述光致抗蚀剂用于在至少一部分具有铜布线的绝缘层上形成电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少一种。

[0029]

[12]一种半导体元件搭载用封装基板的制造方法,其中,所述半导体元件搭载用封装基板具有铜布线及电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少一种,

[0030]

所述制造方法包括:

[0031]

在至少一部分具有铜布线的绝缘层上形成铜层的工序;

[0032]

在前述铜层的表面形成干膜抗蚀层,对前述干膜抗蚀层进行曝光显影,从而形成

由光致抗蚀剂构成的抗蚀图案的工序;

[0033]

对前述抗蚀图案的开口部实施镀铜,并在前述镀铜上实施选自由镀锡及镀锡合金组成的组中的至少1种,从而形成电路图案的工序,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种;

[0034]

在前述电路图案形成后,使前述光致抗蚀剂与[1]~[10]中任一项所述的组合物接触,从而将前述光致抗蚀剂去除的工序;和

[0035]

在前述光致抗蚀剂去除后,将露出的前述铜层去除的工序。

[0036]

[13]一种半导体元件的制造方法,其中,所述半导体元件具有电路图案,所述电路图案成为铜布线及前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种,

[0037]

所述制造方法包括:

[0038]

在至少一部分具有铜布线的绝缘层上形成铜层的工序;

[0039]

在前述铜层的表面形成干膜抗蚀层,对前述干膜抗蚀层进行曝光显影,从而形成由光致抗蚀剂构成的抗蚀图案的工序;

[0040]

对前述抗蚀图案的开口部实施镀铜,并在前述镀铜上实施选自由镀锡及镀锡合金组成的组中的至少1种,从而形成电路图案的工序,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种;

[0041]

在前述电路图案形成后,使前述光致抗蚀剂与[1]~[10]中任一项所述的组合物接触,从而将前述光致抗蚀剂去除的工序;和

[0042]

在前述光致抗蚀剂去除后,将露出的前述铜层去除的工序。

[0043]

[14]一种半导体封装体的制造方法,其包括:借助选自由锡及锡合金组成的组中的至少一种,对半导体元件搭载用封装基板与半导体元件进行电连接,

[0044]

前述半导体元件搭载用封装基板及前述半导体元件中的至少一者具有电路图案,所述电路图案成为连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种,

[0045]

前述半导体元件搭载用封装基板具有包含铜以及选自由锡及锡合金组成的组中的至少1种的电路图案时,利用[12]所述的制造方法来制造具有包含铜以及选自由锡及锡合金组成的组中的至少1种的电路图案的半导体元件搭载用封装基板,

[0046]

前述半导体元件具有包含铜以及选自由锡及锡合金组成的组中的至少1种的电路图案时,利用[13]所述的制造方法来制造具有包含铜以及选自由锡及锡合金组成的组中的至少1种的电路图案的半导体元件,

[0047]

所述制造方法包括:

[0048]

将前述半导体元件搭载用封装基板及前述半导体元件以各自的连接部相对的方式进行配置,并加热至选自由锡及锡合金组成的组中的至少1种熔融的温度,从而借助选自由锡及锡合金组成的组中的至少1种对半导体元件搭载用封装基板与半导体元件进行电连接。

[0049]

发明的效果

[0050]

根据本发明的优选方式,通过使用本发明的光致抗蚀剂去除用组合物,在印刷电路板或半导体元件中,能够于使用光致抗蚀剂在至少一部分具有铜布线的绝缘层上形成电路图案后,抑制该电路图案的损伤,并将光致抗蚀剂去除,所述电路图案成为前述铜布线的

连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。

附图说明

[0051]

图1为示出本发明的一个实施方式的半导体元件搭载用封装基板的制造方法的工序的一个例子的图。

[0052]

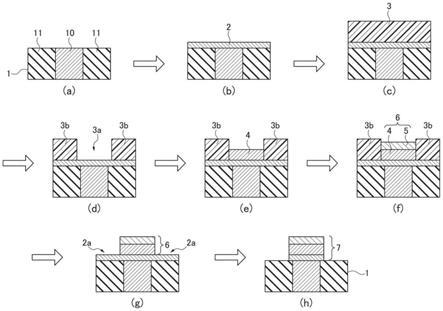

图2为示出本发明的一个实施方式的半导体元件的制造方法的工序的一个例子的图。

具体实施方式

[0053]

以下,对本发明的光致抗蚀剂去除用组合物、光致抗蚀剂的去除方法、以及包括光致抗蚀剂的去除工序的、半导体元件搭载用封装基板、半导体元件及半导体封装体的制造方法进行具体说明。需要说明的是,本发明并不限定于此,在不脱离其主旨的范围内,可以进行各种变形。

[0054]

1.光致抗蚀剂去除用组合物

[0055]

本发明的光致抗蚀剂去除用组合物(以下也称作“本发明的组合物”。)的特征在于,其用于在下述电路图案形成后将光致抗蚀剂去除,所述光致抗蚀剂用于在至少一部分具有铜布线的绝缘层上形成电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种,

[0056]

该组合物包含烷醇胺(a)、氢氧化季铵(b)、糖醇(c)、极性有机溶剂(d)及水(e),

[0057]

以组合物的总量基准计,烷醇胺(a)的含量为2.5~50质量%,氢氧化季铵(b)的含量为0.5~4质量%,糖醇(c)的含量为0.5~20质量%,

[0058]

极性有机溶剂(d)为选自由乙二醇单乙醚、2-丁氧基乙醇、苯氧乙醇、丙二醇单乙醚、二乙二醇单乙醚、二乙二醇单丁醚及二乙二醇单苯醚组成的组中的1种以上,

[0059]

该组合物实质上不包含唑化合物。

[0060]

本发明的组合物可以将光致抗蚀剂去除,所述光致抗蚀剂用于在至少一部分具有铜布线的绝缘层上形成电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。通过本发明的优选方式,可以在使用光致抗蚀剂形成电路图案后,抑制得到的电路图案的损伤,并去除光致抗蚀剂。

[0061]

需要说明的是,本说明书中“锡合金”是指在锡中添加1种以上锡以外的金属元素或非金属元素而成的合金,只要具有金属的性质就没有特别限定。锡合金中的前述金属元素或非金属元素的含量没有特别限定,优选包含50质量%以上的锡,更优选包含80质量%以上,进一步优选包含90质量%以上,特别优选包含98质量%以上。作为前述金属元素或非金属元素,可举出例如银(ag)。

[0062]

以下,对本发明的组合物中包含的各成分进行说明。

[0063]

[烷醇胺(a)]

[0064]

本发明的组合物包含烷醇胺(a)(以下也称作成分(a)。)。作为烷醇胺(a),没有特别限定,可举出单烷醇胺、双烷醇胺、三烷醇胺及它们的烷基化物(n-烷基化物、o-烷基化物)。

[0065]

作为烷醇胺(a),可优选举出例如2-氨基乙醇(单乙醇胺)、n-甲基乙醇胺、n-乙基

乙醇胺、n-丙基乙醇胺、n-丁基乙醇胺、二乙醇胺、1-氨基-2-丙醇(异丙醇胺)、n-甲基异丙醇胺、n-乙基异丙醇胺、n-丙基异丙醇胺、2-氨基丙烷-1-醇、n-甲基-2-氨基-丙烷-1-醇、n-乙基-2-氨基-丙烷-1-醇、1-氨基丙烷-3-醇、n-甲基-1-氨基丙烷-3-醇、n-乙基-1-氨基丙烷-3-醇、1-氨基丁烷-2-醇、n-甲基-1-氨基丁烷-2-醇、n-乙基-1-氨基丁烷-2-醇、2-氨基丁烷-1-醇、n-甲基-2-氨基丁烷-1-醇、n-乙基-2-氨基丁烷-1-醇、3-氨基丁烷-1-醇、n-甲基-3-氨基丁烷-1-醇、n-乙基-3-氨基丁烷-1-醇、1-氨基丁烷-4-醇、n-甲基-1-氨基丁烷-4-醇、n-乙基-1-氨基丁烷-4-醇、1-氨基-2-甲基丙烷-2-醇、2-氨基-2-甲基丙烷-1-醇、1-氨基戊烷-4-醇、2-氨基-4-甲基戊烷-1-醇、2-氨基己烷-1-醇、3-氨基庚烷-4-醇、1-氨基辛烷-2-醇、5-氨基辛烷-4-醇、1-氨基丙烷-2,3-二醇、2-氨基丙烷-1,3-二醇、三(氧甲基)氨基甲烷、1,2-二氨基丙烷-3-醇、1,3-二氨基丙烷-2-醇、2-(2-氨基乙氧基)乙醇等。这些可以单独使用1种,也可组合使用2种以上。

[0066]

这些之中,作为烷醇胺(a),优选选自由2-氨基乙醇(单乙醇胺)及1-氨基-2-丙醇组成的组中的1种以上。

[0067]

以组合物的总量基准计,烷醇胺(a)的含量为2.5~50质量%的范围,优选为3~30质量%,更优选为3.5~15质量%,进一步优选为4~10质量%的范围。需要说明的是,本说明书中,数值范围的上限值及下限值可以适当组合。通过使烷醇胺(a)的含量为上述范围,光致抗蚀剂的去除性变良好,另外,可以抑制电路图案的损伤,所述电路图案成为铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。

[0068]

[氢氧化季铵(b)]

[0069]

本发明的组合物通过包含氢氧化季铵(b)(以下也称作成分(b)。),可以对光致抗蚀剂剥离片进行微细化,从而抑制光致抗蚀剂的剥离残渣的产生。

[0070]

作为氢氧化季铵(b),没有特别限定,可举出例如四甲基氢氧化铵、四乙基氢氧化铵、四丙基氢氧化铵、三乙基甲基氢氧化铵、乙基三甲基氢氧化铵、三甲基(2-羟基乙基)氢氧化铵、三乙基(2-羟基乙基)氢氧化铵。这些可以单独使用1种,也可组合使用2种以上。

[0071]

这些之中,优选选自由四甲基氢氧化铵、四乙基氢氧化铵及三乙基甲基氢氧化铵组成的组中的1种以上。

[0072]

以组合物的总量基准计,氢氧化季铵(b)的含量为0.5~4质量%的范围,优选为0.5~3.5质量%,更优选为1~3.5质量%,进一步优选为1~2质量%的范围。通过使氢氧化季铵(b)的含量为上述范围,光致抗蚀剂的去除性变良好,另外,可以抑制电路图案的损伤,所述电路图案成为铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。

[0073]

[糖醇(c)]

[0074]

本发明的组合物通过包含糖醇(c)(以下也称作成分(c)。),可以不损害光致抗蚀剂的去除性,并抑制电路图案的损伤,所述电路图案成为铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。特别是可以有效地抑制镀锡的损伤。

[0075]

作为糖醇(c),没有特别限定,可优选举出例如苏糖醇、赤藓糖醇、阿东糖醇(adonitol)、阿糖醇、木糖醇、塔罗糖醇、山梨糖醇、甘露糖醇、艾杜糖醇、半乳糖醇及肌醇。这些可以单独使用1种,也可组合使用2种以上。

[0076]

这些之中,优选山梨糖醇、木糖醇及甘露糖醇组成的组中的1种以上,从抑制选自

由锡及锡合金组成的组中的至少1种的损伤的观点来看,更优选选自山梨糖醇或木糖醇中的至少1种。

[0077]

以组合物的总量基准计,糖醇(c)的含量为0.5~20质量%的范围,优选为1~20质量%,更优选为2~15质量%,进一步优选为3~10质量%的范围。通过使糖醇(c)的含量为上述范围,光致抗蚀剂的去除性变良好,另外,可以抑制电路图案的损伤,所述电路图案成为铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。

[0078]

[极性有机溶剂(d)]

[0079]

认为本发明的组合物通过包含极性有机溶剂(d)(以下也称作成分(d)。),可以提高组合物对光致抗蚀剂的浸透性,光致抗蚀剂的去除性变良好,另外,可以抑制光致抗蚀剂的剥离残渣的产生。

[0080]

作为极性有机溶剂(d),使用选自由乙二醇单乙醚、2-丁氧基乙醇、乙二醇单苯醚(苯氧乙醇)、丙二醇单乙醚、二乙二醇单乙醚、二乙二醇单丁醚及二乙二醇单苯醚组成的组中的1种以上。其中,从抑制选自由锡及锡合金组成的组中的至少1种的损伤的观点来看,优选乙二醇单苯醚、二乙二醇单苯醚。这些可以单独使用1种,也可组合使用2种以上。本发明中,通过使用这些特定的极性有机溶剂,可以提高光致抗蚀剂的去除性。上述以外的极性有机溶剂、例如极性有机溶剂的烷基醚部分为甲基醚时,光致抗蚀剂的去除性会降低。

[0081]

以组合物的总量基准计,极性有机溶剂(d)的含量优选为0.5~10质量%的范围,更优选为1~10质量%的范围,进一步优选为1.5~8质量%,更进一步优选为2~6质量%的范围。通过使极性有机溶剂(d)的含量为上述范围,光致抗蚀剂的去除性变得更良好,另外,可以抑制电路图案的损伤,所述电路图案成为铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。

[0082]

[水(e)]

[0083]

本发明的组合物包含水(e)(以下也称作成分(e)。)。作为水(e),并无特别限制,优选通过蒸馏、离子交换处理、过滤器处理、各种吸附处理等将金属离子、有机杂质、微粒颗粒等去除的水,更优选纯水,特别优选超纯水。

[0084]

水(e)的含量为本发明的组合物的余量,以组合物的总量基准计,优选为40质量%以上,更优选大于40质量%,更优选为40~99质量%的范围,进一步优选为50~97质量%,更进一步优选为60~95质量%,特别优选为70~95质量%。水的含量为上述的范围时,烷醇胺(a)及氢氧化季铵(b)相对于光致抗蚀剂的反应性提高,因此可以提高光致抗蚀剂的去除性。水过少时,光致抗蚀剂的去除性有时会降低。

[0085]

[其他成分]

[0086]

在不损害本发明的组合物的效果的范围内,本发明的组合物根据需要也可含有其他成分。

[0087]

作为其他成分,可举出表面活性剂、消泡剂等。

[0088]

唑化合物容易吸附于铜,在化学溶液处理后会残留在铜表面,因此后工序中会成为电连接不良的原因。通过酸清洗、碱清洗,可以将唑化合物从铜表面去除,但同时锡及锡合金也会被腐蚀。因此,为了防止唑化合物向铜的吸附,将本发明的组合物设为实质上不包含唑化合物。此处,实质上不包含唑化合物是指,以组合物的总量基准计,唑化合物的含量小于0.01质量%。唑化合物的含量更优选小于0.001质量%,进一步优选小于0.0001质

量%,特别优选设为不包含。

[0089]

本发明的组合物优选对锡及锡合金的损伤小。例如,通过例如喷雾与本发明的组合物接触时,选自由锡及锡合金组成的组中的至少1种的50℃下的蚀刻速率优选为0.1μm/分钟以下,更优选为0.07μm/分钟以下,进一步优选为0.05μm/分钟以下,特别优选为0.03μm/分钟以下。前述蚀刻速率可以用实施例记载的方法测定。

[0090]

需要说明的是,本发明的组合物优选为溶解液,并设为不含研磨颗粒等固体颗粒。

[0091]

[组合物的制备]

[0092]

本发明的组合物可以通过对成分(a)、成分(b)、成分(c)、成分(d)及成分(e)、进而根据需要的其他成分进行均匀地搅拌来制备。这些成分的搅拌方法没有特别限制,可以采用通常使用的搅拌方法。

[0093]

[组合物的用途]

[0094]

本发明的组合物可以适宜地用于在下述电路图案形成后将光致抗蚀剂去除,所述光致抗蚀剂用于在至少一部分具有铜布线的绝缘层上形成电路图案,所述电路图案成为所述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。

[0095]

此处,“在至少一部分具有铜布线的绝缘层”只要是表面或内部嵌入有铜布线的绝缘层就没有特别限定,可举出例如印刷电路板、半导体元件搭载用封装基板、半导体晶圆的硅绝缘层等。

[0096]

另外,“电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种”是指,作为前述绝缘层具有的铜布线的连接端子部,用于进行与其他构件的电连接。本发明的一个实施方式中,前述连接端子部为印刷电路板中的铜布线的连接端子部。另外,本发明的一个实施方式中,前述连接端子部为半导体元件搭载用封装基板中的铜布线的连接端子部。另外,本发明的一个实施方式中,前述连接端子部为半导体元件中的铜布线的连接端子部。

[0097]

例如,在印刷电路板(例如半导体元件搭载用封装基板)的制造工序中,本发明的组合物可以适宜地用于在下述电路图案形成后将光致抗蚀剂去除,所述光致抗蚀剂用于在至少一部分具有铜布线的绝缘层上形成电路图案,所述电路图案成为所述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。

[0098]

另外,在半导体元件的制造工序中,本发明的组合物可以适宜地用于在下述电路图案形成后将光致抗蚀剂去除,所述光致抗蚀剂用于在至少一部分具有铜布线的绝缘层上形成电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。

[0099]

此处,作为印刷电路板中使用的光致抗蚀剂,可举出例如包含粘结剂聚合物、光聚合性单体、光聚合引发剂及其他添加剂的组合物。

[0100]

作为粘结剂聚合物,可举出例如以甲基丙烯酸及丙烯酸中的至少1种作为必须成分,对甲基丙烯酸酯、丙烯酸酯、苯乙烯等多种乙烯基单体进行共聚而得的聚合物。

[0101]

作为光聚合性单体,可优选举出甲基丙烯酸酯及丙烯酸酯中的至少1种。

[0102]

作为光聚合引发剂,可举出由二苯甲酮、4,4

’‑

二氨基二苯甲酮、4,4

’‑

双(二甲基氨基)二苯甲酮、2-乙基蒽醌、苯偶姻、苯偶姻甲基醚、9-苯基吖啶、苯偶酰二甲基缩酮、苯偶酰二乙基缩酮组成的组中的至少1种。另外,也可使用由六芳基联咪唑和供氢体(2-巯基苯

并噁唑、n-苯甘氨酸)形成的双分子体系。

[0103]

作为其他添加剂,可举出热聚合引发剂、染料等。

[0104]

作为半导体元件中使用的光致抗蚀剂,可优选举出苯酚甲醛树脂(总称为“酚醛树脂”)与作为感光成分的萘醌二叠氮化合物的组合等。

[0105]

本发明的组合物的使用温度并无特别限制,优选10~70℃的温度,更优选为20~65℃,进一步优选为25~60℃。若本发明的组合物的温度为10℃以上,则光致抗蚀剂的去除性变良好,因此可以得到优异的生产效率。另一方面,若本发明的组合物的温度为70℃以下,则可以抑制组合物的组成变化,将光致抗蚀剂的去除条件保持恒定。通过提高组合物的温度,光致抗蚀剂的去除性提高,但考虑到将组合物的组成变化抑制为较小等,确定最适当的处理温度即可。

[0106]

另外,基于本发明的组合物的处理时间没有特别限制,优选为20~600秒,更优选为30~300秒,也可以为30~240秒。处理时间根据作为去除对象物的光致抗蚀剂的表面的状态、组合物的浓度、温度及处理方法等各种条件适当选择即可。

[0107]

使光致抗蚀剂与本发明的组合物接触的方法没有特别限制。可以采用例如利用滴加(单片旋转处理)或喷雾等形式,使本发明的组合物与作为去除对象物的光致抗蚀剂接触的方法、或使作为去除对象物的光致抗蚀剂浸渍于本发明的组合物的方法等方法。本发明中采用任意方法均可。

[0108]

2.光致抗蚀剂的去除方法

[0109]

本发明的光致抗蚀剂的去除方法包括使本发明的组合物与光致抗蚀剂接触的工序,所述光致抗蚀剂用于在至少一部分具有铜布线的绝缘层上形成电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。

[0110]

关于本发明的组合物、使用温度及处理时间,如前述“1.光致抗蚀剂去除用组合物”中所述。关于使本发明的组合物与光致抗蚀剂接触的方法,也如前述“1.光致抗蚀剂去除用组合物”中所述。根据本发明的优选方式,通过使用本发明的组合物,可以抑制对电路图案的损伤,并去除光致抗蚀剂,所述电路图案成为铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。由此,可以在至少一部分具有铜布线的绝缘层上成品率良好地形成电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。

[0111]

3.半导体元件搭载用封装基板的制造方法

[0112]

本发明的半导体元件搭载用封装基板的制造方法的特征在于,所述半导体元件搭载用封装基板具有铜布线和电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种,

[0113]

所述制造方法包括:

[0114]

在至少一部分具有铜布线的绝缘层上形成铜层的工序;

[0115]

在前述铜层的表面形成干膜抗蚀层,对前述干膜抗蚀层进行曝光显影,从而形成由光致抗蚀剂构成的抗蚀图案的工序;

[0116]

对前述抗蚀图案的开口部实施镀铜,并在前述镀铜上实施选自由镀锡及镀锡合金组成的组中的至少1种,从而形成电路图案的工序,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种;

[0117]

在前述电路图案形成后,使前述光致抗蚀剂与本发明的组合物接触,从而将前述光致抗蚀剂去除的工序;和

[0118]

在前述光致抗蚀剂去除后,将露出的前述铜层去除的工序。

[0119]

以下,使用附图,对本发明的半导体元件搭载用封装基板的制造方法进行说明。

[0120]

图1为示出本发明的一个实施方式的半导体元件搭载用封装基板的制造方法的工序的一个例子的图。

[0121]

如图1的(a)所示,首先,准备树脂基板1,其是在层间绝缘树脂11之间嵌入有铜布线10的、在一部分具有铜布线10的绝缘层。

[0122]

接着,如图1的(b)所示,在树脂基板1的表面形成铜层2。对于铜层2,可以对树脂基板1的表面实施化学镀铜(非电解镀铜)而形成,例如可使用改良型半加成法(modified semi-additive process,m-sap)等带载体铜箔的极薄铜箔等形成铜箔层,也可利用溅射对铜进行成膜来形成。利用溅射形成铜层2时,虽未图示,但也可以在形成铜层2前任选地形成钛层、镍-铬合金层等势垒金属层并在其上形成铜层2。本发明的半导体元件搭载用封装基板的制造方法中,优选利用化学镀铜来形成铜层2。

[0123]

然后,如图1的(c)所示,在铜层2的表面形成干膜抗蚀层3,虽未图示,但在其上施加电路掩模图案,进行曝光显影,如图1的(d)所示,形成具有铜层2的表面的一部分露出的开口部3a的、由光致抗蚀剂3b形成的抗蚀图案。

[0124]

接着,如图1的(e)所示,对抗蚀图案的开口部3a实施电镀铜(电解镀铜),形成铜层4。进而,如图1的(f)所示,对铜层4的表面实施镀锡或镀锡合金,形成锡层或锡合金层5,从而形成电路图案6,所述电路图案6成为铜布线10的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。或,也可对铜层4的表面依次实施镀锡及镀锡合金,形成锡层及锡合金层,从而形成成为铜布线10的连接端子部且包含铜、锡及锡合金的电路图案。此时,镀锡及镀锡合金的顺序没有特别限定,适当确定即可。

[0125]

形成电路图案6后,使光致抗蚀剂3b与本发明的组合物接触,如图1的(g)所示,将光致抗蚀剂3b去除。

[0126]

然后,将露出的铜层2的露出部2a去除,如图1的(h)所示,可以在树脂基板1上形成铜布线10的连接端子部7。

[0127]

如上所述,可以制造具有铜布线及电路图案的半导体元件搭载用封装基板,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。连接端子部7可以在将半导体元件等部件搭载于半导体元件搭载用封装基板时使用。

[0128]

可以与本发明的半导体元件搭载用封装基板的制造方法同样地,可制造其他印刷电路板例如通过添加法所制造的被称作高密度安装布线板的母板中的连接端子部。

[0129]

4.半导体元件的制造方法

[0130]

接着,对本发明的半导体元件的制造方法进行说明。

[0131]

本发明的半导体元件的制造方法的特征在于,所述半导体元件具有铜布线和电路图案,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种,

[0132]

所述制造方法包括:

[0133]

在至少一部分具有铜布线的绝缘层上形成铜层的工序;

[0134]

在前述铜层的表面形成干膜抗蚀层,对前述干膜抗蚀层进行曝光显影,从而形成由光致抗蚀剂构成的抗蚀图案的工序;

[0135]

对前述抗蚀图案的开口部实施镀铜,并在前述镀铜上实施选自由镀锡及镀锡合金组成的组中的至少1种,从而形成电路图案的工序,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种;

[0136]

在前述电路图案形成后,使前述光致抗蚀剂与本发明的组合物接触,从而将前述光致抗蚀剂去除的工序;和

[0137]

在前述光致抗蚀剂去除后,将露出的前述铜层去除的工序。

[0138]

图2为示出本发明的一个实施方式的半导体元件的制造方法的工序的一个例子的图。

[0139]

如图2的(a)所示,首先,准备硅基板1’,其是在硅绝缘层12之间嵌入有铜布线10的、在一部分具有铜布线10的绝缘层。

[0140]

接着,如图2的(b)所示,在硅基板1’的表面形成铜层2。对于铜层2,可以对硅基板1’的表面实施化学镀铜而形成,也可利用溅射对铜进行成膜而形成。本发明的半导体元件的制造方法中,优选利用溅射对铜进行成膜来形成铜层2。也可在形成铜层2前任选地形成钛层等势垒金属层8并在其上形成铜层2,虽未图示,但也可在铜层2与势垒金属层8之间进一步形成其他层。钛层等势垒金属层8例如可以利用溅射进行成膜来形成。

[0141]

然后,如图2的(c)所示,在铜层2的表面形成干膜抗蚀层3,虽未图示,但在其上施加电路掩模图案,进行曝光显影,如图2的(d)所示,形成具有铜层2的表面的一部分露出的开口部3a的、由光致抗蚀剂3b形成的抗蚀图案。

[0142]

接着,如图2的(e)所示,对抗蚀图案的开口部3a实施电镀铜,形成铜层4。进而,如图2的(d)所示,对铜层4的表面实施镀锡或镀锡合金,形成锡层或锡合金层5,形成电路图案6,所述电路图案6成为铜布线10的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。或,也可对铜层4的表面依次实施镀锡及镀锡合金,形成锡层及锡合金层,从而形成成为铜布线10的连接端子部且包含铜、锡及锡合金的电路图案。此时,镀锡及镀锡合金的顺序没有特别限定,适当确定即可。

[0143]

形成电路图案6后,使光致抗蚀剂3b与本发明的组合物接触,如图2的(g)所示,将光致抗蚀剂3b去除。

[0144]

然后,将露出的铜层2的露出部2a去除,进而,通过露出部2a的去除将露出的势垒金属层8去除,如图2的(h)所示,可以在硅基板1’上形成铜布线10的连接端子部7’。之后,可以将硅基板1’裁切成规定的大小,并用作半导体元件。

[0145]

如上所述,可以制造具有铜布线及电路图案的半导体元件,所述电路图案成为前述铜布线的连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。连接端子部7’可以在将得到的半导体元件搭载于半导体元件搭载用封装基板等时使用。

[0146]

5.半导体封装体的制造方法

[0147]

接着,对本发明的半导体封装体的制造方法进行说明。

[0148]

本发明的半导体封装体的制造方法的特征在于,其包括:借助选自由锡及锡合金组成的组中的至少1种,对半导体元件搭载用封装基板与半导体元件进行电连接,

[0149]

前述半导体元件搭载用封装基板及前述半导体元件中的至少一者具有电路图案,所述电路图案成为连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种,

[0150]

前述半导体元件搭载用封装基板具有包含铜以及选自由锡及锡合金组成的组中的至少1种的电路图案时,利用前述半导体元件搭载用封装基板的制造方法来制造具有包含铜以及选自由锡及锡合金组成的组中的至少1种的电路图案的半导体元件搭载用封装基板,

[0151]

前述半导体元件具有包含铜以及选自由锡及锡合金组成的组中的至少1种的电路图案时,利用前述半导体元件的制造方法来制造具有包含铜以及选自由锡及锡合金组成的组中的至少1种的电路图案的半导体元件,

[0152]

所述制造方法包括:

[0153]

将前述半导体元件搭载用封装基板及前述半导体元件以各自的连接部相对的方式进行配置,并加热至选自由锡及锡合金组成的组中的至少1种熔融的温度,从而借助选自由锡及锡合金组成的组中的至少1种对半导体元件搭载用封装基板与半导体元件进行电连接。

[0154]

本发明的半导体封装体的制造方法中,半导体元件搭载用封装基板及半导体元件中的任一者、或两者具有电路图案,所述电路图案成为连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。另外,将前述半导体元件搭载用封装基板及前述半导体元件以各自的连接部相对的方式进行配置,并加热至电路图案所具有的选自由锡及锡合金组成的组中的至少1种熔融的温度,由此可以借助选自由锡及锡合金组成的组中的至少1种对半导体元件搭载用封装基板及半导体元件进行电连接。

[0155]

此时的加热温度只要为选自由锡及锡合金组成的组中的至少1种熔融的温度,就没有特别限定,从使半导体元件搭载用封装基板及半导体元件的电连接良好、并防止它们的损伤的观点来看,通常为180~280℃,优选为180~260℃,更优选为180~240℃。

[0156]

如上所述,本发明的半导体封装体的制造方法中,欲连接的半导体元件搭载用封装基板及半导体元件中的至少一者具有电路图案,所述电路图案成为连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种,由此可以借助选自由锡及锡合金组成的组中的至少1种对半导体元件搭载用封装基板及半导体元件进行电连接。通过本发明的优选方式,与以往的将焊锡球、焊锡膏直接涂布于连接构件并进行半导体元件搭载用封装基板与半导体元件的电连接的情况相比,可以容易控制电连接、还可应对电子设备的布线的高密度化及小型化的需求。

[0157]

需要说明的是,本发明的一个实施方式中,也可在半导体元件搭载用封装基板及半导体元件中的至少一者所具有的电路图案的锡层或锡合金层上进一步配置焊锡球、焊锡膏等接合剂来强化电连接,所述电路图案成为连接端子部且包含铜以及选自由锡及锡合金组成的组中的至少1种。通过借助连接端子部配置焊锡球、焊锡膏等接合剂,与将这些接合剂直接涂布于连接构件的情况相比,变得容易控制电连接。

[0158]

对半导体元件搭载用封装基板与半导体元件进行电连接后,为了确保电连接强度及机械连接强度,优选注入密封树脂,并对半导体元件搭载用封装基板与半导体元件的间隙进行密封。

[0159]

实施例

[0160]

以下,利用实施例对本发明进行具体说明,只要能发挥本发明的效果,则可以对实施方式进行适当变更。

[0161]

[实施例1~28]

[0162]

在容量1l的玻璃烧杯中,按表1记载的组成,投入成分(a)、成分(b)、成分(c)、成分(d)、成分(e)及其他任选成分,搅拌而成为均匀的状态,从而制备水性组合物。

[0163]

[比较例1~16]

[0164]

设为表2记载的组成,除此以外,与上述实施例同样地制备水性组合物。

[0165]

[光致抗蚀剂去除性评价用样品的制作]

[0166]

在绝缘层(ajinomoto fine-techno co.,inc.制“abf-gx-92”)上实施化学镀铜(上村工业株式会社制“thru-cup peaver.2”),制膜成铜薄膜(厚度:0.8μm)。使该铜薄膜的表面附着干膜抗蚀剂(日立化成株式会社制“rd-1225”、厚度:25μm),对其上施加电路掩模图案并进行曝光显影。对干膜抗蚀剂进行曝光显影,对形成的电路图案开口部实施电镀铜(厚度:20μm),得到光致抗蚀剂去除性评价用样品。

[0167]

[锡防腐性评价用样品的制作]

[0168]

对覆铜箔层叠板(三菱瓦斯化学株式会社制“ccl-hl832hs 12/12hs-l”)的表面实施石原化学株式会社制的镀锡(厚度:10μm),得到锡防腐性评价用样品。

[0169]

《评价方法》

[0170]

对具有表1或2的组成的水性组合物进行喷射压0.15mpa、50℃、3分钟喷雾,使其分别与光致抗蚀剂去除性评价用样品及锡防腐性评价用样品接触。

[0171]

对于光致抗蚀剂去除性能,使用光学显微镜“olympus mx-61l物镜50倍”,确认光致抗蚀剂去除性评价用样品的光致抗蚀剂去除的程度。

[0172]

《光致抗蚀剂去除性评价基准》

[0173]

a:光致抗蚀剂被全部去除。

[0174]

b:光致抗蚀剂部分地残留。

[0175]

c:光致抗蚀剂完全不能被去除。

[0176]

《锡防腐性评价》

[0177]

对于锡防腐性评价,测定处理前后的样品质量,根据其质量差、锡的密度(7.37g/cm3)及样品尺寸(处理面积[m2],需要说明的是、样品的背面被遮蔽胶带保护,因此处理面积为样品表面的面积。)计算被蚀刻的厚度,通过下式求出每1分钟的蚀刻量(锡的蚀刻速率)。

[0178]

锡的蚀刻速率[μm/分钟]=(处理前样品质量[g]-处理后样品质量[g])/{(处理面积[m2]

×

7.37[g/cm3](锡的密度)

×

处理时间[分钟])}

[0179]

蚀刻速率为0.1μm/分钟以下则合格,为0.05μm/分钟以下则特别优异。

[0180]

将结果分别示于表1及2。

[0181]

[表1]

[0182]

[0183][0184]

[表2]

[0185][0186]

如表1所示,对于实施例1~28的水性组合物,光致抗蚀剂均被全部去除,且锡防腐性也良好。

[0187]

另一方面,如表2所示,对于比较例1~16的水性组合物,均为光致抗蚀剂的去除性

不充分,或锡防腐性不充分。

[0188]

附图标记说明

[0189]

1 树脂基板

[0190]1’ꢀ

硅基板

[0191]

2 铜层

[0192]

2a 露出部

[0193]

3 干膜抗蚀剂

[0194]

3a 开口部

[0195]

3b 光致抗蚀剂

[0196]

4 铜层

[0197]

5 锡层或锡合金层

[0198]

6 电路图案

[0199]

7 连接端子部

[0200]7’ꢀ

连接端子部

[0201]

8 势垒金属层

[0202]

10 铜布线

[0203]

11 层间绝缘树脂

[0204]

12 硅绝缘层

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。