1.本发明属于半导体封装技术领域,具体涉及一种扇出式堆叠芯片的封装方法及封装结构。

背景技术:

2.电子产品的体积越来越小,功能越来越强。随之需要半导体封装更加轻薄,互连密度更高。传统的封装无法满足未来的需求。图1为典型的传统多层芯片封装结构,芯片1,2通过贴片膜3,4 垂直堆叠在基板6上,芯片1,2通过金线5与基板6形成连接。芯片1,2和金线5通过塑封料7保护。整个封装通过焊球8与外界进行连接。在目前的封装中,由于金线成型的高度限制,以及塑封料到金线保护距离限制,塑封料到芯片2表面的高度受到严格限制,无法持续降低。同时基板工艺由于材料限制以及基板强度的限制,超薄基板的生产难度极大,这些都限制了传统封装在超薄多层封装中的应用。而且不管是传统打线连接,还是倒转焊连接,焊盘间距都在30um以上,持续缩小的难度极大。

3.针对上述问题,有必要提出一种设计合理且可以有效解决上述问题的一种扇出式堆叠芯片的封装方法及封装结构。

技术实现要素:

4.本发明旨在至少解决现有技术中存在的技术问题之一,提供一种扇出式堆叠芯片封装结构及封装方法。

5.本发明的一方面提供一种扇出式堆叠芯片的封装方法,所述方法包括:

6.将第一芯片固定在假片上的槽体内;

7.将第二芯片与所述第一芯片进行混合键合,所述第二芯片在所述假片上的正投影与所述假片重合;

8.将所述假片与所述第二芯片分离,并在所述第二芯片朝向所述第一芯片的表面、以及在所述第一芯片的外侧形成多个导电凸柱;

9.形成第一塑封层,所述第一塑封层包裹所述第一芯片和所述多个导电凸柱;

10.形成第二塑封层,所述第二塑封层包裹所述第一芯片、所述第二芯片和所述第一塑封层;

11.在所述第一芯片和所述第一塑封层背离所述第二芯片的表面形成重布线层,所述重布线层通过所述多个导电凸柱与所述第二芯片电连接。

12.可选的,所述第一芯片朝向所述第二芯片的表面设置有第一钝化层和第一金属焊盘,所述第二芯片朝向所述第一芯片的表面设置有第二钝化层和第二金属焊盘;

13.所述将第二芯片与所述第一芯片进行混合键合,包括:

14.将所述第一芯片的第一钝化层与所述第二芯片的所述第二钝化层键合;以及,

15.将所述第一芯片的第一金属焊盘与所述第二芯片的所述第二金属焊盘键合。

16.可选的,所述将第二芯片与所述第一芯片进行混合键合之前,所述方法还包括:

17.在所述假片和所述第一芯片的第一表面形成粘合胶,并使得部分所述粘合胶填充至所述假片和所述第一芯片之间的缝隙中;

18.将所述第一芯片的第一表面的粘合胶完全去除,同时保留部分所述假片表面的粘合胶,以露出所述第一芯片的所述第一钝化层和所述第一金属焊盘。

19.可选的,所述形成所述第二塑封层,包括:

20.将所述第一塑封层背离所述第二芯片的一侧进行减薄,露出所述多个导电凸柱,以使所述第一塑封层与所述第一芯片的第二表面齐平;

21.将减薄后的所述第一塑封层和所述第一芯片的第二表面固定到临时载板上,之后形成所述第二塑封层。

22.可选的,所述在所述第一芯片和所述第一塑封层背离所述第二芯片的表面形成重布线层,包括:

23.将所述第一芯片和所述第一塑封层与所述临时载板分离;

24.在所述第一芯片和所述第一塑封层背离所述第二芯片的表面形成介电层;

25.图形化所述介电层,在所述图形化后的介电层上形成重布线层;

26.图形化所述重布线层,在所述图形化后的重布线层上形成焊球。

27.可选的,所述第一芯片的第一表面凸出于所述假片的表面。

28.本发明的另一方面提供一种扇出式堆叠芯片的封装结构,所述封装结构包括第一芯片、第二芯片、多个导电凸柱、混合键合结构、第一塑封层、第二塑封层和重布线层;

29.所述第二芯片通过所述混合键和结构堆叠设置在所述第一芯片上;

30.所述多个导电凸柱设置在所述第二芯片朝向所述第一芯片的一侧,并且设置在所述第一芯片的外侧;

31.所述第一塑封层包裹所述第一芯片和所述多个导电凸柱;

32.所述第二塑封层包裹所述第一芯片、所述第二芯片和所述第一塑封层;

33.所述重布线层设置在所述第一芯片和所述第一塑封层背离所述第二芯片的表面,所述重布线层通过所述多个导电凸柱与所述第二芯片电连接。

34.可选的,所述混合键合结构包括设置在所述第一芯片朝向所述第二芯片的表面的第一钝化层和第一金属焊盘、以及设置在所述第二芯片朝向所述第一芯片的表面的第二钝化层和第二金属焊盘;

35.所述第一钝化层和所述第二钝化层键合连接,所述第一金属焊盘和所述第二金属焊盘键合连接。

36.可选的,所述封装结构还包括介电层和焊球;

37.所述介电层设置在所述第二塑封层和所述第一芯片背离所述第二芯片的表面,所述介电层上设置有所述重布线层,所述焊球设置在所述重布线层上。

38.可选的,所述导电凸柱与所述第二金属焊盘相对应。

39.本发明提供的扇出式堆叠芯片的封装方法及封装结构,该封装方法将第一芯片固定在假片上的槽体内,通过假片将两种不同尺寸的第一芯片和第二芯片调整为同一尺寸,然后将第一芯片和第二芯片进行晶圆级混合键合,通过晶圆扩展技术进行晶圆级混合键合,实现高密度互连的同时提高生产效率。

40.本发明中将假片与第二芯片分离,并在第二芯片上朝向第一芯片的表面,以及在

第一芯片的外侧形成多个导电凸柱,通过多个导电凸柱将第二芯片的部分信号引出,在第一芯片和第一塑封层背离第二芯片的表面形成重布线层,通过导电凸柱和扇出式重布线层替代传统的基板互连,降低了封装尺寸。

41.本发明中由于第一芯片与第二芯片之间采用直接晶圆键合,键合后厚度与芯片本体厚度相同,最大程度的降低了封装高度,实现了超薄的多层高密度堆叠封装。

附图说明

42.图1为现有技术典型的传统多层芯片封装结构的结构示意图;

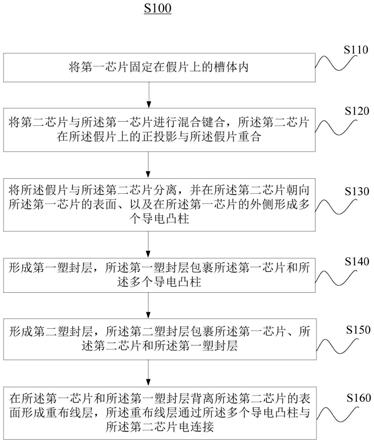

43.图2本发明另一实施例的一种扇出式堆叠芯片的封装方法流程示意图;

44.图3~图16为本发明另一实施例的一种扇出式堆叠芯片的封装工艺示意图。

具体实施方式

45.为使本领域技术人员更好地理解本发明的技术方案,下面结合附图和具体实施方式对本发明作进一步详细描述。

46.如图2所示,本发明的一方面提供一种扇出式堆叠芯片的封装方法s100,该封装方法s100包括:

47.s110、将第一芯片固定在假片上的槽体内。

48.具体地,如图1所示,将第一芯片110的背面通过贴片胶121 固定在假片120上的槽体内,其中,第一芯片110的第一表面凸出于假片120的表面,也就是说,第一芯片110的正面凸出于假片120的表面。

49.如图3所示,第一芯片110的第一表面设置有第一钝化层111 和第一金属焊盘112,也就是说,第一芯片110的正面设置有第一钝化层111和第一金属焊盘112,在本实施例中,第一钝化层111 的材料为二氧化硅钝化层,也可以时其他可以起到钝化作用的材料,本实施例不做具体限定。在本实施例中,第一金属焊盘112 的材料为金属铜,也可以是其他的金属材料,本实施例不做具体限定。

50.s120、将第二芯片与所述第一芯片进行混合键合,所述第二芯片在所述假片上的正投影与所述假片重合。

51.示例性的,所述将第二芯片与所述第一芯片进行混合键合之前,所述方法还包括:

52.首先,在所述假片和所述第一芯片的第一表面形成粘合胶,并使得部分所述粘合胶填充至所述假片和所述第一芯片之间的缝隙中。

53.具体地,具体地,如图4所示,在假片120和第一芯片110 的第一表面形成粘合胶122,并使得部分粘合胶121填充至假片 120和第一芯片110之间的缝隙中,将第一芯片110完全固定在假片120的槽体内。因为第一芯片110的第一表面凸出于假片120 的表面,所以假片120上的粘合胶122要比第一芯片110的第一表面上的粘合胶122要厚,这样在第一芯片110与第二芯片140 进行混合键合时,第二芯片140可以粘贴在假片120上。

54.其次,将所述第一芯片的第一表面的粘合胶完全去除,同时保留部分所述假片表面的粘合胶,以露出所述第一芯片的所述第一钝化层和所述第一金属焊盘。

55.具体地,如图5所示,可以对第一芯片110的第一表面的粘合胶121进行表面研磨抛光和化学清洁处理,将第一芯片110第一表面的粘合胶122完全去除,也就是说,将第一芯片

110正面的粘合胶122去除,同时保留部分假片120表面的粘合胶122,露出第一芯片110的第一钝化层111和第一金属焊盘112。部分假片 120表面的粘合胶122,可以将假片120固定在第二芯片140上。

56.具体地,如图6所示,第二芯片140朝向第一芯片110的表面设置有第二钝化层141和第二金属焊盘142。在本实施例中,第二钝化层141的材料均可以为二氧化硅层或者氮化硅层,也可以时其他可以起到钝化作用的材料。第二金属焊盘142的材料为金属铜,也可以是其他的金属材料,本实施例不做具体限定。

57.示例性的,所述将第二芯片与所述第一芯片进行混合键合,包括:

58.首先,将所述第一芯片的第一钝化层与所述第二芯片的所述第二钝化层键合。

59.具体地,如图6所示,将第一芯片110的第一钝化层111与第二芯片140的第二钝化层141键合。先将第一钝化层111与第二钝化层141对准,然后通过高温压合作用,将第一钝化层111 与第二钝化层141进行连接。

60.其次,将所述第一芯片的第一金属焊盘与所述第二芯片的所述第二金属焊盘键合。

61.具体地,如图6所示,将第一芯片110的第一金属焊盘112 与第二芯片140的第二金属焊盘142键合。现将第一金属焊盘112 与第二金属焊盘142对准,然后通过高温压合作用,利用铜受热膨胀实现连接。

62.如图6所示,第二芯片140在假片120上的正投影与假片120 重合,也就是说,第二芯片140的尺寸与假片120的尺寸一致。采用假片将两种不同尺寸的第一芯片110和第二芯片140调整为同一尺寸,通过晶圆扩展技术进行晶圆级混合键合,实现高密度互连的同时提高生产效率。

63.s130、将所述假片与所述第二芯片分离,并在所述第二芯片朝向所述第一芯片的表面、以及所述第一芯片的外侧形成多个导电凸柱。

64.具体地,如图7所示,将键合后的第一芯片110和假片120 的背面进行减薄。其中,减薄后第一芯片110和假片120的残留厚度为40um以下。通过对第一芯片110和假片120的背面进行减薄,进一步降低了封装高度。

65.如图8所示,对第一芯片110和假片120进行激光或者紫外光照射,光波根据粘合胶122的特性决定,在光波能量作用下,粘合胶122失去粘性,这样,如图9所示,假片120从第二芯片 140上脱离,也就是第二芯片140与假片120分离,留下混合键和的第一芯片110和第二芯片140。需要说明的是,将第二芯片140 与假片120分离也可以采用其他的方法,本实施例不做具体限定。

66.如图10所示,第二芯片140与假片120分离后,在第二芯片 140朝向第一芯片110的表面、以及第一芯片110的外侧通过电镀等工艺形成多个导电凸柱150。也就是说,多个导电凸柱150位于第二芯片140与假片120分离之前的假片120处的位置。多个导电凸柱150电镀在第二金属焊盘142上,与第二金属焊盘142相对应,可根据实际需要进行导电凸柱150的电镀。采用多个导电凸柱150可以将第二芯片140的部分信号引出,相对于基板互连,采用导电凸柱150实现垂直电气互连,降低了封装高度。

67.在本实施例中,导电凸柱150为金属铜柱,也可以根据需要选择其他的金属材料。

68.s140、形成第一塑封层,所述第一塑封层包裹所述第一芯片和所述多个导电凸柱。

69.具体地,如图11所示,形成多个导电凸柱150后,在第一芯片110背离第二芯片140的一侧形成第一塑封层160,第一塑封层 160包裹多个导电凸柱150和第一芯片110,第一塑封层160对多个导电凸柱150和第一芯片起到保护作用。塑封方法可以是膜层真空压合或传统塑封工艺,本实施例不做具体限定

70.s150、形成第二塑封层,所述第二塑封层包裹所述第一芯片、所述第二芯片和所述第一塑封层。

71.首先,将所述第一塑封层背离所述第二芯片的一侧进行减薄,露出所述导电凸柱,以使所述第一塑封层与所述第一芯片的第二表面齐平。

72.具体地,如图12所示,通过研磨抛光和化学清洁处理对第一塑封层160背离第二芯片140的一侧进行减薄,露出导电凸柱150,以使第一塑封层160与减薄后第一芯片110的第二表面齐平。也就是说说,以使第一塑封层160与减薄后第一芯片110的背面齐平

73.其次,将减薄后的所述第一塑封层和所述第一芯片的第二表面固定到临时载板上,之后形成所述第二塑封层。

74.具体地,以上的封装步骤是对多个第一芯片110、多个假片 120和多个第二芯片140同时进行封装,将第一塑封层160背离第二芯片140的一侧完成减薄后,需要将完成减薄后的多个芯片组合体进行切割,形成如图12所示的多个独立芯片组合体。然后进行以下封装步骤,如图13所示,将减薄后的第一塑封层160和第一芯片110背离第二芯片140的表面通过粘结胶固定到临时载板 161上,也就是以第一芯片110的背面为接触面,按照最终封装尺寸,逐个贴合到带有临时键合胶的临时载板161上,之后进行塑封,形成如图14所示的第二塑封层170,第二塑封层170包裹第一芯片110、第二芯片140和第一塑封层160。塑封方法可以是膜层真空压合或传统塑封工艺,本实施例不做具体限定。

75.s160、在所述第一芯片和所述第一塑封层背离所述第二芯片的表面形成重布线层,所述重布线层通过所述多个导电凸柱与所述第二芯片电连接。

76.示例性的,所述在所述第一芯片和所述第一塑封层背离所述第二芯片的表面形成重布线层,包括:

77.首先,将所述第一芯片和所述第一塑封层与所述临时载板分离。

78.具体地,如图15所示,将第一芯片110和第一塑封层160与临时载板161分离,也就是去除临时载板161。分离方法可以采用热分离,激光分离,紫外光分离,机械分离等方法,此等方法均为目前常用的临时键合分离方法,对于分离方法本实施例不做具体限定,可根据实际需要进行选择。

79.其次,在所述第一芯片和所述第一塑封层背离所述第二芯片的表面形成介电层。

80.具体地,如图16所示,在第一芯片110和第一塑封层160背离第二芯片150的表面涂敷介电层180。介电层180的材料可以为聚酰亚胺(pi)、聚苯并噁唑(pbo)等,涂敷方法通常为晶圆旋涂,本实施例不做具体限定。

81.再次,图形化所述介电层,在所述图形化后的介电层上形成重布线层。

82.具体地,如图16所示,通过光刻工艺将介电层180图形化,在图形化后的介电层180上形成重布线层190。重布线层190通过多个导电凸柱150与第二芯片140电连接。形成重布线层190方法可以为电镀、溅射、热蒸发、等离子体增强化学气相沉积、低压化学气相沉积、大气压化学气相沉积或电子回旋谐振化学气相沉积等工艺,本实施例不做具体限定。重布

线层190的材料可以为金属钛和金属铜,对于重布线层190的材料本实施例不做限定。

83.最后,图形化所述重布线层,在所述图形化后的重布线层上形成焊球。

84.具体地,通过光刻工艺将重布线层190图形化,在图形化后的重布线层190进行植球形成多个焊球(图中未示出),通过焊球与外界电连接。

85.本发明提供的扇出式堆叠芯片的封装方法及封装结构,该封装方法将第一芯片固定在假片上的槽体内,通过假片将两种不同尺寸的第一芯片和第二芯片调整为同一尺寸,然后将第一芯片和第二芯片进行晶圆级混合键合,通过晶圆扩展技术进行晶圆级混合键合,实现高密度互连的同时提高生产效率。

86.本发明中将假片与第二芯片分离,并在第二芯片上朝向第一芯片的表面,以及在第一芯片的外侧形成多个导电凸柱,通过多个导电凸柱将第二芯片的部分信号引出,在第一芯片和第一塑封层背离第二芯片的表面形成重布线层,通过导电凸柱和扇出式重布线层替代传统的基板互连,降低了封装尺寸。

87.本发明中由于第一芯片与第二芯片之间采用直接晶圆键合,键合后厚度与芯片本体厚度相同,最大程度的降低了封装高度,实现了超薄的多层高密度堆叠封装。

88.如图16所示,本发明的另一方面提供一种扇出式堆叠芯片封装结构,封装结构包括第一芯片110、第二芯片140、多个导电凸柱150、混合键合结构(图中未标出)、第一塑封层160、第二塑封层170和重布线层190。

89.第二芯片140通过所述混合键和结构堆叠设置在第一芯片 110上。

90.多个导电凸柱150设置在第二芯片140朝向第一芯片110的一侧,并且设置在第一芯片110的外侧。

91.第一塑封层160包裹第一芯片110和多个导电凸柱150,第一塑封层160对第一芯片110和多个导电凸柱150起到保护作用。

92.第二塑封层170包裹第一芯片110、第二芯片140和第一塑封层160,第二塑封层170对第一芯片110、第二芯片140和第一塑封层160起到保护作用。

93.重布线层190设置在第一芯片110和第一塑封层160背离第二芯片140的表面,重布线层190通过多个导电凸柱150与第二芯片140电连接。

94.示例性的,如图16所示,混合键合结构包括设置在第一芯片 110朝向第二芯片140的表面的第一钝化层111和第一金属焊盘 112、以及设置在第二芯片140朝向第一芯片110的表面的第二钝化层141和第二金属焊盘142,第一钝化层111和第二钝化层141 键合连接,第一金属焊盘112和第二金属焊盘142键合连接。

95.示例性的,如图16所示,封装结构还包括介电层180和焊球(图中未示出),介电层180设置在第二塑封层170和第一芯片 110背离第二芯片140的表面,介电层180上设置有重布线层190,焊球设置在重布线层190上。封装结构通过焊球与外界电连接。

96.示例性的,如图16所示,导电凸柱150与第二金属焊盘142 相对应,也就是说,多个导电凸柱150电镀在第二金属焊盘142 上,与第二金属焊盘142相对应,可根据实际需要进行导电凸柱 150的电镀。采用多个导电凸柱150可以将第二芯片140的部分信号引出,相对于基板互连,采用导电凸柱150实现垂直电气互连,降低了封装高度。

97.需要说明的是,在本实施例中,第一钝化层111与第二钝化层141均可以为二氧化硅层或者氮化硅层,也可以是其他可以起到钝化作用的材料。第一金属焊盘112和第二金属

焊盘142的材料为金属铜,也可以是其他的金属材料,本实施例不做具体限定。介电层180的材料可以为聚酰亚胺(pi)、聚苯并噁唑(pbo)等,涂敷方法通常为晶圆旋涂,本实施例不做具体限定。重布线层190 的材料可以是金属钛和铜,也可以是其他的金属材料,本实施例不做具体限定。

98.本发明的扇出式堆叠芯片的封装结构,第二芯片通过混合键合结构与第一芯片混合键合连接,实现了高密度互连的同时提高生产效率,最大程度的降低了封装高度。多个导电凸柱设置在第二芯片朝向第一芯片的一侧,并且设置在第一芯片的外侧,通过导电凸柱可以将第二芯片的部分信号引出,重布线层设置在第一芯片和第一塑封层背离第二芯片的表面,相对于基板互连,采用导电凸柱和重布线层进行垂直电气互连,降低了封装高度,实现了高密度和超薄化的封装。

99.可以理解的是,以上实施方式仅仅是为了说明本发明的原理而采用的示例性实施方式,然而本发明并不局限于此。对于本领域内的普通技术人员而言,在不脱离本发明的精神和实质的情况下,可以做出各种变型和改进,这些变型和改进也视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。