1.本发明涉及继电器驱动技术领域,尤其涉及一种继电器的驱动电路。

背景技术:

2.电动汽车通常采用高压动力电池提供动力,为满足整车的需求,需要电池系统提供不同供电回路,例如整车行驶时,放电回路需要接通;电池充电时,充电回路需要接通;电池加热时,加热回路需要接通。为确保这些不同回路的控制,需要根据要求,控制回路中的高压继电器的通断。

3.对于运行中的电动汽车,如果高压继电器与高压动力电池之间产生非预期的脱开,将导致车辆动力丢失,出现安全问题。由于高压继电器是由继电器驱动电路进行驱动的,为了解决以上问题,一般会在继电器驱动电路的处理器与高压继电器之间增加一个延时模块,延时模块的功能是在处理器出现复位时,能够保持高压继电器闭合一段时间,保证车辆动力不丢失,当处理器完成复位后,接管高压继电器的控制。

4.然而,如果延时模块异常使能,将导致高压继电器非预期结合,车辆非预期上高压电,导致发生车辆加速或人员触电的安全事故,系统的安全性和鲁棒性较差。并且在处理器复位过程中,由于延时模块的延时保持作用,车辆运行时高压继电器上仍有大电流,此时高压继电器的供电出现短时间跌落,将导致高压继电器断开后立即结合,烧坏高压继电器;同时,若延时模块的供电出现跌落,导致延时模块不能正常工作,高压继电器可能会因为延时模块误动作。

技术实现要素:

5.本发明的目的在于提供一种继电器的驱动电路,能够在需要的时候关闭继电器的驱动电路的延时保持功能。

6.为了达到上述目的,本发明提供了一种继电器的驱动电路,包括:

7.处理模块,用于输出使能信号;

8.延时模块,连接所述处理模块的输出端,用于对所述使能信号进行延时,以输出延时信号;

9.触发模块,用于根据预定的触发条件输出有效的触发信号;以及,

10.使能模块,连接所述处理模块、所述延时模块及所述触发模块的输出端,用于在所述使能信号或所述延时信号有效时控制所述继电器闭合,且在所述处理模块复位过程中当所述触发信号有效时控制所述继电器断开。

11.可选的,还包括:

12.供电模块,至少用于向所述延时模块提供供电电压;

13.继电器驱动模块,连接所述使能模块的输出端,用于根据所述使能模块的输出信号输出驱动信号控制所述继电器的通断;以及,

14.所述触发条件包括所述供电电压低于第一参考电压和/或所述驱动信号的电压低

于第二参考电压。

15.可选的,所述触发模块包括:

16.第一比较器,所述第一比较器的第一输入端连接所述供电模块的输出端,所述第一比较器的第二输入端接入所述第一参考电压,所述第一比较器用于比较所述供电电压和所述第一参考电压,并在所述供电电压低于所述第一参考电压时输出有效的第一比较信号;

17.第二比较器,所述第二比较器的第一输入端连接所述继电器驱动模块的输出端,所述第二比较器的第二输入端接入所述第二参考电压,所述第一比较器用于比较所述驱动信号的电压和所述第二参考电压,并在所述驱动信号的电压低于所述第二参考电压时输出有效的第二比较信号;以及,

18.第一或门,连接所述第一比较器和所述第二比较器的输出端,用于对所述第一比较信号和所述第二比较信号进行或运算,并在所述第一比较信号或所述第二比较信号有效时输出有效的所述触发信号。

19.可选的,所述触发模块包括:

20.第一比较器,所述第一比较器的第一输入端连接所述供电模块的输出端,所述第一比较器的第二输入端接入所述第一参考电压,所述第一比较器用于比较所述供电电压和所述第一参考电压,并在所述供电电压低于所述第一参考电压时输出有效的所述触发信号;或者,

21.第二比较器,所述第二比较器的第一输入端连接所述继电器驱动模块的输出端,所述第二比较器的第二输入端接入所述第二参考电压,所述第一比较器用于比较所述驱动信号的电压和所述第二参考电压,并在所述驱动信号的电压低于所述第二参考电压时输出有效的所述触发信号。

22.可选的,所述使能模块包括:

23.锁存器,所述锁存器的输入端连接所述处理模块的输出端,所述锁存器的复位端接入所述触发信号,当所述触发信号无效时,所述锁存器处于锁存状态,当所述触发信号有效时,所述锁存器处于复位状态;

24.与门,连接所述延时模块及所述锁存器的输出端,用于对所述延时信号及所述锁存器的输出信号进行与运算;以及,

25.第二或门,连接所述处理模块及所述与门的输出端,用于对所述使能信号和所述与门的输出信号进行或运算,并输出逻辑信号控制所述继电器的通断。

26.可选的,所述继电器为双边控制的继电器,所述延时模块、所述继电器驱动模块、所述与门及所述第二或门均具有两组,分别用于控制所述继电器的高边和低边;以及,

27.所述触发条件包括所述供电电压低于第一参考电压和/或高边的所述驱动信号的电压低于第二参考电压。

28.可选的,所述锁存器的输出端上设置有第一采样点,所述处理模块实时采集所述第一采样点上的信号;和/或,所述与门的输出端上设置有第二采样点,所述处理模块实时采集所述第二采样点上的信号。

29.可选的,所述继电器为单边控制的继电器。

30.可选的,所述继电器驱动电路用于驱动至少两个所述继电器,所述继电器的工作

电压相同或不相同。

31.可选的,所述继电器共用所述触发模块、所述延时模块、所述锁存器和所述与门;

32.所述触发条件包括所述供电电压低于第一参考电压和/或任一所述继电器对应的所述驱动信号的电压低于对应的所述第二参考电压。

33.在本发明提供的继电器的驱动电路中,包括处理模块、延时模块、触发模块及使能模块,所述处理模块用于输出使能信号,所述延时模块用于对所述使能信号进行延时,以输出延时信号,所述触发模块用于在所述处理模块复位过程中根据预定的触发条件输出有效的触发信号,所述使能模块用于在所述使能信号或所述延时信号有效时控制所述继电器闭合,并在所述触发信号的有效时控制所述继电器断开。本发明通过所述触发模块预设了触发条件,当满足所述触发条件时,所述触发模块可以输出有效的所述触发信号,所述使能模块可以在所述处理模块复位过程中根据所述触发信号控制所述继电器断开,相当于可以在所述处理模块的复位过程中根据需要关闭所述延时模块的延时保持功能,从而保护所述继电器的驱动电路。

34.此外,所述触发条件包括所述供电电压低于第一参考电压和/或所述驱动信号的电压低于第二参考电压,从而防止所述处理模块在复位过程中,所述继电器的供电出现短时间跌落时,所述继电器断开后立即结合,导致烧坏所述继电器的问题;同时还可以防止所述延时模块的供电出现跌落时,所述延时模块不能正常工作,导致所述继电器因为所述延时模块误动作的问题。

附图说明

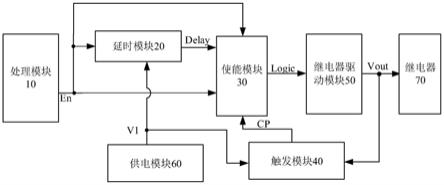

35.图1为本发明实施例一提供的继电器的驱动电路的电路图;

36.图2为本发明实施例一提供的使能模块及触发模块的具体电路图;

37.图3为本发明实施例二提供的继电器的驱动电路的局部示意图;

38.图4为本发明实施例三提供的继电器的驱动电路的局部示意图;

39.图5为本发明实施例四提供的继电器的驱动电路的局部示意图;

40.其中,附图标记为:

41.10-处理模块;20、21、22-延时模块;30-使能模块;31-锁存器;32、321、322-与门;33、331、332、333、334、335、336-第二或门;40-触发模块;41-第一比较器;42-第二比较器;43-第一或门;50、51、52、53、54、55、56-继电器驱动模块;60-供电模块;70、71、72、73、74-继电器;

42.en-使能信号;delay、delay1、delay2-延时信号;v1-供电电压;cp-触发信号;logic、logic1、logic2、logic3、logic4、logic5、logic6-逻辑信号;vout、vout1、vout2、vout3、vout4、vout5、vout6-驱动信号;vref1-第一参考电压;vref2-第二参考电压;k1-第一采样点;k2、k21、k22-第二采样点;d-锁存器的输入端;e-锁存器的复位端;y-锁存器的输出端。

具体实施方式

43.下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下列描述,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准

的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

44.实施例一

45.图1为本实施例提供的继电器的驱动电路的电路图。如图1所示,所述继电器的驱动电路包括处理模块10、延时模块20、使能模块30、触发模块40、继电器驱动模块50及供电模块60。本实施例中,所述继电器的驱动电路用于驱动单个的继电器70,且所述继电器70为单边控制的继电器。

46.本实施例中,所述继电器的驱动电路驱动的所述继电器70为电池管理系统(battery management system,bms)中的高压继电器,但不应以此为限,所述继电器的驱动电路可以用于驱动任何可能的继电器。

47.具体而言,所述处理模块10用于输出使能信号en,以控制所述继电器70高压上电或低压上电。本实施例中,为了便于描述,将所述处理模块10输出的使能信号en简化为一个信号,但应理解,所述处理模块10输出的所述使能信号en可以是一个或多个,此处不再过多赘述。

48.所述延时模块20连接所述处理模块10的输出端,用于接入所述使能信号en,并对所述使能信号en进行延时,从而输出延时信号delay。所述延时模块20例如可以是采用电容的充放电效应进行延时的电路,当所述使能信号en无效时,所述延时模块20中的电容开始充电,电容两端的电压开始上升,直至充满电后,所述延时模块20输出的所述延时信号delay无效。当所述使能信号en有效时;所述延时模块20中的电容开始放电,电容两端的电压开始下降,直至放电完成后,所述延时模块20输出的所述延时信号delay有效。可见,所述延时模块20可以实现延时输出的功能,延时时间即为电容充放电的时间。

49.所述供电模块60用于为所述延时模块20提供供电电压v1,以保证所述延时模块20正常工作。作为可选实施例,所述供电模块60不仅可以为所述延时模块20供电,还可以为所述处理模块10提供供电电压,且为所述延时模块20提供的供电电压v1可以与为所述处理模块10提供的供电电压相同或不相同,当然,所述供电模块60还可以为所述继电器的驱动电路中的其他模块供电,此处不再一一举例说明。

50.所述触发模块40中预设有触发条件,所述触发模块40可以根据预定的所述触发条件输出有效的触发信号cp。所述触发条件可以根据实际需要进行设计,具体将在下文中描述。

51.所述使能模块30连接所述处理模块10、所述延时模块20及所述触发模块40的输出端,用于接入所述使能信号en、所述延时信号delay及所述触发信号cp,并根据所述使能信号en、所述延时信号delay及所述触发信号cp输出可用于控制所述继电器70通断的逻辑信号logic。具体而言,所述使能模块30可以在所述使能信号en或所述延时信号delay有效时输出有效的逻辑信号logic控制所述继电器70闭合,在所述使能信号en或所述延时信号delay均无效时输出无效的逻辑信号logic控制所述继电器70断开,以及在所述处理模块10复位过程中当所述触发信号cp有效时输出无效的逻辑信号logic控制所述继电器70断开。

52.所述继电器驱动模块50连接所述使能模块30的输出端,用于接入所述逻辑信号logic,并根据所述逻辑信号logic输出驱动信号vout,所述继电器70连接所述继电器驱动模块50的输出端,用于接入所述驱动信号vout,并在所述驱动信号vout的控制下闭合或断开。具体而言,所述驱动信号vout为模拟信号,当所述逻辑信号logic有效时,所述继电器驱

动模块50会输出电压大于或等于第二参考电压vref2的所述驱动信号vout,从而控制所述继电器70闭合,当所述逻辑信号logic无效时,所述继电器驱动模块50会输出电压小于所述第二参考电压vref2的所述驱动信号vout,控制所述继电器70断开。

53.所述第二参考电压vref2可以根据所述继电器70的工作电压进行设计,例如,所述继电器70的工作电压可以为5v,所述第二参考电压vref2可以设定为3.5v,当所述驱动信号vout的电压大于或等于3.5v时,即可控制所述继电器70闭合,当所述驱动信号vout的电压小于3.5v时,所述继电器70断开。

54.所述处理模块10在复位过程中,由于所述延时模块20的延时保持作用,车辆运行时所述继电器70上仍有大电流,此时所述继电器70的供电出现短时间跌落,将导致所述继电器70断开后立即结合,烧坏所述继电器70;同时,若所述延时模块20的供电出现跌落,导致所述延时模块20不能正常工作,所述继电器70可能会因为所述延时模块20误动作。基于此,所述触发条件可以根据所述延时模块20的供电跌落和所述继电器70的供电跌落进行设计,本实施例中,所述触发条件包括所述供电电压v1低于第一参考电压vref1和/或所述驱动信号vout的电压低于所述第二参考电压vref2,也即当所述供电电压v1低于所述第一参考电压vref1和/或所述驱动信号vout的电压低于所述第二参考电压vref2时,所述触发模块40会输出有效的触发信号cp,从而控制所述继电器70断开,防止所述处理模块10在复位过程中,所述继电器70的供电出现短时间跌落时,所述继电器70断开后立即结合,导致烧坏所述继电器70的问题;同时还可以防止所述延时模块20的供电出现跌落时,所述延时模块20不能正常工作,导致所述继电器70因为所述延时模块20误动作的问题。

55.当然,所述触发条件不限于此,还可以是其他可能的触发条件,此处不再一一解释说明,本实施例通过所述触发模块40预设了触发条件,当满足所述触发条件时,所述触发模块40可以输出有效的所述触发信号cp,所述使能模块30可以在所述处理模块10复位过程中根据所述触发信号cp控制所述继电器70断开,相当于可以在所述处理模块10的复位过程中根据需要关闭所述延时模块20的延时保持功能,从而保护所述继电器的驱动电路。

56.图2为本实施例提供的使能模块30及触发模块40的具体电路图。如图2所示,所述触发模块40包括第一比较器41、第二比较器42和第一或门43。其中,所述第一比较器41的第一输入端连接所述供电模块60的输出端,用于接入所述供电电压v1;所述第一比较器41的第二输入端接入所述第一参考电压vref1,所述第一比较器41用于比较所述供电电压v1和所述第一参考电压vref1,并在所述供电电压v1低于所述第一参考电压vref1时输出有效的第一比较信号。所述第二比较器42的第一输入端连接所述继电器驱动模块50的输出端,用于接入所述驱动信号vout,所述第二比较器42的第二输入端接入所述第二参考电压vref2,所述第一比较器41用于比较所述驱动信号vout的电压和所述第二参考电压vref2,并在所述驱动信号vout的电压低于所述第二参考电压vref2时输出有效的第二比较信号。所述第一或门43连接所述第一比较器41和所述第二比较器42的输出端,用于接入所述第一比较信号和所述第二比较信号,用于对所述第一比较信号和所述第二比较信号进行或运算,并在所述第一比较信号或所述第二比较信号有效时输出有效的所述触发信号cp。如此一来,当所述供电电压v1低于所述第一参考电压vref1和/或所述驱动信号vout的电压低于所述第二参考电压vref2时,所述触发模块40均可以输出有效的所述触发信号cp,其它情况下,所述触发模块40输出无效的所述触发信号cp。

57.作为可选实施例,所述触发模块40可以仅包括第一比较器41,所述第一比较器41的第一输入端连接所述供电模块60的输出端,用于接入所述供电电压v1;所述第一比较器41的第二输入端接入所述第一参考电压vref1,所述第一比较器41用于比较所述供电电压v1和所述第一参考电压vref1,并在所述供电电压v1低于所述第一参考电压vref1时输出有效的所述触发信号cp。如此一来,当所述供电电压v1低于所述第一参考电压vref1时,所述触发模块40可以输出有效的所述触发信号cp,其它情况下,所述触发模块40输出无效的所述触发信号cp。

58.作为可选实施例,所述触发模块40可以仅包括第二比较器42,所述第二比较器42的第一输入端连接所述继电器驱动模块50的输出端,用于接入所述驱动信号vout,所述第二比较器42的第二输入端接入所述第二参考电压vref2,所述第一比较器41用于比较所述驱动信号vout的电压和所述第二参考电压vref2,并在所述驱动信号vout的电压低于所述第二参考电压vref2时输出有效的所述触发信号cp。如此一来,当所述驱动信号vout的电压低于所述第二参考电压vref2时,所述触发模块40可以输出有效的所述触发信号cp,其它情况下,所述触发模块40输出无效的所述触发信号cp。

59.进一步地,请继续参阅图2,本实施例中,所述使能模块30包括锁存器31、与门32及第二或门33。所述锁存器31的输入端d连接所述处理模块10的输出端,用于接入所述使能信号en,所述锁存器31的复位端e接入所述触发信号cp,当所述触发信号cp无效时,所述锁存器31处于锁存状态,当所述触发信号cp有效时,所述锁存器31处于复位状态。所述与门32连接所述延时模块20及所述锁存器31的输出端y,用于接入所述延时信号delay与所述锁存器31的输出信号并对所述延时信号delay和所述锁存器31的输出信号进行与运算。所述第二或门33连接所述处理模块10及所述与门32的输出端,用于接入所述使能信号en及所述与门32的输出信号并对所述使能信号en及所述与门32的输出信号进行或运算,并输出所述逻辑信号logic。

60.本实施例中,所述使能信号en、延时信号delay、所述逻辑信号logic及所述触发信号cp均为数字信号。接下来将以数字信号为“1”时有效,为“0”时无效详细说明所述触发模块40及所述使能模块30的时序。

61.当所述处理模块10上电时,所述使能信号en为“1”,不论所述第二或门33的另一个输入是“1”还是“0”,所述第二或门33输出的所述逻辑信号logic为“1”,所述继电器驱动模块50输出所述驱动信号vout控制所述继电器70闭合。所述处理模块10正常下电/复位时,所述使能信号en为“0”,由于所述延时模块20的延时作用,所述延时信号delay在延时时间过后变为“0”,此时所述锁存器31处于锁存状态(锁存上电时的使能信号en),所述锁存器31的输出为“1”,所述与门32的输出在延时时间过后变为“0”,所述第二或门33输出的所述逻辑信号logic在延时时间过后变为“0”,所述继电器驱动模块50输出所述驱动信号vout控制所述继电器70断开。所述处理模块10在复位过程中,在所述延时时间内,若所述供电电压v1低于第一参考电压vref1和/或所述驱动信号vout的电压低于第二参考电压vref2,所述第一或门43输出有效的触发信号cp,所述锁存器31处于复位状态,所述锁存器31的输出立即变为“0”,所述与门32的输出立即变为“0”,所述第二或门33输出的所述逻辑信号logic立即变为“0”,所述继电器驱动模块50立即输出所述驱动信号vout控制所述继电器70断开。可见,所述使能模块30可以在所述使能信号en或所述延时信号delay有效时控制所述继电器70闭

合,且在所述处理模块10复位过程中当所述触发信号cp有效时控制所述继电器70断开。

62.进一步地,所述锁存器31的输出端y上设置有第一采样点k1,所述处理模块10实时采集所述第一采样点k1上的信号;和/或,所述与门32的输出端上设置有第二采样点k2,所述处理模块10实时采集所述第二采样点k2上的信号。由于所述第一采样点k1上的信号可以表征所述锁存器31的输出信号,所述第二采样点k2上的信号可以表征所述延时信号delay及所述锁存器31的输出信号,所述处理模块10通过实时采集所述第一采样点k1及所述第二采样点k2上的信号可以对所述锁存器31或所述延时模块20进行故障诊断。

63.实施例二

64.图3为本实施例提供的继电器的驱动电路的局部示意图。如图3所示,与实施例一的区别在于,本实施例中,所述继电器70为双边控制的继电器,所述延时模块、所述继电器驱动模块、所述与门及所述第二或门均具有两组,分别用于控制所述继电器70的高边和低边。

65.具体而言,所述延时模块包括延时模块21和延时模块22,所述继电器驱动模块包括继电器驱动模块51和继电器驱动模块52,所述与门包括与门321及与门322,所述第二或门包括第二或门331及第二或门332。所述延时模块21及所述延时模块22均连接所述处理模块10的输出端,用于接入所述使能信号en,所述延时模块21及所述延时模块22分别根据所述使能信号en输出所述延时信号delay1和所述延时信号delay2。所述与门321连接所述延时模块21及所述锁存器31的输出端y,用于接入所述延时信号delay1和所述锁存器31的输出信号并对所述延时信号delay1与所述锁存器31的输出信号进行与运算;所述与门322连接所述延时模块22及所述锁存器31的输出端y,用于接入所述延时信号delay2和所述锁存器31的输出信号并对所述延时信号delay2与所述锁存器31的输出信号进行与运算。所述第二或门331连接所述处理模块10及所述与门321的输出端,用于接入所述使能信号en及所述与门321的输出信号并对所述使能信号en及所述与门321的输出信号进行或运算,并输出所述逻辑信号logic1;所述第二或门332连接所述处理模块10及所述与门322的输出端,用于接入所述使能信号en及所述与门322的输出信号并对所述使能信号en及所述与门322的输出信号进行或运算,并输出所述逻辑信号logic2。所述继电器驱动模块51和所述继电器驱动模块52分别连接所述第二或门331及所述第二或门332的输出端,并分别根据所述逻辑信号logic1和所述逻辑信号logic2输出所述驱动信号vout1和所述驱动信号vout2。所述驱动信号vout1和所述驱动信号vout2共同驱动所述继电器70的高边和低边。

66.本实施例中,所述继电器70的高边和低边共用所述触发模块40及所述锁存器31,所述触发条件包括所述供电电压v1低于所述第一参考电压vref1和/或所述继电器70的高边的所述驱动信号vout1的电压低于所述第二参考电压vref2。因此,所述第二比较器42的第一输入端可以连接所述继电器驱动模块51的输出端,用于接入所述驱动信号vout1,所述第二比较器42用于比较所述驱动信号vout1的电压和所述第二参考电压vref2,并在所述驱动信号vout1的电压低于所述第二参考电压vref2时输出有效的第二比较信号。

67.进一步地,本实施例中,所述与门321及所述与门322的输出端分别设置了第二采样点k21和第二采样点k22,由于所述第一采样点k1上的信号可以表征所述锁存器31的输出信号,所述第二采样点k21上的信号又可以表征所述延时信号delay1及所述锁存器31的输出信号,所述第二采样点k22上的信号又可以表征所述延时信号delay2及所述锁存器31的

输出信号,所述处理模块10通过实时采集所述第一采样点k1、所述第二采样点k21及所述第二采样点k22上的信号可以对所述锁存器31、所述延时模块21及所述延时模块22进行故障诊断。

68.实施例三

69.图4为本实施例提供的继电器的驱动电路的局部示意图。如图4所示,与实施例一的区别在于,本实施例中,所述继电器驱动电路用于驱动两个单边控制的继电器,两个所述继电器的工作电压可以相同或不相同。

70.具体而言,所述继电器包括继电器71和继电器72,所述继电器71和所述继电器72共用所述触发模块40、所述延时模块20、所述锁存器31及所述与门32。所述第二或门和所述继电器驱动模块均具有两组,所述第二或门包括第二或门333及第二或门334,所述继电器驱动模块包括继电器驱动模块53和继电器驱动模块54。

71.所述第二或门333连接所述处理模块10及所述与门32的输出端,用于接入所述使能信号en及所述与门32的输出信号并对所述使能信号en及所述与门32的输出信号进行或运算,并输出所述逻辑信号logic3;所述第二或门334连接所述处理模块10及所述与门32的输出端,用于接入所述使能信号en及所述与门32的输出信号并对所述使能信号en及所述与门32的输出信号进行或运算,并输出所述逻辑信号logic4。所述继电器驱动模块53和所述继电器驱动模块54分别连接所述第二或门333及所述第二或门334的输出端,并分别根据所述逻辑信号logic3和所述逻辑信号logic4输出驱动信号vout3和驱动信号vout4。所述驱动信号vout3和所述驱动信号vout4分别驱动所述继电器71和所述继电器72。

72.本实施例中,所述继电器71和所述继电器72的工作电压相同,所述触发条件包括所述供电电压v1低于所述第一参考电压vref1和/或所述驱动信号vout3的电压低于所述第二参考电压vref2;或者,所述触发条件包括所述供电电压v1低于所述第一参考电压vref1和/或所述驱动信号vout4的电压低于所述第二参考电压vref2。因此,所述第二比较器42的第一输入端可以连接所述继电器驱动模块53的输出端,用于接入所述驱动信号vout3,所述第二比较器42用于比较所述驱动信号vout3的电压和所述第二参考电压vref2,并在所述驱动信号vout3的电压低于所述第二参考电压vref2时输出有效的第二比较信号;或者,所述第二比较器42的第一输入端可以连接所述继电器驱动模块54的输出端,用于接入所述驱动信号vout4,所述第二比较器42用于比较所述驱动信号vout4的电压和所述第二参考电压vref2,并在所述驱动信号vout4的电压低于所述第二参考电压vref2时输出有效的第二比较信号。

73.当然,若所述继电器71和所述继电器72的工作电压不相同,则所述第二比较器42的第二输入端输入的所述第二参考电压vref2的数值应该与所述继电器71和所述继电器72对应。例如,所述继电器71的工作电压为5v,当所述驱动信号vout3的电压大于3.5v时即可控制所述继电器71闭合,所述继电器72的工作电压为10v,当所述驱动信号vout4的电压大于8v时即可控制所述继电器72闭合,当所述第二比较器42的第一输入端连接所述继电器驱动模块53的输出端时,所述第二比较器42的第二输入端输入的所述第二参考电压vref2的数值应该为3.5v;当所述第二比较器42的第一输入端连接所述继电器驱动模块54的输出端时,所述第二比较器42的第二输入端输入的所述第二参考电压vref2的数值应该为8v。

74.应理解,所述继电器的驱动电路不限于驱动两个单边控制的继电器,还可以驱动

三个或三个以上的单边控制的继电器。

75.实施例四

76.图5为本实施例提供的继电器的驱动电路的局部示意图。如图5所示,与实施例二的区别在于,本实施例中,所述继电器驱动电路用于驱动两个双边控制的继电器,两个所述继电器的工作电压可以相同或不相同。

77.具体而言,所述继电器包括继电器73和继电器74,所述继电器73和所述继电器74共用所述触发模块40、所述延时模块21、所述延时模块22、所述锁存器31、所述与门321及所述与门322。所述第二或门及所述继电器驱动模块均具有四组,所述继电器73和所述继电器74分别对应两组所述第二或门及所述继电器驱动模块,每两组所述第二或门及所述继电器驱动模块分别用于控制所述继电器73和所述继电器74的高边和低边。

78.具体而言,所述第二或门包括第二或门331、第二或门332、第二或门335、第二或门336,所述继电器驱动模块包括继电器驱动模块51、继电器驱动模块52、继电器驱动模块55、继电器驱动模块56。所述第二或门331及所述第二或门335均连接所述处理模块10及所述与门321的输出端,用于接入所述使能信号en及所述与门321的输出信号并对所述使能信号en及所述与门321的输出信号进行或运算,并分别输出所述逻辑信号logic1及逻辑信号logic5;所述第二或门332和所述第二或门336连接所述处理模块10及所述与门322的输出端,用于接入所述使能信号en及所述与门322的输出信号并对所述使能信号en及所述与门322的输出信号进行或运算,并分别输出所述逻辑信号logic2及逻辑信号logic6。所述继电器驱动模块51和所述继电器驱动模块52分别连接所述第二或门331及所述第二或门332的输出端,并分别根据所述逻辑信号logic1和所述逻辑信号logic2输出所述驱动信号vout1和所述驱动信号vout2,所述驱动信号vout1和所述驱动信号vout2共同驱动所述继电器73的高边和低边。所述继电器驱动模块55和所述继电器驱动模块56分别连接所述第二或门335及所述第二或门336的输出端,并分别根据所述逻辑信号logic5和所述逻辑信号logic6输出所述驱动信号vout5和所述驱动信号vout6,所述驱动信号vout5和所述驱动信号vout6共同驱动所述继电器74的高边和低边。

79.本实施例中,所述继电器73和所述继电器74的工作电压相同,所述触发条件包括所述供电电压v1低于所述第一参考电压vref1和/或所述继电器73的高边的驱动信号vout1的电压低于所述第二参考电压vref2;或者,所述触发条件包括所述供电电压v1低于所述第一参考电压vref1和/或所述继电器74的高边的驱动信号vout5的电压低于所述第二参考电压vref2。因此,所述第二比较器42的第一输入端可以连接所述继电器驱动模块51的输出端,用于接入所述驱动信号vout1,所述第二比较器42用于比较所述驱动信号vout1的电压和所述第二参考电压vref2,并在所述驱动信号vout1的电压低于所述第二参考电压vref2时输出有效的第二比较信号;或者,所述第二比较器42的第一输入端可以连接所述继电器驱动模块55的输出端,用于接入所述驱动信号vout5,所述第二比较器42用于比较所述驱动信号vout5的电压和所述第二参考电压vref2,并在所述驱动信号vout5的电压低于所述第二参考电压vref2时输出有效的第二比较信号。

80.当然,若所述继电器73和所述继电器74的工作电压不相同,则所述第二比较器42的第二输入端输入的所述第二参考电压vref2的数值应该与所述继电器73和所述继电器74对应。例如,所述继电器73的工作电压为5v,当所述驱动信号vout1的电压大于3.5v时即可

控制所述继电器73闭合,所述继电器74的工作电压为10v,当所述驱动信号vout5的电压大于8v时即可控制所述继电器72闭合,当所述第二比较器42的第一输入端连接所述继电器驱动模块51的输出端时,所述第二比较器42的第二输入端输入的所述第二参考电压vref2的数值应该为3.5v;当所述第二比较器42的第一输入端连接所述继电器驱动模块55的输出端时,所述第二比较器42的第二输入端输入的所述第二参考电压vref2的数值应该为8v。

81.应理解,所述继电器的驱动电路不限于驱动两个双边控制的继电器,还可以驱动三个或三个以上的双边控制的继电器。

82.综上,在本发明实施例提供的继电器的驱动电路中,包括处理模块、延时模块、触发模块及使能模块,所述处理模块用于输出使能信号,所述延时模块用于对所述使能信号进行延时,以输出延时信号,所述触发模块用于在所述处理模块复位过程中根据预定的触发条件输出有效的触发信号,所述使能模块用于在所述使能信号或所述延时信号有效时控制所述继电器闭合,并在所述触发信号的有效时控制所述继电器断开。本发明通过所述触发模块预设了触发条件,当满足所述触发条件时,所述触发模块可以输出有效的所述触发信号,所述使能模块可以在所述处理模块复位过程中根据所述触发信号控制所述继电器断开,相当于可以在所述处理模块的复位过程中根据需要关闭所述延时模块的延时保持功能,从而保护所述继电器的驱动电路。

83.此外,所述触发条件包括所述供电电压低于第一参考电压和/或所述驱动信号的电压低于第二参考电压,从而防止所述继电器的供电出现短时间跌落时,所述继电器断开后立即结合,导致烧坏所述继电器的问题;同时还可以防止所述延时模块的供电出现跌落时,所述延时模块不能正常工作,导致所述继电器因为所述延时模块误动作的问题。

84.需要说明的是,本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的系统而言,由于与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

85.还需要说明的是,虽然本发明已以较佳实施例披露如上,然而上述实施例并非用以限定本发明。对于任何熟悉本领域的技术人员而言,在不脱离本发明技术方案范围情况下,都可利用上述揭示的技术内容对本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围。

86.还应当理解的是,除非特别说明或者指出,否则说明书中的术语“第一”、“第二”、“第三”等描述仅仅用于区分说明书中的各个组件、元素、步骤等,而不是用于表示各个组件、元素、步骤之间的逻辑关系或者顺序关系等。

87.此外还应该认识到,此处描述的术语仅仅用来描述特定实施例,而不是用来限制本发明的范围。必须注意的是,此处的以及所附权利要求中使用的单数形式“一个”和“一种”包括复数基准,除非上下文明确表示相反意思。例如,对“一个步骤”或“一个装置”的引述意味着对一个或多个步骤或装置的引述,并且可能包括次级步骤以及次级装置。应该以最广义的含义来理解使用的所有连词。以及,词语“或”应该被理解为具有逻辑“或”的定义,而不是逻辑“异或”的定义,除非上下文明确表示相反意思。此外,本发明实施例中的方法

和/或设备的实现可包括手动、自动或组合地执行所选任务。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。