一种用于差分逐次逼近寄存器型adc的参考电压缓冲器

技术领域

1.本发明涉及集成电路设计技术领域,具体涉及一种为高精度全差分逐次逼近寄存器型adc提供系列参考电压的缓冲器。

背景技术:

2.模数转换器(analog-to-digital converter,adc)是现实世界与数字世界之间的桥梁,逐次逼近寄存器(successive approximation register,sar)型结构非常适合于实现中等速度和中高精度的adc,具有结构紧凑、低功耗、能够从制造工艺进步中受益等优点。

3.图1至4以3位为例图示了差分sar型adc的量化过程,其中,图1为采样相位状态,图2为第一次比较得b2,图3为第二次比较得b1,图4为第三次比较得b0。这种电容阵列数字模拟转换器(digital-to-analog converter,dac)架构一般在学术上称之为基于共模电压的电容阵列dac,具有开关功耗低、匹配性好、比较器失调小等优点。如何以最少的功耗设计缓冲器以提供这种差分结构所需要的三个参考电压(正参考电压vrp、负参考电压vrn、共模电压vcm)是设计差分sar型adc时的一个关键问题,因此,参考电压缓冲器的功耗往往占据sar型adc整体功耗的大部分。在单电源系统中,一般选取参考地为负参考电压vrn,那么,参考电压缓冲器需要提供正参考电压vrp和共模电压vcm这两个电压。

4.电压串联负反馈是实现参考电压缓冲器的基本途径。首先,环路增益必须足够高以克服误差放大器增益受工艺、电压、温度变化而变化导致的静态输出电压误差;其次,在最恶劣的场景下,缓冲器必须能够在规定的时间内完成输出电压的建立,一般情况下我们以动态误差小于最小分辨位(least significant bit,lsb)电压的一半作为建立完成的标准。此外,sar型adc所需要的两个参考电压中,正参考电压vrp须具有较高的绝对精度以使量化范围与设计目标一致,而共模电压vcm对绝对精度没有要求,因为其作用仅在于定义电容阵列dac的输出电压的共模电平。

技术实现要素:

5.本发明目的是提供一种用于差分逐次逼近寄存器型adc的参考电压缓冲器,具有瞬变特性好、低功耗和易于修调的特点。

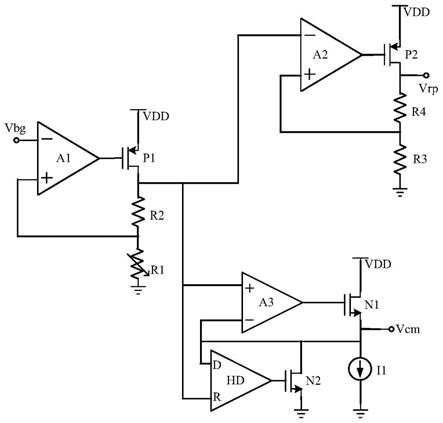

6.本发明的技术方案是:一种用于差分逐次逼近寄存器型adc的参考电压缓冲器,包括可修调的第一电压缓冲器、产生正参考电压vrp的第二电压缓冲器以及产生共模电压vcm的第三电压缓冲器,其中,带隙基准电压通过所述第一电压缓冲器输出到第二电压缓冲器的输入端和第三电压缓冲器的输入端;

7.所述第一电压缓冲器包括第一误差放大器a1、第一pmos管p1、第一电阻r1以及第二电阻r2;

8.所述第二电压缓冲器包括第二误差放大器a2、第二pmos管p2、第三电阻r3以及第四电阻r4;

9.所述第三电压缓冲器包括第三误差放大器a3、第一nmos管n1、第二nmos管n2、第一

电流源i1以及高电压检测器hd。

10.上述技术方案中,所述第一电压缓冲器的偏置电流小于第三电压缓冲器的偏置电流小于第二电压缓冲器的偏置电流。

11.上述技术方案中,所述第一误差放大器a1的反相输入端电性连接到带隙基准电压,同相输入端分别电性连接到第一电阻r1的一端和第二电阻r2的一端,输出端电性连接到pmos管p1的栅极;

12.所述pmos管p1的源极电性连接到电源vdd,漏极分别电性连接到第二电阻r2的另一端、第二误差放大器a2的反相输入端、第三误差放大器a3的同相输入端和高电压检测器hd的参考输入端;

13.所述第一电阻r1的另一端接地;

14.所述第二误差放大器a2的同相输入端分别电性连接到第三电阻r3的一端和第四电阻r4的一端,输出端电性连接到pmos管p2的栅极;

15.所述pmos管p2的源极电性连接到电源vdd,漏极分别电性连接到第四电阻r4的另一端和输出电源端vrp;

16.所述第三电阻r3的另一端接地;

17.所述第三误差放大器a3的反相输入端分别电性连接到高电压检测器hd的检测输入端和nmos管n2的漏极并经偏置电流源ib 1接地,输出端电性连接到nmos管n1的栅极;

18.所述高电压检测器hd的检测输出端电性连接到nmos管n2的栅极,所述nmos管n2的源极接地;

19.所述nmos管n1的漏极电性连接到电源vdd,源极电性连接到输出电源端vcm并经偏置电流源ib 1接地。

20.上述技术方案中,所述第一电阻r1为可通过控制字修调其阻值的可修调电阻。

21.上述技术方案中,所述高电压检测器hd包括pmos管p3、pmos管p4、nmos管n3、nmos管n4和偏置电流源i2,其中,

22.所述pmos管p3的源极经偏置电流源i2电性连接到电源电压vdd,栅极电性连接到高电压检测器hd的参考输入端,漏极分别电性连接到nmos管n3的漏极和高电压检测器hd的输出端;

23.所述pmos管p4的源极经偏置电流源i2电性连接到电源电压vdd,栅极电性连接到高电压检测器hd的检测输入端,漏极分别电性连接到nmos管n4的漏极、栅极和nmos管n3的栅极;

24.所述nmos管n3的源极接地;

25.所述nmos管n4的源极接地。

26.上述技术方案中,所述第三nmos管n3与第四nmos管n4的尺寸相互匹配,且所述第三nmos管n3与第四nmos管n4的尺寸比为3:1。

27.上述技术方案中,所述高电压检测器hd被配置为在检测到检测输入端的电压高于参考输入端的电压超过预设定比例时输出高电平。

28.上述技术方案中,所述预设定比例为20%。

29.本发明的优点是:

30.1.本发明中的第一电阻r1和第二电阻r2的阻值非常大,容易通过数字修调第一电

阻r1的阻值以获得绝对精度较高的输出电压vrp;

31.2.本发明的第一和第二电压缓冲器均采用传统的两级放大结构和密勒频率补偿方法,具有瞬态特性好的优点;

32.3.本发明的高电压检测器hd可大大降低第三电压缓冲器中分配给第一电流源i1的偏置电流,因为高电压检测器hd在共模电压vcm连接到较高电平时会临时打开nmos管n2以加快下拉的速度。

附图说明

33.下面结合附图及实施例对本发明作进一步描述:

34.图1至4为背景技术中的差分sar型adc的量化过程原理图。

35.图5为本发明的参考电压缓冲器的电路结构图。

36.图6为本发明的高电压检测器hd的电路结构图。

37.图7为在55nm cmos工艺(3.3v电源电压)下本发明的稳定性仿真结果。

38.图8为在55nm cmos工艺(3.3v电源电压)下本发明的参考电压缓冲器分别从2.5v和0v缓冲至1.25v下的瞬态响应仿真结果。

39.图9为在55nm cmos工艺(3.3v电源电压)下本发明的参考电压缓冲器分别从2.5v和0v缓冲至1.25v下的瞬态响应仿真结果局部放大图。

40.图10为本发明与传统参考电压缓冲器的输出电压瞬态仿真结果对比图。

具体实施方式

41.实施例:

42.参见图5所示,本实施例提供一种用于差分逐次逼近寄存器型adc的参考电压缓冲器,包括可修调的第一电压缓冲器、产生正参考电压vrp的第二电压缓冲器以及产生共模电压vcm的第三电压缓冲器,其中,带隙基准电压通过所述第一电压缓冲器输出到第二电压缓冲器的输入端和第三电压缓冲器的输入端;

43.所述第一电压缓冲器包括第一误差放大器a1、第一pmos管p1、第一电阻r1以及第二电阻r2;

44.所述第二电压缓冲器包括第二误差放大器a2、第二pmos管p2、第三电阻r3以及第四电阻r4;

45.所述第三电压缓冲器包括第三误差放大器a3、第一nmos管n1、第二nmos管n2、第一电流源i1以及高电压检测器hd。

46.在一种实施方式中,所述第一电压缓冲器的偏置电流小于第三电压缓冲器的偏置电流小于第二电压缓冲器的偏置电流。

47.在一种实施方式中,所述第一误差放大器a1的反相输入端电性连接到带隙基准电压,同相输入端分别电性连接到第一电阻r1的一端和第二电阻r2的一端,输出端电性连接到pmos管p1的栅极;

48.所述pmos管p1的源极电性连接到电源vdd,漏极分别电性连接到第二电阻r2的另一端、第二误差放大器a2的反相输入端、第三误差放大器a3的同相输入端和高电压检测器hd的参考输入端;

49.所述第一电阻r1的另一端接地;

50.所述第二误差放大器a2的同相输入端分别电性连接到第三电阻r3的一端和第四电阻r4的一端,输出端电性连接到pmos管p2的栅极;

51.所述pmos管p2的源极电性连接到电源vdd,漏极分别电性连接到第四电阻r4的另一端和输出电源端vrp;

52.所述第三电阻r3的另一端接地;

53.所述第三误差放大器a3的反相输入端分别电性连接到高电压检测器hd的检测输入端和nmos管n2的漏极并经偏置电流源ib 1接地,输出端电性连接到nmos管n1的栅极;

54.所述高电压检测器hd的检测输出端电性连接到nmos管n2的栅极,所述nmos管n2的源极接地;

55.所述nmos管n1的漏极电性连接到电源vdd,源极电性连接到输出电源端vcm并经偏置电流源ib 1接地。

56.在一种实施方式中,所述第一电阻r1为可通过控制字修调其阻值的可修调电阻。

57.请参见图6所示,在一种实施方式中,所述高电压检测器hd包括pmos管p3、pmos管p4、nmos管n3、nmos管n4和偏置电流源i2,其中,

58.所述pmos管p3的源极经偏置电流源i2电性连接到电源电压vdd,栅极电性连接到高电压检测器hd的参考输入端,漏极分别电性连接到nmos管n3的漏极和高电压检测器hd的输出端;

59.所述pmos管p4的源极经偏置电流源i2电性连接到电源电压vdd,栅极电性连接到高电压检测器hd的检测输入端,漏极分别电性连接到nmos管n4的漏极、栅极和nmos管n3的栅极;

60.所述nmos管n3的源极接地;

61.所述nmos管n4的源极接地。

62.在一种实施方式中,所述第三nmos管n3与第四nmos管n4的尺寸相互匹配,且所述第三nmos管n3与第四nmos管n4的尺寸比为3:1。

63.在一种实施方式中,所述高电压检测器hd被配置为在检测到检测输入端的电压高于参考输入端的电压超过预设定比例时输出高电平。

64.在一种实施方式中,所述预设定比例为20%。

65.下面结合附图具体说明本发明的优点

66.参见图7所示,本发明的参考电压缓冲器环路增益带宽积为80khz,0db带宽为47mhz,相位裕度为80度,环路稳定性较好。

67.参见图8所示,是参考电压缓冲器的输出电压瞬态仿真结果图,考虑到adc中比较器的建立时间,需要参考电压在250ns内缓冲至稳定的1.25v,可以看到,本发明的参考电压缓冲器在100ns以内就可以达到稳定输出。

68.参见图9所示,是输出电压仿真结果局部放大图,可以看到,下过冲电压和上过冲电压分别可以在58ns和52ns内恢复到终值

±

0.5lsb范围内(即1.2497v~1.2503v)。

69.参见图10所示,是本发明与传统参考电压缓冲器的输出电压瞬态仿真结果对比,可以看到,传统参考电压缓冲器需要160ns才能完成建立,而本发明通过高电压检测器hd检测输出电压来控制n2导通,大大加快了下拉速度,将建立时间缩短至52ns。

70.当然上述实施例只为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明主要技术方案的精神实质所做的修饰,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。