1.本发明涉及芯片载板制造的技术领域,尤其涉及一种芯片载板的制造方法及芯片载板。

背景技术:

2.随着消费电子市场的快速增长,加上超大规模集成电路的广泛应用,人们对于可视化硬件产品质量要求越来越高、功能越来越全面,模块的尺寸、功能已经成为消费者购买电子设备时首要考虑的指标。随着移动信息技术的不断发展,便携式电子设备也在朝着轻薄化等方向发展,与此同时,对搭载在便携式电子设备上的芯片载板有着更轻薄的要求,围绕着更轻薄的载板制造工艺过程中也会产生一些相应的制造工艺的问题。

技术实现要素:

3.为了解决轻薄芯片载板的制造工艺相关的问题,本发明的目的在于提供一种生产更为轻薄的芯片载板的芯片载板的制造方法及芯片载板,并且针对载板在制造过程中的一些问题如镍层的黑盘问题、提高抗氧化性和导电线、以及化学镀钯存在的镀层性能以及镀液的稳定性方面的问题也提出了相应的解决方案。

4.根据本发明的一方面,提供一种芯片载板的制造方法,所述芯片载板的制造方法包括:

5.开料,将基板开料;

6.内层线路制作,在基板上进行内层线路制作;所述内层线路制作包括:

7.磨板,将基板表面通过刷磨和微蚀以粗化处理;

8.贴膜,将15-20μm的干膜贴附在基板上;

9.曝光,将贴有干膜的基板曝光处理,其中曝光能量为80-90毫焦耳;

10.显影,将曝光后的基板通过显影液显影处理并得到内层线路图形;

11.蚀刻,将基板上内层线路图形以外的铜层蚀刻去除,退膜后得到所需的内层线路板,其中,蚀刻速度为4-5米/min;

12.层压,将内层线路板与半固化片的单侧覆铜板抽真空压合成整体线路板;

13.沉铜,在所述整体线路板上沉铜处理;

14.外层线路制作,在所述整体线路板上进行外层线路制作;所述外层线路制作包括:

15.磨板,将整体线路板表面粗化处理;

16.贴膜,将15-20μm的干膜贴附在整体线路板上;

17.曝光,将贴有干膜的整体线路板曝光处理,其中曝光能量为80-90毫焦耳;

18.显影,将曝光后的整体线路板通过显影液显影处理并得到外层线路图形;

19.外层阻焊,对整体线路板进行阻焊处理;

20.表面处理,对整体线路板进行表面处理。

21.作为本发明的一个实施例,所述外层阻焊包括:

22.在整体线路板上贴设第一阻焊层;

23.在所述第一阻焊膜上设置第一金层;

24.在所述第一金层上贴设置第一金属钯层;

25.在所述第一金属钯层上设有第一镍层;

26.在所述第一镍层上交替贴附有若干铜线路层和若干介质层;

27.在所述铜线路层上设置第二镍层;

28.在所述第二镍层上设置第二金属钯层;

29.在所述第二金属钯层上设置第二金层;

30.在所述第二金层上设有第二阻焊层。

31.作为本发明的一个实施例,所述在所述第一镍层上交替贴附有若干铜线路层和若干介质层包括:

32.在所述第一镍层上贴附有第一铜线路层;

33.在所述第一铜线路层上贴附有第一介质层;

34.在所述第一介质层上贴附有第二铜线路层;

35.在所述第二铜线路层上贴附有第三介质层;

36.在所述第三介质层上贴附有第四铜线路层。

37.作为本发明的一个实施例,所述在所述第一阻焊膜上设置第一金层使用化学镀金工艺,其中,化学镀金液的配方为:hdq-71化学镀金液100ml/l、kau(cn)21.5g/l,化学镀金工艺的镀液ph为4.8,化学镀金工艺的温度84℃,化学镀金工艺的时间20min;

38.所述在所述第一金层上贴设置第一金属钯层使用化学镀钯工艺,其中,化学镀钯液配方:硫酸四氨钯(pd(nh3)4so4)0.005mol/l、还原剂次磷酸钠(nah2po2·

h2o)0.01mol/l、络合剂有机胺0.1mol/l、甘氨酸0.08mol/l、稳定剂b0.3mol/l、稳定剂c1ppm,化学镀钯工艺的镀液ph为6.0或6.6或7.2或7.8,化学镀钯工艺的温度45℃-60℃,化学镀钯工艺的时间15min;

39.所述在所述第一金属钯层上设有第一镍层使用化学镀镍工艺,其中,化学镀镍液配方为:hdq-209m化学镍镀液120ml/l、hdq-209a化学镍镀液45ml/l、hdq-209d化学镍镀液3ml/l,化学镀镍工艺的镀液为ph=4.7,化学镀镍工艺的温度84℃,化学镀镍工艺的时间25min。

40.作为本发明的一个实施例,所述在所述铜线路层上设置第二镍层使用化学镀镍工艺,其中,化学镀镍液配方为:hdq-209m化学镍镀液120ml/l、hdq-209a化学镍镀液45ml/l、hdq-209d化学镍镀液3ml/l,化学镀镍工艺的镀液为ph=4.7,化学镀镍工艺的温度84℃,化学镀镍工艺的时间25min;

41.在所述第二镍层上设置第二金属钯层使用化学镀钯工艺,其中,化学镀钯液配方:硫酸四氨钯(pd(nh3)4so4)0.005mol/l、还原剂次磷酸钠(nah2po2·

h2o)0.01mol/l、络合剂有机胺0.1mol/l、甘氨酸0.08mol/l、稳定剂b0.3mol/l、稳定剂c1ppm,化学镀钯工艺的镀液ph为6.0或6.6或7.2或7.8,化学镀钯工艺的温度45℃-60℃,化学镀钯工艺的时间15min;

42.在所述第二金属钯层上设置第二金层使用化学镀金工艺,其中,化学镀金液的配方为:hdq-71化学镀金液100ml/l、kau(cn)21.5g/l,化学镀金工艺的镀液ph为4.8,化学镀金工艺的温度84℃,化学镀金工艺的时间20min。

43.作为本发明的一个实施例,所述外层线路制作的步骤中,所述磨板工艺包括:

44.铝粉磨板,所述铝粉磨板工艺中,al2o3含量为15-25%,al2o3喷压为20-30psi,磨板速度为:1.9-2m/min。

45.作为本发明的一个实施例,所述芯片载板的制造方法还包括:

46.字符制作,在所述整体线路板上制作文字;所述字符制作的步骤位于所述外层线路制作和所述表面处理的步骤之间;

47.成型处理,在所述整体线路板上放入锣机,按设计的外形尺寸锣出成品,所述成型处理的步骤位于所述表面处理的步骤之后。

48.作为本发明的一个实施例,所述基板为覆铜板。

49.作为本发明的一个实施例,所述沉铜的步骤包括依次进行的如下步骤:膨松、除胶渣、酸洗、整孔、微蚀、预浸、活化、沉铜和烘干。

50.根据本发明的另一方面,提供一种芯片载板,所述芯片载板由上述任一实施例中的所述的芯片载板的制造方法制成。

51.实施本发明实施例,将具有如下有益效果:

52.1、本实施例中的芯片载板的制造方法,由于内层线路制作中,干膜的厚度为15-20μm,在后续曝光工艺和显影工艺之后,不仅能够很好的保证形成的内层线路图形的导通率,还能够使得形成的内层线路图形的厚度更小,从而可以使得制成的芯片载板的厚度能够更薄。由于干膜的厚度为15-20μm,故而需要将曝光机的曝光能量调整为80-90毫焦耳,在这个范围内,能够使厚度为15-20μm的干膜充分曝光,又不会曝光过度,从而使得后续的显影工艺能够将干膜未被曝光的部位充分显影。将蚀刻速度设为4-5米/min,不仅能够快速完成蚀刻工艺,而且需要被去除的部分能够保证被完全去除。最终能够在保证生产效率的前提下,制成的芯片载板也具有质量保证。同样,由于外层线路制作中的工艺步骤和工艺参数和内层线路制作工艺基本相同,故而使得本实施例中的芯片载板的制造方法制造的芯片载板更薄,且质量更佳。

53.2、本技术中设置,芯片载板的装贴面到焊接面依次为第一阻焊膜、第一金层、第一金属钯层、第一镍层、若干铜线路层、若干介质层、第二镍层、第二金属钯层、第二金层和第二阻焊层,通过以上述工艺制成的芯片载板不仅抗氧化性能极佳,从而间接提高了导电性能,而且还具有多次焊接的性能以及焊接的可靠性,且具有很好的防腐蚀性能,还能够防止第一镍层表面出现黑盘的问题。

54.3、本技术中通过设置三层介质层和四层铜线路层,将每一层介质层分别夹设在两个铜线路层之间,从而能够大大提高抗氧化性能和导电性能。

55.4、本技术中化学镀钯工艺的温度在40-50℃的范围内,化学镀靶的表面呈现出完整、无缺陷的状态,化学镀钯温度选择40-50℃,既保证了镀层性能和镀液稳定性,同时也降低了能耗,同时,当镀液的ph值在6.0-7.8的范围内,镀层的表面呈现出完整的状态,同时对镀层的腐蚀性较低。

附图说明

56.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本

发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

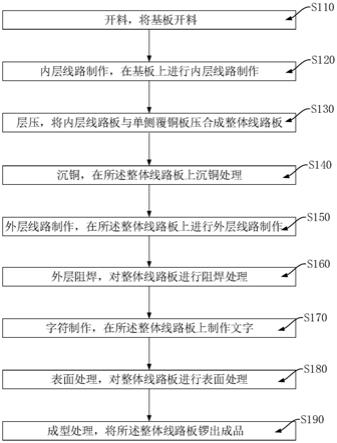

57.图1为本发明一实施例所述的芯片载板的制造方法的工艺流程示意图;

58.图2为图1中的内层线路制作的工艺流程示意图;

59.图3为图1中的外层线路制作的工艺流程示意图;

60.图4为图1中的外层阻焊的工艺流程示意图。

具体实施方式

61.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的较佳的实施例。但是,本发明可以容许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容的理解更加透彻全面。

62.需要说明的是,当元件被称为“固定于”另一个元件,它可以直接在另一个元件上或者也可以存在居中的元件。当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中元件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

63.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

64.请参考图1,本发明一实施例提供了一种芯片载板的制造方法。本实施例中的芯片载板的制造方法包括:

65.s110、开料,将基板开料。

66.具体地,基板为覆铜板。

67.s120、内层线路制作,在基板上进行内层线路制作。

68.请参考图2,在一实施例中,内层线路制作的步骤包括如下步骤:

69.s121、磨板,将基板表面通过刷磨和微蚀以粗化处理。通过对基板表面粗化处理后,能够方便后续贴膜工艺的进行,能够提高后续贴膜工艺的成功率。

70.优选地,可通过磨板机磨刷,去除基板表面的氧化层及毛刺。

71.s122、贴膜,将15-20μm的干膜贴附在基板上;当干膜的厚度为15-20μm,在后续曝光工艺和显影工艺之后,不仅能够很好的保证形成的内层线路图形的导通率,能够满足范围在1.7/1.7-2.1/2.1mil的线宽线距的电路板,从而能够使得形成的内层线路图形的厚度更小,从而可以使得制成的芯片载板的厚度能够更薄。

72.优选地,干膜的厚度为18μm,实验证明,当干膜的厚度为18μm时,在内层线路图形的导通率达标的情况下,芯片载板的厚度也较小,且曝光效果最佳。

73.s123、曝光,将贴有干膜的基板曝光处理,其中曝光能量为80-90毫焦耳。由于干膜的厚度为15-20μm,故而需要将曝光机的曝光能量调整为80-90毫焦耳,在这个范围内,能够使厚度为15-20μm的干膜充分曝光,又不会曝光过度,从而使得后续的显影工艺能够将干膜未被曝光的部位充分显影。

74.优选地,当干膜的厚度为18μm时,曝光机的曝光能量调整为85毫焦耳,此时曝光的效果最佳。

75.参照下述表格中的实验数据,能够清楚得知本技术中的干膜厚度的最佳范围。

[0076][0077]

由上述表格可知,当干膜的厚度在15-20μm的时候,此时线宽线距均较小,制成的芯片载板的厚度相对更薄,而且在此范围内,不会造成过度曝光,从而不会影响后续的工艺步骤,也就不会影响制成的芯片载板的性能。

[0078]

s124、显影,将曝光后的基板通过显影液显影处理并得到内层线路图形;通过显影液能够将干膜未被曝光的部位去除从而得到内层线路图形。

[0079]

优选地,显影液为碳酸钠水溶液。

[0080]

s125、蚀刻,将基板上内层线路图形以外的铜层蚀刻去除,退膜后得到所需的内层线路板,其中,蚀刻速度为4-5米/min;将蚀刻速度设为4-5米/min,不仅能够快速完成蚀刻工艺,而且需要被去除的部分能够保证被完全去除。最终能够在保证生产效率的前提下,制成的芯片载板也具有质量保证。

[0081]

优选地,蚀刻工序中,控制蚀刻液中的cu2浓度为135

±

15g/1,c1浓度为5.3

±

0.5n,温度为50

±

2℃,ph值为8.3

±

0.4,比重1.185

±

0.02,蚀刻速度为4-5m/min,蚀刻次数为3次,每次蚀刻后翻转板面一次。

[0082]

在其它实施例中,还可以是通过盐酸和双氧水的混合液作为蚀刻液进行蚀刻。

[0083]

s130、层压,将内层线路板与半固化片的单侧覆铜板抽真空压合成整体线路板;通过层压后能够进一步降低制成后的芯片载板的厚度,使芯片载板更为轻薄。

[0084]

s140、沉铜,在整体线路板上沉铜处理。

[0085]

在一实施例中,沉铜步骤s130包括:依次进行的如下步骤:膨松、除胶渣、酸洗、整孔、微蚀、预浸、活化、沉铜和烘干。

[0086]

s150、外层线路制作,在整体线路板上进行外层线路制作。

[0087]

请参考图3,在一实施例中,外层线路制作的步骤包括如下步骤:

[0088]

s151、磨板,将整体线路板表面粗化处理。通过对基板表面粗化处理后,能够方便后续贴膜工艺的进行,能够提高后续贴膜工艺的成功率。

[0089]

优选地,磨板工艺s151为铝粉磨板,在该铝粉磨板工艺中,al2o3含量为15-25%,al2o3喷压为20-30psi,磨板速度为:1.9-2m/min。将磨板工艺s151设为铝粉磨板,使得其对整体线路板的边角和毛刺的刷磨效果更佳,利于后续的贴膜。

[0090]

s152、贴膜,将15-20μm的干膜贴附在整体线路板上;当干膜的厚度为15-20μm,在后续曝光工艺和显影工艺之后,不仅能够很好的保证形成的外层线路图形的导通率,还能够使得形成的外层线路图形的厚度更小,从而可以使得制成的芯片载板的厚度能够更薄。

[0091]

优选地,干膜的厚度为18μm,实验证明,当干膜的厚度为18μm时,在外层线路图形的导通率达标的情况下,外层线路图形的厚度也在最小。

[0092]

s153、曝光,将贴有干膜的整体线路板曝光处理,其中曝光能量为80-90毫焦耳。由于干膜的厚度为15-20μm,故而需要将曝光机的曝光能量调整为80-90毫焦耳,在这个范围内,能够使厚度为15-20μm的干膜充分曝光,又不会曝光过度,从而使得后续的显影工艺能够将干膜未被曝光的部位充分显影。

[0093]

优选地,当干膜的厚度为18μm时,曝光机的曝光能量调整为52毫焦耳,此时曝光的效果最佳。

[0094]

s154、显影,将曝光后的基板通过显影液显影处理并得到外层线路图形;具体地,通过显影液能够将干膜未被曝光的部位去除从而得到外层线路图形。

[0095]

优选地,显影液为碳酸钠水溶液。

[0096]

s160、外层阻焊,对整体线路板进行阻焊处理;通过外层阻焊能够防止焊接前整体线路板发生氧化。

[0097]

具体地,外层阻焊可使用抗氧化性材料。

[0098]

请参考图4,在一实施例中,外层阻焊的步骤s160包括如下步骤:

[0099]

s161、在整体线路板上贴设第一阻焊层;

[0100]

s162、在第一阻焊膜上设置第一金层;

[0101]

s163、在第一金层上贴设置第一金属钯层;

[0102]

s164、在第一金属钯层上设有第一镍层;

[0103]

s165、在第一镍层上交替贴附有若干铜线路层和若干介质层;

[0104]

s166、在铜线路层上设置第二镍层;

[0105]

s167、在第二镍层上设置第二金属钯层;

[0106]

s168、在第二金属钯层上设置第二金层;

[0107]

s169、在第二金层上设有第二阻焊层。

[0108]

通过外层阻焊的步骤s160所制造出来的芯片载板,自芯片载板的装贴面到焊接面依次为第一阻焊膜、第一金层、第一金属钯层、第一镍层、若干铜线路层、若干介质层、第二镍层、第二金属钯层、第二金层和第二阻焊层。通过上述工艺制成的芯片载板不仅抗氧化性能极佳,从而间接提高了导电性能,而且还具有多次焊接的性能以及焊接的可靠性,且具有很好的防腐蚀性能,还能够防止第一镍层表面出现黑盘的问题。

[0109]

进一步地,在第一镍层上交替贴附有若干铜线路层和若干介质层的步骤s165包括:

[0110]

在第一镍层上贴附有第一铜线路层;

[0111]

在第一铜线路层上贴附有第一介质层;

[0112]

在第一介质层上贴附有第二铜线路层;

[0113]

在第二铜线路层上贴附有第三介质层;

[0114]

在第三介质层上贴附有第四铜线路层。

[0115]

本实施例中,通过设置三层介质层和四层铜线路层,将每一层介质层分别夹设在两个铜线路层之间,从而能够大大提高抗氧化性能和导电性能。

[0116]

最佳工艺条件下,钯层性能良好,而且可以减少镀金中对镍层造成的影响,同时,这种情况下具有耐腐蚀工艺良好的优势,可以被运用在线路板镍钯金的工艺生产中。

[0117]

在一具体的实施例中,在第一阻焊膜上设置第一金层的步骤s162使用化学镀金工艺,其中,化学镀金液的配方为:hdq-71化学镀金液100ml/l、kau(cn)21.5g/l,化学镀金工艺的镀液ph为4.8,化学镀金工艺的温度84℃,化学镀金工艺的时间20min。由于化学镀金工艺的镀液ph为4.8,化学镀金工艺的温度84℃,此时化学镀金速率最高,将化学镀金工艺的时间设为20min,能够在最短的时间内充分镀金。

[0118]

在第一金层上贴设置第一金属钯层的步骤s163使用化学镀钯工艺,其中,化学镀钯液配方:硫酸四氨钯(pd(nh3)4so4)0.005mol/l、还原剂次磷酸钠(nah2po2·

h2o)0.01mol/l、络合剂有机胺0.1mol/l、甘氨酸0.08mol/l、稳定剂b0.3mol/l、稳定剂c1ppm,化学镀钯工艺的镀液ph为6.0或6.6或7.2或7.8,化学镀钯工艺的温度45℃-60℃,化学镀钯工艺的时间15min。当镀液的ph值在6.0-7.8的范围内,镀层的表面呈现出完整的状态,同时对镀层的腐蚀性较低。

[0119]

优选地,化学镀钯工艺的温度在40-50℃的范围内,化学镀靶的表面呈现出完整、无缺陷的状态。化学镀钯温度选择40-50℃,既保证了镀层性能和镀液稳定性,同时也降低了能耗。

[0120]

在第一金属钯层上设有第一镍层的步骤s164使用化学镀镍工艺,其中,化学镀镍液配方为:hdq-209m化学镍镀液120ml/l、hdq-209a化学镍镀液45ml/l、hdq-209d化学镍镀液3ml/l,化学镀镍工艺的镀液为ph=4.7,化学镀镍工艺的温度84℃,化学镀镍工艺的时间25min。

[0121]

本实施例中,在上述工艺条件下,钯层性能良好,而且可以减少镀金中对镍层造成的影响,同时,这种情况下具有耐腐蚀工艺良好的优势。

[0122]

在一具体的实施例中,在铜线路层上设置第二镍层的步骤s166使用化学镀镍工艺,其中,化学镀镍液配方为:hdq-209m化学镍镀液120ml/l、hdq-209a化学镍镀液45ml/l、hdq-209d化学镍镀液3ml/l,化学镀镍工艺的镀液为ph=4.7,化学镀镍工艺的温度84℃,化学镀镍工艺的时间25min。

[0123]

在第二镍层上设置第二金属钯层的步骤s167使用化学镀钯工艺,其中,化学镀钯液配方:硫酸四氨钯(pd(nh3)4so4)0.005mol/l、还原剂次磷酸钠(nah2po2·

h2o)0.01mol/l、络合剂有机胺0.1mol/l、甘氨酸0.08mol/l、稳定剂b0.3mol/l、稳定剂c1ppm,化学镀钯工艺的镀液ph为6.0或6.6或7.2或7.8,化学镀钯工艺的温度45℃-60℃,化学镀钯工艺的时间15min;当镀液的ph值在6.0-7.8的范围内,镀层的表面呈现出完整的状态,同时对镀层的腐蚀性较低。

[0124]

优选地,化学镀钯工艺的温度在40-50℃的范围内,化学镀靶的表面呈现出完整、无缺陷的状态。化学镀钯温度选择40-50℃,既保证了镀层性能和镀液稳定性,同时也降低了能耗。

[0125]

在一具体的实施例中,在第二金属钯层上设置第二金层的步骤s168使用化学镀金工艺,其中,化学镀金液的配方为:hdq-71化学镀金液100ml/l、kau(cn)21.5g/l,化学镀金工艺的镀液ph为4.8,化学镀金工艺的温度84℃,化学镀金工艺的时间20min。由于化学镀金工艺的镀液ph为4.8,化学镀金工艺的温度84℃,此时化学镀金速率最高,将化学镀金工艺的时间设为20min,能够在最短的时间内充分镀金。

[0126]

本实施例中,在上述工艺条件下,钯层性能良好,而且可以减少镀金中对镍层造成的影响,同时,这种情况下具有耐腐蚀工艺良好的优势。

[0127]

s170、字符制作,在整体线路板上制作文字。

[0128]

s180、表面处理,对整体线路板进行表面处理。

[0129]

s190、成型处理,在整体线路板上放入锣机,按设计的外形尺寸锣出成品。

[0130]

本发明还提供了一种芯片载板,该芯片载板由上述任一实施例中的芯片载板的制造方法制成。通过上述芯片载板的制造方法制成芯片载板的厚度更薄,稳定性更高。

[0131]

以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对申请专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。