1.实施方式涉及布线结构、形成该布线结构的方法以及包括该布线结构的半导体器件。

背景技术:

2.如果布线结构包括掺有杂质的多晶硅层以及金属层,则需要减小多晶硅层和金属层之间的接触电阻,并防止多晶硅层和金属层的元素扩散。因此,可以在多晶硅层和金属层之间形成欧姆接触层或扩散阻挡物。然而,如果欧姆接触层或扩散阻挡物具有厚的厚度,则布线结构的厚度可能增加。

技术实现要素:

3.实施方式涉及一种布线结构,该布线结构包括在衬底上的包括掺杂多晶硅的第一导电图案、在第一导电图案上的包括金属硅化物的欧姆接触图案、在欧姆接触上的包括金属硅氮化物的防氧化图案、在防氧化图案上的包括石墨烯的扩散阻挡物、以及在扩散阻挡物上的包括金属的第二导电图案。第一导电图案、欧姆接触图案、防氧化图案、扩散阻挡物和第二导电图案可以以所述顺序依次堆叠在衬底上。

4.实施方式还涉及一种布线结构,该布线结构包括在衬底上的包括掺杂多晶硅的第一导电图案、在第一导电图案上的包括金属硅化物的欧姆接触图案、在欧姆接触图案上的包括石墨烯的扩散阻挡物、在扩散阻挡物上的包括金属氮化物的防氧化图案、以及在防氧化图案上的包括金属的第二导电图案。第一导电图案、欧姆接触图案、扩散阻挡物、防氧化图案和第二导电图案可以以所述顺序依次堆叠在衬底上。

5.实施方式还涉及一种形成布线结构的方法。在该方法中,可以在衬底上形成包括掺杂多晶硅的第一导电层。可以在第一导电层上形成包括金属硅化物的欧姆接触层。可以通过氮化处理工艺在欧姆接触层上形成包括金属硅氮化物的防氧化层。可以在防氧化层上形成包括石墨烯的扩散阻挡层。可以在扩散阻挡层上形成包括金属的第二导电层。可以通过使用掩模的蚀刻工艺图案化第二导电层、扩散阻挡层、防氧化层、欧姆接触层和第一导电层以在衬底上形成依次堆叠的第一导电图案、欧姆接触图案、防氧化图案、扩散阻挡物和第二导电图案。

6.实施方式还涉及一种形成布线结构的方法。在该方法中,可以在衬底上形成包括掺杂多晶硅的第一导电层。可以在第一导电层上形成包括石墨烯的扩散阻挡层。可以在扩散阻挡层上形成金属层,从而可以在第一导电层和扩散阻挡层之间形成包括金属硅化物的欧姆接触层。可以对金属层执行氮化处理工艺以在扩散阻挡层上形成防氧化层。可以在扩散阻挡层上形成包括金属的第二导电层。可以通过使用掩模的蚀刻工艺图案化第二导电层、防氧化层、扩散阻挡层、欧姆接触层和第一导电层以形成依次堆叠在衬底上的第一导电图案、欧姆接触图案、扩散阻挡物、防氧化图案和第二导电图案。

7.实施方式还涉及一种半导体器件,该半导体器件包括在衬底上的有源图案、掩埋

在有源图案的上部处的栅极结构、在有源图案上的位线结构、在有源图案的与位线结构相邻的部分上的接触插塞结构、以及在接触插塞结构上的电容器。位线结构可以包括包含掺杂多晶硅的第一导电图案、在第一导电图案上的包括金属硅化物的第一欧姆接触图案、在第一欧姆接触图案上的包括金属硅氮化物的第一防氧化图案、在第一防氧化图案上的包括石墨烯的第一扩散阻挡物、以及在第一扩散阻挡层上的包括金属的第二导电图案。第一导电图案、第一欧姆接触图案、第一防氧化图案、第一扩散阻挡物和第二导电图案可以以所述顺序依次堆叠。

8.实施方式还涉及一种半导体器件,该半导体器件包括在衬底上的有源图案、掩埋在有源图案的上部处的栅极结构、在有源图案上的位线结构、在有源图案的与位线结构相邻的部分上的接触插塞结构、以及在接触插塞结构上的电容器。位线结构可以包括包含掺杂多晶硅的第一导电图案、在第一导电图案上的包括金属硅化物的第一欧姆接触图案、在第一欧姆接触图案上的包括石墨烯的第一扩散阻挡物、在第一扩散阻挡物上的包括金属氮化物的防氧化图案、以及在防氧化图案上的包括金属的第二导电图案。第一导电图案、第一欧姆接触图案、第一扩散阻挡物、防氧化图案和第二导电图案可以以所述顺序依次堆叠。

附图说明

9.通过参考附图详细描述示例实施方式,特征对本领域技术人员将变得明显,其中:

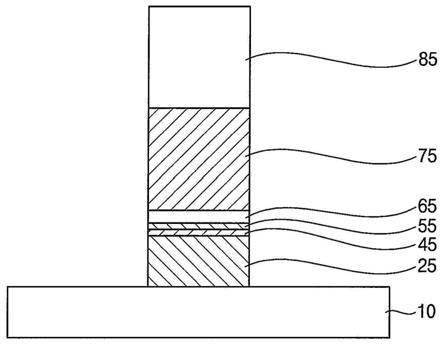

10.图1是示出根据示例实施方式的布线结构的截面图。

11.图2至图5是示出根据示例实施方式的形成布线结构的方法的截面图。

12.图6是示出根据示例实施方式的布线结构的截面图。

13.图7和图8是示出根据示例实施方式的形成布线结构的方法的截面图。

14.图9和图10是示出根据示例实施方式的半导体器件的平面图和截面图。

15.图11至图25是示出根据示例实施方式的制造半导体器件的方法的平面图和截面图。

16.图26是示出根据示例实施方式的半导体器件的截面图。

17.图27是示出根据示例实施方式的半导体器件的截面图。

18.图28是示出根据示例实施方式的制造半导体器件的方法的截面图。

19.图29是示出根据示例实施方式的半导体器件的截面图。

具体实施方式

20.图1是示出根据示例实施方式的布线结构的截面图。

21.参照图1,布线结构可以包括可依次堆叠在衬底10上的第一导电图案25、欧姆接触图案45、防氧化图案55、扩散阻挡物65和第二导电图案75。掩模85可以在布线结构上,例如在第二导电图案75上。

22.衬底10可以包括硅、锗、硅锗或诸如gap、gaas或gasb的iii-v族化合物半导体。在示例实施方式中,衬底10可以是绝缘体上硅(soi)衬底或绝缘体上锗(goi)衬底。

23.在示例实施方式中,欧姆接触图案45可以包括金属硅化物。在一示例实施方式中,欧姆接触图案45可以包括钛硅化物(tisi2)。在另一实现方式中,欧姆接触图案45可以包括钽硅化物或钨硅化物。

24.欧姆接触图案45可以具有约0.1nm至约1nm的厚度。在一示例实施方式中,欧姆接触图案45可以具有约0.5nm的厚度。

25.在示例实施方式中,防氧化图案55可以包括金属硅氮化物。在一示例实施方式中,防氧化图案55可以包括钛硅氮化物(tisin)。在另一实现方式中,防氧化图案55可以包括钽硅氮化物或钨硅氮化物。

26.防氧化图案55可以具有约0.1nm至约1nm的厚度。在一示例实施方式中,防氧化图案55可以具有约0.5nm的厚度。

27.在示例实施方式中,扩散阻挡物65可以包括石墨烯。扩散阻挡物65可具有约0.5nm至约2nm的厚度。在一示例实施方式中,扩散阻挡物65可以具有约1nm的厚度。

28.第二导电图案75可以包括具有比第一导电图案25的电阻小的电阻的材料,例如低电阻金属,诸如钨、铝、铜、钌、钼、铑、铱等。

29.掩模85可以包括氮化物,例如硅氮化物。

30.布线结构可以包括依次堆叠在第一导电图案25和第二导电图案75之间的欧姆接触图案45、防氧化图案55和扩散阻挡物65。

31.扩散阻挡物65可以减少或防止第一导电图案25中的硅和第二导电图案75中的金属扩散。与一般的扩散阻挡物相比,扩散阻挡物65可以具有相对减小的厚度,因此包括扩散阻挡物65的布线结构可以具有减小的厚度。

32.欧姆接触图案45可以增强第一导电图案25和第二导电图案75之间的欧姆特性。由于欧姆接触图案45形成在第一导电图案25和第二导电图案75之间,所以第一导电图案25和第二导电图案75之间的接触电阻可以减小,并且布线结构的总电阻可以减小。如下文参照图2至图5所示,欧姆接触图案45可以形成在第一导电图案25上,因此可以防止由于自然氧化物层(即,金属氧化物层)而引起的电阻增大。

33.金属氧化物层,例如钛氧化物层、钽氧化物层、钨氧化物层等,可能进一步形成在第一导电图案25和防氧化图案55之间,然而,金属氧化物层可以不形成在第一导电图案25的整个上表面上,而是形成在第一导电图案25的上表面的一部分上。因此,由于金属氧化物层引起的电阻增大可以非常轻微。

34.防氧化图案55可以阻止氧被提供到欧姆接触图案45上,使得可以不形成自然氧化物层。

35.欧姆接触图案45和防氧化图案55可以具有比扩散阻挡物65小的厚度,因此,即使欧姆接触图案45和防氧化图案55形成在第一导电图案25和第二导电图案75之间,布线结构也可以具有减小的厚度。在一示例实施方式中,欧姆接触图案45和防氧化图案55的组合厚度可以小于或等于扩散阻挡物65的厚度。

36.即使具有减小的厚度,布线结构也可以提供减小的电阻。

37.图2至图5是示出根据示例实施方式的形成布线结构的方法的截面图。

38.参照图2,可以在衬底10上形成第一导电层20。

39.在示例实施方式中,第一导电层20可以包括掺有杂质的多晶硅。

40.可以通过包含在空气中的氧在第一导电层20上形成自然氧化物层30。

41.参照图3,可以去除第一导电层20上的自然氧化物层30。

42.在示例实施方式中,可以通过等离子体处理工艺去除自然氧化物层30。可以使用

例如氢等离子体、氩等离子体等来执行等离子体处理工艺。

43.即使进行等离子体处理工艺,第一导电层20上的自然氧化物层30也可能没有被完全去除,而是其一些部分可能保留。在另一实现方式中,可以不进行等离子体处理工艺,在这种情况下,自然氧化物层30可以保留在第一导电层20上。

44.参照图3,可以在第一导电层20上形成欧姆接触层401。欧姆接触层401可以通过例如化学气相沉积(cvd)工艺、等离子体增强化学气相沉积(pe-cvd)工艺、原子层沉积(ald)工艺等形成。

45.在一示例实施方式中,可以使用四氯化钛(ticl4)作为前体在等于或小于约700℃的温度执行pe-cvd工艺以在第一导电层20上形成钛层,包括在第一导电层20中的硅可以与钛层结合以形成包括钛硅化物的欧姆接触层401。

46.如果自然氧化物层30全部或部分地保留在第一导电层20的上表面上,则自然氧化物层30可以与钛结合以形成钛氧化物(tio2)层,然而,钛氧化物层可以不完全形成在第一导电层20的上表面上而是仅部分地形成在第一导电层20的上表面上。由于欧姆接触层401形成,第一导电层20的上表面的整个部分或大部分可以被欧姆接触层401覆盖。

47.在另一实现方式中,可以使用钽或钨作为前体来执行沉积工艺,使得欧姆接触层401可以形成为包括钽硅化物或钨硅化物。

48.欧姆接触层401可以包括约0.2nm至约2nm的厚度。

49.参照图4,可以对欧姆接触层401执行氮化处理工艺以形成包括金属硅氮化物的防氧化层50。

50.在示例实施方式中,氮化处理工艺可以在氨(nh3)气或氮(n2)气的气氛下通过等离子体处理工艺或热处理工艺进行。

51.在示例实施方式中,欧姆接触层401的上部可以被氮化以形成防氧化层50,其下部成为欧姆接触层40。欧姆接触层40和防氧化层50中的每个可以具有约0.1nm至约1nm的厚度。例如,欧姆接触层401的厚度的大约二分之一可以转化为相应的氮化物。

52.如上所述,如果欧姆接触层401包括钛硅化物,则防氧化层50可以包括钛硅氮化物。在另一实现方式中,如果欧姆接触层401包括钽硅化物或钨硅化物,则防氧化层50可以分别包括钽硅氮化物或钨硅氮化物。

53.因为防氧化层50形成在欧姆接触层40的上表面上,所以自然氧化物层可能不会由于包含在空气中的氧而形成在欧姆接触层40的上表面上。

54.参照图5,可以在防氧化层50上形成扩散阻挡层60,并且可以在扩散阻挡层60上形成第二导电层70。

55.在示例实施方式中,扩散阻挡层60可以通过使用例如烃作为前体、例如氢气或氩气作为载气、并且例如热或等离子体作为用于分解前体的能量源的cvd工艺而形成。扩散阻挡层60可以具有约0.5nm至约2nm的厚度。扩散阻挡层60可以是例如通过例如烃前体的还原和/或分解形成的石墨烯层。

56.在示例实施方式中,可以原位执行用于形成防氧化层50的工艺和用于形成扩散阻挡层60的工艺,因此可以防止自然氧化物层的形成。

57.再次参照图1,可以在第二导电层70上形成掩模85,并且可以使用掩模85作为蚀刻掩模依次蚀刻和图案化第二导电层70、扩散阻挡层60、防氧化层50、欧姆接触层40和第一导

电层20,以在衬底10上形成布线结构。

58.如上所述,在第一导电层20上形成扩散阻挡层60之前,可以在第一导电层20上形成欧姆接触层40,因此保留在第一导电层20上的自然氧化物层30可以被去除。即使形成了欧姆接触层40,自然氧化物层(即,金属氧化物层)也可能保留在第一导电层20上,然而,金属氧化物层可以不形成在第一导电层20的整个上表面上,而是仅形成在第一导电层20的上表面的非常小的部分上,这可以仅导致电阻的非常轻微的增大。另外,可以对自然氧化物层30执行另外的等离子体处理工艺,从而可以防止金属氧化物层的形成。

59.欧姆接触层40可以增强第一导电层20和第二导电层70之间的欧姆接触特性,因此可以减小它们之间的接触电阻。

60.另外,可以通过对欧姆接触层40的上表面的氮化处理工艺而在欧姆接触层40上形成防氧化层50,从而可以防止由包含在空气中的氧形成自然氧化物层。

61.第一导电层20和第二导电层70之间的扩散阻挡层60可以用作用于防止或减少包括在第一导电层20和第二导电层70中的元素扩散的阻挡物。

62.扩散阻挡层60可以具有约1nm的厚度,并且依次堆叠在扩散阻挡层60下方的防氧化层50和欧姆接触层40中的每个也可以具有约0.5nm的厚度。因此,包括欧姆接触层40、防氧化层50和扩散阻挡层60的布线结构可以具有减小的总厚度,并且可以在第一导电图案25和第二导电图案75之间提供减小的电阻和增强的扩散阻挡特性。

63.图6是示出根据示例实施方式的布线结构的截面图。除了防氧化图案之外,布线结构可以与图1的布线结构基本相同或相似。因此,相同的附图标记指代相同的元件,并且在这里省略对其的详细描述。

64.参照图6,布线结构可以包括依次堆叠在衬底10上的第一导电图案25、欧姆接触图案45、扩散阻挡物65、防氧化图案57和第二导电图案75。掩模85可以在第二导电图案75上。

65.因此,布线结构可以不包括在欧姆接触图案45和扩散阻挡物65之间的防氧化图案55,但是可以包括在扩散阻挡物65和第二导电图案75之间的防氧化图案57。

66.在示例实施方式中,防氧化图案57可以包括金属氮化物。在一示例实施方式中,防氧化图案57可以包括钛氮化物。在另一实现方式中,防氧化图案57可以包括钽氮化物或钨氮化物。

67.防氧化图案57可以阻止氧被提供到扩散阻挡物65上以防止形成自然氧化物层。防氧化图案57可以具有约0.1nm至约1nm的厚度。在一示例实施方式中,防氧化图案57可以具有约0.5nm的厚度。

68.图7和图8是示出根据示例实施方式的形成布线结构的方法的截面图。该方法可以包括与参照图2至图5和图1所示的那些基本相同或相似的工艺,因此在这里省略其重复说明。

69.参照图7,可以执行与参照图2所示的那些基本相同或相似的工艺以在衬底10上形成第一导电层20,并且可以在第一导电层20上形成自然氧化物层30。自然氧化物层30可以通过等离子体处理工艺被完全或部分地去除,或者在没有等离子体处理工艺的情况下完全保留在第一导电层20上。

70.可以执行与参照图5所示的那些基本相同或相似的工艺以在第一导电层20上形成扩散阻挡层60。

71.参照图8,可以执行与参照图3和图4所示的那些基本相同或相似的工艺以在第一导电层20和扩散阻挡层60之间形成欧姆接触层40并且在欧姆接触层40上形成防氧化层52。

72.在一示例实施方式中,pe-cvd工艺可以使用例如四氯化钛(ticl4)作为前体在等于或小于约700℃的温度执行以在扩散阻挡层60上形成钛层。钛层的一部分可以穿过扩散阻挡层60移动到第一导电层20的上表面,并且可以与包括在第一导电层20中的硅结合。因此,欧姆接触层40可以在第一导电层20上形成为包括钛硅化物(tisi2)。如果例如在扩散阻挡层60上形成钽层或钨层而不是钛层,则欧姆接触层40可以形成为分别包括钽硅化物或钨硅化物。

73.不同于图3所示的结构,欧姆接触层40可以不直接形成在第一导电层20的上表面上,并且钛可以穿过扩散阻挡层60移动到第一导电层20的上表面以形成欧姆接触层40,从而不会过度形成欧姆接触层40。因此,扩散阻挡层60可以用作过滤钛的过滤器,因此欧姆接触层40可以具有约0.5nm的厚度,这可以是欧姆接触特性的最小厚度。

74.由于欧姆接触层40形成在第一导电层20上,所以第一导电层20上的自然氧化物层30可以大部分被去除,并且自然氧化物层30的一些部分可以保留,但可以不完全覆盖第一导电层20的上表面。

75.在欧姆接触层40形成在第一导电层20上之后,可以对扩散阻挡层60上的钛层进行氮化处理工艺以形成包括钛氮化物的防氧化层52。由于形成了防氧化层52,所以氧可以不被提供到扩散阻挡层60上,从而防止自然氧化物层的形成。

76.防氧化层52可以具有约0.5nm的厚度。代替钛氮化物,防氧化层52可以包括例如钽氮化物、钨氮化物等。

77.再次参照图5和图6,可以在防氧化层52上形成第二导电层70,并且可以执行与参照图6所示的那些基本相同或相似的工艺以形成第二导电图案75和下方的图案,并完成布线结构的形成。

78.图9和图10是示出根据示例实施方式的半导体器件的平面图和截面图,其中图10是沿着图9中的线b-b'和c-c'截取的截面图。该半导体器件可以是应用图1的布线结构的动态随机存取存储器(dram)装置,在这里省略重复说明。

79.基本平行于衬底100的上表面且彼此基本垂直的两个方向可以分别被称为第一方向和第二方向,基本平行于衬底100的上表面且相对于第一方向和第二方向具有锐角的方向可以被称为第三方向,基本平行于衬底100的上表面并且基本垂直于第三方向的方向可以被称为第四方向。

80.参照图9和图10,半导体器件可以包括栅极结构160、位线结构325、接触插塞结构和电容器540。此外,半导体器件可以包括间隔物结构、第二盖图案410、第一至第五绝缘图案175、185、195、340和350、蚀刻停止层500、以及第一至第三绝缘夹层480、490和550。

81.隔离图案110可以形成在衬底100上。有源图案105(其侧壁被隔离图案110覆盖)可以被限定在衬底100上。隔离图案110可以包括氧化物,例如,硅氧化物。

82.在示例实施方式中,多个有源图案105可以在第一方向和第二方向中的每个方向上彼此间隔开。每个有源图案105可以在第三方向上延伸至特定长度。

83.栅极结构160可以在第一方向上延伸穿过有源图案105的上部和隔离图案110的上部。多个栅极结构160可以在第二方向上彼此间隔开。因此,栅极结构160可以掩埋在有源图

案105的上部和隔离图案110的上部处。栅极结构160可以包括在基本垂直于衬底100的上表面的垂直方向上依次堆叠的栅极绝缘层130、栅电极140和栅极掩模150。

84.栅极绝缘层130可以形成在有源图案105的表面上。栅电极140可以在栅极绝缘层130和隔离图案110上沿第一方向延伸。栅极掩模150可以覆盖栅电极140的上表面。

85.栅极绝缘层130可以包括氧化物,例如硅氧化物。栅电极140可以包括金属(例如钨、钛、钽等)或者金属氮化物(例如钨氮化物、钛氮化物、钽氮化物等)。栅极掩模150可以包括氮化物,例如硅氮化物。

86.在示例实施方式中,位线结构325可以在有源图案105、隔离图案110和栅极结构160上沿第二方向延伸。多个位线结构325可以在第一方向上彼此间隔开。每个位线结构325可以接触有源图案105的上表面的在第三方向上的中心部分。

87.位线结构325可以包括在基本垂直于衬底100的上表面的垂直方向上依次堆叠的导电结构265、第一欧姆接触图案275、第一防氧化图案285、第一扩散阻挡物295、第六导电图案305。第一盖图案315可以堆叠在第六导电图案305上。在示例实施方式中,包括在位线结构325中的导电结构265、第一欧姆接触图案275、第一防氧化图案285、第一扩散阻挡物295、第六导电图案305和第一盖图案315可以包括分别与结合图1在以上描述的第一导电图案25、欧姆接触图案45、防氧化图案55、扩散阻挡物65、第二导电图案75和掩模85的材料基本相同的材料。

88.如上所述,位线结构325可以包括包含石墨烯并且具有相对薄的厚度的第一扩散阻挡物295,因此可以具有增强的扩散阻挡特性和减小的厚度。另外,位线结构325可以包括第一欧姆接触图案275和第一防氧化图案285,因此可以具有减小的电阻。

89.导电结构265可以包括依次堆叠的第四导电图案245和第五导电图案255(参见图16和图17)或依次堆叠的第三导电图案215和第五导电图案255(参见图16和图17)。在示例实施方式中,多个第四导电图案245可以在第一方向和第二方向中的每个方向上彼此间隔开。因此,每个第四导电图案245可以形成在有源图案105的上表面以及与其相邻的隔离图案110和栅极掩模150的上表面上的第二凹槽230中。第三导电图案215可以形成在第二凹槽230的外部。

90.第五导电图案255可以在第三导电图案215和第四导电图案245上沿第二方向延伸。第五导电图案255可以包括与第三导电图案215和第四导电图案245的材料基本相同的材料,例如掺有杂质的多晶硅,并且可以与第三导电图案215和第四导电图案245合并。

91.第一欧姆接触图案275、第一防氧化图案285、第一扩散阻挡物295、第六导电图案305和第一盖图案315中的每个可以在第五导电图案255上沿第二方向延伸。

92.间隔物结构可以形成在位线结构325的每个相对侧壁上,因此可以沿第二方向延伸。间隔物结构可以包括在位线结构的每个相对侧壁上在第一方向上依次堆叠的第一间隔物335、空气间隔物365、第三间隔物385和第四间隔物425。

93.第一间隔物335可以接触位线结构325的在第一方向上的侧壁。空气间隔物365可以接触第一间隔物335的外侧壁的一部分。第三间隔物385可以接触空气间隔物365的外侧壁。第四间隔物425可以接触第一盖图案315的上表面、第一间隔物335的上表面和上外侧壁、空气间隔物365的上表面以及第三间隔物385的上表面和上外侧壁。然而,在位线结构325的在第一方向上的侧壁被第二盖图案410围绕的区域中,空气间隔物365和第三间隔物

385可以在第一间隔物335的外侧壁上在第一方向上依次堆叠,并且可以不形成第四间隔物425。

94.在示例实施方式中,空气间隔物365和第三间隔物385的最上表面可以低于第一间隔物335的最上表面,并且可以高于位线结构325的第六导电图案305的上表面。

95.第一、第三和第四间隔物335、385和425中的每个可以包括氮化物,例如硅氮化物。空气间隔物365可以包括空气。

96.位线结构325的在第二凹槽230中的部分的侧壁和第二凹槽230的底部可以被第一间隔物335覆盖。第四绝缘图案340可以形成在第一间隔物335的在第二凹槽230中的部分上,第五绝缘图案350可以形成在第四绝缘图案340上以填充第二凹槽230的剩余部分。在示例实施方式中,空气间隔物365可以接触第四绝缘图案340的上表面和第五绝缘图案350的上表面,并且第三间隔物385可以接触第五绝缘图案350的上表面。

97.可以在第二凹槽230的外部在位线结构325与部分有源图案105和部分隔离图案110之间形成绝缘图案结构(包括在垂直方向上依次堆叠的第一至第三绝缘图案175、185和195)。第二绝缘图案185可以接触具有“l”形截面的第一间隔物335的下表面。第三绝缘图案195可以接触位线结构325的下表面。

98.第一、第三和第五绝缘图案175、195和350中的每个可以包括氮化物,例如硅氮化物,或者氧化物。第二绝缘图案185和第四绝缘图案340中的每个可以包括氧化物,例如硅氧化物,或者氮化物。

99.第二盖图案410可以沿第一方向延伸以在垂直方向上与栅极结构160重叠,并且可以部分地覆盖在位线结构325的在第一方向上的侧壁上的间隔物结构的外侧壁。在示例实施方式中,多个第二盖图案410可以在第二方向上彼此间隔开。第二盖图案410可以包括氮化物,例如硅氮化物。

100.接触插塞结构可以包括在垂直方向上依次堆叠的下接触插塞405、第二和第三欧姆接触图案435和445、第二扩散阻挡层450和上接触插塞465。

101.下接触插塞405可以形成于在第一方向上相邻的位线结构325之间以及在第二方向上相邻的第二盖图案410之间在有源图案105和隔离图案110上的第三凹槽390上,并且可以接触间隔物结构的第三间隔物385的外侧壁和每个第二盖图案410的侧壁。因此,多个下接触插塞405可以形成为在第一方向和第二方向中的每个方向上彼此间隔开。在一示例实施方式中,下接触插塞405的最上表面可以低于空气间隔物365和第三间隔物385的最上表面。

102.下接触插塞405可以包括掺有杂质的多晶硅。可以在下接触插塞405中形成气隙(未示出)。

103.第二欧姆接触图案435可以形成在下接触插塞405上。第二欧姆接触图案435可以包括例如钴硅化物、镍硅化物等。

104.第三欧姆接触图案445可以形成在第二欧姆接触图案435上。第三欧姆接触图案445可以包括例如钛硅化物、钽硅化物、钨硅化物等。

105.第二扩散阻挡层450可以形成在第三欧姆接触图案445的上表面以及第四间隔物425的侧壁和上表面上。第二扩散阻挡层450可以包括例如钛氮化物、钽氮化物、钨氮化物等。

106.上接触插塞465可以形成在第二扩散阻挡层450上。上接触插塞465的上表面可以高于位线结构325和第二盖图案410的上表面。

107.在示例实施方式中,多个上接触插塞465可以形成在第一方向和第二方向中的每个方向上,并且可以通过依次堆叠的第一绝缘夹层480和第二绝缘夹层490彼此间隔开。第一绝缘夹层480可以部分地穿透位线结构325的第一盖图案315的上部和位线结构325的侧壁上的间隔物结构的上部。第一绝缘夹层480可以包括具有低间隙填充特性的绝缘材料。第二绝缘夹层490可以包括氮化物,例如硅氮化物。

108.在示例实施方式中,在平面图中,上接触插塞465可以布置成蜂巢图案。在平面图中,每个上接触插塞465可以具有圆形、椭圆形或多边形的形状。上接触插塞465可以包括低电阻金属,例如钨、铝、铜等。

109.电容器540可以包括依次堆叠在上接触插塞465上的下电极510、电介质层520和上电极530。下电极510和上电极530可以包括相同的材料,例如掺杂多晶硅和/或金属。电介质层520可以包括硅氧化物、金属氧化物和/或者诸如硅氮化物或金属氮化物的氮化物,其中金属可以包括例如铝、锆、钛、铪等。

110.蚀刻停止层500可以形成在电介质层520与第一和第二绝缘夹层480和490之间,并且可以包括氮化物,例如硅氮化物。

111.第三绝缘夹层550可以形成在第一绝缘夹层480和第二绝缘夹层490上,并且可以覆盖电容器540。第三绝缘夹层550可以包括氧化物,例如硅氧化物。

112.图11至图25是示出根据示例实施方式的制造半导体器件的方法的平面图和截面图。具体地,图11、图13、图16和图20是平面图,并且图12、图14-15、图17-19和图21-25中的每个包括沿相应平面图的线b-b'和c-c'截取的截面图。

113.本示例实施方式是将参照图2至图5和图1所示的形成布线结构的方法应用于制造动态随机存取存储器(dram)装置的方法,并且在这里省略对形成布线结构的方法的重复描述。

114.参照图11和图12,可以在衬底100上形成有源图案105。隔离图案110可以形成为覆盖有源图案105的侧壁。

115.可以对衬底100执行离子注入工艺以形成杂质区(未示出),并且可以部分地蚀刻有源图案105和隔离图案110以形成在第一方向上延伸的第一凹槽。

116.可以在第一凹槽中形成栅极结构160。栅极结构160可以包括在有源图案105的被第一凹槽暴露的表面上的栅极绝缘层130、在栅极绝缘层130上以填充第一凹槽的下部的栅电极140、以及在栅电极140上以填充第一凹槽的上部的栅极掩模150。栅极结构160可以在第一方向上延伸,并且多个栅极结构160可以在第二方向上彼此间隔开。

117.栅极绝缘层130可以通过对有源图案105的被第一凹槽暴露的表面执行热氧化工艺而形成。

118.参照图13和图14,可以在衬底100上依次形成绝缘层结构200、第三导电层210和第一掩模220。可以使用第一掩模220作为蚀刻掩模蚀刻第三导电层210和绝缘层结构200以形成暴露有源图案105的第一孔。第一孔可以对应于图1的第二凹槽230。

119.在示例实施方式中,绝缘层结构200可以包括依次堆叠的第一、第二和第三绝缘层170、180和190。第一绝缘层170和第三绝缘层190中的每个可以包括氧化物,例如硅氧化物,

或者氮化物,第二绝缘层180可以包括氮化物,例如硅氮化物,或者氧化物。

120.第三导电层210可以包括例如掺杂多晶硅。第一掩模220可以包括氮化物,例如硅氮化物。

121.在蚀刻工艺期间,通过第一孔暴露的有源图案105的上部和与其相邻的隔离图案110的上部以及栅极掩模150的上部也可以被蚀刻以形成第二孔。因此,第二孔的底部可以被称为第二凹槽230。

122.在示例实施方式中,第二孔可以暴露在第三方向上延伸的每个有源图案105的中心上表面。多个第二孔可以在第一方向和第二方向中的每个方向上形成。

123.可以形成第四导电层240以填充第二凹槽230。

124.在示例实施方式中,第四导电层240可以通过以下形成:在有源图案105、隔离图案110、栅极掩模150和第一掩模220上形成初步第四导电层以填充第二孔,然后通过例如cmp工艺和/或回蚀刻工艺去除初步第四导电层的上部。因此,第四导电层240可以具有与第三导电层210的上表面基本共面的上表面。

125.在示例实施方式中,多个第四导电层240可以在第一方向和第二方向中的每个方向上彼此间隔开。第四导电层240可以包括例如掺杂多晶硅,并且可以与第三导电层210合并。

126.参照图15,可以去除第一掩模220。然后,可以在第三导电层210和第四导电层240上依次形成第五导电层250、第一欧姆接触层270、第一防氧化层280、第一扩散阻挡层290、第六导电层300和第一覆盖层310。

127.在示例实施方式中,第五导电层250、第一欧姆接触层270、第一防氧化层280、第一扩散阻挡层290和第六导电层300可以通过相同的工艺形成为包括分别与结合图2至图5描述的第一导电层20、欧姆接触层40、防氧化层50、扩散阻挡层60和第二导电层70相同的材料。另外,第一覆盖层310可以包括与结合图1描述的掩模85的材料基本相同的材料。

128.因此,第五导电层250可以包括掺杂多晶硅,并且可以与第三导电层210和第四导电层240合并。

129.参照图16和图17,可以图案化第一覆盖层310以形成第一盖图案315。然后,可以使用第一盖图案315作为蚀刻掩模依次蚀刻第六导电层300、第一扩散阻挡层290、第一防氧化层280、第一欧姆接触层270、第五导电层250、第三和第四导电层210和240以及第三绝缘层190。

130.在示例实施方式中,第一盖图案315可以在衬底100上沿第二方向延伸,并且多个第一盖图案315可以形成为在第一方向上彼此间隔开。

131.通过蚀刻工艺,可以在第二凹槽230中在有源图案105、隔离图案110和栅极掩模150上形成依次堆叠的第四导电图案245、第五导电图案255、第一欧姆接触图案275、第一防氧化图案285、第一扩散阻挡物295、第六导电图案305。此外,第三绝缘图案195、第三导电图案215、第五导电图案255、第一欧姆接触图案275、第一防氧化图案285、第一扩散阻挡物295、第六导电图案305和第一盖图案315可以在第二凹槽230的外部依次堆叠在绝缘层结构200的第二绝缘层180上。

132.如上所述,第三至第五导电层210、240和250可以彼此合并,因此依次堆叠的第四和第五导电图案245和255以及依次堆叠的第三和第五导电图案215和255可以各自形成一

个导电结构265。在下文中,依次堆叠的导电结构265、第一欧姆接触图案275、第一防氧化图案285、第一扩散阻挡物295、第六导电图案305和第一盖图案315可以被称为位线结构325。

133.在示例实施方式中,位线结构325可以在衬底100上沿第二方向延伸,并且多个位线结构325可以在第一方向上彼此间隔开。每个位线结构325可以通过第二凹槽230接触每个有源图案105的在第三方向上的中心部分,从而可以与其电连接。

134.参照图18,可以在有源图案105、隔离图案110和栅极掩模150的通过第二凹槽230暴露的上表面、第二凹槽230的侧壁和第二绝缘层180上形成第一间隔物层以覆盖位线结构325。第四绝缘层和第五绝缘层可以依次形成在第一间隔物层上。

135.第一间隔物层还可以覆盖第二绝缘层180和位线结构325之间的第三绝缘图案195的侧壁。第五绝缘层可以填充第二凹槽230。

136.第四绝缘层和第五绝缘层可以通过蚀刻工艺被蚀刻。在示例实施方式中,蚀刻工艺可以通过湿蚀刻工艺执行,并且除了第二凹槽230中的部分之外,第四绝缘层和第五绝缘层的其它部分可以被去除。因此,第一间隔物层的整个表面的大部分(也就是,除了其在第二凹槽230中的部分之外的整个表面)可以暴露,并且第四绝缘层和第五绝缘层的保留在第二凹槽230中的部分可以分别形成第四绝缘图案340和第五绝缘图案350。

137.可以在第一间隔物层的暴露表面以及第二凹槽230中的第四绝缘图案340和第五绝缘图案350上形成第二间隔物层。可以各向异性地蚀刻第二间隔物层以在第一间隔物层的表面以及第四绝缘图案340和第五绝缘图案350上形成第二间隔层360以覆盖位线结构325的侧壁。

138.可以使用第一盖图案315和第二间隔物360作为蚀刻掩模来执行干蚀刻工艺以形成暴露有源图案105的上表面的第一开口370。隔离图案110的上表面和栅极掩模150的上表面也可以通过第一开口370暴露。

139.通过干蚀刻工艺,可以去除第一间隔物层的在第一盖图案315和第二绝缘层180的上表面上的部分,因此可以形成覆盖位线结构325的侧壁的第一间隔物335。另外,在干蚀刻工艺期间,第一绝缘层170和第二绝缘层180可以被部分地去除,使得第一绝缘图案175和第二绝缘图案185可以保留在位线结构325之下。依次堆叠在位线结构325下方的第一至第三绝缘图案175、185和195可以形成绝缘图案结构。

140.参照图19,可以在第一盖图案315的上表面、第二间隔物360的外侧壁、第四和第五绝缘图案340和350的上表面的部分、以及通过第一开口370暴露的有源图案105、隔离图案110和栅极掩模150的上表面上形成第三间隔物层。可以各向异性地蚀刻第三间隔物层以形成覆盖位线结构325的侧壁的第三间隔物385。

141.第三间隔物层可以包括氮化物,例如硅氮化物。

142.从位线结构325的侧壁在基本上平行于衬底100的上表面的第一方向上依次堆叠的第一至第三间隔物335、360和385可以被称为初步间隔物结构。

143.可以通过蚀刻工艺去除有源图案105的上部以形成连接到第一开口370的第三凹槽390。

144.可以在衬底100上形成下接触插塞层400以填充第一开口370和第三凹槽390。下接触插塞层400的上部可以被平坦化直到第一盖图案315的上表面暴露。

145.在示例实施方式中,下接触插塞层400可以沿第二方向延伸。多个下接触插塞层

400可以形成为通过位线结构325在第一方向上彼此间隔开。下接触插塞层400可以包括例如掺杂多晶硅。

146.参照图20和图21,可以在第一盖图案315和下接触插塞层400上形成包括第二开口(每个第二开口可以沿第一方向延伸,在第二方向上彼此间隔开)的第二掩模(未示出)。可以使用第二掩模作为蚀刻掩模来蚀刻下接触插塞层400。

147.在示例实施方式中,每个第二开口可以在基本垂直于衬底100的上表面的垂直方向上与栅极结构160重叠。通过蚀刻工艺,可以形成第三开口以暴露在衬底100上在位线结构325之间的栅极结构160的栅极掩模150的上表面。

148.在去除第二掩模之后,可以在衬底100上形成第二盖图案410以填充第三开口。第二盖图案410可以包括氮化物,例如硅氮化物。在示例实施方式中,第二盖图案410可以在位线结构325之间沿第一方向延伸。可以在第二方向上形成多个第二盖图案410。

149.因此,在位线结构325之间沿第二方向延伸的下接触插塞层400可以被分成多个下接触插塞405,所述多个下接触插塞405通过第二盖图案410在第二方向上彼此间隔开。每个下接触插塞405可以接触有源图案105中的对应一个的在第三方向上的相对端中的对应一个,并且可以与其电连接。

150.参照图22,可以去除下接触插塞405的上部以暴露在位线结构325的侧壁上的初步间隔物结构的上部。被暴露的初步间隔物结构的第二和第三间隔物360和385的上部可以被去除。

151.下接触插塞405的上部可以通过例如回蚀刻工艺被进一步去除。因此,下接触插塞405的上表面可以低于第二和第三间隔物360和385的最上表面。

152.可以在位线结构325、初步间隔物结构、第二盖图案410和下接触插塞405上形成第四间隔物层。可以各向异性地蚀刻第四间隔物层,使得第四间隔物425覆盖位线结构325的在第一方向上的相对侧壁中的每个上的第一至第三间隔物335、360、385,而下接触插塞405的上表面可以不被第四间隔物425覆盖而是可以暴露。

153.可以在下接触插塞405的被暴露的上表面上形成第二欧姆接触图案435。在示例实施方式中,第二欧姆接触图案435可以通过以下形成:在下接触插塞405、第四间隔物425、以及第一和第二盖图案315和410上形成金属层,热处理金属层,并去除金属层的未反应部分。第二欧姆接触图案435可以包括例如钴硅化物、镍硅化物等。

154.参照图23,例如,可以在第二欧姆接触图案435、第四间隔物425以及第一和第二盖图案315和410上形成第三欧姆接触层。可以在第三欧姆接触层的与第二欧姆接触图案435接触的部分上形成第三欧姆接触图案445。

155.在示例实施方式中,第三欧姆接触层可以包括例如钛,因此第三欧姆接触图案445可以包括钛硅化物。在另一实现方式中,第三欧姆接触层可以包括例如钽、钨等,因此第三欧姆接触图案445可以包括钽硅化物、钨硅化物等。

156.然后,可以在第三欧姆接触层和第三欧姆接触图案445上形成第二扩散阻挡层450。第二扩散阻挡层450可以包括例如钛氮化物。当形成第二扩散阻挡层450时,第二扩散阻挡层450下方的第三欧姆接触层可以被氮化为包括钛氮化物。因此,第三欧姆接触层可以与第二扩散阻挡层450合并。

157.参照图24,可以在第二扩散阻挡层450上形成上接触插塞层460。上接触插塞层460

的上部可以被平坦化。

158.在示例实施方式中,上接触插塞层460的上表面可以高于第一和第二盖图案315和410的上表面。

159.参照图25,可以去除上接触插塞层460的上部的一部分、第二扩散阻挡层450的一部分、第一盖图案315的上部的一部分以及第一、第三和第四间隔物335、385和425的上部的一部分以形成第二孔470。因此,第二间隔物360的上表面可以暴露。

160.因为第二孔470形成,上接触插塞层460可以转变为上接触插塞465。在示例实施方式中,多个上接触插塞465可以形成为在第一方向和第二方向中的每个方向上彼此间隔开,并且在平面图中可以布置成蜂巢图案。在平面图中,每个上接触插塞465可以具有圆形、椭圆形或多边形的形状。

161.依次堆叠在衬底100上的下接触插塞405、第二和第三欧姆接触图案435和445以及上接触插塞465可以形成接触插塞结构。

162.暴露的第二间隔物360可以被去除以形成连接到第二孔470的气隙365。气隙365也可以被称为空气间隔物365。第二间隔物360可以通过例如湿蚀刻工艺去除。

163.在示例实施方式中,可以去除在位线结构325的侧壁上通过第二孔470直接暴露的沿第二方向延伸的第二间隔物360的一部分,并且还可以去除第二间隔物360的在水平方向上平行于其被直接暴露的部分的其它部分。因此,不仅第二间隔物360的被第二孔470暴露而没有被上接触插塞465覆盖的部分,而且第二间隔物360的在第二方向上与暴露部分相邻而被第二盖图案410覆盖的部分以及第二间隔物360的在第二方向上与暴露部分相邻而被上接触插塞465覆盖的部分可以都被去除。

164.可以依次堆叠第一绝缘夹层480和第二绝缘夹层490以填充第二孔470。第一绝缘夹层480和第二绝缘夹层490也可以依次堆叠在第二盖图案410上。

165.第一绝缘夹层480可以包括具有低间隙填充特性的材料,因此第二孔470下方的气隙365可以不被填充。气隙365也可以被称为空气间隔物365,并且可以与第一、第三和第四间隔物335、385和425一起形成间隔物结构。气隙365可以是包括空气的间隔物。

166.再次参照图9和图10,电容器540可以形成为接触上接触插塞465的上表面。

167.例如,蚀刻停止层500和模具层(未示出)可以依次形成在上接触插塞465以及第一和第二绝缘夹层480和490上,并且被部分地蚀刻以形成部分地暴露上接触插塞465的上表面的第三孔。

168.可以在第三孔的侧壁、上接触插塞465的暴露的上表面和模具层上形成下电极层(未示出)。可以在下电极层上形成牺牲层(未示出)以填充第三孔。下电极层和牺牲层可以被平坦化直到模具层的上表面暴露以分隔下电极层。可以通过例如湿蚀刻工艺去除牺牲层和模具层。因此,可以在上接触插塞465的暴露的上表面上形成具有圆筒形形状的下电极510。在另一实现方式中,下电极510可以具有填充第三孔的柱形状。

169.可以在下电极510和蚀刻停止层500的表面上形成电介质层520。可以在电介质层520上形成上电极530,从而形成包括下电极510、电介质层520和上电极530的电容器540。

170.可以在衬底100上形成第三绝缘夹层550以覆盖电容器540从而完成半导体器件的制造。第三绝缘夹层550可以包括氧化物,例如硅氧化物。

171.图26是示出根据示例实施方式的半导体器件的截面图。除了位线结构之外,该半

导体器件可以与图9和图10的半导体器件基本相同或相似。

172.参照图26,位线结构325'可以包括依次堆叠的导电结构265、第一欧姆接触图案275、第一扩散阻挡物295、第二防氧化图案287、第六导电图案305和第一盖图案315。

173.第一欧姆接触图案275、第一扩散阻挡物295和第二防氧化图案287可以包括分别与以上结合图6描述的欧姆接触图案45、扩散阻挡物65和防氧化图案57的材料基本相同的材料。

174.图27是示出根据示例实施方式的半导体器件的截面图。除了接触插塞结构之外,该半导体器件可以与图9和图20或图26的半导体器件基本相同或相似。

175.参照图27,接触插塞结构可以包括依次堆叠的下接触插塞405、第二和第四欧姆接触图案435和605、第三防氧化图案615、第三和第四扩散阻挡层617和620、以及上接触插塞465。

176.第四欧姆接触图案605、第三防氧化图案615和第四扩散阻挡层620可以包括分别与以上结合图1描述的欧姆接触图案45、防氧化图案55和扩散阻挡物65的材料基本相同的材料。第三扩散阻挡层617可以包括与图6中所示的防氧化图案57的材料基本相同的材料。

177.在示例实施方式中,第四欧姆接触图案605可以形成在第二欧姆接触图案435上,第三防氧化图案615可以形成在第四欧姆接触图案605上,第三扩散阻挡层617可以形成在第四间隔物425上,第四扩散阻挡层620可以形成在第三防氧化图案615和第三扩散阻挡层617上以接触其上表面。因此,第三扩散阻挡层617可以接触第三防氧化图案615的在第一方向上的相对端中的每个的上表面和第四扩散阻挡层620的外侧壁。

178.图28是示出根据示例实施方式的制造半导体器件的方法的截面图。该方法可以包括与参照图11至图25、图9和图10或图26所示的工艺基本相同或相似的工艺,因此这里省略重复的说明。

179.参照图28,可以执行与参照图11至图22所示的工艺基本相同或相似的工艺,并且可以执行与参照图3至5所示的工艺基本相同或相似的工艺。

180.参照图28,可以形成第四欧姆接触层和第四欧姆接触图案层,然后可以使用氮化处理工艺将它们分别转变为第三扩散阻挡层617和第三防氧化图案615。

181.例如,第四欧姆接触层可以形成在第二欧姆接触图案435、第四间隔物425以及第一和第二盖图案315和410上。第四欧姆接触图案层可以形成在第四欧姆接触层与第二欧姆接触图案435之间。

182.在示例实施方式中,第四欧姆接触层可以包括钛,因此第四欧姆接触图案层可以包括钛硅化物。在另一实现方式中,第四欧姆接触层可以包括钽、钨等,因此第四欧姆接触图案层可以包括钽硅化物、钨硅化物等。

183.可以对第四欧姆接触层和第四欧姆接触图案层执行氮化处理工艺,因此第四欧姆接触图案层的上部可以转变为第三防氧化图案615,其下部可以成为第四欧姆接触图案605,并且第四欧姆接触层可以转变为第三扩散阻挡层617。第三防氧化图案615可以包括例如钨硅氮化物、钽硅氮化物、钛硅氮化物等。第三扩散阻挡层617可以包括例如钛氮化物、钽氮化物、钨氮化物等。

184.第四扩散阻挡层620可以形成在第三防氧化图案615和第三扩散阻挡层617上。第四扩散阻挡层620可以包括石墨烯。

185.可以执行与参照图24以及图9和图10所示的那些基本相同或相似的工艺以完成半导体器件的制造。

186.图29是示出根据示例实施方式的半导体器件的截面图。除了接触插塞结构之外,该半导体器件可以与图27的半导体器件基本相同或相似。

187.参照图29,接触插塞结构可以包括依次堆叠的下接触插塞405、第二和第四欧姆接触图案435和605、第三和第四扩散阻挡层617和620以及上接触插塞465。

188.在示例实施方式中,第四欧姆接触图案605可以形成在第二欧姆接触图案435上。第四扩散阻挡层620可以形成在第四欧姆接触图案605和第四间隔物425上。第三扩散阻挡层617可以形成在第四扩散阻挡层620上。

189.在一些实施方式中,半导体器件可以包括图26所示的位线结构325'和图27或图29所示的接触插塞结构。

190.如上所述,实施方式可以提供具有改进特性的布线结构。实施方式还可以提供形成具有改进特性的布线结构的方法。实施方式还可以提供具有改进特性的半导体器件。

191.实施方式可以提供具有减小的厚度和减小的电阻的布线结构。此外,可以减少布线结构中图案之间的扩散。

192.这里已经公开了示例实施方式,并且虽然使用了特定术语,但是它们被使用并且仅以一般和描述性的意义来解释,而不是为了限制的目的。在一些情况下,对于在提交本技术时的本领域普通技术人员将明显的是,结合特定实施方式描述的特征、特性和/或元件可以单独使用或与结合其它实施方式描述的特征、特性和/或元件组合使用,除非另外特别指明。因此,本领域技术人员将理解,在不脱离如权利要求中阐述的本发明的精神和范围的情况下,可以在形式和细节上进行各种改变。

193.于2020年9月14日向韩国知识产权局提交的名称为“wiring structures,methods of forming the same,and semiconductor devices including the same(布线结构、形成其的方法以及包括其的半导体器件)”的韩国专利申请第10-2020-0117704号通过引用整体合并于此。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。