1.本公开总体上可涉及半导体存储器装置和制造该半导体存储器装置的方法,更具体地,涉及三维半导体存储器装置和制造该三维半导体存储器装置的方法。

背景技术:

2.半导体存储器装置包括能够存储数据的多个存储器单元。三维半导体存储器装置可以包括三维布置的存储器单元。存储器单元可以构成多个单元存储器串。存储器单元串可以连接到字线和选择线。选择线可以包括源极选择线和漏极选择线。

技术实现要素:

3.根据本公开的一个实施方式的半导体存储器装置可以包括:栅极叠层,其包括在第一方向上交替层叠的层间绝缘层和字线;沟道柱,其穿过栅极叠层并且朝向第一方向逐渐变窄;源极选择线,其围绕沟道柱并且延伸以与栅极叠层交叠;以及源极隔离绝缘层,其在源极选择线之间与栅极叠层交叠,并且朝向与第一方向相反的方向逐渐变窄。

4.根据本公开的一个实施方式的制造半导体存储器装置的方法可以包括以下步骤:形成包括沟道柱、层间绝缘层和导电图案的初步结构,沟道柱中的每一个朝着面向第一方向的第一端逐渐变窄,层间绝缘层和导电图案围绕沟道柱并且在第一方向上交替层叠;形成穿过导电图案中的第一导电图案并且朝向与第一方向相反的方向逐渐变窄的沟槽;以及形成填充沟槽的源极隔离绝缘层。

附图说明

5.图1是示出根据本公开的一个实施方式的半导体存储器装置的存储器块的电路图。

6.图2示出根据本公开的一个实施方式的半导体存储器装置的栅极叠层、沟道柱和位线的布局图。

7.图3a是沿着图2所示的线a-a’截取的半导体存储器装置的截面图,并且图3b是图3a所示的区域r1的放大截面图。

8.图4a是根据本公开的一个实施方式的半导体存储器装置的截面图,并且图4b是图4a所示的区域r2的放大截面图。

9.图5是根据本公开的一个实施方式的半导体存储器装置的源极选择线的放大截面图。

10.图6a是根据本公开的一个实施方式的半导体存储器装置的截面图,并且图6b是图6a所示的区域r3的放大截面图。

11.图7a至图7h是示出根据本公开的一个实施方式的制造半导体存储器装置的方法的截面图。

12.图8a至图8d是示出在图7h所示的工艺之后的后续工艺的放大截面图。

13.图9a至图9c是示出根据本公开的一个实施方式的制造半导体存储器装置的方法的截面图。

14.图10a至图10c是示出在图9c所示的工艺之后的后续工艺的放大截面图。

15.图11a至图11d是示出根据本公开的一个实施方式的制造半导体存储器装置的方法的放大截面图。

16.图12a至图12d是示出根据本公开的一个实施方式的制造半导体存储器装置的方法的截面图。

17.图13a和图13b是示出在图12d所示的工艺之后的后续工艺的放大截面图。

18.图14是示出根据本公开的一个实施方式的存储器系统的配置的框图。

19.图15是示出根据本公开的一个实施方式的计算系统的配置的框图。

具体实施方式

20.本文公开的特定结构描述或功能描述仅仅是出于描述根据本公开的构思的实施方式的目的而示出的。根据本公开的构思的实施方式可以以各种形式实现,并且它们不应被解释为限于本文阐述的特定实施方式。

21.在下文中,术语“第一”和“第二”用于区分一个组件和另一组件,而并不意图暗示组件的特定数量或顺序。这些术语可以用来描述各种组件,但这些组件不受这些术语的限制。

22.本公开的一个实施方式可以提供一种半导体存储器装置和制造该半导体存储器装置的方法,该半导体存储器装置能够改善将源极选择线彼此分开的源极隔离绝缘层的对准余量。

23.图1是示出根据本公开的一个实施方式的半导体存储器装置的存储器块blk的电路图。

24.参照图1,半导体存储器装置可以包括多个存储器块blk。每个存储器块blk可以包括连接到公共源极层csl和位线bl的多个存储器单元串ms1、ms2和ms3。

25.存储器单元串ms1、ms2和ms3中的每一个可以包括串联连接的多个存储器单元mc、至少一个源极选择晶体管sst和至少一个漏极选择晶体管dst。在一个实施方式中,存储器单元串ms1、ms2和ms3中的每一个可以包括连接在多个存储器单元mc和公共源极层csl之间的一个源极选择晶体管sst。在一个实施方式中,存储器单元串ms1、ms2和ms3中的每一个可以包括串联连接在多个存储器单元mc和公共源极层csl之间的两个或更多个源极选择晶体管sst。在一个实施方式中,存储器单元串ms1、ms2和ms3中的每一个可以包括连接在多个存储器单元mc和位线bl之间的一个漏极选择晶体管dst。在一个实施方式中,存储器单元串ms1、ms2和ms3中的每一个可以包括串联连接在多个存储器单元mc和位线bl之间的两个或更多个漏极选择晶体管dst。

26.多个存储器单元mc可以经由源极选择晶体管sst连接到公共源极层csl。多个存储器单元mc可以经由漏极选择晶体管dst连接到位线bl。

27.设置在相同水平的源极选择晶体管sst的栅极可以连接到彼此分离的源极选择线ssl1、ssl2和ssl3。设置在相同水平的漏极选择晶体管dst的栅极可以连接到彼此分离的漏极选择线dsl1、dsl2和dsl3。多个存储器单元mc的栅极可以连接到多条字线wl。字线wl可以

设置在不同的水平,并且设置在相同水平的存储器单元mc的栅极可以连接到单条字线wl。

28.在下文中,基于存储器块blk包括在相同水平处彼此分离的第一源极选择线ssl1、第二源极选择线ssl2和第三源极选择线ssl3,并且包括在相同水平处彼此分离的第一漏极选择线dsl1、第二漏极选择线dsl2和第三漏极选择线dsl3的实施方式来描述本公开。本公开的实施方式不限于此,并且存储器块blk可以包括在相同水平处彼此分离的两条源极选择线,或者可以包括在相同水平处彼此分离的四条或更多条源极选择线。类似地,存储器块blk可以包括在相同水平处彼此分离的两条漏极选择线,或者可以包括在相同水平处彼此分离的四条或更多条漏极选择线。

29.多个存储器单元串ms1、ms2和ms3可以连接到字线wl中的每一条。多个存储器单元串ms1、ms2和ms3可以包括可由第一源极选择线ssl1、第二源极选择线ssl2和第三源极选择线ssl3单独选择的第一组、第二组和第三组。第一组可以包括第一存储器单元串ms1,第二组可以包括第二存储器单元串ms2,并且第三组可以包括第三存储器单元串ms3。

30.第一存储器单元串ms1可以分别经由连接到第一漏极选择线dsl1的漏极选择晶体管dst连接到位线bl。第二存储器单元串ms2可以分别经由连接到第二漏极选择线dsl2的漏极选择晶体管dst连接到位线bl。第三存储器单元串ms3可以分别经由连接到第三漏极选择线dsl3的漏极选择晶体管dst连接到位线bl。第一存储器单元串ms1中的一个、第二存储器单元串ms2中的一个和第三存储器单元串ms3中的一个可以连接到单条位线bl。

31.第一存储器单元串ms1可以在连接到第一源极选择线ssl1的源极选择晶体管sst的控制下连接到公共源极层csl。第二存储器单元串ms2可以在连接到第二源极选择线ssl2的源极选择晶体管sst的控制下连接到公共源极层csl,并且第三存储器单元串ms3可以在连接到第三源极选择线ssl3的源极选择晶体管sst的控制下连接到公共源极层csl。因此,在读取操作或验证操作期间,对于源极选择线ssl1、ssl2和ssl3中的每一条,可以将多个存储器单元串ms1、ms2和ms3划分成可同时单独选择的组。在一个实施方式中,在读取操作或验证操作期间,第一存储器单元串ms1的第一组、第二存储器单元串ms2的第二组和第三存储器单元串ms3的第三组中的一者可以通过选择第一源极选择线ssl1、第二源极选择线ssl2和第三源极选择线ssl3中的一条而连接到公共源极层csl。因此,与第一存储器单元串ms1、第二存储器单元串ms2和第三存储器单元串ms3在读取操作或验证操作期间同时连接到公共源极层csl的情况相比,本公开的实施方式可以减小沟道电阻。因此,本公开的实施方式可以减少读取干扰。

32.图2示出根据本公开的一个实施方式的半导体存储器装置的栅极叠层g1、g2和g3、沟道柱ch和位线bl的布局图。

33.参照图2,栅极叠层g1、g2和g3可以通过栅极隔离绝缘层sg彼此分开。栅极叠层g1、g2和g3可以围绕在第一方向d1上延伸的沟道柱ch。

34.沟道柱ch可以按照在与沟道柱ch交叉的平面中的沿第二方向d2布置的多个行以及在与沟道柱ch交叉的平面中的沿第三方向d3布置的多个列来设置。在一个实施方式中,分别穿过栅极叠层g1、g2和g3的多个沟道柱ch可以包括布置成在第二方向d2上彼此间隔开的第一沟道柱ch1、第二沟道柱ch2和第三沟道柱ch3。

35.栅极叠层g1、g2和g3中的每一个可以包括字线wl和漏极选择线dsl1、dsl2和dsl3。

36.在一个实施方式中,栅极叠层g1、g2和g3中的每一个可以包括围绕第一沟道柱ch1

的第一漏极选择线dsl1、围绕第二沟道柱ch2的第二漏极选择线dsl2和围绕第三沟道柱ch3的第三漏极选择线dsl3。第一漏极选择线dsl1、第二漏极选择线dsl2和第三漏极选择线dsl3可以通过漏极隔离绝缘层sd在第二方向d2上彼此间隔开。第一漏极选择线dsl1、第二漏极选择线dsl2、第三漏极选择线dsl3和漏极隔离绝缘层sd可以在第三方向d3上延伸。漏极隔离绝缘层sd的形状可以是各种各样的,诸如波形或直线形。

37.字线wl可以与漏极选择线dsl1、dsl2和dsl3交叠。字线wl中的每一条可以在第二方向d2上延伸,以围绕第一沟道柱ch1、第二沟道柱ch2和第三沟道柱ch3。字线wl中的每一条可以与漏极隔离绝缘层sd交叠。

38.字线wl中的每一条可以被虚设沟道柱dch贯穿。虚设沟道柱dch可以与漏极隔离绝缘层sd交叠。虚设沟道柱dch可以在漏极隔离绝缘层sd的延伸方向上布置成一行。尽管图中未示出,但是可以省略虚设沟道柱dch。

39.位线bl可以在与漏极选择线dsl1、dsl2和dsl3交叉的方向上延伸。在一个实施方式中,位线bl可以在第二方向d2上延伸。位线bl可以通过接触插塞ct连接到沟道柱ch。位线bl中的每一条可以共同连接到可由不同的漏极选择线dsl1、dsl2和dsl3控制的沟道柱。在一个实施方式中,位线bl中的每一条可以共同连接到可由第一漏极选择线dsl1控制的第一沟道柱ch1、可由第二漏极选择线dsl2控制的第二沟道柱ch2和可由第三漏极选择线dsl3控制的第三沟道柱ch3。

40.图3a是沿着图2所示的线a-a’截取的半导体存储器装置的截面图,并且图3b是图3a所示的区域r1的放大截面图。

41.图2所示的线a-a’与第一沟道柱ch1和第二沟道柱ch2之间的虚设沟道柱dch交叠,但是不与第二沟道柱ch2和第三沟道柱ch3之间的虚设沟道柱dch交叠。

42.参照图3a,半导体存储器装置可以包括与位线bl交叠的公共源极层csl。栅极叠层g1和g2可以设置在公共源极层csl和位线bl之间。半导体存储器装置可以包括外围电路结构50。位线bl可以设置在栅极叠层g1和g2与外围电路结构50之间。半导体存储器装置可以包括与栅极叠层g1和g2中的每一个交叠的源极选择线ssl1、ssl2和ssl3。源极选择线ssl1、ssl2和ssl3可以设置在栅极叠层g1和g2中的每一个与公共源极层csl之间。

43.沟道柱ch可以在第一方向d1上延伸以穿过栅极叠层g1和g2以及源极选择线ssl1、ssl2和ssl3。沟道柱ch可以延伸到公共源极层csl中。沟道柱ch中的每一个可以包括沟道层cl、芯绝缘层co和封盖图案cap。芯绝缘层co和封盖图案cap可以设置在沟道柱ch的中心区域中。芯绝缘层co可以与封盖图案cap交叠。封盖图案cap可以包括掺杂半导体层。在一个实施方式中,封盖图案cap可以包括含有n型杂质的掺杂硅。沟道层cl可以围绕封盖图案cap的侧壁和芯绝缘层co的侧壁。沟道层cl可以延伸到芯绝缘层co的面向公共源极层csl的表面上。沟道层cl可以构成存储器单元串的沟道区域。沟道层cl可以包括半导体层。在一个实施方式中,沟道层cl可以包括硅。

44.公共源极层csl可以包括在第一方向d1上层叠的掺杂半导体层181和金属层185。公共源极层csl还可以包括第一金属阻挡层183。掺杂半导体层181可以包括n型杂质和p型杂质中的至少一种。在一个实施方式中,掺杂半导体层181可以包括掺杂有n型杂质的硅。公共源极层csl可以通过第一绝缘层11与源极选择线ssl1、ssl2和ssl3绝缘。第一绝缘层11可以在公共源极层csl与源极选择线ssl1、ssl2和ssl3中的每一条之间延伸。

45.沟道柱ch可以延伸到公共源极层csl的掺杂半导体层181中。沟道柱ch的沟道层cl可以与公共源极层csl的掺杂半导体层181接触。

46.源极选择线ssl1、ssl2和ssl3可以通过源极隔离绝缘层ss彼此分开。换句话说,源极隔离绝缘层ss可以设置在源极选择线ssl1、ssl2和ssl3之间。源极隔离绝缘层ss可以与漏极隔离绝缘层sd交叠。源极隔离绝缘层ss可以平行于漏极隔离绝缘层sd延伸。在一个实施方式中,源极隔离绝缘层ss可以在第三方向d3上延伸。源极隔离绝缘层ss可以在第一方向d1上延伸以穿过第一绝缘层11。

47.源极隔离绝缘层ss可以具有与沟道柱ch中的每一个的锥形形状相反的锥形形状。沟道柱ch中的每一个可以具有朝向第一方向d1逐渐变窄的锥形形状。因此,可以将沟道柱ch的在第一方向上延伸超出栅极叠层g1的突起之间的距离限定为大于沟道柱ch的设置在栅极叠层g1内部的部分之间的距离。因此,根据本公开的一个实施方式,可以增加在沟道柱ch的突起之间的对准源极隔离绝缘层ss的余量空间。

48.源极隔离绝缘层ss可以具有朝向与第一方向d1相反的方向逐渐变窄的锥形形状。因此,源极隔离绝缘层ss的面向公共源极层csl的上端的宽度可以形成为比源极隔离绝缘层ss的面向栅极叠层g1的下端的宽度更宽。

49.因为沟道柱ch可以具有朝向第一方向d1逐渐变窄的锥形形状,所以沟道柱ch之间的空间可以随着沟道柱ch接近公共源极层csl而变得更宽。因此,其中设置有源极隔离绝缘层ss的上端的沟道柱ch之间的空间可以被限定为比其中设置有源极隔离绝缘层ss的下端的沟道柱ch之间的空间更宽。结果,可以在沟道柱ch之间增大用于对准源极隔离绝缘层ss的具有较宽宽度的上端的余量空间。因此,根据本公开的一个实施方式,可以提高源极隔离绝缘层ss的对准余量。

50.栅极叠层g1和g2中的每一个可以包括在第一方向d1上交替层叠的层间绝缘层21和导电图案23。栅极叠层g1和g2中的每一个可以围绕沟道柱ch并且存储器图案ml介于沟道柱ch与栅极叠层g1和g2中的每一个之间。存储器图案ml可以沿着沟道柱ch的侧壁延伸。存储器图案ml可以在源极选择线ssl1、ssl2和ssl3中的每一个与沟道柱ch之间延伸。

51.导电图案23可以包括相同的导电材料。每个导电图案23可以围绕沟道柱ch并且第一阻挡绝缘层25介于沟道柱ch和每个导电图案23之间。第一阻挡绝缘层25可以设置在每个导电图案23与存储器图案ml之间。第一阻挡绝缘层25可以在导电图案23中的每一个和层间绝缘层21之间延伸。

52.导电图案23可以用作字线wl以及漏极选择线dsl1、dsl2和dsl3。导电图案23中的与位线bl相邻的至少一层可以用作漏极选择线dsl1、dsl2和dsl3,并且剩余的层可以用作字线wl。在一个实施方式中,漏极选择线dsl1、dsl2和dsl3可以包括由与位线bl相邻的第一水平的导电图案23a和第二水平的导电图案23b构成的两层的第一漏极选择线dsl1至第三漏极选择线dsl3。漏极选择线dsl1、dsl2和dsl3可以通过漏极隔离绝缘层sd在相同水平处彼此间隔开。漏极隔离绝缘层sd可以具有朝向第一方向d1逐渐变窄的锥形形状。

53.源极选择线ssl1、ssl2和ssl3可以与漏极选择线dsl1、dsl2和dsl3交叠并且字线wl介于源极选择线ssl1、ssl2和ssl3与漏极选择线dsl1、dsl2和dsl3之间。在一个实施方式中,源极选择线ssl1、ssl2和ssl3可以包括分别平行于第一漏极选择线dsl1、第二漏极选择线dsl2和第三漏极选择线dsl3延伸的第一源极选择线ssl1、第二源极选择线ssl2和第三源

极选择线ssl3。第一源极选择线ssl1可以围绕第一沟道柱ch1,第二源极选择线ssl2可以围绕第二沟道柱ch2,并且第三源极选择线ssl3可以围绕第三沟道柱ch3。

54.字线wl可以被虚设沟道柱dch贯穿。虚设沟道柱dch可以设置在源极隔离绝缘层ss和漏极隔离绝缘层sd之间。虚设沟道柱dch的侧壁可以被虚设存储器图案dml围绕。虚设沟道柱dch可以包括虚设芯绝缘层dco和虚设沟道层dcl。虚设芯绝缘层dco可以设置在虚设沟道柱dch的中心区域中,并且虚设沟道层dcl可以设置在虚设芯绝缘层dco和虚设存储器图案dml之间。

55.源极选择线ssl1、ssl2和ssl3的导电材料可以是各种各样的。半导体存储器装置的制造工艺可以包括使用各种蚀刻材料执行的多个蚀刻工艺。源极选择线ssl1、ssl2和ssl3可以包括对一些蚀刻材料具有抗蚀刻性的材料。在一个实施方式中,源极选择线ssl1、ssl2和ssl3中的每一个可以包括硅。

56.接触插塞ct可以穿过设置在位线bl和沟道柱ch之间的至少一个绝缘层。在一个实施方式中,第二绝缘层133和第三绝缘层165可以设置在栅极叠层g1和g2中的每一个与位线bl之间。接触插塞ct可以与封盖图案cap接触,并且可以朝向位线bl延伸以穿过第二绝缘层133和第三绝缘层165。

57.半导体存储器装置可以包括第一绝缘结构171、第一互连结构173和第一接合金属图案175。

58.第一绝缘结构171可以设置在外围电路结构50和位线bl之间。第一绝缘结构171可以包括两层或更多层的绝缘层。第一互连结构173和第一接合金属图案175可以埋入第一绝缘结构171中。第一互连结构173可以包括各种形状的导电图案。第一互连结构173可以设置在位线bl和第一接合金属图案175之间。位线bl可以经由第一互连结构173电连接到第一接合金属图案175。第一接合金属图案175可以面向外围电路结构50。

59.外围电路结构50可以包括具有晶体管tr的基板101、第二绝缘结构121、第二互连结构123和第二接合金属图案125。

60.晶体管tr可以设置在基板101的由元件隔离层103分隔的有源区中。每个晶体管tr可以包括设置在有源区上的栅极绝缘层、设置在栅极绝缘层113上的栅极115以及形成在栅极绝缘层113两侧的有源区中的结111a和111b。一些晶体管tr可以构成控制位线bl的预充电操作和放电操作的页缓冲电路pb。页缓冲电路pb可以经由第二互连结构123和第一互连结构173连接到位线bl。

61.第二绝缘结构121可以设置在第一绝缘结构171和基板101之间。第二绝缘结构121可以包括两层或更多层的绝缘层。第二绝缘结构121可以接合到第一绝缘结构171。第二互连结构123和第二接合金属图案125可以埋入第二绝缘结构121中。第二互连结构123可以包括各种形状的导电图案。第二互连结构123可以设置在晶体管tr和第二接合金属图案125之间。页缓冲电路pb的晶体管tr可以经由第二互连结构123电连接到第二接合金属图案125。第二接合金属图案125可以面向第一接合金属图案175,并且可以接合到第一接合金属图案175。

62.参照图3b,导电图案23可以包括金属层mt和第二金属阻挡层bm。

63.沟道柱ch可以超出存储器图案ml而突出到公共源极层的掺杂半导体层181中。沟道柱ch的沟道层cl可以在掺杂半导体层181和芯绝缘层co之间延伸。

64.存储器图案ml可以设置在源极选择线ssl2或ssl3与沟道柱ch之间。存储器图案ml可以在沟道柱ch与层间绝缘层21、导电图案23和第一绝缘层11中的每一个之间延伸。存储器图案ml可以包括隧穿绝缘层ti、沿着隧穿绝缘层ti的外壁延伸的数据存储层dl以及沿着数据存储层dl的外壁延伸的第二阻挡绝缘层bi。数据存储层dl可以由能够存储数据的材料层形成。在一个实施方式中,数据存储层dl可以由能够存储使用福勒-诺德海姆(fowler nordheim)隧穿效应而改变的数据的材料层形成。材料层可以包括能够捕获电荷的氮化物层。第二阻挡绝缘层bi可以包括能够阻挡电荷的氧化物层。隧穿绝缘层ti可以由能够进行电荷隧穿的氧化硅层形成。

65.第一阻挡绝缘层25可以包括介电常数高于第二阻挡绝缘层bi的介电常数的材料层。在一个实施方式中,第一阻挡绝缘层25可以包括氧化铝层。可以省略第一阻挡绝缘层25和第二阻挡绝缘层bi中的一个。

66.源极隔离绝缘层ss可以包括面向层间绝缘层21的底表面和面向掺杂半导体层181的上表面。根据本公开的一个实施方式,通过锥形形状,源极隔离绝缘层ss的底表面宽度w11可以比源极隔离绝缘层ss的上表面宽度w12窄。

67.图4a是根据本公开的一个实施方式的半导体存储器装置的截面图,并且图4b是图4a所示的区域r2的放大截面图。

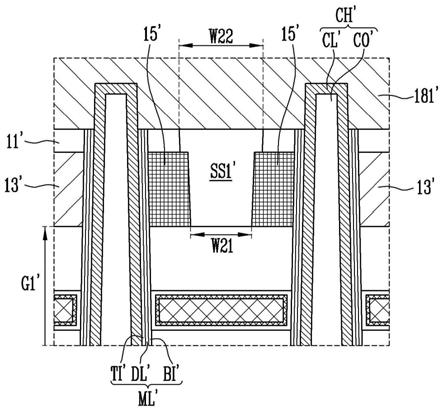

68.参照图4a,半导体存储器装置可以包括与图2和图3a所示的位线bl、公共源极层csl、栅极叠层g1和g2、漏极隔离绝缘层sd以及接触插塞ct结构相同的位线bl’、公共源极层csl’、栅极叠层g1’和g2’、漏极隔离绝缘层sd’以及接触插塞ct’。如参照图3a所述的,栅极叠层g1’和g2’中的每一个可以被沟道柱ch’和虚设沟道柱dch’贯穿。沟道柱ch’和虚设沟道柱dch’可以在第一方向d1上延伸。沟道柱ch’的侧壁可以被存储器图案ml’围绕,并且虚设沟道柱dch’的侧壁可以被虚设存储器图案dml’围绕。

69.此外,半导体存储器装置可以包括与图3a所示的外围电路结构50、第一互连结构173和第一接合金属图案175结构相同的外围电路结构50’、第一互连结构173’和第一接合金属图案175’。此外,半导体存储器装置可以包括设置在栅极叠层g1’和g2’与公共源极层csl’之间的源极选择线ssl1’、ssl2’和ssl3’。

70.源极选择线ssl1’、ssl2’和ssl3’中的每一条可以在与沟道柱ch’交叉的平面中在第二方向d2和第三方向d3上延伸。源极选择线ssl1’、ssl2’和ssl3’可以布置成在第二方向d2上彼此间隔开。源极选择线ssl1’、ssl2’和ssl3’可以通过第一绝缘层11’与公共源极层csl’绝缘。

71.源极选择线ssl1’、ssl2’和ssl3’可以通过第一源极隔离绝缘层ss1’和第二源极隔离绝缘层ss2’彼此分开。第一源极隔离绝缘层ss1’和第二源极隔离绝缘层ss2’中的每一个可以包括设置在源极选择线ssl1’、ssl2’和ssl3’之间的第一部分和穿过第一绝缘层11’的第二部分。第一源极隔离绝缘层ss1’和第二源极隔离绝缘层ss2’中的每一个的第一部分可以形成为锥形形状。第一源极隔离绝缘层ss1’和第二源极隔离绝缘层ss2’中的每一个的锥形形状可以如参照图3a所述的是沟道柱ch’的锥形形状的相反形状。因此,如参照图3a所述,本公开的实施方式可以提高第一源极隔离绝缘层ss1’和第二源极隔离绝缘层ss2’的对准余量。

72.第一源极隔离绝缘层ss1’可以与栅极叠层g1’交叠。第一源极隔离绝缘层ss1’可

以平行于漏极隔离绝缘层sd’延伸。在一个实施方式中,第一源极隔离绝缘层ss1’和漏极隔离绝缘层sd’可以在第三方向d3上延伸。

73.第二源极隔离绝缘层ss2’可以与栅极隔离绝缘层sg’交叠。第二源极隔离绝缘层ss2’可以平行于栅极隔离绝缘层sg’延伸。在一个实施方式中,第二源极隔离绝缘层ss2’和栅极隔离绝缘层sg’可以在第三方向d3上延伸。

74.源极选择线ssl1’、ssl2’和ssl3’可以与栅极叠层g1’的漏极选择线dsl1’、dsl2’和dsl3’交叠。在一个实施方式中,源极选择线ssl1’、ssl2’和ssl3’中的每一条可以包括硅层13’和金属硅化物层15’。参照图4a,硅层13’可以在半导体存储器装置的制造工艺中用作蚀刻停止层。金属硅化物层15’可以设置在第一源极隔离绝缘层ss1’和第二源极隔离绝缘层ss2’中的每一个与硅层13’之间。金属硅化物层15’可以与硅层13’接触。金属硅化物层15’可以减小源极选择线ssl1’、ssl2’和ssl3’的电阻。

75.第二绝缘层133’和第三绝缘层165’可以以与图3a所示的第二绝缘层133和第三绝缘层165相同的结构形成。

76.参照图4b,如参照图3b所述的,沟道柱ch’可以超出存储器图案ml’而突出到公共源极层的掺杂半导体层181’中。沟道柱ch’的沟道层cl’和芯绝缘层co’可以延伸到掺杂半导体层181’中。

77.如参照图3b所述的,存储器图案ml’可以包括隧穿绝缘层ti’、数据存储层dl’和阻挡绝缘层bi’。

78.第一源极隔离绝缘层ss1’可以包括面向栅极叠层g1’的底表面和面向掺杂半导体层181’的上表面。根据本公开的一个实施方式,通过锥形形状,第一源极隔离绝缘层ss1’的底表面宽度w21可以比第一源极隔离绝缘层ss1’的上表面宽度w22’窄。

79.图5是根据本公开的一个实施方式的半导体存储器装置的源极选择线ssl的放大截面图。

80.参照图5,栅极叠层g1’、第一绝缘层11’、存储器图案ml’、隧穿绝缘层ti’、数据存储层dl’、阻挡绝缘层bi’、沟道柱ch’、芯绝缘层co’、沟道层cl’和公共源极层的掺杂半导体层181’可以以参照图4a和图4b描述的结构形成。

81.源极选择线ssl可以通过与栅极叠层g1’交叠的源极隔离绝缘层ss1”彼此分开。源极选择线ssl中的每一条可以包括硅层13a和侧壁导电图案20。如参照图4a所述,硅层13a可以在半导体存储器装置的制造工艺中用作蚀刻停止层。侧壁导电图案20可以设置在源极隔离绝缘层ss1”和硅层13a之间。侧壁导电图案20可以包括与硅层13a接触的金属阻挡层17以及设置在金属阻挡层17和源极隔离绝缘层ss1”之间的金属层19。金属层19可以减小源极选择线ssl的电阻。金属阻挡层17可以在金属层19和第一绝缘层11’之间延伸。金属阻挡层17可以在金属层19和栅极叠层g1’之间延伸。

82.图6a是根据本公开的一个实施方式的半导体存储器装置的截面图,并且图6b是图6a所示的区域r3的放大截面图。

83.参照图6a,半导体存储器装置可以包括与图2和图3a所示的位线bl、公共源极层csl、栅极叠层g1和g2、漏极隔离绝缘层sd以及接触插塞ct结构相同的位线bl”、公共源极层csl”、栅极叠层g1”和g2”、漏极隔离绝缘层sd”和接触插塞ct”。如参照图3a所述的,栅极叠层g1”和g2”中的每一个可以被沟道柱ch1”和虚设沟道柱dch”贯穿。沟道柱ch1”的侧壁可以

被存储器图案ml”围绕,并且虚设沟道柱dch”的侧壁可以被虚设存储器图案dml”围绕。

84.此外,半导体存储器装置可以包括与图3a所示的外围电路结构50、第一互连结构173和第一接合金属图案175结构相同的外围电路结构50”、第一互连结构173”和第一接合金属图案175”。此外,半导体存储器装置可以包括设置在栅极叠层g1”和g2”与公共源极层csl”之间的源极选择线ssl1”、ssl2”和ssl3”。

85.源极选择线ssl1”、ssl2”和ssl3”中的每一条可以在与作为沟道柱ch”的延伸方向的第一方向d1交叉的平面中在第二方向d2和第三方向d3上延伸。源极选择线ssl1”、ssl2”和ssl3”可以包括与栅极叠层g1”的字线wl”相同的导电材料。源极选择线ssl1”、ssl2”和ssl3”可以与漏极选择线dsl1”、dsl2”和dsl3”交叠。源极选择线ssl1”、ssl2”和ssl3”可以设置在沿第一方向d1彼此间隔开的两层或更多层上。

86.在一个实施方式中,源极选择线ssl1”、ssl2”和ssl3”可以由设置在字线wl”和第一绝缘层11”之间的选择叠层30形成。选择叠层30可以包括第一导电图案31a、层间绝缘层33和第二导电图案31b。第一导电图案31a可以设置在层间绝缘层33和第一绝缘层11”之间,并且第二导电图案31b可以设置在层间绝缘层33和栅极叠层g1”之间。

87.选择叠层30可以被源极隔离绝缘层ss”和栅极隔离绝缘层sg”贯穿。第一导电图案31a和第二导电图案31b中的每一个可以被源极隔离绝缘层ss”分离成源极选择线ssl1”、ssl2”和ssl3”。在一个实施方式中,源极选择线ssl1”、ssl2”和ssl3”可以包括两层的第一源极选择线ssl1”、两层的第二源极选择线ssl2”和两层的第三源极选择线ssl3”。两层的第一源极选择线ssl1”至两层的第三源极选择线ssl3”可以由第一导电图案31a和第二导电图案31b构成。

88.如参照图3a所述的,源极隔离绝缘层ss”可以形成为与沟道柱ch”的锥形形状相反的形状。因此,如参照图3a所述的,本公开的实施方式可以提高源极隔离绝缘层ss”的对准余量。

89.源极隔离绝缘层ss”可以与栅极叠层g1”交叠。源极隔离绝缘层ss”可以平行于漏极隔离绝缘层sd”延伸。在一个实施方式中,源极隔离绝缘层ss”和漏极隔离绝缘层sd”可以在第三方向d3上延伸。

90.第二绝缘层133”和第三绝缘层165”可以以与图3a所示的第二绝缘层133和第三绝缘层165相同的结构形成。

91.参照图6b,选择叠层30的第一导电图案31a和第二导电图案31b中的每一个可以包括金属层mt”和金属阻挡层bm”。金属阻挡层bm”可以设置在金属层mt”和存储器图案ml”之间。金属阻挡层bm”可以在金属层mt”和第一绝缘层11”之间延伸。金属阻挡层bm”可以在金属层mt”和层间绝缘层33之间延伸。金属阻挡层bm”可以在金属层mt”和栅极叠层g1”之间延伸。

92.如参照图3b所述的,存储器图案ml”可以包括隧穿绝缘层ti”、数据存储层dl”和阻挡绝缘层bi”。如参照图3b所述的,沟道柱ch”可以超出存储器图案ml”而突出到公共源极层的掺杂半导体层181”中。沟道柱ch”的沟道层cl”和芯绝缘层co”可以延伸到掺杂半导体层181”中。

93.源极隔离绝缘层ss”可以包括面向栅极叠层g1”的底表面和面向掺杂半导体层181”的上表面。根据本公开的一个实施方式,通过锥形形状,源极隔离绝缘层ss”的底表面

宽度w31可以比源极隔离绝缘层ss”的上表面宽度w32窄。

94.图7a至图7h是示出根据本公开的一个实施方式的制造半导体存储器装置的方法的截面图。

95.参照图7a,可以在牺牲基板601上形成保护层603。保护层603可以包括对牺牲基板601具有蚀刻选择性的材料。在一个实施方式中,牺牲基板601可以是硅基板,并且保护层603可以包括氮化硅层。

96.随后,可以在保护层603上层叠第一绝缘层605和第一导电图案607。此后,可以在第一导电图案607上交替地层叠层间绝缘层611和牺牲层613。

97.第一绝缘层605可以包括氧化硅层。第一导电图案607可以包括对层间绝缘层611和牺牲层613具有蚀刻选择性的导电材料。在一个实施方式中,第一导电图案607可以包括硅层,层间绝缘层611可以包括氧化硅层,并且牺牲层613可以包括氮化硅层。

98.此后,可以在层间绝缘层611和牺牲层613的叠层上形成第一掩模图案615。随后,可以形成穿过层间绝缘层611和牺牲层613并且延伸到保护层603中的沟道孔619。可以通过使用形成沟道孔619的工艺来形成与每个沟道孔619的形状相同的虚设孔619d。

99.可以通过使用第一掩模图案615作为蚀刻阻挡层的蚀刻工艺来蚀刻层间绝缘层611、牺牲层613、第一导电图案607和第一绝缘层605,来形成沟道孔619和虚设孔619d中的每一个。在形成沟道孔619和虚设孔619d的蚀刻工艺期间,可以对保护层603的一部分进行蚀刻,但是保护层603可以沿着沟道孔619和虚设孔619d中的每一个的底表面而保留。

100.可以通过从与第一掩模图案615相邻的层间绝缘层611朝向保护层603依次蚀刻层间绝缘层611、牺牲层613、第一导电图案607和第一绝缘层605来执行用于形成沟道孔619和虚设孔619d的蚀刻工艺。因此,沟道孔619和虚设孔619d中的每一个可以具有沿着第一方向d1朝向牺牲基板601逐渐变窄的锥形形状。

101.随后,可以在沟道孔619和虚设孔619d的表面上分别形成存储器层621和虚设存储器层621d。存储器层621和虚设存储器层621d中的每一个可以包括图8a所示的第一阻挡绝缘层621a、数据存储层621b和隧穿绝缘层621c。

102.此后,可以在由存储器层621开设的沟道孔619的中心区域中形成沟道柱630。在形成沟道柱630时,可以在由虚设存储器层621d开设的虚设孔619d的中心区域中形成虚设沟道柱630d。

103.形成沟道柱630和虚设沟道柱630d的步骤可以包括:沿着沟道孔619和虚设沟道孔619d中的每一个的表面形成半导体层;在半导体层上形成填充绝缘层;去除填充绝缘层的一部分;利用掺杂半导体层填充其中填充绝缘层被去除的区域;以及使掺杂半导体层和半导体层平坦化,以使得第一掩模图案615暴露。通过上述系列工艺,填充绝缘层可以在沟道孔619内部作为芯绝缘层625保留,并且可以在虚设沟道孔619d内部作为虚设芯绝缘层625d保留。此外,半导体层可以在沟道孔619内部作为沟道层623保留,并且可以在虚设沟道孔619d内部作为虚设沟道层623保留。此外,掺杂半导体层可以在沟道孔619内部作为封盖图案627保留,并且可以在虚设沟道孔619d内部作为虚设封盖图案627d保留。半导体层可以包括硅层,并且掺杂半导体层可以包括含有n型杂质的掺杂硅层。

104.沟道柱630中的每一个可以包括面向第一方向d1的第一端ep1a和面向与第一端ep1a相反的方向的第二端ep2a。沟道柱630中的每一个可以具有随着沟道柱630接近第一端

ep1a而逐渐变窄的锥形形状。

105.在形成沟道柱630和虚设沟道柱630d之后,可以去除第一掩模图案615。

106.参照图7b,可以形成覆盖沟道柱630和虚设沟道柱630d的第二绝缘层635。第二绝缘层635可以延伸以与层间绝缘层611交叠。

107.随后,可以形成第一狭缝637以穿过第二绝缘层635、图7a所示的层间绝缘层611和牺牲层613。在形成第一狭缝637的蚀刻工艺期间,第一导电图案607可以用作蚀刻停止层。

108.此后,通过经由第一狭缝637选择性地去除牺牲层613,可以在层间绝缘层611之间开设水平空间639。

109.参照图7c,可以通过第一狭缝637分别在图7b所示的水平空间639内部形成第二导电图案649。在形成第二导电图案649之前,可以在每个水平空间639的表面上形成第二阻挡绝缘层641。

110.形成第二导电图案649的步骤可以包括:利用导电材料填充由第二阻挡绝缘层641开设的水平空间639,以及去除第一狭缝637内部的导电材料,以使得导电材料可以被分离成第二导电图案649。第二导电图案649的导电材料可以包括图8a所示的金属阻挡层643和金属层645。

111.可以通过上面参照图7a至图7c描述的工艺来限定初步结构650。初步结构650可以包括具有锥形形状的沟道柱630、围绕沟道柱630的第一导电图案607以及交替地层叠在第一导电图案607上并围绕沟道柱630的层间绝缘层611和第二导电图案649。

112.此后,可以通过蚀刻经由第一狭缝637暴露的第一导电图案607来形成第二狭缝651。第二狭缝651可以穿过第一导电图案607,并且可以连接到第一狭缝637。

113.参照图7d,可以利用栅极隔离绝缘层653来填充图7c所示的第一狭缝637和第二狭缝651。此后,可以形成漏极沟槽657。漏极沟槽657可以穿过图7c所示的第二导电图案649中的至少一层。漏极沟槽657所贯穿的第二导电图案649与沟道柱630的第二端ep2a相邻。

114.漏极沟槽657可以在沟道柱630之间沿第三方向d3延伸。图7c所示的第二导电图案649可以被漏极沟槽657分离成漏极选择线649d。漏极选择线649d可以在与沟道柱630交叉的平面中在第二方向d2和第三方向d3上延伸,以围绕沟道柱630。

115.在用于形成漏极沟槽657的蚀刻工艺期间,可以蚀刻虚设沟道柱630d的一部分。可以通过从第二绝缘层635朝向图7c所示的第二导电图案649依次蚀刻第二绝缘层635、层间绝缘层611以及图7c所示的第二导电图案649中的至少一层来执行用于形成漏极沟槽657的蚀刻工艺。因此,漏极沟槽657可以具有朝向第一方向d1逐渐变窄的锥形形状。

116.可以将图7c所示的第二导电图案649中的一些限定为字线649w。字线649w可以不被漏极沟槽657贯穿,并且可以设置在漏极选择线649d和第一导电图案607之间。

117.漏极沟槽657的一些区域可以与虚设沟道柱630d交叠,并且其它区域可以与未被虚设沟道柱630d贯穿的字线649w的一些区域交叠。虽然图中未示出,但是图7d所示的虚设沟道柱630d可以在第三方向d3上与另一虚设沟道柱相邻。与漏极沟槽657交叠的字线649w的一些区域可以设置在沿第三方向d3相邻的虚设沟道柱之间。虚设沟道柱和漏极沟槽657的布置与图2所示的虚设沟道柱dch和漏极隔离绝缘层sd的布置相同。

118.参照图7e,可以利用漏极隔离绝缘层659来填充图7d所示的漏极沟槽657。漏极隔离绝缘层659可以具有与图7d所示的漏极沟槽657相同的锥形形状。

119.根据本公开的一个实施方式,在利用图7c所示的第二导电图案649替换图7a所示的牺牲层613之后形成漏极隔离绝缘层659。因此,当执行利用图7c所示的第二导电图案649替换图7a所示的牺牲层613的工艺时,不会出现漏极隔离绝缘层659引起的蚀刻材料或导电材料的流入受阻的问题。因此,根据本公开的一个实施方式,因为可以在对蚀刻材料或导电材料的流入没有设计限制的情况下设计漏极隔离绝缘层659的布局,所以可以提高漏极隔离绝缘层659的设计自由度。

120.随后,可以在第二绝缘层635上形成第三绝缘层661。此后,可以形成接触插塞663以与沟道柱630交叠地穿过第二绝缘层635和第三绝缘层661。接触插塞663可以与沟道柱630的封盖图案627接触。

121.随后,可以形成位线665。位线665可以面向每个沟道柱630的第二端ep2a。位线665可以形成在第三绝缘层661上并且可以与接触插塞663接触。位线665可以在与漏极隔离绝缘层659交叉的方向上延伸。在本实施方式中,位线665可以在第二方向d2上延伸。

122.在形成位线665之后,可以形成第一互连结构668和第一接合金属图案669。第一互连结构668和第一接合金属图案669可以埋入第一绝缘结构667中。第一互连结构668可以包括各种形状的导电图案。第一接合金属图案669可以连接到第一互连结构668。第一接合金属图案669中的至少一个可以与位线665交叠,并且可以经由第一互连结构668连接到位线665。

123.参照图7f,可以设置外围电路结构670。外围电路结构670可以包括含有晶体管675的基板671、覆盖基板671的第二绝缘结构681以及埋入第二绝缘结构681中的第二互连结构682和第二接合金属图案683。

124.基板671可以是诸如硅基板或锗基板之类的半导体基板。晶体管675可以形成在由元件隔离层673分隔的基板671的有源区中。晶体管675中的每一个可以被配置为与参照图3a描述的晶体管tr相同。晶体管675中的一些可以被包括在页缓冲电路679中。

125.第二互连结构682可以包括各种形状的导电图案。第二接合金属图案683可以连接到第二互连结构682。第二接合金属图案683中的至少一个可以与页缓冲电路679交叠,并且可以经由第二互连结构682连接到页缓冲电路679。

126.牺牲基板601可以与外围电路结构670对准,使得第一接合金属图案669面向外围电路结构670的第二接合金属图案683。此后,第一接合金属图案669和第二接合金属图案683可以彼此接合。

127.参照图7g,可以去除图7f所示的牺牲基板601。在去除牺牲基板601时,图7f所示的保护层603可以保护沟道柱630和存储器层621。随后,可以通过选择性地去除图7f所示的保护层603而暴露第一绝缘层605。

128.可以保留存储器层621以覆盖在第一方向上突出而超过第一绝缘层605的沟道柱630中的每一个的表面,并且可以保留虚设存储器层621d以覆盖在第一方向上突出而超过第一绝缘层605的虚设沟道柱630d的表面。

129.参照图7h,可以在第一绝缘层605上形成第二掩模图案685。随后,可以通过使用第二掩模图案685作为蚀刻阻挡层的蚀刻工艺来形成穿过图7g所示的第一绝缘层605和图7g所示的第一导电图案607的源极沟槽687。因此,图7g所示的第一导电图案607可以被源极沟槽687分离成源极选择线607s。

130.源极选择线607s可以在第二方向d2和第三方向d3上延伸,以围绕沟道柱630。源极沟槽687可以在沟道柱630之间在第三方向d3上延伸。源极沟槽687可以与漏极隔离绝缘层659交叠并且字线649w介于源极沟槽687和漏极隔离绝缘层659之间。源极沟槽687可以与虚设沟道柱630d交叠。在用于形成源极沟槽687的蚀刻工艺期间,可以蚀刻虚设存储器层621d的一部分和虚设沟道柱630d的一部分。

131.可以通过朝向与第一方向d1相反的方向依次蚀刻图7g所示的第一绝缘层605和图7g所示的第一导电图案607来执行用于形成源极沟槽687的蚀刻工艺。因此,源极沟槽687可以具有朝向与第一方向d1相反的方向逐渐变窄的锥形形状。

132.图8a至图8d是示出在图7h所示的工艺之后的后续工艺的放大截面图。图8a至图8d是图7h所示的区域ra的放大截面图。

133.参照图8a,可以通过去除图7h所示的第二掩模图案685来暴露第一绝缘层605和存储器层621。存储器层621可以包括第一阻挡绝缘层621a、数据存储层621b和隧穿绝缘层621c。第一阻挡绝缘层621a可以包括氧化硅层,数据存储层621b可以包括氮化硅层,并且隧穿绝缘层621c可以包括氧化硅层。第二阻挡绝缘层641可以包括介电常数高于第一阻挡绝缘层621a的介电常数的材料层。在一个实施方式中,第二阻挡绝缘层641可以包括氧化铝层。

134.参照图8b,可以利用源极隔离绝缘层693来填充图8a所示的源极沟槽687。源极隔离绝缘层693可以包括氧化物层。

135.随后,可以去除第一阻挡绝缘层621a的一部分,从而暴露数据存储层621b。此时,可以去除源极隔离绝缘层693的一部分。可以利用回蚀工艺来去除第一阻挡绝缘层621a的一部分和源极隔离绝缘层693的一部分。

136.参照图8c,可以通过依次执行选择性蚀刻数据存储层621b的蚀刻工艺和选择性蚀刻隧穿绝缘层621c的蚀刻工艺来限定存储器图案621ml。沟道柱630的沟道层623和芯绝缘层625可以突出超过存储器图案621ml,并且沟道层623的表面可以在沟道柱630的突起处暴露。

137.在蚀刻数据存储层621b和隧穿绝缘层621c时,可以蚀刻源极隔离绝缘层693的一部分,但是可以保留第一绝缘层605以围绕沟道柱630。

138.参照图8d,可以形成与沟道层623的暴露表面接触的掺杂半导体图案695。掺杂半导体图案695可以构成公共源极层。掺杂半导体图案695可以延伸以与源极选择线607s和源极隔离绝缘层693交叠。掺杂半导体图案695可以通过第一绝缘层605与源极选择线607s间隔开。

139.图9a至图9c是示出根据本公开的一个实施方式的制造半导体存储器装置的方法的截面图。

140.参照图9a,可以通过使用参照图7a至图7c描述的工艺在牺牲基板701上形成保护层703、第一绝缘层705和初步结构750。

141.初步结构750的第一导电图案707可以包括硅。初步结构750的层间绝缘层711和第二导电图案749可以交替地层叠在第一导电图案707上。第二导电图案749的导电材料可以包括如图10a所示的金属阻挡层743和金属层745。

142.初步结构750的沟道柱730中的每一个可以具有朝向面向牺牲基板701的第一方向

d1逐渐变窄的锥形形状。

143.层间绝缘层711、第二导电图案749和第一导电图案707可以被形状与沟道柱730的形状类似的虚设沟道柱730d贯穿。沟道柱730和虚设沟道柱730d可以穿过第一绝缘层705并且延伸到保护层703中。

144.如参照图7a所述的,沟道柱730中的每一个可以包括芯绝缘层725、封盖图案727和沟道层723。沟道柱730中的每一个可以包括面向第一方向d1的第一端ep1b和面向与第一方向d1相反的方向的第二端ep2b。存储器层721可以沿着沟道柱730的第一端ep1b和沟道柱730的侧壁延伸。如图10a所示,存储器层721可以包括第一阻挡绝缘层721a、数据存储层721b和隧穿绝缘层721c。

145.可以沿着第二导电图案749中的每一个的表面形成第二阻挡绝缘层741。

146.如参照图7a所述的,虚设沟道柱730d可以由虚设存储器层721d围绕,并且可以包括虚设沟道层723d、虚设芯绝缘层725d和虚设封盖图案727d。

147.沟道柱730中的每一个的第二端ep2b和虚设沟道柱730d可以被第二绝缘层735覆盖。

148.将初步结构750分隔的栅极隔离绝缘层753可以设置在第一导电图案707上而不穿过第一导电图案707。

149.参照图9b,在形成栅极隔离绝缘层753之后,可以通过参照图7d和图7e描述的工艺形成具有朝向第一方向d1逐渐变窄的锥形形状的漏极隔离绝缘层759。漏极隔离绝缘层759可以将图9a所示的第二导电图案749中的至少一层划分成漏极选择线749d。划分成漏极选择线749d的第二导电图案与沟道柱730的第二端ep2b相邻。在第二导电图案749当中,漏极隔离绝缘层759和第一导电图案707之间的第二导电图案可以被限定为字线749w。

150.漏极隔离绝缘层759的一些区域可以与虚设沟道柱730d交叠,并且其它区域可以与未被虚设沟道柱730d贯穿的字线749w的一些区域交叠。

151.参照图9c,可以通过参照图7e描述的工艺形成第三绝缘层761、接触插塞763、位线765、第一互连结构768和第一接合金属图案769。如参照图7e所述的,第一互连结构768和第一接合金属图案769可以埋入第一绝缘结构767中。

152.随后,外围电路结构770的第二接合金属图案783可以通过参照图7f描述的工艺接合到第一接合金属图案769。如参照图7f所述的,外围电路结构770可以包括具有晶体管775的基板771、覆盖基板771的第二绝缘结构781以及埋入第二绝缘结构781中的第二互连结构782和第二接合金属图案783。

153.随后,可以依次去除图9b所示的牺牲基板701和保护层703。因此,可以暴露第一绝缘层705。

154.此后,可以在第一绝缘层705上形成掩模图案785。随后,可以通过使用掩模图案785作为蚀刻阻挡层的蚀刻工艺来形成穿过图9b所示的第一绝缘层705和第一导电图案707的源极沟槽787。如参照图7h所述的,源极沟槽787可以具有在与第一方向d1相反的方向上逐渐变窄的锥形形状。

155.图9b所示的第一导电图案707可以被源极沟槽787分离成初步选择线707a。初步选择线707a可以在与沟道柱730交叉的平面中在第二方向d2和第三方向d3上延伸。源极沟槽787可以在沟道柱730之间在第三方向d3上延伸。源极沟槽787可以与虚设沟道柱730d、漏极

隔离绝缘层759和栅极隔离绝缘层753交叠。

156.图10a至图10c是示出在图9c所示的工艺之后的后续工艺的放大截面图。图10a至图10c是图9c所示的区域rb的放大截面图。

157.参照图10a,可以通过去除图9c所示的掩模图案785来暴露第一绝缘层705和存储器层721。随后,可以在通过源极沟槽787暴露的初步选择线707a的侧壁上形成金属层789。金属层789可以沿着源极沟槽787的表面延伸。金属层789可以沿着第一绝缘层705的表面和存储器层721的表面延伸。

158.金属层789可以包括导电材料,该导电材料能够通过经由在450℃或更低的温度下执行的硅化工艺与初步选择线707a进行反应来提供金属硅化物层。在一个实施方式中,金属层789可以包括镍。

159.参照图10b,通过在450℃或更低的温度下执行硅化工艺,可以将图10a所示的初步选择线707a的一部分转换成金属硅化物层。此后,可以去除没有与硅层反应的剩余金属层。图10a中所示的初步选择线707a的一些区域可能未转换成金属硅化物层,而是可作为硅层保留。保留的硅层可以构成第一选择图案707b。此外,金属硅化物层可以构成沿着第一选择图案707b的侧壁延伸的第二选择图案791。

160.可以通过上述工艺来限定包括第一选择图案707b和第二选择图案791的源极选择线790ssl。由金属硅化物层构成的第二选择图案791可以补偿由硅层构成的第一选择图案707b的电阻,从而减小源极选择线790ssl的电阻。

161.在超过450℃的高温工艺中,在图9c所示的第一接合金属图案769和第二接合金属图案783中可能出现缺陷。由于根据本公开的一个实施方式的硅化工艺是在450℃或更低的低温下执行的,因此根据本公开的该实施方式,在图9c所示的第一接合金属图案769和第二接合金属图案783中,可以减少由于高温导致的缺陷发生。

162.参照图10c,可以使用参照图8b描述的工艺利用源极隔离绝缘层793来填充图10b所示的源极沟槽787。

163.随后,如参照图8b和图8c所述的,可以通过依次执行第一阻挡绝缘层721a的蚀刻工艺、数据存储层721b的蚀刻工艺和隧穿绝缘层721c的蚀刻工艺来限定存储器图案721m。沟道柱730的沟道层723和芯绝缘层725可以突出超过存储器图案721ml,并且沟道层723的表面可以在沟道柱730的突起处暴露。

164.此后,可以形成与暴露的沟道层723的表面接触的掺杂半导体图案795。

165.图11a至图11d是示出根据本公开的一个实施方式的制造半导体存储器装置的方法的放大截面图。

166.在执行图11a至图11d所示的工艺之前,可以先进行参照图9a至图9c描述的工艺。因此,可以形成由源极沟槽787’划分的初步选择线707s’。

167.初步选择线707s’可以与导电图案749’和层间绝缘层711’的叠层交叠。导电图案749’、层间绝缘层711’和初步选择线707s’可以围绕沟道柱730’。沟道柱730’可以具有朝向第一方向d1逐渐变窄的锥形形状。沟道柱730’可以包括芯绝缘层725’和沟道层723’。沟道柱730’中的每一个的侧壁可以被存储器层721’围绕。

168.存储器层721’可以延伸以覆盖每个沟道柱730’的面向第一方向d1的第一端ep1c。存储器层721’可以包括第一阻挡绝缘层721a’、数据存储层721b’和隧穿绝缘层721c’。

169.初步选择线707s’可以比导电图案749’更靠近沟道柱730’的第一端ep1c设置。初步选择线707s’中的每一条可以由硅层构成。

170.导电图案749’可以包括金属阻挡层743’和金属层745’。第二阻挡绝缘层741’可以设置在导电图案749’和存储器层721’之间。第二阻挡绝缘层741’可以在导电图案749’和层间绝缘层711’之间延伸。

171.源极沟槽787’可以延伸以穿过第一绝缘层705’。可以通过源极沟槽787’蚀刻初步选择线707’中的每一条的一部分。因此,可以在第一绝缘层705’和层间绝缘层711’之间限定凹槽788’。

172.掩模图案785’可以在用于形成源极沟槽787’的蚀刻工艺期间用作蚀刻阻挡层。掩模图案785’可以在用于形成凹槽788’的蚀刻工艺期间保护存储器层721’和沟道柱730’。

173.参照图11b,可以利用导电层789’来填充图11a中所示的凹槽788’。导电层789’可以包括可在450℃或更低温度的工艺中沉积的各种导电材料。在一个实施方式中,导电层789’可以包括通过物理气相沉积(pvd)法或原子层沉积法沉积的各种导电材料。导电层789’可以包括金属层789b以及位于金属层789b和初步选择线707s’之间的金属阻挡层789a。金属阻挡层789a可以与初步选择线707s’的侧壁接触。金属层789b和金属阻挡层789a可以补偿由硅层构成的初步选择线707s’的电阻。

174.因为用于补偿硅层的电阻的导电层789’是在450℃或更低的低温下形成,所以根据本公开的一个实施方式,在图9c所示的第一接合金属图案769和第二接合金属图案783中,可以减少由于高温导致的缺陷发生。

175.参照图11c,可以通过诸如回蚀之类的蚀刻工艺去除源极沟槽787’中的金属层789b和金属阻挡层789a。因此,可以限定包括侧壁导电图案789p和初步选择线707s’的源极选择线790ssl’。侧壁导电图案789p可以保留在初步选择线707s’的侧壁上。

176.参照图11d,通过使用参照图8b描述的工艺,可以利用源极隔离绝缘层793’来填充图11c所示的源极沟槽787’。

177.随后,如参照图8b和图8c所述,可以通过依次执行第一阻挡绝缘层721a’的蚀刻工艺、数据存储层721b’的蚀刻工艺和隧穿绝缘层721c’的蚀刻工艺来限定存储器图案721ml’。此外,沟道柱730’的沟道层723’和芯绝缘层725’可以突出超过存储器图案721ml’,并且沟道层723’的表面可以在沟道柱730’的突起处暴露。

178.此后,可以形成与沟道层723’的暴露表面接触的掺杂半导体图案795’。

179.图12a至图12d是示出根据本公开的一个实施方式的制造半导体存储器装置的方法的截面图。

180.参照图12a,在牺牲基板801上形成第一绝缘层805之后,可以在第一绝缘层805上交替地层叠牺牲层813和层间绝缘层811。

181.第一绝缘层805可以包括氧化硅层。牺牲层813可以包括氮化硅层。层间绝缘层811可以包括氧化硅层。

182.可以使用参照图7a描述的工艺来形成沟道柱830。在形成沟道柱830时,可以形成虚设沟道柱830d。沟道柱830和虚设沟道柱830d可以延伸到牺牲基板801中。

183.沟道柱830中的每一个可以包括面向相反方向的第一端ep1d和第二端ep2d。第一端ep1d可以面向第一方向d1。沟道柱830的侧壁可以被存储器层821围绕。存储器层821可以

在第一端ep1d和牺牲基板801之间延伸。沟道柱830可以包括沟道层823、芯绝缘层825和封盖图案827。沟道柱830可以具有朝向第一端ep1d逐渐变窄的锥形形状。存储器层821可以包括图13a所示的第一阻挡绝缘层821a、数据存储层821b和隧穿绝缘层821c。

184.虚设沟道柱830d可以被虚设存储器层821d围绕。虚设沟道柱830d可以包括虚设沟道层823d、虚设芯绝缘层825d和虚设封盖图案827d。

185.沟道柱830和虚设沟道柱830d可以被第二绝缘层835覆盖。

186.第二绝缘层835、层间绝缘层811、牺牲层813和第一绝缘层805可以被狭缝837贯穿。

187.参照图12b,可以通过狭缝837用导电图案849来替换图12a所示的牺牲层813。导电图案849可以由相同的导电材料形成。如图13a所示,导电图案849中的每一个可以包括金属阻挡层843和金属层845。在形成导电图案849之前,可以在图12a所示的牺牲层813被去除的区域中的每一个的表面上形成第二阻挡绝缘层841。

188.通过以上参照图12a和图12b描述的工艺,可以形成初步结构850,该初步结构850包括具有锥形形状的沟道柱830、以及围绕沟道柱830并且交替地层叠在第一绝缘层805上的导电图案849和层间绝缘层811。

189.参照图12c,可以利用栅极隔离绝缘层853来填充图12b所示的狭缝837。随后,可以形成穿过图12b所示的导电图案849中的至少一层的漏极隔离绝缘层859。漏极隔离绝缘层859所贯穿的导电图案与沟道柱830的第二端ep2d相邻。

190.与第二端ep2d相邻的导电图案可以被漏极隔离绝缘层859分离成漏极选择线849d。漏极选择线849d可以在与沟道柱830交叉的平面中在第二方向d2和第三方向d3上延伸以围绕沟道柱830。漏极隔离绝缘层859可以在沟道柱830之间在第三方向d3上延伸。漏极隔离绝缘层859可以具有朝向第一方向d1逐渐变窄的锥形形状。

191.漏极隔离绝缘层859可以包括与虚设沟道柱830d交叠的区域和不与虚设沟道柱830d交叠的区域。

192.参照图12d,可以使用参照图7e描述的工艺形成第三绝缘层861、接触插塞863、位线865、第一互连结构868和第一接合金属图案869。如参照图7e所述的,第一互连结构868和第一接合金属图案869可以埋入第一绝缘结构867中。

193.随后,可以通过参照图7f描述的工艺将外围电路结构870的第二接合金属图案883接合到第一接合金属图案869。如参照图7f所述的,外围电路结构870可以包括具有晶体管875的基板871、覆盖基板871的第二绝缘结构881以及埋入第二绝缘结构881中的第二互连结构882和第二接合金属图案883。

194.随后,可以去除图12c所示的牺牲基板801。因此,可以暴露第一绝缘层805。

195.此后,可以在第一绝缘层805上形成掩模图案885。随后,可以通过使用掩模图案885作为蚀刻阻挡层的蚀刻工艺来形成源极沟槽887。源极沟槽887可以穿过图12c所示的导电图案849中的至少一层。源极沟槽887所贯穿的导电图案与沟道柱830的第一端ep1d相邻。如参照图7h所述的,源极沟槽887可以具有朝向与第一方向d1相反的方向逐渐变窄的锥形形状。

196.被源极沟槽887贯穿的导电图案可以被分离成源极选择线849s。源极选择线849s可以在第二方向d2和第三方向d3上延伸以围绕沟道柱830。源极沟槽887可以在沟道柱830

之间在第三方向d3上延伸。源极沟槽887可以与漏极隔离绝缘层859交叠。

197.图13a和图13b是示出在图12d所示的工艺之后的后续工艺的放大截面图。图13a和图13b是图12d所示的区域rc的放大截面图。

198.参照图13a,可以通过去除图12d所示的掩模图案885来暴露第一绝缘层805。随后,可以利用源极隔离绝缘层893来填充源极沟槽887。如参照图8b所述的,在用于形成源极隔离绝缘层893的工艺中,可以蚀刻第一阻挡绝缘层821a,并且可以使数据存储层821b暴露。

199.源极隔离绝缘层893可以使相同水平处的相邻源极选择线849s电绝缘。源极隔离绝缘层893可以与字线849w的与源极沟槽887交叠的一些区域交叠。

200.参照图13b,如参照图8c所述的,可以通过依次执行数据存储层821b的蚀刻工艺和隧穿绝缘层821c的蚀刻工艺来限定存储器图案821ml。沟道柱830的沟道层823和芯绝缘层825可以突出超过存储器图案821ml,并且沟道层823的表面可以在沟道柱830的突起处暴露。

201.此后,可以形成与沟道层823的暴露表面接触的掺杂半导体图案895。

202.根据本公开的一个实施方式的源极隔离绝缘层893是在利用图12b所示的导电图案849替换图12a所示的牺牲层813之后形成的。因此,本公开的实施方式可以设计源极隔离绝缘层893的布局,而在为了利用图12b所示的导电图案849替换图12a所示的牺牲层813而流入蚀刻材料或导电材料方面没有设计限制。因此,根据本公开的一个实施方式,可以提高源极隔离绝缘层893的设计自由度。

203.图14是示出根据本公开的一个实施方式的存储器系统1100的配置的框图。

204.参照图14,存储器系统1100可以包括存储器装置1120和存储器控制器1110。

205.存储器装置1120可以包括具有锥形形状的沟道柱、具有与沟道柱的锥形形状相反的锥形形状的源极隔离绝缘层、以及围绕沟道柱并且在相同水平处彼此分离的源极选择线。源极隔离绝缘层可以设置在源极选择线之间。

206.存储器装置1120可以是由多个闪存芯片构成的多芯片封装件。

207.存储器控制器1110可以被配置成控制存储器装置1120。存储器控制器1110可以包括静态随机存取存储器(sram)1111、中央处理单元(cpu)1112、主机接口1113、纠错块1114和存储器接口1115。sram 1111可以用作cpu 1112的操作存储器,cpu1112可以执行用于存储器控制器1110的数据交换的整体控制操作,并且主机接口1113可以包括连接到存储器系统1100的主机的数据交换协议。此外,纠错块1114可以检测并且纠正从存储器装置1120读取的数据中包含的错误。存储器接口1115可以执行与存储器装置1120的接口连接。此外,存储器控制器1110还可以包括用于存储与主机进行接口连接的代码数据的只读存储器(rom)等。

208.图15是示出根据本公开的一个实施方式的计算系统的配置1200的框图。

209.参照图15,计算系统1200可以包括电连接到系统总线1260的cpu 1220、随机存取存储器(ram)1230、用户接口1240、调制解调器1250和存储器系统1210。计算系统1200可以是移动装置。

210.存储器系统1210可以包括存储器装置1212和存储器控制器1211。存储器装置1212可以包括具有锥形形状的沟道柱、具有与沟道柱的锥形形状相反的锥形形状的源极隔离绝缘层、以及围绕沟道柱并且在相同水平处彼此分离的源极选择线。源极隔离绝缘层可以设

置在源极选择线之间。

211.根据本公开,因为设置在沟道柱之间的源极隔离绝缘层在与沟道柱相反的方向上逐渐变窄,所以可以提高沟道柱之间的源极隔离绝缘层的对准余量。

212.相关申请的交叉引用

213.本技术要求于2020年9月10日向韩国知识产权局提交的韩国专利申请no.10-2020-0116060的优先权,其全部内容通过引用结合于此。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。