1.本发明涉及二极管,尤其涉及低电磁干扰(electro magnetic interference,emi)的二极管及其半导体结构。

背景技术:

2.图1是现有的芯片的功能方框图。芯片100包含内部电路110、内部电路120、二极管130、二极管140及输出/输入垫150。内部电路110及内部电路120负责芯片100的功能,而内部电路120通过输出/输入垫150接收信号或是输出信号。二极管130串接于电压源vdd与输出/输入垫150之间,而二极管140串接于输出/输入垫150与接地电平之间。二极管130及二极管140可以防止静电放电(electrostatic discharge,esd)损害内部电路120。

3.随着集成电路的功能越来越强、操作速度越来越快,芯片100上的电磁干扰问题也越来越严重。一般而言,在解决电磁干扰的问题上,越往信号的源头着手效果越好,而且所付出的代价也较低。因此,设计低电磁干扰的二极管成为本技术领域的一个重要课题。

技术实现要素:

4.鉴于先前技术的不足,本发明的一目的在于提供一种二极管及其半导体结构。

5.本发明披露一种二极管,应用于一半导体结构,包含基板、第一导体结构及第二导体结构。基板包含一第一掺杂区及一第二掺杂区,其中该第一掺杂区用作该二极管的一第一电极,该第二掺杂区用作该二极管的一第二电极,且该第一掺杂区的掺杂物不同于该第二掺杂区的掺杂物。第一导体结构位于该第一掺杂区的上方且连接该第一掺杂区,并且具有多个第一导体,其中这些第一导体分布于该半导体结构的多个导体层,且这些第一导体以多个导孔互相连接。第二导体结构位于该第二掺杂区的上方且连接该第二掺杂区,并且具有多个第二导体,其中这些第二导体分布于该半导体结构的这些导体层,且这些第二导体以多个导孔互相连接。该第一导体结构的一侧视图呈现一阶梯状。

6.本发明另披露一种二极管,应用于一半导体结构,包含基板、第一导体、第二导体、第三导体及第四导体。基板包含一第一掺杂区及一第二掺杂区,其中该第一掺杂区用作该二极管的一第一电极,该第二掺杂区用作该二极管的一第二电极,且该第一掺杂区的掺杂物不同于该第二掺杂区的掺杂物。第一导体位于该半导体结构的一第一导体层,且连接该第一掺杂区。第二导体位于该半导体结构的一第二导体层,且连接该第一导体。第三导体位于该半导体结构的该第一导体层,且连接该第二掺杂区。第四导体位于该半导体结构的该第二导体层,且连接该第三导体。在该半导体结构的一侧视图中,该第一导体与该第三导体的重叠面积大于该第二导体与该第四导体的重叠面积。

7.本发明的二极管及其半导体结构具有较小的电流回路面积,因此,相较于传统技术,本发明的二极管及其半导体结构产生较小的电磁干扰。

8.有关本发明的特征、实际操作与效果,配合图式作实施例详细说明如下。

附图说明

9.图1为现有的芯片的功能方框图;

10.图2为本发明一实施例的二极管在基板上的布局;

11.图3显示本发明一实施例的半导体结构;

12.图4a为本发明一实施例的二极管的第一横截面图;

13.图4b为本发明一实施例的二极管的第二横截面图;

14.图5a、图5b、图5c、图5d、图5e为本发明一实施例的二极管的多个俯视图;

15.图6为本发明另一实施例的二极管的第一横截面图;

16.图7a、图7b、图7c、图7d、图7e为本发明另一实施例的二极管的多个俯视图;

17.图8为本发明另一实施例的二极管在基板上的布局;

18.图9a、图9b、图9c、图9d、图9e为本发明另一实施例的二极管的多个俯视图;以及

19.图10显示本发明另一实施例的导体的形状。

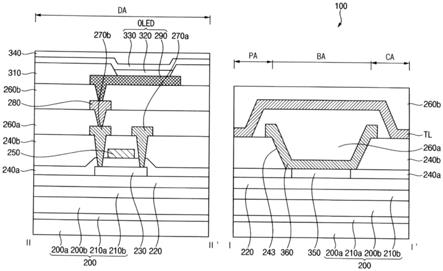

具体实施方式

20.以下说明内容的技术用语是参照本技术领域的习惯用语,如本说明书对部分用语有加以说明或定义,该部分用语的解释是以本说明书的说明或定义为准。

21.图2为本发明一实施例的二极管在基板上的布局。基板200上有掺杂区210及掺杂区220,掺杂区210为n型掺杂区(即,二极管的阴极),而掺杂区220为p型掺杂区(即,二极管的阳极)。换言之,掺杂区210的掺杂物与掺杂区220的掺杂物不同。在一些实施例中,掺杂区210与掺杂区220实质上互相平行。

22.图3显示本发明一实施例的半导体结构。半导体结构300包含基板200及堆栈于基板200上方(z方向)的氧化层310。在氧化层310内部有多个导体层320(至少包含导体层320-1、导体层320-2及导体层320-3)。相邻的导体层之间通过多个导孔(via)330连接,而导体层320-3与基板200之间通过多个触点(contact)340连接。在一些实施例中,这些导体层320由下到上(即,由接近基板200至远离基板200)依序是金属层1(m1)、金属层2(m2)、金属层3(m3)、

……

、超厚金属(ultra-thick metal,utm)层及重布线层(re-distribution layer,rdl)。图2为半导体结构300的基板200本身的俯视图(x-y平面)。

23.图4a为本发明一实施例的二极管的第一横截面图(即侧视图,y-z平面)(对应于图2的横截面a-a'),图4b为本发明一实施例的二极管的第二横截面图(对应于图2的横截面b-b')。

24.如图4a所示,掺杂区210的上方有一导体结构410,掺杂区210与导体结构410之间通过多个触点连接,换言之,导体结构410为二极管的阴极。导体结构410包含多个导体415(即,导体415-1、导体415-2、导体415-3、导体415-4、

……

、导体415-n,n为大于1的整数)。相邻的导体415之间通过多个导孔连接,因此,导体结构410的多个导体415实质上等电位。由下而上,导体415-1位于金属层m1(具有厚度h1)、导体415-2位于金属层m2(具有厚度h2)、导体415-3位于金属层m3(具有厚度h3)、导体415-4位于金属层m4(具有厚度h4)、

……

、导体415-n位于金属层mn(具有厚度hn)。在一些实施例中,导体415-1至导体415-n实质上等长度(l)。

25.如图4b所示,掺杂区220的上方有一导体结构420,掺杂区220与导体结构420之间

通过多个触点连接,换言之,导体结构420为二极管的阳极。导体结构420包含多个导体425(即,导体425-1、导体425-2、导体425-3、导体425-4、

……

、导体425-n)。相邻的导体425之间通过多个导孔连接,因此,导体结构420的多个导体425实质上等电位。由下而上,导体425-1位于金属层m1、导体425-2位于金属层m2、导体425-3位于金属层m3、导体425-4位于金属层m4、

……

、导体425-n位于金属层mn。导体结构420呈现阶梯状:导体425-1比导体425-2长d1的长度、导体425-2比导体425-3长d2的长度、导体425-3比导体425-4长d3的长度、

……

,且导体425-n为导体结构420中最短的导体,换句话说,导体结构420中的导体不等长。如图4b所示,导体结构420中的这些导体425的位于侧视图左侧的一端实质上对齐,然而本发明不限于这些导体的同一端是否实质上对齐。在一些实施例中,导体425-1、导体425-2、导体425-3、导体425-4、

……

、导体425-n的长度呈等差数列(即,d1=d2=d3)。

26.如图2、图3及图4a和图4b所示,本发明的二极管为一个立体结构,应用于半导体结构300中,包含基板200上的掺杂区210及掺杂区220、导体结构410及导体结构420。

27.图5a至图5e为本发明一实施例的二极管的多个俯视图,分别显示各导体层与基板上的掺杂区的关系。图5a至图5e对应于图4a和图4b的横截面图。

28.图5a显示金属层m1上的导体415-1及导体425-1与掺杂区210及掺杂区220的对应关系。导体415-1完全覆盖掺杂区210且与掺杂区210实质上平行。导体425-1完全覆盖掺杂区220且与掺杂区220实质上平行。导体415-1与导体425-1实质上平行。导体415-1与导体425-1的长度皆为l。

29.图5b显示金属层m2上的导体415-2及导体425-2与掺杂区210及掺杂区220的对应关系。导体415-2完全覆盖掺杂区210且与掺杂区210实质上平行。导体425-2部分覆盖掺杂区220且与掺杂区220实质上平行。导体415-2与导体425-2实质上平行。导体415-2的长度为l,导体415-2与导体425-2的长度差为d1。

30.图5c显示金属层m3上的导体415-3及导体425-3与掺杂区210及掺杂区220的对应关系。导体415-3完全覆盖掺杂区210且与掺杂区210实质上平行。导体425-3部分覆盖掺杂区220且与掺杂区220实质上平行。导体415-3与导体425-3实质上平行。导体415-3的长度为l,导体415-3与导体425-3的长度差为d1 d2。

31.图5d显示金属层m4上的导体415-4及导体425-4与掺杂区210及掺杂区220的对应关系。导体415-4完全覆盖掺杂区210且与掺杂区210实质上平行。导体425-4部分覆盖掺杂区220且与掺杂区220实质上平行。导体415-4与导体425-4实质上平行。导体415-4的长度为l,导体415-4与导体425-4的长度差为d1 d2 d3。

32.图5e显示金属层mn上的导体415-n及导体425-n与掺杂区210及掺杂区220的对应关系。导体415-n完全覆盖掺杂区210且与掺杂区210实质上平行。导体425-n部分覆盖掺杂区220且与掺杂区220实质上平行。导体415-n与导体425-n实质上平行。导体415-n的长度为l。

33.请同时参考图4a和图4b及图5a至图5e。导体415-1及导体425-1在y-z平面上实质上互相重叠(重叠面积a1≈l*h1);导体415-2及导体425-2在y-z平面上部分重叠(重叠面积a2≈(l-d1)*h2);导体415-3及导体425-3在y-z平面上部分重叠(重叠面积a3≈(l-d1-d2)*h3);导体415-4及导体425-4在y-z平面上部分重叠(重叠面积a4≈(l-d1-d2-d3)*h4);以及导体415-n及导体425-n在y-z平面上部分重叠(重叠面积为所有导体层中最小的)。如果所

有导体层的厚度实质上相同(即,h1、h2、h3、h4、hn实质上相等),则a1》a2》a3》a4。

34.因为导体结构420呈阶梯状(或称为后退状(retrograde-type)),所以导体结构410与导体结构420在每一导体层(y-z平面上)的重叠面积并不相同。更明确地说,导体结构410与导体结构420在金属层m1上的重叠面积最大、在金属层m2上的次之、

……

、在金属层mn上的最小。这样的设计可以降低二极管的阳极与阴极之间的电流回路面积(current loop area),因而降低电磁干扰。

35.图6为本发明另一实施例的二极管的第一横截面图(对应于图2的横截面a-a')。图6与图4a的差别在于,在图6的实施例中,导体结构410呈现阶梯状:导体415-1比导体415-2长d4的长度、导体415-2比导体415-3长d5的长度、导体415-3比导体415-4长d6的长度、

……

,且导体415-n为导体结构410中最短的导体,换句话说,导体结构410中的导体不等长。如图6所示,导体结构410中的这些导体415的位于侧视图右侧的一端实质上对齐,然而本发明不限于这些导体的同一端是否实质上对齐。在一些实施例中,导体415-1、导体415-2、导体415-3、导体415-4、

……

、导体415-n的长度呈等差数列(即,d4=d5=d6)。

36.图7a至图7e为本发明另一实施例的二极管的多个俯视图,分别显示各导体层与基板上的掺杂区的关系。图7a至图7e对应于图4b及图6的横截面图。

37.图7a显示金属层m1上的导体415-1及导体425-1与掺杂区210及掺杂区220的对应关系。导体415-1完全覆盖掺杂区210且与掺杂区210实质上平行。导体425-1完全覆盖掺杂区220且与掺杂区220实质上平行。导体415-1与导体425-1实质上平行。导体415-1与导体425-1的长度皆为l。

38.图7b显示金属层m2上的导体415-2及导体425-2与掺杂区210及掺杂区220的对应关系。导体415-2部分覆盖掺杂区210且与掺杂区210实质上平行。导体425-2部分覆盖掺杂区220且与掺杂区220实质上平行。导体415-2与导体425-2实质上平行。导体415-2的长度为(l-d4),导体425-2的长度为(l-d1)。

39.图7c显示金属层m3上的导体415-3及导体425-3与掺杂区210及掺杂区220的对应关系。导体415-3部分覆盖掺杂区210且与掺杂区210实质上平行。导体425-3部分覆盖掺杂区220且与掺杂区220实质上平行。导体415-3与导体425-3实质上平行。导体415-3的长度为(l-d4-d5),导体425-3的长度为(l-d1-d2)。

40.图7d显示金属层m4上的导体415-4及导体425-4与掺杂区210及掺杂区220的对应关系。导体415-4部分覆盖掺杂区210且与掺杂区210实质上平行。导体425-4部分覆盖掺杂区220且与掺杂区220实质上平行。导体415-4与导体425-4实质上平行。导体415-4的长度为(l-d4-d5-d6),导体425-4的长度为(l-d1-d2-d3)。

41.图7e显示金属层mn上的导体415-n及导体425-n与掺杂区210及掺杂区220的对应关系。导体415-n部分覆盖掺杂区210且与掺杂区210实质上平行。导体425-n部分覆盖掺杂区220且与掺杂区220实质上平行。导体415-n与导体425-n实质上平行。

42.请同时参考图4b、图6及图7a至图7e。因为导体结构410及导体结构420皆呈阶梯状,所以导体结构410与导体结构420在每一导体层(y-z平面上)的重叠面积并不相同。更明确地说,导体结构410与导体结构420在金属层m1上的重叠面积最大、在金属层m2上的次之、

……

、在金属层mn上的最小(或是不重叠)。相较于前一实施例(即对应于图4a和图4b及图5a至图5e的实施例),导体结构410与导体结构420之间整体的重叠面积更小,因此可以进

一步降低电磁干扰。

43.需注意的是,掺杂区210与掺杂区220是否平行,以及各导体层的两个导体之间是否平行并非本发明的实施关键。上述的实质上平行的两个组件亦可设计为非平行。

44.本发明的二极管不限于图2的布局,图8为本发明另一实施例的二极管在基板上的布局。掺杂区210包围掺杂区220。图9a至图9e为本发明另一实施例的二极管的多个俯视图,分别显示各导体层与基板上的掺杂区的关系。图9a至图9e对应于图4b及图6的横截面图。本技术领域具有通常知识者可以由上述的实施例了解图8及图9a至图9e的实施细节与变化,故不再赘述。值得注意的是,在图9a至图9e的实施例中,导体415为e字型,导体425为u字型(如图10所示,以导体415-1及导体425-1为例),e字型的导体415的指状结构(位于范围r内的部分)的长度由图9a至图9e逐渐递减,且u字型的导体425的指状结构(位于范围r内的部分)的长度由图9a至图9e逐渐递减。

45.请注意,前示图标中,组件的形状、尺寸以及比例等仅为示意,是供本技术领域具有通常知识者了解本发明之用,非用以限制本发明。

46.虽然本发明的实施例如上所述,然而这些实施例并非用来限定本发明,本技术领域具有通常知识者可依据本发明的明示或隐含的内容对本发明的技术特征施以变化,凡此种种变化均可能属于本发明所寻求的专利保护范畴,换言之,本发明的专利保护范围须视本说明书的权利要求书范围所界定者为准。

47.【符号说明】

48.100:芯片

49.110、120:内部电路

50.130、140:二极管

51.150:输出/输入垫

52.vdd:电压源

53.200:基板

54.210、220:掺杂区

55.300:半导体结构

56.310:氧化层

57.320、320-1、320-2、320-3:导体层

58.330:导孔

59.340:触点

60.410、420:导体结构

61.415-1、415-2、415-3、415-4、415-n、425-1、425-2、425-3、425-4、425-n:导体

62.m1、m2、m3、m4、mn:金属层

63.r:范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。