用于加载片寄存器对的系统和方法

本技术是2018年11月30日提交的、申请号为201811452229.3,题为“用于加载片寄存器对的系统和方法”的发明专利申请的分案申请。

技术领域

1.本发明的领域总体上涉及计算机处理器架构,更具体地涉及用于加载片寄存器对的系统和方法。

背景技术:

2.在诸如机器学习和其他批量数据处理之类的计算任务中,矩阵正变得日益重要。

附图说明

3.在所附附图中以示例方式而非限制方式说明本发明,在附图中,类似的附图标记指示类似的要素,其中:

4.图1a图示经配置的片(tile)的实施例;

5.图1b图示经配置的片的实施例;

6.图2图示矩阵存储的若干示例;

7.图3图示利用矩阵(片)操作加速器的系统的实施例;

8.图4和图5示出如何使用矩阵操作加速器来共享存储器的不同实施例;

9.图6图示使用片的矩阵乘法累加(“tmma”)操作的实施例;

10.图7图示链式融合乘法累加指令的迭代的执行的子集的实施例;

11.图8图示链式融合乘法累加指令的迭代的执行的子集的实施例;

12.图9图示链式融合乘法累加指令的迭代的执行的子集的实施例;

13.图10图示链式融合乘法累加指令的迭代的执行的子集的实施例;

14.图11图示根据实施例的尺寸为2的幂的simd实现方式,其中,累加器使用比至乘法器的输入的尺寸大的输入尺寸;

15.图12图示利用矩阵操作电路的系统的实施例;

16.图13图示处理器核流水线的实施例,该处理器核流水线支持使用片的矩阵操作;

17.图14图示处理器核流水线的实施例,该处理器核流水线支持使用片的矩阵操作;

18.图15图示按行为主格式和列为主格式表达的矩阵的示例;

19.图16图示矩阵(片)的使用的示例;

20.图17图示矩阵(片)的使用的方法的实施例;

21.图18图示根据实施例的对片的使用的配置的支持;

22.图19图示将支持的矩阵(片)的描述的实施例;

23.图20(a)-图20(d)图示(多个)寄存器的示例;

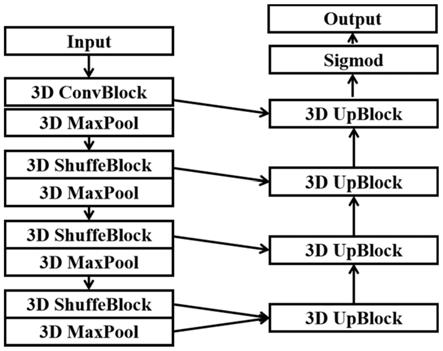

24.图21图示tileloadqpair指令的示例性执行;

25.图22图示执行tileloadqpair指令的处理器的实施例;

26.图23图示tileloadqpair指令的执行的更详细的描述;

27.图24a是描述执行tileloadqpair指令的处理器的实施例的示例性伪代码;

28.图24b是描述由执行tileloadqpair指令的处理器使用的助手函数的实施例的示例性伪代码;

29.图25a-图25b是图示根据本发明的实施例的通用向量友好指令格式及其指令模板的框图;

30.图25a是图示根据本发明的实施例的通用向量友好指令格式及其a类指令模板的框图;

31.图25b是图示根据本发明的实施例的通用向量友好指令格式及其b类指令模板的框图;

32.图26a是图示根据本发明的实施例的示例性专用向量友好指令格式的框图;

33.图26b是图示根据本发明的一个实施例的构成完整操作码字段的具有专用向量友好指令格式的字段的框图;

34.图26c是图示根据本发明的一个实施例的构成寄存器索引字段的具有专用向量友好指令格式的字段的框图;

35.图26d是图示根据本发明的一个实施例的构成扩充操作字段的具有专用向量友好指令格式的字段的框图;

36.图27是根据本发明的一个实施例的寄存器架构的框图;

37.图28a是图示根据本发明的实施例的示例性有序流水线以及示例性寄存器重命名的乱序发布/执行流水线两者的框图;

38.图28b是图示根据本发明的实施例的要包括在处理器中的有序架构核的示例性实施例和示例性的寄存器重命名的乱序发布/执行架构核的框图;

39.图29a-图29b图示更具体的示例性有序核架构的框图,该核将是芯片中的若干逻辑块之一(包括相同类型和/或不同类型的其他核);

40.图29a是根据本发明的实施例的单个处理器核以及它与管芯上互连网络的连接及其第二级(l2)高速缓存的本地子集的框图;

41.图29b是根据本发明的实施例的图29a中的处理器核的一部分的展开图;

42.图30是根据本发明的实施例的可具有超过一个的核、可具有集成存储器控制器、并且可具有集成图形器件的处理器的框图;

43.图31-图34是示例性计算机架构的框图;

44.图31示出根据本发明的一个实施例的系统的框图;

45.图32是根据本发明的实施例的第一更具体的示例性系统的框图;

46.图33是根据本发明的实施例的第二更具体的示例性系统的框图;

47.图34是根据本发明的实施例的芯片上系统(soc)的框图;以及

48.图35是根据本发明的实施例的对照使用软件指令转换器将源指令集中的二进制指令转换成目标指令集中的二进制指令的框图。

具体实施方式

49.在以下描述中,陈述了众多特定细节。然而,应当理解,可在没有这些特定细节的

情况下实践本发明的实施例。在其他实例中,未详细示出公知的电路、结构和技术,以免使对本描述的理解模糊。

50.说明书中对“一个实施例”、“实施例”、“示例实施例”等的引用表明所描述的实施例可以包括特定的特征、结构或特性,但是每个实施例不一定都包括该特定的特征、结构或特性。此外,此类短语不一定是指同一个实施例。此外,当结合实施例描述特定的特征、结构或特性时,认为结合无论是否被明确描述的其他实施例而影响此类特征、结构或特性是在本领域技术人员的知识范围之内的。

51.在许多主流处理器中,处置矩阵是困难的和/或指令密集性任务。例如,可将矩阵的多行置入多个紧缩数据(例如,simd或向量)寄存器中,随后可单独地对矩阵的多行进行操作。例如,取决于数据尺寸,将两个8x2矩阵相加可能要求加载或聚集到四个紧缩数据寄存器中。随后,执行对与来自每个矩阵的第一行对应的紧缩数据寄存器的第一加法,并执行对于来自每个矩阵的第二行对应的紧缩数据寄存器的第二加法。随后,将所得到的紧缩数据寄存器往回分散到存储器。虽然对于小型矩阵,这种场景可能是可接受的,但是对于较大的矩阵,这通常是不可接受的。i.高层级讨论

52.本文中详述的是用于在诸如中央处理单元(cpu)、图形处理单元(gpu)和加速器之类的计算机硬件中支持矩阵操作的机制。矩阵操作利用表示存储器(诸如,寄存器)的一个或多个紧缩区域的2维(2-d)数据。贯穿本说明书,这些2-d数据被称为片。注意,矩阵可以比片小(使用少于所有片),或可利用多个片(矩阵大于任一片的尺寸)。贯穿本说明书,使用矩阵(片)语言来指示使用影响矩阵的片来执行的操作;矩阵是否大于任一片通常是不相关的。

53.每个片可由不同的操作来作用,这些操作诸如本文中详述的那些操作,包括但不限于:矩阵(片)乘法、片加法、片减法、片对角线、片零、片转置、片电极、片广播、片行广播、片列广播、片乘法、片乘法和累加、片移动,等等。此外,在未来可以与这些操作一起使用对诸如使用缩放和/或偏置的操作器的支持,或支持非数值应用,例如,opencl、“本地存储器”、数据压缩/解压缩,等等。

54.存储(诸如,(非易失性和易失性的)存储器、寄存器、高速缓存等)的多个部分被布置为具有不同横向尺度和纵向尺度的片。例如,片可具有横向尺度4(例如,矩阵的四行)和纵向尺度8(例如,矩阵的8列)。典型地,横向尺度是相关的元素尺寸(例如,2位、4位、8位、16位、32位、64位、128位等)。可支持多种数据类型(单精度浮点、双精度浮点、整数等)。a.经配置的片的示例使用

55.在一些实施例中,可配置片参数。例如,可配置给定的片以提供片选项。示例性片选项包括但不限于:片的行数、片的列数、片是否为有效以及片是否由相等尺寸的片对组成。

56.图1a图示经配置的片的实施例。如图所示,应用存储器102的4kb具有存储于其上的1kb的片——片0 104、片1 106、片2 108和片3 110。在该示例中,这4个片不由对组成,并且每个片具有以行和列布置的元素。片t0104和片t1 106具有4字节元素(例如,单精度数据)的k行和n列,其中k=8,且n=32。片t2 108和片t3 110具有8字节元素(例如,双精度数据)的k行和n/2列。由于双精度操作数的宽度是单精度操作数的两倍,因此该配置与用于提

供片选项的调色板一致,将至少4kb的总存储提供给至少4个名称。在操作中,可使用加载操作和存储操作从存储器加载片以及向存储器存储片。取决于所使用的指令编码方案,可用的应用存储器的量以及可用片的尺寸、数量和配置有所不同。

57.图1b图示经配置的片的实施例。如图所示,应用存储器122的4kb可具有存储于其上的2对1kb的片,第一对是片t4l 124和片t4r 126,第二对是片t5l 128和片t5r 130。如图所示,片对被划分为左片和右片。在其他实施例中,片对被划分为偶数片和奇数片。在该示例中,这4个片各自都具有以行和列布置的元素。片t4l 124和片t4r 126具有4字节元素(例如,单精度数据)的k行和n列,其中k=8,且n=32。片t5l 128和片t5r 130具有8字节元素(例如,双精度数据)的k行和n/2列。由于双精度操作数的宽度是单精度操作数的两倍,因此该配置与用于提供片选项的调色板一致,将至少4kb的总存储提供给至少2个名称。图1a的四个片使用4个名称,每一个名称对1kb的片命名,而图1b中的片对可使用2个名称来指定成对的片。在一些实施例中,片指令将成对的片的名称接受为操作数。在操作中,可使用加载操作和存储操作从存储器加载片以及向存储器存储片。取决于所使用的指令编码方案,可用的应用存储器的量以及可用片的尺寸、数量和配置有所不同。

58.在一些实施例中,可配置片参数。例如,“调色板”用于提供片选项。示例性选项包括但不限于:片名称的数量、存储的行中的字节数、片中的行数和列数,等等。例如,片的最大“高度”(行数)可定义为:

59.片最大行=所构造的存储/(调色板名称的数量/每行的字节数)

60.由此,可写入应用,使得名称的固定使用将能够利用跨实现方式的不同存储尺寸。

61.使用片配置(“tileconfig”)指令完成对片的配置,其中,在所选择的调色板中定义特定的片使用。该声明包括要使用的片名称的数量、每个名称(片)的所请求的行数和列数,并且在一些实施例中包括每个片的所请求的数据类型。在一些实施例中,在tileconfig指令的执行期间执行一致性校验,以确定其匹配调色板条目的限制。b.示例性片存储类型

62.图2图示矩阵存储的若干示例。在(a)中,片被存储在存储器中。如图所示,每“行”由四个紧缩数据元素组成。为了达到下一“行”,使用跨步值。注意,行可被连续地存储在存储器中。当片存储不映射底层存储器阵列行宽度时,跨步式存储器访问允许对一行以及随后对下一行的访问。

63.从存储器加载以及向存储器存储典型地是从应用存储器到紧缩的数据行的跨步式访问。示例性tileload和tilestore指令或其他指令将应用存储器引用为加载操作指令中的tile(片)操作数,并且在一些实施例中是可重新开始的,以处置(高达)2*行的页错误、未掩蔽的浮点异常和/或每条指令的中断。

64.在(b)中,矩阵存储在由多个寄存器组成的片中,这些寄存器诸如,紧缩数据寄存器(单指令多数据(simd)或向量寄存器)。在该示例中,片被叠加在三个物理寄存器上。典型地,使用连续的寄存器,然而,情况不必是这样。

65.在(c)中,矩阵被存储在可由在片操作中使用的融合乘法累加(fma)电路访问的非寄存器存储的片中。该存储可在fma内部,或邻近fma。此外,在一些实施例中,如下文所讨论,该存储可用于数据元素,而不是片的整行。

66.经由cpuid报告tmma架构的所支持的参数。在一些实施例中,信息列表包括最大高

度和最大simd尺度。配置tmma架构要求指定每个片的尺度、每个片的元素尺寸以及调色板标识符。通过执行tileconfig指令来完成该配置。

67.tileconfig指令的成功执行启用后续的tile操作器。tilereleaseall指令清除片配置,并禁用tile操作(知道下一tileconfig指令执行)。在一些实施例中,在使用片的上下文切换中使用xsave、xstore等。在一些实施例中,在xsave总使用2个xce0位,一个用于tileconfif元数据,一个位与实际的片有效载荷数据对应。

68.tileconfig不仅配置片使用,还设置状态变量,该状态变量指示在片经配置的情况下程序在代码区域中。实现方式可枚举对可与片区域一起使用的其他指令的限制,诸如,没有对现有寄存器组的使用,等等。

69.退出片区域典型地利用tilereleaseall指令来完成。该指令不取参数并迅速使所有片无效(指示数据元素不再需要任何保存和恢复),并且清除与处于片区域中对应的内部状态。

70.在一些实施例中,片操作将使超出由片配置指定的尺度的任何行和任何列归零。例如,随着每一行被写入,片操作将使超出所配置的列数(将元素的尺寸考虑在内)的数据归零。例如,对于64字节的行以及配置有10行和12列的片,写入fp32元素的操作将以12*4字节向前10行中的每一行写入输出/结果数据,并且使每一行中的其余的4*4字节归零。片操作还对前10个经配置的行之后的任何行完全归零。当使用具有64字节的行的1k的片时,将会有16行,因此,在该示例中,最后6行也将被归零。

71.在一些实施例中,当加载数据时,上下文恢复(例如,xrstor)强制使超出片的所配置的行的数据类型将被维持为零。如果没有有效配置,则所有行被归零。对片数据的xrstor会加载超出那些所配置的列的列中的无用信息。xrstor超出所配置的列数进行清除不应当是可能的,因为不存在与片配置相关联的元素宽度。

72.当将整个tile存储区写入存储器时,上下文保存(例如,xsave)暴露整个tile存储区。如果xrstor将无用数据加载到片的最右边部分中,则将由xsave保存那个数据。对于超出为每个片指定的数量的行,xsave将写入零。

73.在一些实施例中,片指令是可重新开始的。访问存储器的操作允许在页错误之后重新开始。凭借受控制和/或状态寄存器控制的对异常的掩蔽,处理浮点操作的计算指令也允许未掩蔽的浮点异常。

74.为了支持在这些事件之后重新开始指令,指令将信息存储在下文详述的开始寄存器中。ii.矩阵(片)操作系统a.示例性硬件支持

75.图3图示利用矩阵(片)操作加速器的系统的实施例。在该图示中,主机处理器/处理系统301将命令311(例如,矩阵操纵操作,诸如,算术或矩阵操纵操作、或加载和存储操作)传递至矩阵操作加速器307。然而,这以这种方式示出,仅用于讨论的目的。如稍后所详述,加速器307可以是处理核的部分。典型地,作为片操纵操作器指令的命令311将片称为寄存器-寄存器(“reg-reg”)或寄存器-存储器(“reg-mem”)格式。诸如tilestore、tileload、tileconfig等的其他命令不对片执行数据操作。命令可以是供加速器307处置的经解码的指令(例如,微操作)或宏指令。

76.在该示例中,一致性存储器接口303耦合至主机处理器/处理系统301和矩阵操作加速器307,使得它们能够共享存储器。图4和图5示出如何使用矩阵操作加速器来共享存储器的不同实施例。如图4中所示,主机处理器401和矩阵操作加速器405共享同一存储器403。图5图示其中主机处理器501和矩阵操作加速器505不共享存储器,但可访问彼此的存储器的实施例。例如,处理器501可访问片存储器507,并照常利用其主机存储器503。类似地,矩阵操作加速器505可访问主机存储器503,但更典型地使用其自身的存储器507。注意,这些存储器可以是不同类型的。

77.在一些实施例中,矩阵操作加速器307包括耦合至数据缓冲器305的多个fma 309(在一些实现方式中,这些缓冲器305中的一个或多个被存储在如图所示的网格的fma中)。数据缓冲器305对(例如,使用片加载或片存储指令)从存储器加载的片和/或向存储器存储的片进行缓冲。数据缓冲器可以是例如多个寄存器。典型地,这些fma被布置为能够读取和写入片的链式fma309的网格。在该示例中,矩阵操作加速器307用于使用片t0、t1和t2来执行矩阵乘法操作。片中的至少一个片被容纳在fma网格309中。在一些实施例中,操作中的所有片都被存储在fma网格309中。在其他实施例中个,仅子集被存储在fma网格309中。如图所示,t1被容纳,而t0和t2不被容纳。注意,a、b和c是指这些片的矩阵,这些片可以占据或可以不占据片的整个空间。

78.图6图示使用片的矩阵乘法累加(“tmma”)操作的实施例。

79.矩阵(片a 601)的行数与串联的(链式)fma的数量匹配,这些串联的fma包括计算的等待时间。实现方式可自由地在更小高度的网格上再循环,但是计算保持相同。

80.源/目的地向量来自n行的片(片c 605),并且fma的网格611执行n个向量-矩阵操作,从而导致执行片的矩阵乘法的完整指令。片b 603是另一向量源,并将“广播”项提供给每一级中的fma。

81.在操作中,在一些实施例中(存储在片b 603)中的矩阵b的元素跨fma的矩形网格散布。(存储在片a 601中的)矩阵b使其行的元素被转置,以与fma的矩阵网格的列尺度匹配。在网格中的每个fma处,a和b的元素相乘,并被加到(来自图中上方的)被加数,并且传出和被传递至fma的下一行(或最终输出)。

82.单个步骤的等待时间与k(矩阵b的行高)成比例,并且从属的tmma典型地(在单片中或跨片)具有足够的源-目的地行以隐藏该等待时间。实现方式还可跨时间步长分割simd(紧缩数据元素)尺度m(矩阵a的行高),但是这仅改变k乘以的常数。当程序指定比由tmacc枚举的最大值小的k时,实现方式利用“掩蔽”或“早出”来自由地实现此。

83.整个tmma的等待时间与n*k成比例。重复率与n成比例。每条tmma指令的mac的数量为n*k*m。

84.图7图示链式融合乘法累加指令的迭代的执行的子集的实施例。具体而言,图7图示目的地的一个紧缩数据元素位置的迭代的执行电路。在该实施例中,链式融合乘法累加对于多个有符号源进行操作,其中累加器2倍于输入数据尺寸。

85.第一有符号源(源1 701)和第二有符号源(源2 703)各自都有具有四个紧缩数据元素。这些紧缩数据元素中的每一个都存储诸如浮点数据之类的有符号数据。第三有符号源(源3 709)具有两个紧缩数据元素,其中的每一个都存储有符号数据。第一有符号源701的尺寸和第二有符号源703的尺寸是第三有符号源(初始值或先前结果)709的尺寸的一半。

例如,第一有符号源701和第二有符号源703可具有32位的紧缩数据元素(例如,单精度浮点),而第三有符号源709可具有64位的紧缩数据元素(例如,双精度浮点)。

86.在该图示中,仅示出第一有符号源701和第二有符号源703的最高有效的两个紧缩数据元素位置以及第三有符号源709的最高有效的紧缩数据元素位置。当然,还将处理其他紧缩数据元素位置。

87.如图所示,成对地处理紧缩数据元素。例如,使用乘法器电路705将第一有符号源701和第二有符号源703的最高有效的紧缩数据元素位置的数据相乘,并且使用乘法器电路707将第一有符号源701和第二有符号源703的次高有效的紧缩数据元素位置的数据相乘。在一些实施例中,这些乘法器电路705和707重新用于其他紧缩数据元素位置。在其他实施例中,使用附加的乘法器电路,使得并行地处理紧缩数据元素。在一些上下文中,使用尺寸为有符号第三源709的尺寸的通道来完成并行执行。使用加法电路711将这些乘法中的每个乘法的结果相加。

88.(使用不同的加法器713或同一加法器711)将这些乘法结果的加法的结果加到来自有符号源3 709的最高有效紧缩数据元素位置的数据。

89.最终,第二加法的结果被存储到与用来自有符号第三源709的紧缩数据元素位置对应的紧缩数据元素位置中的有符号目的地715中,或者如果有下一迭代,则该第二加法的结果被继续传递到该下一迭代。在一些实施例中,将写掩码应用于此存储,使得如果对应的掩码(位)被置位,则存储发生,如果对应的掩码(位)未被置位,则存储不发生。

90.图8图示链式融合乘法累加指令的迭代的执行的子集的实施例。具体而言,图8图示目的地的一个紧缩数据元素位置的迭代的执行电路。在该实施例中,链式融合乘法累积正对有符号源进行操作,其中,累加器2倍于输入数据的尺寸。

91.第一有符号源(源1 801)和第二有符号源(源2 803)各自都有具有四个紧缩数据元素。这些紧缩数据元素中的每一个都存储诸如整数数据之类的有符号数据。第三有符号源(源3 809)具有两个紧缩数据元素,其中的每一个都存储有符号数据。第一有符号源801的尺寸和第二有符号源803的尺寸是第三有符号源809的尺寸的一半。例如,第一有符号源801和第二有符号源803可具有32位的紧缩数据元素(例如,单精度浮点),而第三有符号源809可具有64位的紧缩数据元素(例如,双精度浮点)。

92.在该图示中,仅示出第一有符号源801和第二有符号源803的最高有效的两个紧缩数据元素位置以及第三有符号源809的最高有效的紧缩数据元素位置。当然,还将处理其他紧缩数据元素位置。

93.如图所示,成对地处理紧缩数据元素。例如,使用乘法器电路805将第一有符号源801和第二有符号源803的最高有效的紧缩数据元素位置的数据相乘,并且使用乘法器电路807将第一有符号源801和第二有符号源803的次高有效的紧缩数据元素位置的数据相乘。在一些实施例中,这些乘法器电路805和807重新用于其他紧缩数据元素位置。在其他实施例中,使用附加的乘法器电路,使得并行地处理紧缩数据元素。在一些上下文中,使用尺寸为有符号第三源(初始值或先前迭代结果)809的尺寸的通道来完成并行执行。使用加法/饱和电路813将多个乘法中的每个乘法的结果加到有符号第三源809。

94.当加法导致过大的值时,加法/饱和(累加器)电路813保留操作数的符号。具体而言,对于多路加法与向目的地或下一迭代的写入之间的无限精度结果,饱和评估发生。当累

加器813是浮点且输入项是整数时,乘积的和以及浮点累加器输入值被转换为无限精度值(数百位的定点数),执行乘法结果与第三输入的加法,并执行向实际累加器类型的单次舍入。

95.无符号饱和意味着输入值被限于那个元素宽度的最大无符号数(全1)。有符号饱和意味着值被限于处于那个元素宽度的最小复数与最大整数之间的范围中(例如,对于字节,范围为从-128(=-2^7)到127(=2^7-1))。

96.最终,加法和饱和校验的结果被存储到与用自有符号第三源809的紧缩数据元素位置对应的紧缩数据元素位置中的有符号结果815中,或者如果有下一迭代,则该结果被继续传递到该下一迭代。在一些实施例中,将写掩码应用于此存储,使得如果对应的掩码(位)被置位,则存储发生,如果对应的掩码(位)未被置位,则存储不发生。

97.图9图示链式融合乘法累加指令的迭代的执行的子集的实施例。具体而言,图9图示目的地的一个紧缩数据元素位置的迭代的执行电路。在该实施例中,链式融合乘法累积正对有符号源和无符号源进行操作,其中,累加器4倍于输入数据的尺寸。

98.第一有符号源(源1 901)和第二无符号源(源2 903)各自都有具有四个紧缩数据元素。这些紧缩数据元素中的每一个都具有诸如浮点数据或整数数据之类的数据。第三有符号源(初始值或结果915)具有存储紧缩数据的紧缩数据元素。第一源901的尺寸和第二源903的尺寸是第三有符号源915的尺寸的四分之一。例如,第一源901和第二源903可具有16位的紧缩数据元素(例如,字),而第三有符号源915可具有64位的紧缩数据元素(例如,双精度浮点或64位整数)。

99.在该图示中,仅示出第一源901和第二源903的最高有效的四个紧缩数据元素位置以及第三有符号源915的最高有效的紧缩数据元素位置。当然,如果还有任何其他紧缩数据元素位置,则还将处理这些紧缩数据元素位置。

100.如图所示,按四元组处理紧缩数据元素。例如,使用乘法器电路905将第一源901和第二源903的最高有效的紧缩数据元素位置的数据相乘,使用乘法器电路907将第一源901和第二源903的次高有效的紧缩数据元素位置的数据相乘,使用乘法器电路909将第一源901和第二源903的第三高有效的紧缩数据元素位置的数据相乘,并且使用乘法器电路911将第一源901和第二源903的最低有效的紧缩数据元素位置的数据相乘。在一些实施例中,在乘法之前,对第一源901的有符号紧缩数据元素进行符号扩展,并且对第二源903的无符号紧缩数据元素进行零扩展。

101.在一些实施例中,这些乘法器电路905-911重新用于其他紧缩数据元素位置。在其他实施例中,使用附加的乘法器电路,使得并行地处理紧缩数据元素。在一些上下文中,使用尺寸为有符号第三源915的尺寸的通道来完成并行执行。使用加法电路911将这些乘法中的每个乘法的结果相加。

102.(使用不同的加法器913或同一加法器911)将这些乘法结果的加法的结果加到来自有符号源9 915的最高有效紧缩数据元素位置的数据。

103.最终,第二加法的结果919被存储到与用自有符号第三源915的紧缩数据元素位置对应的紧缩数据元素位置中的有符号目的地中,或者被传递到下一迭代。在一些实施例中,将写掩码应用于此存储,使得如果对应的掩码(位)被置位,则存储发生,如果对应的掩码(位)未被置位,则存储不发生。

104.图10图示链式融合乘法累加指令的迭代的执行的子集的实施例。具体而言,图10图示目的地的一个紧缩数据元素位置的迭代的执行电路。在该实施例中,链式融合乘法累积正对有符号源和无符号源进行操作,其中,累加器4倍于输入数据的尺寸。

105.第一有符号源(源1 1001)和第二无符号源(源2 1003)各自都有具有四个紧缩数据元素。这些紧缩数据元素中的每一个都存储诸如浮点数据或整数数据之类的数据。第三有符号源(初始值或先前结果1015)具有存储紧缩数据的紧缩数据元素。第一源1001的尺寸和第二源1003的尺寸是第三有符号源1015的尺寸的四分之一。例如,第一源1001和第二源1003可具有16位的紧缩数据元素(例如,字),而第三有符号源1015可具有64位的紧缩数据元素(例如,双精度浮点或64位整数)。

106.在该图示中,仅示出第一源1001和第二源1003的最高有效的四个紧缩数据元素位置以及第三有符号源1015的最高有效的紧缩数据元素位置。当然,如果还有任何其他紧缩数据元素位置,则还将处理这些紧缩数据元素位置。

107.如图所示,按四元组处理紧缩数据元素。例如,使用乘法器电路1005将第一源1001和第二源1003的最高有效的紧缩数据元素位置的数据相乘,使用乘法器电路1007将第一源1001和第二源1003的次高有效的紧缩数据元素位置的数据相乘,使用乘法器电路1009将第一源1001和第二源1003的第三高有效的紧缩数据元素位置的数据相乘,并且使用乘法器电路1011将第一源1001和第二源1003的最低有效的紧缩数据元素位置的数据相乘。在一些实施例中,在乘法之前,对第一源1001的有符号紧缩数据元素进行符号扩展,并且对第二源1003的无符号紧缩数据元素进行零扩展。

108.在一些实施例中,这些乘法器电路1005-1011重新用于其他紧缩数据元素位置。在其他实施例中,使用附加的乘法器电路,使得并行地处理紧缩数据元素。在一些上下文中,使用尺寸为有符号第三源1015的尺寸的通道来完成并行执行。使用加法/饱和电路1013将这些乘法结果的加法的结果加到来自有符号源3 1015的最高有效紧缩数据元素位置的数据。

109.当加法导致对于有符号饱和过大或过小的值时,加法/饱和(累加器)电路1013保留操作数的符号。具体而言,对于多路加法与向目的地的写入之间的无限精度结果,饱和评估发生。当累加器1013是浮点且输入项是整数时,乘积的和以及浮点累加器输入值被转换为无限精度值(数百位的定点数),执行乘法结果与第三输入的加法,并执行向实际累加器类型的单次舍入。

110.最终,加法和饱和校验的结果1019被存储到与用自有符号第三源1015的紧缩数据元素位置对应的紧缩数据元素位置中的有符号目的地中,或者被传递到下一迭代。在一些实施例中,将写掩码应用于此存储,使得如果对应的掩码(位)被置位,则存储发生,如果对应的掩码(位)未被置位,则存储不发生。

111.图11图示根据实施例的尺寸为2的幂的simd实现方式,其中,累加器使用比至乘法器的输入的尺寸大的输入尺寸。注意,(至乘法器的)源和累加器值可以是有符号值或无符号值。对于具有2x输入尺寸的累加器(换言之,累加器输入值的尺寸是源的紧缩数据元素的尺寸的2倍),表1101图示不同的配置。对于字节尺寸的源,累加器使用尺寸为16位的字或半精度浮点(hpfp)值。对于字尺寸的源,累加器使用尺寸为32位的32位整数或单精度浮点(spfp)值。对于spfp或32位整数尺寸的源,累加器使用尺寸为64位的64位整数或双精度浮

点(spfp)值。

112.对于具有4x输入尺寸的累加器(换言之,累加器输入值的尺寸是源的紧缩数据元素的尺寸的4倍),表1103图示不同的配置。对于字节尺寸的源,累加器使用尺寸为32位的32位整数或单精度浮点(spfp)值。对于字尺寸的源,累加器使用尺寸为64位的64位整数或双精度浮点(dpfp)值。

113.对于具有8x输入尺寸的累加器(换言之,累加器输入值的尺寸是源的紧缩数据元素的尺寸的8倍),表1105图示配置。对于字节尺寸的源,累加器使用64位整数。

114.如之前所提示,矩阵操作电路可被包括在核中,或可作为外部加速器。图12图示利用矩阵操作电路的系统的实施例。在该图示中,多个实体与环形互连1245耦合。

115.多个核1201、1203、1205和1207提供基于非片的指令支持。在一些实施例中,矩阵操作电路1251设于核1203中,在其他实施例中,矩阵操作电路1211和1213是在环形互连1245上可访问的。

116.此外,提供一个或多个存储器控制器1223-1225,以代表核和/或矩阵操作电路来与存储器1233和1231通信。

117.图13图示处理器核流水线的实施例,该处理器核流水线支持使用片的矩阵操作。分支预测和解码电路1303执行对来自存储在指令存储1301中的指令的分支预测、对这些指令的解码和/或分支预测和解码两者。例如,本文中详述的指令可存储在指令存储中。在一些实现方式中,分开的电路用于分支预测,并且在一些实施例中,至少一些指令被解码为一个或多个微操作、微代码进入点、微指令、其他指令或使用微代码1305的其他控制信号。分支预测和解码电路1303可使用各种不同的机制来实现。合适机制的示例包括但不限于查找表、硬件实现、可编程逻辑阵列(pla)、微代码只读存储器(rom)等。

118.分支预测和解码电路1303耦合至重命名/分配器电路1307,在一些实施例中,该重命名/分配器电路1307耦合至调度器电路1309。在一些实施例中,这些电路通过执行以下步骤中的一个或多个来提供寄存器重命名、寄存器分配和/或调度功能:1)将逻辑操作数值重命名为物理操作数值(例如,一些实施例中的寄存器别名表);2)将状态位和标志分配给经解码的指令;以及3)(例如,在一些实施例中,使用预留站)调度经解码的指令供在指令池外部的执行电路上执行。

119.(多个)调度器电路1309表示任何数量的不同调度器,包括预留站、中央指令窗等。(多个)调度器单元调度器电路1309耦合至(多个)物理寄存器堆1315或包括(多个)物理寄存器堆1315。(多个)物理寄存器堆1315中的每一个表示一个或多个物理寄存器堆,其中不同的物理寄存器堆存储一种或多种不同的数据类型,诸如,标量整数、标量浮点、紧缩整数、紧缩浮点、向量整数、向量浮点、状态(例如,作为要执行的下一指令的地址的指令指针)、片,等等。在一个实施例中,(多个)物理寄存器堆1315包括向量寄存器电路、写掩码寄存器电路和标量寄存器电路。这些寄存器电路可提供架构向量寄存器、向量掩码寄存器和通用寄存器。(多个)物理寄存器堆1315被引退单元1317覆盖,以图示可实现寄存器重命名和乱序执行的各种方式(诸如,使用(多个)重排序缓冲器和(多个)引退寄存器堆、使用(多个)未来文件(future file)、(多个)历史缓冲器、(多个)引退寄存器堆、使用寄存器映射和寄存器池,等等)。引退电路1317和(多个)物理寄存器堆1315耦合至(多个)执行电路1311。

120.尽管在乱序执行的上下文中描述了寄存器重命名,但应当理解,可以在有序架构

中使用寄存器重命名。虽然处理器的所图示的实施例也可包括分开的指令和数据高速缓存单元以及共享的l2高速缓存单元,但替代实施例也可具有用于指令和数据两者的单个内部高速缓存,诸如例如,第一级(l1)内部高速缓存、或多个级别的内部高速缓存。在一些实施例中,该系统可包括内部高速缓存和在核和/或处理器外部的外部高速缓存的组合。替代地,所有高速缓存都可在核和/或处理器的外部。

121.执行电路1311包括一个或多个执行电路1321、1323和1327的集合以及一个或多个存储器访问电路1325的集合。执行电路1321、1323和1327执行各种操作(例如,移位、加法、减法、乘法)并对各种数据类型(例如,标量浮点、紧缩整数、紧缩浮点、向量整数、向量浮点)执行。尽管一些实施例可以包括专用于特定功能或功能集的多个执行单元,但其他实施例可包括仅一个执行单元或全部执行所有功能的多个执行单元。标量电路1321执行标量操作,向量/simd电路1323执行向量/simd操作,并且矩阵操作电路1327执行本文中详述的矩阵(片)操作。

122.作为示例,示例性寄存器重命名的、乱序发布/执行核架构可以如下所述地实现流水线:1)指令取出电路执行取出和长度解码级;2)分支和解码电路1303执行解码级;3)重命名/分配器电路1307执行分配级和重命名级;4)调度器电路1309执行调度级;5)(耦合至或被包括在调度器电路1309和重命名/分配电路1307和存储器单元中的)(多个)物理寄存器堆执行寄存器读取/存储器读取级;执行电路1311执行执行级;6)存储器单元和(多个)物理寄存器堆单元执行写回/存储器写入级;7)各个单元可涉及异常处置级;以及8)引退单元和(多个)物理寄存器堆单元执行提交级。

123.核可支持一个或多个指令集(例如,x86指令集(具有与较新版本一起添加的一些扩展);加利福尼亚州桑尼维尔市的mips技术公司的mips指令集;加利福尼州桑尼维尔市的arm控股公司的arm指令集(具有诸如neon等任选附加扩展)),其中包括本文中描述的(多条)指令。在一个实施例中,核1390包括用于支持紧缩数据指令集扩展(例如,avx1、avx2)的逻辑,由此允许许多多媒体应用所使用的操作利用紧缩数据来执行。

124.应当理解,核可支持多线程化(执行两个或更多个并行的操作或线程的集合),并且可以按各种方式来完成该多线程化,此各种方式包括时分多线程化、同步多线程化(其中单个物理核为物理核正在同步多线程化的各线程中的每一个线程提供逻辑核)、或其组合(例如,时分取出和解码以及此后诸如用超线程化技术来同步多线程化)。

125.图14图示处理器核流水线的实施例,该处理器核流水线支持使用片的矩阵操作。分支预测和解码电路1403执行对来自存储在指令存储1401中的指令的分支预测、对这些指令的解码和/或分支预测和解码两者。例如,本文中详述的指令可存储在指令存储中。在一些实现方式中,分开的电路用于分支预测,并且在一些实施例中,至少一些指令被解码为一个或多个微操作、微代码进入点、微指令、其他指令或使用微代码1405的其他控制信号。分支预测和解码电路1403可使用各种不同的机制来实现。合适机制的示例包括但不限于查找表、硬件实现、可编程逻辑阵列(pla)、微代码只读存储器(rom)等。

126.分支预测和解码电路1403耦合至重命名/分配器电路1407,在一些实施例中,该重命名/分配器电路1407耦合至调度器电路1409。在一些实施例中,这些电路通过执行以下一个或多个步骤来提供寄存器重命名、寄存器分配和/或调度功能:1)将逻辑操作数值重命名为物理操作数值(例如,一些实施例中的寄存器别名表);2)将状态位和标志分配给经解码

的指令;以及3)(例如,在一些实施例中,使用预留站)调度经解码的指令用在指令池外部的执行电路上执行。

127.(多个)调度器电路1409表示任何数量的不同调度器,包括预留站、中央指令窗等。(多个)调度器单元调度器电路1409耦合至(多个)物理寄存器堆1415或包括(多个)物理寄存器堆1415。(多个)物理寄存器堆1415中的每一个表示一个或多个物理寄存器堆,其中不同的物理寄存器堆存储一种或多种不同的数据类型,诸如,标量整数、标量浮点、紧缩整数、紧缩浮点、向量整数、向量浮点、状态(例如,作为要执行的下一指令的地址的指令指针)、片,等等。在一个实施例中,(多个)物理寄存器堆1415包括向量寄存器电路、写掩码寄存器电路和标量寄存器电路。这些寄存器电路可提供架构向量寄存器、向量掩码寄存器和通用寄存器。(多个)物理寄存器堆1415被引退单元1417覆盖,以图示可实现寄存器重命名和乱序执行的各种方式(诸如,使用(多个)重排序缓冲器和(多个)引退寄存器堆、使用(多个)未来文件(future file)、(多个)历史缓冲器、(多个)引退寄存器堆、使用寄存器映射和寄存器池,等等)。引退电路1417和(多个)物理寄存器堆1415耦合至(多个)执行电路1411。

128.尽管在乱序执行的上下文中描述了寄存器重命名,但应当理解,可以在有序架构中使用寄存器重命名。虽然处理器的所图示的实施例也可包括分开的指令和数据高速缓存单元以及共享的l2高速缓存单元,但替代实施例也可具有用于指令和数据两者的单个内部高速缓存,诸如例如,第一级(l1)内部高速缓存、或多个级别的内部高速缓存。在一些实施例中,该系统可包括内部高速缓存和在核和/或处理器外部的外部高速缓存的组合。替代地,所有高速缓存都可在核和/或处理器的外部。

129.执行电路141411包括一个或多个执行电路1427的集合以及一个或多个存储器访问电路1325的集合。执行电路1427执行本文中详述的向量(片)操作。

130.作为示例,示例性寄存器重命名的、乱序发布/执行核架构可以如下所述地实现流水线:1)指令取出电路执行取出和长度解码级;2)分支和解码电路1403执行解码级;3)重命名/分配器电路1407执行分配级和重命名级;4)调度器电路1409执行调度级;5)(耦合至或被包括在调度器电路1409和重命名/分配电路1407和存储器单元中的)(多个)物理寄存器堆执行寄存器读取/存储器读取级;执行电路1411执行执行级;6)存储器单元和(多个)物理寄存器堆单元执行写回/存储器写入级;7)各个单元可涉及异常处置级;以及8)引退单元和(多个)物理寄存器堆单元执行提交级。

131.核可支持一个或多个指令集(例如,x86指令集(具有与较新版本一起添加的一些扩展);加利福尼亚州桑尼维尔市的mips技术公司的mips指令集;加利福尼州桑尼维尔市的arm控股公司的arm指令集(具有诸如neon等任选附加扩展)),其中包括本文中描述的(多条)指令。在一个实施例中,核1490包括用于支持紧缩数据指令集扩展(例如,avx1、avx2)的逻辑,由此允许许多多媒体应用所使用的操作利用紧缩数据来执行。

132.应当理解,核可支持多线程化(执行两个或更多个并行的操作或线程的集合),并且可以按各种方式来完成该多线程化,此各种方式包括时分多线程化、同步多线程化(其中单个物理核为物理核正在同步多线程化的各线程中的每一个线程提供逻辑核)、或其组合(例如,时分取出和解码以及此后诸如用超线程化技术来同步多线程化)。b.布局

133.贯穿本说明书,使用行为主的数据布局来表达数据。列为主的用户应当根据项的

定向来变换这些项。图15图示按行为主格式和列为主格式表达的矩阵的示例。如图所示,矩阵a是2x3矩阵。当该矩阵按行为主的格式存储时,行的数据元素是连续的。当该矩阵按列为主的格式存储时,列的数据元素是连续的。a

t

*b

t

=(ba)

t

是矩阵的公知属性,其中,上标t表示转置。按行为主的数据那样来读取列为主的数据导致看起来像转置矩阵的矩阵。

134.在一些实施例中,在硬件中利用行为主的语义,并且列为主的数据将交换操作数顺序并使结果是矩阵的转置,但是对于从存储器的后续列为主的读取,其是正确的非转置矩阵。

135.例如,如果具有两个要相乘的列为主的矩阵:a b g i k ag bh ai bj ak blc d*h j l=cg dh ci dj ck dle f eg fh ei fj ek fl(3x2) (2x3) (3x3)

136.数据矩阵将按如下方式被存储在线性存储器中(列为主):a c e b d f以及g h i j k l.

137.以尺度2x3和3x2将那些矩阵读取为列为主的,则它们表现为:a c e和g hb d f i jk l

138.交换顺序和矩阵乘法:g h a c e ag bh cg dh eg fhi j*b d f=ai bj ci dj ei fjk l ak bl ck dl ek fl转置矩阵移出,并且随后可按行为主的顺序被存储:ag bh cg dh eg fh ai bj ci dj ei fj ak bl ck dl ek fl并且在后续的列为主的计算中被使用,其是正确的未转置矩阵:ag bh ai bj ak blcg dh ci dj ck dleg fh ei fj ek fliii.示例性使用

139.图16图示矩阵(片)的使用的示例。在该示例中,矩阵c 1601包括两个片,矩阵a 1603包括一个片,并且矩阵b 1605包括两个片。该图示出用于计算矩阵乘法的算法的内循环的示例。在该示例中,来自矩阵c 1601的两个结果片tmm0和tmm1用于将中间结果累加。当来自矩阵b 1603的一个片(tmm2)乘以来自矩阵b 1605的两个片时,这个片被重复使用2次。指针用于加载来自箭头所指示方向的新a片和两个新b片。未示出的外循环调整用于c片的指针。

140.如图所示的示例性代码包括片配置指令的使用,并且被执行以配置片使用,加载片,用于处理片的循环,将片存储到存储器,并释放片使用。

141.图17图示矩阵(片)的使用的实施例。在1701处,配置片使用。例如,执行tileconfig指令以配置片使用,包括设置每个片的行数和列数。典型地,在1703处,从存储器加载至少一个矩阵(片)。在1705处,使用矩阵(片)来执行至少一个矩阵(片)操作。在1707处,将至少一个矩阵(片)向外存储到存储器,并且在1709处,上下文切换可发生。iv.示例性配置

142.a.片配置硬件支持

143.如上文所讨论,片使用通常需要在使用前进行配置。例如,可能不需要完全使用所有的行和列。在一些实施例中不配置这些行和列不仅节省了功率,而且可使用配置来判定操作是否将生成错误。例如,如果m和l不相同,则(nxm)*(l*n)形式的矩阵乘法通常将不起作用。

144.在使用利用片的矩阵之前,在一些实施例中,将配置片支持。例如,配置每个片有多少行和多少列、将使用的片,等等。tileconfig指令是对计算机自身的改进,因为它提供对配置计算机以使用(作为处理器核的部分的、或作为外部设备的)矩阵加速器的支持。具体而言,tileconfig指令的执行使得配置从存储器被检取,并被应用于矩阵加速器内的矩阵(片)设置。

145.i.片使用配置

146.图18图示根据实施例的对片的使用的配置的支持。存储器1801包含将被支持的矩阵(片)的描述1803。

147.处理器/核1805的执行电路1811将片描述1803的多个方面存储到片配置1817中。片配置1817详述配置了用于调色板的什么片(每个片中的行数和列数)以及矩阵支持在使用中的标记。具体而言,指令执行资源1811配置成按片配置1817所指定来使用片。指令执行资源还可包括用于指示片使用的机器专用寄存器或配置寄存器。还设置附加的值,诸如,使用中值和开始值。片配置1817利用一个或多个寄存器1819来存储片使用和配置信息。

148.图19图示将支持的矩阵(片)的描述的实施例。这是将应sttilecfg指令的执行而被存储的描述。在该示例中,每个字段为字节。在字节[0]中,存储调色板id 1901。调色板id用于对调色板表1813进行索引,该调色板表1813如由配置所定义来根据调色板id存储片中的字节数以及与该id相关联的片的每行的字节。

[0149]

字节1存储将被存储在“startrow”寄存器1903中的值,并且字节2存储将被存储在“startp”寄存器1905中的值。为了支持在这些事件后重新开始指令,这些指令将信息存储在这些寄存器中。为了支持在诸如上文详述的那些事件之类的中断事件之后重新开始指令,这些指令将信息存储在这些寄存器中。startrow值指示应当被用于重新开始的行。startp值指示当对被使用时用于存储操作的行内的位置,并且在一些实施例中,该startp值指示(对的较低片中的)行的下半部分或(对的较高片中的)行的上半部分。一般而言,不需要行(列)中的该位置。

[0150]

成功地执行矩阵(片)指令将会将startrow和startp两者设置为零,tileconfig和sttilecfg是例外。

[0151]

在不重新开始被中断的矩阵(片)的任何时刻,使startrow和startp值归零是软件的职责。例如,未掩蔽的浮点异常处置程序可决定在软件中完成操作,并且将程序计数器值改变为另一指令,通常是下一指令。在这种情况下,在恢复程序之前,软件异常处置程序必

须使由操作系统呈现给该软件异常处置程序的异常中的startrow和startp值归零。操作系统随后将使用恢复指令来重新加载那些值。

[0152]

字节3存储片的对的指示(每片1b)1907。

[0153]

字节16-17存储片0的行数1913和列数1915,字节18-19存储片1的行数和列数,以此类推。换言之,每一2字节组指定片的行数和列数。如果2字节的组不用于指定参数,则它们应当具有值零。为比实现限制或调色板限制更多的片指定片参数导致错误。未配置的片用0行0列被设置为初始状态。

[0154]

最终,存储器中的配置通常以诸如用于若干连续字节的全零之类的结尾描述结束。

[0155]

ii.示例性片和片配置存储

[0156]

图20(a)-图20(d)图示(多个)寄存器1819的示例。图20(a)图示多个寄存器1819。如图所示,每个片(tmm0 2001...tmmn 2003)具有分开的寄存器,其中每个寄存器存储那个特定片的行尺寸和列尺寸。startp和startrow被存储在分开的寄存器2011和2013中。对一个或多个状态寄存器2015置位(例如,tiles_configured=1)以指示片经配置以供使用。

[0157]

图20(b)图示多个寄存器1819。如图所示,每个片具有用于其行和其列的分开的寄存器。例如,tmm0行配置2021、tmm0列配置2023、startp和startrow被存储在分开的寄存器2011和2013中。对一个或多个状态寄存器2015置位(例如,tiles_configured=1)以指示片经配置以供使用。

[0158]

图20(c)图示单个寄存器1819。如图所示,该寄存器将片配置(每片的行和列)2031、startp 2011和startrow 2013存储在作为紧缩数据寄存器的单个寄存器中。对一个或多个状态寄存器2015置位(例如,tiles_configured=1)以指示片经配置以供使用。

[0159]

图20(d)图示多个寄存器1819。如图所示,单个寄存器存储片配置(每片的行和列)2031。startp和startrow被存储在分开的寄存器2011和2013中。对一个或多个状态寄存器2015置位(例如,tiles_configured=1)以指示片经配置以供使用。

[0160]

构想了其他组合,诸如,将起始寄存器组合到单个寄存器中,在该单个寄存器中,这些起始寄存器被分开显示,等等。b.片加载对

[0161]

公共矩阵操作例如从存储在一组寄存器中的片加载到存储在存储器中的片。特定使用的示例是将源矩阵(片)的行和列中的矩阵元素加载到相同尺寸的目的地矩阵的对应元素位置。本文中详述的是tileloadqpair指令及其执行的实施例。tileloadqpair指令是对计算机本身的改进,因为它提供了对用单条指令加载矩阵(片)内的数据的支持。具体地,tileloadqpair指令的执行使得源矩阵(片)的左片和右片(或者偶数片和奇数片)的元素被加载到目的地矩阵(片)的左片和右片(或者偶数片和奇数片)的对应元素位置。要加载的数据元素的尺寸可以取决于指令和片支持而有所不同。示例性尺寸包括但不限于:16位、32位、64位、128位、256位等。然而,tileloadqpair指令对四字元素操作。在一些实施例中,将目的地矩阵(片)的、不具有在源矩阵(片)中的对应列的行的元素归零。i.示例性执行

[0162]

图21图示出tileloadqpair指令的示例性执行。tileloadqpair指令格式包括用于操作码、源片标识符“tsrc”和目的地片标识符“tdest”的字段。所标识的源片和目的地片中

的每一个具有k行和n列,并且pair(对)参数设置为true(真)。所标识的源片和目的地片具有4字节的四字元素,如操作码中的“q”所指示。如图所示,由执行电路2108接收经解码的tileloadqpair指令2102,在一些实施例中,执行电路2108使用fma的网格2110从所标识的源矩阵的左片和右片的对应元素位置加载所标识的目的地矩阵的左片和右片的每个元素。

[0163]

在一些实施例中,该执行从第一行开始一次对所标识的目的地矩阵的一行进行操作。在一些实施例中,该执行一次对在正被操作的行的一个c字节的块进行操作。块中的字节数c可以变化为1字节与整行字节之间的任何值。在一些实施例中,执行电路2108在每次(对行操作和块操作中的任一者或对这两者的)加载操作之后定期保存状态,使得执行电路2108在执行被操作期间发生的错误中断的情况下可以在该错误解决后恢复执行,并从该执行停止之处继续执行。在此类实施例中,所保存的状态包括行指针、块指针、字节指针和元素指针中的一个或多个,以标识正被加载的当前目的地片元素。

[0164]

如前文所详述,左源矩阵(片)、右源矩阵(片)、左目的地矩阵(片)和右目的地矩阵(片)可以被加载在寄存器的集合、存储器中的位置或者执行电路可访问的其他存储中。然而,如图所示,源矩阵(片)的所标识的左片2104和右片2106被加载在应用存储器2112中,并且所标识的目的地矩阵(片)的左片2114和右片2116被加载在寄存器的集合中。

[0165]

如图所示,指令2102包括tileloadqpair操作码、目的地片标识符“tdest”和源片标识符“tsrc”。所标识的源矩阵(片)和目的地矩阵(片)包括左片和右片(或者偶数片和奇数片),每个片具有k=8行、n=16列,且具有四字节元素尺寸。然后,所标识的左源矩阵(片)和右源矩阵(片)一起使用1kb的存储(2侧

×

8行

×

16列

×

4b元素)。

[0166]

在一些实施例中,矩阵(片)被配置为仅使用可能的行和列的子集。例如,矩阵(片)可以具有最多16行和16列以供使用,但是仅使用每个矩阵(片)的4行和4列。通常通过在矩阵(片)使用之前执行配置指令来完成每个矩阵(片)的配置。在该示例中,存在可能的n列和k行。ii.(多个)示例性指令格式

[0167]

tileloadqpair指令的格式的实施例是tileloadqpair tdest,tsr。在一些实施例中,tileloadqpair是指令的操作码助记符,其中q表示数据元素尺寸是四字。在一些实施例中,tdest字段是r/m值(诸如,图25a-图25b的2546),tsrc字段是图25a-图25b的reg 2544,并且数据元素尺寸在图25a-图25b的2564中找到。

[0168]

在一些实施例中,指令的编码包括间接地标识存储器中的多个经索引的目的地位置的比例-索引-基址(sib)型存储器寻址操作数(例如,图25a-图25b的字段2550)。在一个实施例中,sib型存储器操作数可包括标识基址寄存器的编码。基址寄存器的内容可表示存储器中的基址,存储器中的特定目的地位置的地址可通过该基址来计算。例如,基址可以是用于扩展向量指令的潜在的目的地位置的块中的第一位置的地址。在一个实施例中,sib型存储器操作数可包括标识索引寄存器的编码。索引寄存器的每个元素可指定索引或偏移值,该索引或偏移值能用于通过基址来计算潜在的目的地地址的块内的相应目的地地址的地址。在一个实施例中,sib型存储器操作数可包括指定在计算相应目的地地址时要用于每个索引值的比例因子的编码。例如,如果比例因子值4被编码在sib型存储器操作数中,则从索引寄存器的元素获得的每个索引值乘以4,且随后加到基址,以计算目的地地址。

[0169]

在一个实施例中vm32{x,y,z}形式的sib型存储器操作数可标识使用sib型存储器

寻址指定的存储器操作数的向量阵列。在该示例中,使用共同的基址寄存器、恒定的比例因子和包含各自都为32位的索引值的各个元素的向量索引寄存器来指定存储器地址的阵列。向量索引寄存器可以是128位的(例如,xmm)寄存器(vm32x)、256位的(例如,ymm)寄存器(vm32y)或512位的(例如,zmm)寄存器(vm32z)。在另一实施例中vm64{x,y,z}形式的sib型存储器操作数可标识使用sib型存储器寻址指定的存储器操作数的向量阵列。在该示例中,使用共同的基址寄存器、恒定的比例因子和包含各自都为64位的索引值的各个元素的向量索引寄存器来指定存储器地址的阵列。向量索引寄存器可以是128位的(例如,xmm)寄存器(vm64x)、256位的(例如,ymm)寄存器(vm64y)或512位的(例如,zmm)寄存器(vm64z)。iii.执行的(多个)示例性方法

[0170]

图22图示了执行tileloadqpair指令的处理器的实施例。在2201处,取出指令。例如,取出具有用于操作码、源标识符和目的地标识符的字段的tileloadqpair指令,该源标识符和目的地标识符标识各自具有等于true的pair参数的源矩阵(片)和目的地矩阵(片)。在一些实施例中,由取出电路从指令高速缓存取出指令。tileloadqpair指令的操作码指示从所标识的源矩阵(片)的左矩阵(片)和右矩阵(片)的对应紧缩数据元素位置加载所标识的目的地矩阵(片)的左矩阵(片)和右矩阵(片)的紧缩四字数据元素位置。tileloadqpair指令的操作码包括“q”以将片元素中的每一个的尺寸指定为四字。

[0171]

在2203处,对取出的指令进行解码。例如,由诸如本文中详述的解码电路对取出的tileloadqpair指令进行解码。

[0172]

在2205处,(根据需要)调度经解码的指令的执行,这是可选步骤(如由其虚线边框所指示),这体现在该步骤可以在不同的时间发生,或者根本不发生。

[0173]

在2207处,由诸如本文中详述的执行电路(硬件)执行经解码的tileloadqpair指令。对于tileloadqpair指令,该执行将使执行电路从所标识的源矩阵的左片和右片的对应元素位置加载所标识的目标矩阵的左片和右片的每个元素,其中该执行从第一行开始一次对所标识的目的地矩阵的一行进行操作。

[0174]

在一些实施例中,在2209处,提交或引退该指令,这是可选步骤(如由其虚线边框所示),这体现在该步骤可以在不同的时间发生,或者根本不发生。

[0175]

图23图示了tileloadqpair指令的执行的更详细的描述。通常,这由诸如上文详述的执行电路执行。

[0176]

在2302处,判定是否以下所有条件都为真:1)是否存在至少一个经配置的矩阵(片)?2)所标识的源矩阵(片)和目的地矩阵(片)是否具有设置为true的valid(有效)参数?以及3)所标识的源矩阵(片)和目的地矩阵(片)是否具有设置为true的pair参数?当这些条件中的任一个不为真时,在2304处生成错误。

[0177]

当在2302处测试的所有条件都为真时,执行电路在2306处从第一行开始,在所标识的目的地矩阵(片)的左矩阵(片)和右矩阵(片)的每个行m上循环。在2308处,对于每一行,执行电路从所标识的源矩阵的对应行加载该行的每个元素。在2310处,执行电路递增m,并判定是否有任何行剩余,并且如果是,则继续到2306处以对下一行进行操作。但是当在2310处的判定指示没有行剩余时,该过程结束。iv.示例性伪代码

[0178]

图24a是描述执行tileloadqpair指令的处理器的实施例的示例性伪代码。如伪代

码2400中所示,tileloadqpair指令包括操作码、tileloadqpair、目的地矩阵(片)标识符“tdest”以及源矩阵(片)标识符“tsib”,该源矩阵(片)标识符“tsib”是用于标识存储器中的目的地矩阵(片)的sib型的存储器操作数。如果tdest和tsib中的任何一个具有未设置为true的valid和/或pair参数,则生成错误。包含在操作码中的字母“q”指示源矩阵(片)和目的地矩阵(片)具有四字尺寸的元素。如图所示,如果三个错误校验中的任何一个失败,则伪代码2400首先使执行电路生成错误。随后,伪代码使得处理器在初始化存储器起始地址、跨步值和字节数之后,在所标识的目的地矩阵(片)的每一行上循环。在每一行处,处理器将字节行从起始存储器地址写入所标识的目的地矩阵(片)。

[0179]

图24b是描述由执行tileloadqpair指令的处理器使用的助手函数的实施例的示例性伪代码。伪代码2450定义“write_row_and_zero(treg,r,data,nbytes)”函数。伪代码2452定义“zero_upper_rows(treg,r)”函数。伪代码2454定义“zero_tileconfig_start()”函数。

[0180]

图24a和图24b中的伪代码凭借该伪代码的所包括的函数名称和变量名称来自文档化。进一步示例

[0181]

示例1提供一种处理器,包括:解码电路,用于对加载矩阵对指令解码,该记载矩阵对指令具有用于操作码、源标识符和目的地标识符的字段,该标识符和目的地标识符用于分别标识源矩阵和目的地矩阵,每个矩阵都具有等于真的pair参数;以及执行电路,该执行电路用于执行经解码的加载矩阵对指令,以分别从所标识的源矩阵的左片和右片的对应元素位置加载所标识的目的地矩阵的左片和右片的每个元素,其中该执行从第一行开始一次对所标识的目的地矩阵的一行进行操作。

[0182]

示例2包括示例1的示例性处理器的实体,其中该执行电路还用于在确定以下少一项时生成错误:经配置的片的数量等于零;所标识的源矩阵和目的地矩阵中的至少一个的pair参数未被设置为真;以及所标识的源矩阵和目的地矩阵中的至少一个的valid参数未被设置为真。

[0183]

示例3包括示例1的示例性处理器的实体,其中该执行电路还用于在对所标识的目的地的每一行进行操作之后保存状态,执行电路还用于:当执行被错误中断时,继续从该错误之前该执行离开之处执行经解码的加载矩阵对指令;其中所保存的状态包括行指针。

[0184]

示例4包括示例1的示例性处理器的实体,其中执行电路还用于一次对所标识的目的地矩阵的每一行的一个字节块进行操作,执行电路还用于在对每个块进行操作之后保存状态,执行电路还用于:当执行被错误中断时,继续从该错误之前该执行停止处执行经解码的加载矩阵对指令;其中所保存的状态包括行指针、块指针、元素指针和字节指针中的一个或多个。

[0185]

示例5包括示例1-4中任一个示例的示例性处理器的实体,其中所标识的左源矩阵和右源矩阵各自是用于表示矩阵的寄存器的集合。

[0186]

示例6包括示例1-4中任一个示例的示例性处理器的实体,其中所标识的左源矩阵和右源矩阵各自是用于表示矩阵的多个存储器位置。

[0187]

示例7包括示例1-4中任一个示例的示例性处理器的实体,其中所标识的左目的地矩阵和右目的地矩阵各自是用于表示矩阵的寄存器的集合。

[0188]

示例8包括示例1-4中任一个示例的示例性处理器的实体,其中所标识的左目的地矩阵和右目的地矩阵各自是用于表示矩阵的多个存储器位置。

[0189]

示例9包括示例1-4中任一个示例的示例性处理器的实体,其中操作码还包括元素尺寸标识符,该元素尺寸标识符用于指定所标识的左源矩阵、右源矩阵、左目的地矩阵和右目的地矩阵的每个数据元素的元素尺寸,其中该元素尺寸是16位、32位、64位、128位和256位中的一个。

[0190]

示例10包括示例1-4中任一个示例的示例性处理器的实体,其中执行电路还用于将所标识的左目的地矩阵和右目的地矩阵的任何剩余的经配置的行和列中的任何数据元素归零。

[0191]

示例11提供一种方法,包括:由解码电路对记载矩阵对指令解码,该加载矩阵对指令具有用于操作码、源标识符和目的地标识符的字段,该源标识符和目的地标识符用于分别标识源矩阵和目的地矩阵,每个矩阵都具有等于真的pair参数;以及由执行电路执行经解码的加载矩阵对指令,以分别从所标识的源矩阵的左片和右片的对应元素位置加载所标识的目的地矩阵的左片和右片的每个元素,其中该执行从第一行开始一次对所标识的目的地矩阵的一行进行操作。

[0192]

示例12包括示例11的示例性方法的实体,还包括由执行电路在判定了以下至少一项时生成错误:经配置的片的数量等于零;所标识的源矩阵和目的地矩阵中的至少一个的pair参数未被设置为真;以及所标识的源矩阵和目的地矩阵中的至少一个的valid参数未被设置为真。

[0193]

示例13包括示例11的示例性方法的实体,还包括:由执行电路在对所标识的目的地的每一行进行操作之后保存状态;以及当执行被错误中断时,继续从该错误之前该执行停止之处执行经解码的加载矩阵对指令;其中所保存的状态至少包括行指针。

[0194]

示例14包括示例11的示例性方法的实体,还包括:由执行电路一次对所标识的目的地矩阵的每一行的一个字节块进行操作;在对每个块进行操作之后保存状态;以及当执行被错误中断时,继续从该错误之前该执行停止之处执行经解码的加载矩阵对指令;其中所保存的状态包括行指针、块指针、元素指针和字节指针中的一个或多个。

[0195]

示例15包括示例11-14中任一个示例的示例性方法的实体,其中所标识的左源矩阵和右源矩阵各自是用于表示矩阵的寄存器的集合。

[0196]

示例16包括示例11-14中任一个示例的示例性方法的实体,其中所标识的左源矩阵和右源矩阵各自是用于表示矩阵的多个存储器位置。

[0197]

示例17包括示例11-14中任一个示例的示例性方法的实体,其中所标识的左目的地矩阵和右目的地矩阵各自是用于表示矩阵的寄存器的集合。

[0198]

示例18包括示例11-14中任一个示例的示例性方法的实体,其中所标识的左目的地矩阵和右目的地矩阵各自是用于表示矩阵的多个存储器位置。

[0199]

示例19包括示例11-14中任一个示例的示例性方法的实体,其中操作码还包括元素尺寸标识符,该元素尺寸标识符用于指定所标识的左源矩阵、右源矩阵、左目的地矩阵和右目的地矩阵的每个数据元素的元素尺寸,其中该元素尺寸是16位、32位、64位、128位和256位中的一个。

[0200]

示例20包括示例11-14中任一个示例的示例性方法的实体,还包括:由执行电路将

所标识的左目的地矩阵和右目的地矩阵的任何剩余的经配置的行和列中的任何数据元素归零。

[0201]

示例21提供一种系统,包括:处理器以及耦合到该处理器的加速器,该加速器包括:用于对加载矩阵对指令解码的装置,该加载矩阵对指令具有用于操作码、源标识符和目的地标识符的字段,该源标识符和目的地标识符用于分别标识源矩阵和目的地矩阵,每个矩阵都具有等于真的的pair参数;以及用于执行经解码的加载矩阵对指令以便分别从所标识的源矩阵的左片和右片的对应元素位置加载所标识的目的地矩阵的左片和右片的每个元素的装置,其中该执行从第一行开始一次对所标识的目的地矩阵的一行进行操作。

[0202]

示例22包括示例21的示例性系统的实体,其中用于执行的装置还用于在判定了以下至少一项时生成错误:经配置的片的数量等于零;所标识的源矩阵和目的地矩阵中的至少一个的pair参数未被设置为真;以及所标识的源矩阵和目的地矩阵中的至少一个的valid参数未被设置为真。

[0203]

示例23包括示例21的示例性系统的实体,其中用于执行的装置还用于在对所标识的目的地的每一行进行操作之后保存状态,执行电路还用于:当执行被错误中断时,继续从错误之前该执行停止之处执行经解码的加载矩阵对指令;其中所保存的状态包括行指针。

[0204]

示例24包括示例21的示例性系统的实体,其中用于执行的装置还用于一次对所标识的目的地矩阵的每一行的一个字节块进行操作,用于执行的装置还用于在对每个块进行操作之后保存状态,执行电路还用于:当执行被错误中断时,继续从该错误之前该执行停止之处执行经解码的加载矩阵对指令;其中所保存的状态包括行指针、块指针、元素指针和字节指针中的一个或多个。

[0205]

示例25包括示例21-24中任一个示例的示例性系统的实体,其中所标识的左源矩阵和右源矩阵各自是用于表示矩阵的寄存器的集合。

[0206]

示例26包括示例21-24中任一个示例的示例性系统的实体,其中所标识的左源矩阵和右源矩阵各自是用于表示矩阵的多个存储器位置。

[0207]

示例27包括示例21-24中任一个示例的示例性系统的实体,其中所标识的左目的地矩阵和右目的地矩阵各自是用于表示矩阵的寄存器的集合。

[0208]

示例28包括示例21-24中任一个示例的示例性系统的实体,其中所标识的左目的地矩阵和右目的地矩阵各自是用于表示矩阵的多个存储器位置。

[0209]

示例29包括示例21-24中任一个示例的示例性系统的实体,其中操作码还包括元素尺寸标识符,该元素尺寸标识符用于指定所标识的左源矩阵、右源矩阵、左目的地矩阵和右目的地矩阵的每个数据元素的元素尺寸,其中该元素尺寸是16位、32位、64位、128位和256位中的一个。

[0210]

示例30包括示例21-24中任一个示例的示例性系统的实体,其中用于执行的装置还用于将所标识的左目的地矩阵和右目的地矩阵的任何剩余的经配置的行和列中的任何数据元素归零。

[0211]

示例31提供一种非瞬态机器可读介质,其存储加载矩阵对指令,该加载矩阵对指令使得处理器通过以下步骤执行指令:对加载矩阵对指令解码,该加载矩阵对指令具有用于操作码、源标识符和目的地标识符的字段,该源标识符和目的地标识符用于分别标识源矩阵和目的地矩阵,每个矩阵都具有等于真的的pair参数;以及执行经解码的加载矩阵对

指令以便分别从所标识的源矩阵的左片和右片的对应元素位置加载所标识的目的地矩阵的左片和右片的每个元素,其中该执行从第一行开始一次对所标识的目的地矩阵的一行进行操作。

[0212]

示例32包括示例31的示例性非瞬态机器可读介质的实体,其中处理器还用于通过以下步骤来执行:由执行电路在判定了以下至少一项时生成错误:经配置的片的数量等于零;所标识的源矩阵和目的地矩阵中的至少一个的pair参数未被设置为真;以及所标识的源矩阵和目的地矩阵中的至少一个的valid参数未被设置为真。

[0213]

示例33包括示例31的示例性非瞬态机器可读介质的实体,其中执行电路还用于通过以下步骤来执行:在对所标识的目的地的每一行进行操作之后由执行电路保存状态;以及当执行被错误中断时,继续从该错误之前该执行停止之处执行经解码的加载矩阵对指令;其中所保存的状态至少包括行指针。

[0214]

示例34包括示例31的示例性非瞬态机器可读介质的实体,其中处理器还用于通过以下步骤来执行:由执行电路一次对所标识的目的地矩阵的每一行的一个字节块进行操作;在对每个块进行操作之后保存状态;以及当执行被错误中断时,继续从该错误之前该执行停止之处执行经解码的加载矩阵对指令;其中所保存的状态包括行指针、块指针、元素指针和字节指针中的一个或多个。

[0215]

示例35包括示例31-34中任一个示例的示例性非瞬态机器可读介质的实体,其中所标识的左源矩阵和右源矩阵各自是用于表示矩阵的寄存器的集合。

[0216]

示例36包括示例31-34中任一个示例的示例性非瞬态机器可读介质的实体,其中所标识的左源矩阵和右源矩阵各自是用于表示矩阵的多个存储器位置。

[0217]

示例37包括示例31-34中任一个示例的示例性非瞬态机器可读介质的实体,其中所标识的左目的地矩阵和右目的地矩阵各自是用于表示矩阵的寄存器的集合。

[0218]

示例38包括示例31-34中任一个示例的示例性非瞬态机器可读介质的实体,其中所标识的左目的地矩阵和右目的地矩阵各自是用于表示矩阵的多个存储器位置。

[0219]

示例39包括示例31-34中任一个示例的示例性非瞬态机器可读介质的实体,其中操作码还包括元素尺寸标识符,该元素尺寸标识符用于指定所标识的左源矩阵、右源矩阵、左目的地矩阵和右目的地矩阵的每个数据元素的元素尺寸,其中该元素尺寸是16位、32位、64位、128位和256位中的一个。

[0220]

示例40包括示例31-34中任一个示例的示例性非瞬态机器可读介质的实体,其中处理器还用于通过以下步骤来执行:由执行电路将所标识的左目的地矩阵和右目的地矩阵的任何剩余的经配置的行和列中的任何数据元素归零。v.详细的示例性系统、处理器和仿真

[0221]

本文详述了用于执行上文描述的指令的硬件、软件等的示例。例如,下文所描述的内容详述了指令执行的多个方面,包括诸如取出、解码、调度、执行、引退等之类的各种流水线级。指令集

[0222]

指令集可以包括一个或多条指令格式。给定的指令格式可定义各种字段(例如,位的数量、位的位置)以指定将要执行的操作(例如,操作码)以及将对其执行该操作的(多个)操作数和/或(多个)其他数据字段(例如,掩码)等等。通过指令模板(或子格式)的定义来进

一步分解一些指令格式。例如,可将给定指令格式的指令模板定义为具有该指令格式的字段(所包括的字段通常按照相同顺序,但是至少一些字段具有不同的位的位置,因为较少的字段被包括)的不同子集,和/或定义为具有以不同方式进行解释的给定字段。由此,isa的每一条指令使用给定的指令格式(并且如果经定义,则按照该指令格式的指令模板中的给定的一条指令模板)来表达,并包括用于指定操作和操作数的字段。例如,示例性add(加法)指令具有特定的操作码和指令格式,该特定的指令格式包括用于指定该操作码的操作码字段和用于选择操作数(源1/目的地以及源2)的操作数字段;并且该add指令在指令流中出现将使得在操作数字段中具有选择特定操作数的特定的内容。已经推出和/或发布了被称为高级向量扩展(avx)(avx1和avx2)和利用向量扩展(vex)编码方案的simd扩展集(参见例如2014年9月的64和ia-32架构软件开发者手册;并且参见2014年10月的高级向量扩展编程参考)。示例性指令格式

[0223]

本文中所描述的(多条)指令的实施例可被具体化为不同格式。另外,下文详细描述示例性系统、架构和流水线。(多条)指令的实施例可在此类系统、架构和流水线上执行,但是不限于详述的那些系统、架构和流水线。通用向量友好指令格式

[0224]

向量友好指令格式是适于向量指令(例如,存在专用于向量操作的特定字段)的指令格式。尽管描述了其中通过向量友好指令格式支持向量和标量操作两者的实施例,但是替代实施例仅使用通过向量友好指令格式的向量操作。

[0225]

图25a-25b是图示出根据本发明的实施例的通用向量友好指令格式及其指令模板的框图。图25a是图示根据本发明的实施例的通用向量友好指令格式及其a类指令模板的框图;而图25b是图示根据本发明的实施例的通用向量友好指令格式及其b类指令模板的框图。具体而言,针对通用向量友好指令格式2500定义a类和b类指令模板,这两者都包括无存储器访问2505的指令模板和存储器访问2520的指令模板。在向量友好指令格式的上下文中的术语“通用”是指不束缚于任何特定指令集的指令格式。

[0226]

尽管将描述其中向量友好指令格式支持以下情况的本发明的实施例,即:64字节向量操作数长度(或尺寸)与32位(4字节)或64位(8字节)数据元素宽度(或尺寸)(并且由此,64字节向量由16个双字尺寸的元素组成,或者替代地由8个四字尺寸的元素组成);64字节向量操作数长度(或尺寸)与16位(2字节)或8位(1字节)数据元素宽度(或尺寸);32字节向量操作数长度(或尺寸)与32位(4字节)、64位(8字节)、16位(2字节)或8位(1字节)数据元素宽度(或尺寸);以及16字节向量操作数长度(或尺寸)与32位(4字节)、64位(8字节)、16位(2字节)、或8位(1字节)数据元素宽度(或尺寸);但是替代实施例可支持更大、更小和/或不同的向量操作数尺寸(例如,256字节向量操作数)与更大、更小或不同的数据元素宽度(例如,128位(16字节)数据元素宽度)。

[0227]

图25a中的a类指令模板包括:1)在无存储器访问2505的指令模板内,示出无存储器访问的完全舍入控制型操作2510的指令模板、以及无存储器访问的数据变换型操作2515的指令模板;以及2)在存储器访问2520的指令模板内,示出存储器访问的时效性2525的指令模板和存储器访问的非时效性2530的指令模板。图25b中的b类指令模板包括:1)在无存储器访问2505的指令模板内,示出无存储器访问的写掩码控制的部分舍入控制型操作2512

的指令模板、以及无存储器访问的写掩码控制的vsize(向量尺寸)型操作2517的指令模板;以及2)在存储器访问2520的指令模板内,示出存储器访问的写掩码控制2527的指令模板。

[0228]

通用向量友好指令格式2500包括下文中按照图25a-图25b中所图示出的顺序列出的下列字段。

[0229]

格式字段2540-该字段中的特定值(指令格式标识符值)唯一地标识向量友好指令格式,并且由此标识指令在指令流中以向量友好指令格式出现。由此,该字段对于仅具有通用向量友好指令格式的指令集是不需要的,在这个意义上该字段是任选的。

[0230]

基础操作字段2542-其内容区分不同的基础操作。

[0231]

寄存器索引字段2544

–

其内容直接或者通过地址生成来指定源或目的地操作数在寄存器中或者在存储器中的位置。这些字段包括足够数量的位以从pxq(例如,32x512、16x128、32x1024、64x1024)个寄存器堆中选择n个寄存器。尽管在一个实施例中n可多达三个源寄存器和一个目的地寄存器,但是替代实施例可支持更多或更少的源寄存器和目的地寄存器(例如,可支持多达两个源寄存器,其中这些源寄存器中的一个还用作目的地寄存器;可支持多达三个源寄存器,其中这些源寄存器中的一个还用作目的地寄存器;可支持多达两个源寄存器和一个目的地寄存器)。

[0232]

修饰符(modifier)字段2546-其内容将指定存储器访问的以通用向量指令格式出现的指令与不指定存储器访问的以通用向量指令格式出现的指令区分开;即在无存储器访问2505的指令模板与存储器访问2520的指令模板之间进行区分。存储器访问操作读取和/或写入到存储器层级结构(在一些情况下,使用寄存器中的值来指定源和/或目的地地址),而非存储器访问操作不这样(例如,源和/或目的地是寄存器)。尽管在一个实施例中,该字段还在三种不同的方式之间选择以执行存储器地址计算,但是替代实施例可支持更多、更少或不同的方式来执行存储器地址计算。

[0233]

扩充操作字段2550-其内容区分除基础操作以外还要执行各种不同操作中的哪一个操作。该字段是针对上下文的。在本发明的一个实施例中,该字段被分成类字段2568、α字段2552和β字段2554。扩充操作字段2550允许在单条指令而非2条、3条或4条指令中执行多组共同的操作。

[0234]

比例字段2560-其内容允许用于存储器地址生成(例如,用于使用2

比例

*索引 基址的地址生成)的索引字段的内容的按比例缩放。

[0235]

位移字段2562a-其内容用作存储器地址生成的一部分(例如,用于使用2

比例

*索引 基址 位移的地址生成)。

[0236]

位移因数字段2562b(注意,位移字段2562a直接在位移因数字段2562b上的并置指示使用一个或另一个)-其内容用作地址生成的一部分;它指定通过存储器访问的尺寸(n)按比例缩放的位移因数,其中n是存储器访问中的字节数量(例如,用于使用2

比例

*索引 基址 按比例缩放的位移的地址生成)。忽略冗余的低阶位,并且因此将位移因数字段的内容乘以存储器操作数总尺寸(n)以生成将在计算有效地址中使用的最终位移。n的值由处理器硬件在运行时基于完整操作码字段2574(稍后在本文中描述)和数据操纵字段2554c确定。位移字段2562a和位移因数字段2562b不用于无存储器访问2505的指令模板和/或不同的实施例可实现这两者中的仅一个或不实现这两者中的任一个,在此意义上,位移字段2562a和位移因数字段2562b是任选的。

[0237]

数据元素宽度字段2564-其内容区分使用多个数据元素宽度中的哪一个(在一些实施例中用于所有指令;在其他实施例中只用于一些指令)。如果支持仅一个数据元素宽度和/或使用操作码的某一方面来支持数据元素宽度,则该字段是不需要的,在这个意义上,该字段是任选的。

[0238]

写掩码字段2570-其内容在每一数据元素位置的基础上控制目的地向量操作数中的数据元素位置是否反映基础操作和扩充操作的结果。a类指令模板支持合并-写掩蔽,而b类指令模板支持合并-写掩蔽和归零-写掩蔽两者。当合并时,向量掩码允许在执行(由基础操作和扩充操作指定的)任何操作期间保护目的地中的任何元素集免于更新;在另一实施例中,保持其中对应掩码位具有0的目的地的每一元素的旧值。相反,当归零时,向量掩码允许在执行(由基础操作和扩充操作指定的)任何操作期间使目的地中的任何元素集归零;在一个实施例中,目的地的元素在对应掩码位具有0值时被设为0。该功能的子集是控制正在被执行的操作的向量长度的能力(即,从第一个到最后一个正在被修改的元素的跨度);然而,被修改的元素不一定要是连续的。由此,写掩码字段2570允许部分向量操作,这包括加载、存储、算术、逻辑等。尽管描述了其中写掩码字段2570的内容选择了多个写掩码寄存器中的包含要使用的写掩码的一个写掩码寄存器(并且由此,写掩码字段2570的内容间接地标识要执行的掩蔽)的本发明的实施例,但是替代实施例替代地或附加地允许掩码写字段2570的内容直接指定要执行的掩蔽。

[0239]

立即数字段2572-其内容允许对立即数的指定。该字段在实现不支持立即数的通用向量友好格式中不存在且在不使用立即数的指令中不存在,在这个意义上,该字段是任选的。

[0240]

类字段2568-其内容在不同类的指令之间进行区分。参考图25a-图25b,该字段的内容在a类指令和b类指令之间进行选择。在图25a-图25b中,圆角方形用于指示特定的值存在于字段中(例如,在图25a-图25b中分别用于类字段2568的a类2568a和b类2568b)。a类指令模板

[0241]

在a类非存储器访问2505的指令模板的情况下,α字段2552被解释为其内容区分要执行不同扩充操作类型中的哪一种(例如,针对无存储器访问的舍入型操作2510和无存储器访问的数据变换型操作2515的指令模板分别指定舍入2552a.1和数据变换2552a.2)的rs字段2552a,而β字段2554区分要执行指定类型的操作中的哪一种。在无存储器访问2505的指令模板中,比例字段2560、位移字段2562a和位移因数字段2562b不存在。无存储器访问的指令模板——完全舍入控制型操作

[0242]

在无存储器访问的完全舍入控制型操作2510的指令模板中,β字段2554被解释为其(多个)内容提供静态舍入的舍入控制字段2554a。尽管在本发明的所描述的实施例中舍入控制字段2554a包括抑制所有浮点异常(sae)字段2556和舍入操作控制字段2558,但是替代实施例可支持这两个概念,可将这两个概念编码为同一字段,或仅具有这些概念/字段中的一个或另一个(例如,可仅具有舍入操作控制字段2558)。

[0243]

sae字段2556-其内容区分是否停用异常事件报告;当sae字段2556的内容指示启用抑制时,给定指令不报告任何种类的浮点异常标志且不唤起任何浮点异常处理程序。

[0244]

舍入操作控制字段2558-其内容区分执行一组舍入操作中的哪一个(例如,向上舍入、向下舍入、向零舍入、以及就近舍入)。由此,舍入操作控制字段2558允许逐指令地改变

舍入模式。在其中处理器包括用于指定舍入模式的控制寄存器的本发明的一个实施例中,舍入操作控制字段2550的内容覆盖该寄存器值。无存储器访问的指令模板-数据变换型操作

[0245]

在无存储器访问的数据变换型操作2515的指令模板中,β字段2554被解释为数据变换字段2554b,其内容区分要执行多个数据变换中的哪一个(例如,无数据变换、混合、广播)。

[0246]

在a类存储器访问2520的指令模板的情况下,α字段2552被解释为驱逐提示字段2552b,其内容区分要使用驱逐提示中的哪一个(在图25a中,对于存储器访问时效性2525的指令模板和存储器访问非时效性2530的指令模板分别指定时效性的2552b.1和非时效性的2552b.2),而β字段2554被解释为数据操纵字段2554c,其内容区分要执行多个数据操纵操作(也称为基元(primitive))中的哪一个(例如,无操纵、广播、源的向上转换以及目的地的向下转换)。存储器访问2520的指令模板包括比例字段2560,并任选地包括位移字段2562a或位移因数字段2562b。

[0247]

向量存储器指令使用转换支持来执行来自存储器的向量加载并将向量存储到存储器。如同寻常的向量指令,向量存储器指令以数据元素式的方式从/向存储器传输数据,其中实际被传输的元素由被选择为写掩码的向量掩码的内容规定。存储器访问的指令模板——时效性的

[0248]

时效性的数据是可能足够快地重新使用以从高速缓存受益的数据。然而,这是提示,并且不同的处理器能以不同的方式实现它,包括完全忽略该提示。存储器访问的指令模板——非时效性的

[0249]

非时效性的数据是不可能足够快地重新使用以从第1级高速缓存中的高速缓存受益且应当被给予驱逐优先级的数据。然而,这是提示,并且不同的处理器能以不同的方式实现它,包括完全忽略该提示。b类指令模板

[0250]

在b类指令模板的情况下,α字段2552被解释为写掩码控制(z)字段2552c,其内容区分由写掩码字段2570控制的写掩码操作应当是合并还是归零。

[0251]

在b类非存储器访问2505的指令模板的情况下,β字段2554的部分被解释为rl字段2557a,其内容区分要执行不同扩充操作类型中的哪一种(例如,针对无存储器访问的写掩码控制的部分舍入控制型操作2512的指令模板和无存储器访问的写掩码控制的vsize型操作2517的指令模板分别指定舍入2557a.1和向量长度(vsize)2557a.2),而β字段2554的其余部分区分要执行指定类型的操作中的哪一种。在无存储器访问2505的指令模板中,比例字段2560、位移字段2562a和位移因数字段2562b不存在。

[0252]

在无存储器访问的写掩码控制的部分舍入控制型操作2510的指令模板中,β字段2554的其余部分被解释为舍入操作字段2559a,并且禁用异常事件报告(给定指令不报告任何种类的浮点异常标志且不唤起任何浮点异常处置程序)。

[0253]

舍入操作控制字段2559a-正如舍入操作控制字段2558,其内容区分要执行一组舍入操作中的哪一个(例如,向上舍入、向下舍入、向零舍入、以及就近舍入)。由此,舍入操作控制字段2559a允许逐指令地改变舍入模式。在其中处理器包括用于指定舍入模式的控制寄存器的本发明的一个实施例中,舍入操作控制字段2550的内容覆盖该寄存器值。

[0254]

在无存储器访问的写掩码控制的vsize型操作2517的指令模板中,β字段2554的其余部分被解释为向量长度字段2559b,其内容区分要执行多个数据向量长度中的哪一个(例如,128字节、256字节、或512字节)。

[0255]

在b类存储器访问2520的指令模板的情况下,β字段2554的部分被解释为广播字段2557b,其内容区分是否要执行广播型数据操纵操作,而β字段2554的其余部分被解释为向量长度字段2559b。存储器访问2520的指令模板包括比例字段2560,并任选地包括位移字段2562a或位移因数字段2562b。

[0256]

针对通用向量友好指令格式2500,示出完整操作码字段2574包括格式字段2540、基础操作字段2542以及数据元素宽度字段2564。尽管示出了其中完整操作码字段2574包括所有这些字段的一个实施例,但是在不支持所有这些字段的实施例中,完整操作码字段2574包括少于所有的这些字段。完整操作码字段2574提供操作代码(操作码)。

[0257]

扩充操作字段2550、数据元素宽度字段2564以及写掩码字段2570允许在每一指令的基础上以通用向量友好指令格式指定这些特征。

[0258]

写掩码字段和数据元素宽度字段的组合创建各种类型的指令,因为这些指令允许基于不同的数据元素宽度应用该掩码。

[0259]

在a类和b类内出现的各种指令模板在不同的情形下是有益的。在本发明的一些实施例中,不同处理器或处理器内的不同核可仅支持a类、仅支持b类、或者可支持这两类。举例而言,旨在用于通用计算的高性能通用乱序核可仅支持b类,旨在主要用于图形和/或科学(吞吐量)计算的核可仅支持a类,并且旨在用于通用计算和图形和/或科学(吞吐量)计算两者的核可支持a类和b类两者(当然,具有来自这两类的模板和指令的一些混合、但是并非来自这两类的所有模板和指令的核在本发明的范围内)。同样,单个处理器可包括多个核,这些核全部都支持相同的类,或者其中不同的核支持不同的类。举例而言,在具有单独的图形核和通用核的处理器中,图形核中的旨在主要用于图形和/或科学计算的一个核可仅支持a类,而通用核中的一个或多个可以是具有旨在用于通用计算的仅支持b类的乱序执行和寄存器重命名的高性能通用核。不具有单独的图形核的另一处理器可包括既支持a类又支持b类的一个或多个通用有序或乱序核。当然,在本发明的不同实施例中,来自一类的特征也可在其他类中实现。将使以高级语言编写的程序成为(例如,及时编译或静态编译)各种不同的可执行形式,这些可执行形式包括:1)仅具有由用于执行的目标处理器支持的(多个)类的指令的形式;或者2)具有替代例程并具有控制流代码的形式,该替代例程使用所有类的指令的不同组合来编写,该控制流代码选择这些例程以基于由当前正在执行代码的处理器支持的指令来执行。示例性专用向量友好指令格式

[0260]

图26a是图示出根据本发明的各实施例的示例性专用向量友好指令格式的框图。图26a示出专用向量友好指令格式2600,其指定位置、尺寸、解释和字段的次序、以及那些字段中的一些字段的值,在这个意义上专用向量友好指令格式800是专用的。专用向量友好指令格式2600可用于扩展x86指令集,并且由此字段中的一些字段与在现有的x86指令集及其扩展(例如,avx)中所使用的那些字段类似或相同。该格式保持与具有扩展的现有x86指令集的前缀编码字段、实操作码字节字段、mod r/m字段、sib字段、位移字段和立即数字段一致。示出来自图25的字段,来自图26a的字段映射到来自图25的字段。

[0261]

应当理解,虽然出于说明的目的在通用向量友好指令格式2500的上下文中,参考专用向量友好指令格式2600描述了本发明的实施例,但是本发明不限于专用向量友好指令格式2600,声明的地方除外。例如,通用向量友好指令格式2500构想了各种字段的各种可能的尺寸,而专用向量友好指令格式2600示出为具有特定尺寸的字段。作为具体示例,尽管数据元素宽度字段2564示出为专用向量友好指令格式2600中的一个位字段,但是本发明不限于此(也就是说,通用向量友好指令格式2500构想数据元素宽度字段2564的其他尺寸)。

[0262]

通用向量友好指令格式2500包括下文中按照图26a中所示出的顺序列出的字段。

[0263]

evex前缀(字节0-3)2602——以四字节形式进行编码。

[0264]

格式字段2540(evex字节0,位[7:0])——第一字节(evex字节0)是格式字段2540,并且它包含0x62(在本发明的一个实施例中用于区分向量友好指令格式的唯一值)。

[0265]

第二-第四字节(evex字节1-3)包括提供专用能力的多个位字段。

[0266]

rex字段2605(evex字节1,位[7-5])-由evex.r位字段(evex字节1,位[7]

–

r)、evex.x位字段(evex字节1,位[6]

–

x)以及(2557bex字节1,位[5]

–

b)组成。evex.r、evex.x和evex.b位字段提供与对应的vex位字段相同的功能,并且使用1补码的形式进行编码,即zmm0被编码为1111b,zmm15被编码为0000b。这些指令的其他字段对如在本领域中已知的寄存器索引的较低的三个位(rrr、xxx和bbb)进行编码,使得可通过增加evex.r、evex.x和evex.b来形成rrrr、xxxx和bbbb。

[0267]

rex’字段2510-这是rex’字段2510的第一部分,并且是用于对扩展的32个寄存器集合的较高16个或较低16个寄存器进行编码的evex.r’位字段(evex字节1,位[4]

–

r’)。在本发明的一个实施例中,该位与下文所指示的其他位一起以位反转的格式存储,以(在公知x86的32位模式下)与bound指令进行区分,该bound指令的实操作码字节是62,但是在mod r/m字段(在下文中描述)中不接受mod字段中的值11;本发明的替代实施例不以反转的格式存储该位以及下文所指示的其他位。值1用于对较低的16个寄存器进行编码。换句话说,通过组合evex.r’、evex.r以及来自其他字段的其他rrr来形成r’rrrr。

[0268]

操作码映射字段2615(evex字节1,位[3:0]

–

mmmm)

–

其内容对隐含的前导操作码字节(0f、0f 38、或0f 3)进行编码。

[0269]

数据元素宽度字段2564(evex字节2,位[7]

–

w)-由记号evex.w表示。evex.w用于定义数据类型(32位数据元素或64位数据元素)的粒度(尺寸)。

[0270]

evex.vvvv 2620(evex字节2,位[6:3]-vvvv)-evex.vvvv的作用可包括如下:1)evex.vvvv对以反转(1补码)形式指定的第一源寄存器操作数进行编码,并且对具有两个或更多个源操作数的指令有效;2)evex.vvvv对针对特定向量位移以1补码的形式指定的目的地寄存器操作数进行编码;或者3)evex.vvvv不对任何操作数进行编码,该字段被预留,并且应当包含1111b。由此,evex.vvvv字段2620对以反转(1补码)的形式存储的第一源寄存器指定符的4个低阶位进行编码。取决于该指令,额外不同的evex位字段用于将指定符尺寸扩展到32个寄存器。

[0271]

evex.u 2568类字段(evex字节2,位[2]-u)-如果evex.u=0,则它指示a类或evex.u0;如果evex.u=1,则它指示b类或evex.u1。

[0272]

前缀编码字段2625(evex字节2,位[1:0]-pp)-提供了用于基础操作字段的附加位。除了对以evex前缀格式的传统sse指令提供支持以外,这也具有压缩simd前缀的益处

(evex前缀仅需要2位,而不是需要字节来表达simd前缀)。在一个实施例中,为了支持使用以传统格式和以evex前缀格式两者的simd前缀(66h、f2h、f3h)的传统sse指令,将这些传统simd前缀编码成simd前缀编码字段;并且在运行时在被提供给解码器的pla之前被扩展成传统simd前缀(因此,在无需修改的情况下,pla既可执行传统格式的这些传统指令又可执行evex格式的这些传统指令)。虽然较新的指令可将evex前缀编码字段的内容直接用作操作码扩展,但是为了一致性,特定实施例以类似的方式扩展,但允许由这些传统simd前缀指定的不同含义。替代实施例可重新设计pla以支持2位simd前缀编码,并且由此不需要扩展。

[0273]

α字段2552(evex字节3,位[7]

–

eh,也称为evex.eh、evex.rs、evex.rl、evex.写掩码控制、以及evex.n;也以α示出)——如先前所述,该字段是针对上下文的。

[0274]

β字段2554(evex字节3,位[6:4]-sss,也称为evex.s

2-0

、evex.r

2-0

、evex.rr1、evex.ll0、evex.llb;也以βββ示出)-如先前所述,该字段是针对上下文的。

[0275]

rex’字段2510-这是rex’字段的其余部分,并且是可用于对扩展的32个寄存器集合的较高16个或较低16个寄存器进行编码的evex.v’位字段(evex字节3,位[3]

–v’

)。该位以位反转的格式存储。值1用于对较低的16个寄存器进行编码。换言之,通过组合evex.v’、evex.vvvv来形成v’vvvv。

[0276]

写掩码字段2570(evex字节3,位[2:0]-kkk)-其内容指定写掩码寄存器中的寄存器索引,如先前所述。在本发明的一个实施例中,特定值evex.kkk=000具有暗示没有写掩码用于特定指令的特殊行为(这能以各种方式实现,包括使用硬连线到所有对象的写掩码或绕过掩蔽硬件的硬件来实现)。

[0277]

实操作码字段2630(字节4)还被称为操作码字节。操作码的部分在该字段中被指定。

[0278]

mod r/m字段2640(字节5)包括mod字段2642、reg字段2644、以及r/m字段2646。如先前所述的,mod字段2642的内容将存储器访问操作和非存储器访问操作区分开。reg字段2644的作用可被归结为两种情形:对目的地寄存器操作数或源寄存器操作数进行编码;或者被视为操作码扩展,并且不用于对任何指令操作数进行编码。r/m字段2646的作用可包括如下:对引用存储器地址的指令操作数进行编码;或者对目的地寄存器操作数或源寄存器操作数进行编码。

[0279]

比例、索引、基址(sib)字节(字节6)-如先前所述的,比例字段2550的内容用于存储器地址生成。sib.xxx 2654和sib.bbb 2656——先前已经针对寄存器索引xxxx和bbbb提及了这些字段的内容。

[0280]

位移字段2562a(字节7-10)-当mod字段2642包含10时,字节7-10是位移字段2562a,并且它与传统32位位移(disp32)一样地工作,并且以字节粒度工作。

[0281]

位移因数字段2562b(字节7)-当mod字段2642包含01时,字节7是位移因数字段2562b。该字段的位置与以字节粒度工作的传统x86指令集8位位移(disp8)的位置相同。由于disp8是符号扩展的,因此它仅能在-128和127字节偏移之间寻址;在64字节高速缓存行的方面,disp8使用可被设为仅四个真正有用的值-128、-64、0和64的8位;由于常常需要更大的范围,所以使用disp32;然而,disp32需要4个字节。与disp8和disp32对比,位移因数字段2562b是disp8的重新解释;当使用位移因数字段2562b时,通过将位移因数字段的内容乘以存储器操作数访问的尺寸(n)来确定实际位移。该类型的位移被称为disp8*n。这减小了

平均指令长度(单个字节用于位移,但具有大得多的范围)。此类经压缩的位移基于有效位移是存储器访问的粒度的倍数的假设,并且因此地址偏移的冗余低阶位不需要被编码。换言之,位移因数字段2562b替代传统x86指令集8位位移。由此,位移因数字段2562b以与x86指令集8位位移相同的方式被编码(因此,在modrm/sib编码规则中没有变化),唯一的不同在于,将disp8超载至disp8*n。换句话说,在编码规则或编码长度方面没有变化,而仅在有硬件对位移值的解释方面有变化(这需要将位移按比例缩放存储器操作数的尺寸以获得字节式地址偏移)。立即数字段2572如先前所描述地操作。完整操作码字段

[0282]

图26b是图示出根据本发明的实施例的构成完整操作码字段2574的具有专用向量友好指令格式2600的字段的框图。具体地,完整操作码字段2574包括格式字段2540、基础操作字段2542和数据元素宽度(w)字段2564。基础操作字段2542包括前缀编码字段2625、操作码映射字段2615和实操作码字段2630。寄存器索引字段

[0283]

图26c是示出根据本发明的一个实施例的构成寄存器索引字段2544的具有专用向量友好指令格式2600的字段的框图。具体地,寄存器索引字段2544包括rex字段2605、rex’字段2610、modr/m.reg字段2644、modr/m.r/m字段2646、vvvv字段2620、xxx字段2654和bbb字段2656。扩充操作字段

[0284]

图26d是示出根据本发明的一个实施例的构成扩充操作字段2550的具有专用向量友好指令格式2600的字段的框图。当类(u)字段2568包含0时,它表明evex.u0(a类2568a);当它包含1时,它表明evex.u1(b类2568b)。当u=0且mod字段2642包含11(表明无存储器访问操作)时,α字段2552(evex字节3,位[7]

–

eh)被解释为rs字段2552a。当rs字段2552a包含1(舍入2552a.1)时,β字段2554(evex字节3,位[6:4]

–

sss)被解释为舍入控制字段2554a。舍入控制字段2554a包括一位sae字段2556和两位舍入操作字段2558。当rs字段2552a包含0(数据变换2552a.2)时,β字段2554(evex字节3,位[6:4]

–

sss)被解释为三位数据变换字段2554b。当u=0且mod字段2642包含00、01或10(表明存储器访问操作)时,α字段2552(evex字节3,位[7]

–

eh)被解释为驱逐提示(eh)字段2552b且β字段2554(evex字节3,位[6:4]

–

sss)被解释为三位的数据操纵字段2554c。

[0285]

当u=1时,α字段2552(evex字节3,位[7]

–

eh)被解释为写掩码控制(z)字段2552c。当u=1且mod字段2642包含11(表明无存储器访问操作)时,β字段2554的一部分(evex字节3,位[4]

–

s0)被解释为rl字段2557a;当它包含1(舍入2557a.1)时,β字段2554的其余部分(evex字节3,位[6-5]

–s2-1

)被解释为舍入操作字段2559a,而当rl字段2557a包含0(vsize 2557.a2)时,β字段2554的其余部分(evex字节3,位[6-5]-s

2-1

)被解释为向量长度字段2559b(evex字节3,位[6-5]

–

l

1-0

)。当u=1且mod字段2642包含00、01或10(表明存储器访问操作)时,β字段2554(evex字节3,位[6:4]

–

sss)被解释为向量长度字段2559b(evex字节3,位[6-5]

–

l

1-0

)和广播字段2,557b(evex字节3,位[4]

–

b)。示例性寄存器架构

[0286]

图27是根据本发明的一个实施例的寄存器架构2700的框图。在所图示的实施例中,存在32个512位宽的向量寄存器2710;这些寄存器被引用为zmm0到zmm31。较低的16个

zmm寄存器的较低阶256个位覆盖在寄存器ymm0-16上。较低的16个zmm寄存器的较低阶128个位(ymm寄存器的较低阶128个位)覆盖在寄存器xmm0-15上。专用向量友好指令格式2600对这些被覆盖的寄存器堆操作,如在以下表格中所图示。

[0287]

换言之,向量长度字段2559b在最大长度与一个或多个其他较短长度之间进行选择,其中每一个此类较短长度是前一长度的一半;并且不具有向量长度字段2559b的指令模板在最大向量长度上操作。此外,在一个实施例中,专用向量友好指令格式2600的b类指令模板对紧缩或标量单/双精度浮点数据以及紧缩或标量整数数据操作。标量操作是对zmm/ymm/xmm寄存器中的最低阶数据元素位置执行的操作;取决于实施例,较高阶数据元素位置要么保持与在指令之前相同,要么归零。

[0288]

写掩码寄存器2715——在所图示的实施例中,有8个写掩码寄存器(k0到k7),每一写掩码寄存器的尺寸是64位。在替代实施例中,写掩码寄存器2715的尺寸是16位。如先前所描述,在本发明的一个实施例中,向量掩码寄存器k0无法用作写掩码;当将正常指示k0的编码用作写掩码时,它选择硬连线的写掩码0xffff,从而有效地禁止写掩蔽用于那条指令。

[0289]

通用寄存器2725——在所图示的实施例中,存在十六个64位通用寄存器,这些寄存器与现有的x86寻址模式一起使用来寻址存储器操作数。这些寄存器通过名称rax、rbx、rcx、rdx、rbp、rsi、rdi、rsp以及r8到r15来引用。

[0290]

标量浮点栈寄存器堆(x87栈)2745,在其上面重叠了mmx紧缩整数平坦寄存器堆2750——在所图示的实施例中,x87栈是用于使用x87指令集扩展来对32/64/80位浮点数据执行标量浮点操作的八元素栈;而mmx寄存器用于对64位紧缩整数数据执行操作,以及为在mmx和xmm寄存器之间执行的一些操作保存操作数。

[0291]

本发明的替代实施例可以使用较宽的或较窄的寄存器。另外,本发明的替代实施例可以使用更多、更少或不同的寄存器堆和寄存器。示例性核架构、处理器和计算机架构

[0292]

处理器核可通过不同的方式、出于不同的目的并且在不同的处理器中实现。例如,此类核的实现可以包括:1)旨在用于通用计算的通用有序核;2)旨在用于通用计算的高性能通用乱序核;3)旨在主要用于图形和/或科学(吞吐量)计算的专用核。不同处理器的实现

可包括:1)cpu,其包括旨在用于通用计算的一个或多个通用有序核和/或旨在用于通用计算的一个或多个通用乱序核;以及2)协处理器,其包括旨在主要用于图形和/或科学(吞吐量)的一个或多个专用核。此类不同的处理器导致不同的计算机系统架构,这些计算机系统架构可包括:1)在与cpu分开的芯片上的协处理器;2)在与cpu相同的封装中但在分开的管芯上的协处理器;3)与cpu在相同管芯上的协处理器(在该情况下,此类协处理器有时被称为专用逻辑或被称为专用核,该专用逻辑诸如,集成图形和/或科学(吞吐量)逻辑);以及4)芯片上系统,其可以将所描述的cpu(有时被称为(多个)应用核或(多个)应用处理器)、以上描述的协处理器和附加功能包括在同一管芯上。接着描述示例性核架构,随后描述示例性处理器和计算机架构。示例性核架构有序和乱序核框图

[0293]

图28a是示出根据本发明的各实施例的示例性有序流水线和示例性的寄存器重命名的乱序发布/执行流水线的框图。图28b是示出根据本发明的多个实施例的要包括在处理器中的有序架构核的示例性实施例和示例性的寄存器重命名的无序发布/执行架构核的框图。图28a-图28b中的实线框示出了有序流水线和有序核,而任选增加的虚线框示出了寄存器重命名的、乱序发布/执行流水线和核。考虑到有序方面是乱序方面的子集,将描述乱序方面。

[0294]

在图28a中,处理器流水线2800包括取出级2802、长度解码级2804、解码级2806、分配级2808、重命名级2810、调度(也称为分派或发布)级2812、寄存器读取/存储器读取级2814、执行级2816、写回/存储器写入级2818、异常处理级2822和提交级2824。

[0295]

图28b示出了包括耦合到执行引擎单元2850的前端单元2830的处理器核2890,且执行引擎单元和前端单元两者都耦合到存储器单元2870。核2890可以是精简指令集计算(risc)核、复杂指令集计算(cisc)核、超长指令字(vliw)核、或者混合或替代的核类型。作为又一选项,核2890可以是专用核,诸如例如,网络或通信核、压缩引擎、协处理器核、通用计算图形处理单元(gpgpu)核、图形核,等等。

[0296]

前端单元2830包括耦合至指令高速缓存单元2834的分支预测单元2832,该指令高速缓存单元2834耦合至指令转换后备缓冲器(tlb)2836,该指令转换后备缓冲器2836耦合至指令取出单元2838,该指令取出单元2838耦合至解码单元2840。解码单元2840(或解码器)可对指令进行解码,并且生成从原始指令解码出的、或以其他方式反映原始指令的、或从原始指令导出的一个或多个微操作、微代码进入点、微指令、其他指令、或其他控制信号作为输出。解码单元2840可使用各种不同的机制来实现。合适的机制的示例包括但不限于查找表、硬件实现、可编程逻辑阵列(pla)、微代码只读存储器(rom)等。在一个实施例中,核2890包括(例如,在解码单元2840中或否则在前端单元2830内的)用于存储某些宏指令的微代码的微代码rom或其他介质。解码单元2840耦合至执行引擎单元2850中的重命名/分配器单元2852。

[0297]

执行引擎单元2850包括重命名/分配器单元2852,该重命名/分配器单元2852耦合至引退单元2854和一个或多个调度器单元的集合2856。(多个)调度器单元2856表示任何数目的不同调度器,包括预留站、中央指令窗等。(多个)调度器单元2856耦合到(多个)物理寄存器堆单元2858。每个物理寄存器堆单元2858表示一个或多个物理寄存器堆,其中不同的

物理寄存器堆存储一种或多种不同的数据类型,诸如标量整数、标量浮点、紧缩整数、紧缩浮点、向量整数、向量浮点、状态(例如,作为要执行的下一指令的地址的指令指针)等。在一个实施例中,物理寄存器堆单元2858包括向量寄存器单元、写掩码寄存器单元和标量寄存器单元。这些寄存器单元可提供架构向量寄存器、向量掩码寄存器和通用寄存器。(多个)物理寄存器堆单元2858由引退单元2854重叠,以图示可实现寄存器重命名和乱序执行的各种方式(例如,使用(多个)重排序缓冲器和(多个)引退寄存器堆;使用(多个)未来文件、(多个)历史缓冲器以及(多个)引退寄存器堆;使用寄存器映射和寄存器池;等等)。引退单元2854和(多个)物理寄存器堆单元2858耦合至(多个)执行集群2860。(多个)执行集群2860包括一个或多个执行单元2862的集合和一个或多个存储器访问单元2864的集合。执行单元2862可执行各种操作(例如,移位、加法、减法、乘法)并可对各种数据类型(例如,标量浮点、紧缩整数、紧缩浮点、向量整数、向量浮点)执行。尽管一些实施例可以包括专用于特定功能或功能集合的数个执行单元,但是其他实施例可仅包括一个执行单元或全都执行所有功能的多个执行单元。(多个)调度器单元2856、(多个)物理寄存器堆单元2858和(多个)执行集群2860示出为可能有多个,因为某些实施例为某些类型的数据/操作创建分开的流水线(例如,标量整数流水线、标量浮点/紧缩整数/紧缩浮点/向量整数/向量浮点流水线,和/或各自具有其自身的调度器单元、物理寄存器堆单元和/或执行集群的存储器访问流水线——并且在分开的存储器访问流水线的情况下,实现其中仅该流水线的执行集群具有(多个)存储器访问单元2864的某些实施例)。还应当理解,在使用分开的流水线的情况下,这些流水线中的一个或多个可以是乱序发布/执行,并且其余流水线可以是有序发布/执行。

[0298]

存储器访问单元2864的集合耦合至存储器单元2870,该存储器单元2870包括数据tlb单元2872,该数据tlb单元2872耦合至数据高速缓存单元2874,该数据高速缓存单元2874耦合至第2级(l2)高速缓存单元2876。在一个示例性实施例中,存储器访问单元2864可包括加载单元、存储地址单元和存储数据单元,其中的每一个均耦合至存储器单元2870中的数据tlb单元2872。指令高速缓存单元2834还耦合到存储器单元2870中的第2级(l2)高速缓存单元2876。l2高速缓存单元2876耦合至一个或多个其他级别的高速缓存,并最终耦合至主存储器。

[0299]

作为示例,示例性寄存器重命名的乱序发布/执行核架构可如下所述地实现流水线2800:1)指令取出2838执行取出级2802和长度解码级2804;2)解码单元2840执行解码级2806;3)重命名/分配器单元2852执行分配级2808和重命名级2810;4)(多个)调度器单元2856执行调度级2812;5)(多个)物理寄存器堆单元2858和存储器单元2870执行寄存器读取/存储器读取级2814;执行集群2860执行执行级2816;6)存储器单元2870和(多个)物理寄存器堆单元2858执行写回/存储器写入级2818;7)各单元可牵涉到异常处置级2822;以及8)引退单元2854和(多个)物理寄存器堆单元2858执行提交级2824。

[0300]

核2890可支持一个或多条指令集(例如,x86指令集(具有已与较新版本一起添加的一些扩展);加利福尼亚州桑尼维尔市的mips技术公司的mips指令集;加利福尼亚州桑尼维尔市的arm控股公司的arm指令集(具有诸如neon之类的任选的附加扩展)),其中包括本文中所描述的(多条)指令。在一个实施例中,核2890包括用于支持紧缩数据指令集扩展(例如,avx1、avx2)的逻辑,由此允许使用紧缩数据来执行由许多多媒体应用使用的操作。

[0301]

应当理解,核可支持多线程化(执行两个或更多个并行的操作或线程的集合),并

且可以按各种方式来完成该多线程化,各种方式包括时分多线程化、同时多线程化(其中单个物理核为物理核正在同时多线程化的线程中的每一个线程提供逻辑核)、或其组合(例如,时分取出和解码以及此后的诸如超线程化技术中的同时多线程化)。

[0302]

尽管在乱序执行的上下文中描述寄存器重命名,但应当理解,寄存器重命名可在有序架构中被使用。尽管所图示的处理器的实施例还包括分开的指令和数据高速缓存单元2834/2874以及共享的l2高速缓存单元2876,但是替代实施例可以具有用于指令和数据两者的单个内部高速缓存,诸如例如,第1级(l1)内部高速缓存或多个级别的内部高速缓存。在一些实施例中,系统可包括内部高速缓存和在核和/或处理器外部的外部高速缓存的组合。替代地,所有高速缓存都可在核和/或处理器的外部。具体的示例性有序核架构

[0303]

图29a-图29b图示出了更具体的示例性有序核架构的框图,该核将是芯片中的若干逻辑块之一(包括相同类型和/或不同类型的其他核)。取决于应用,逻辑块通过高带宽互连网络(例如,环形网络)与一些固定的功能逻辑、存储器i/o接口和其他必要的i/o逻辑进行通信。

[0304]

图29a是根据本发明的实施例的单个处理器核以及该单个处理器核与管芯上互连网络2902的连接及其第2级(l2)高速缓存的本地子集2904的框图。在一个实施例中,指令解码器2900支持具有紧缩数据指令集扩展的x86指令集。l1高速缓存2906允许对进入标量和向量单元中的高速缓存存储器的低等待时间的访问。尽管在一个实施例中(为了简化设计),标量单元2908和向量单元2910使用分开的寄存器集合(分别为标量寄存器2912和向量寄存器2914),并且在这些寄存器之间传输的数据被写入到存储器,并随后从第1级(l1)高速缓存2906读回,但是本发明的替代实施例可以使用不同的方法(例如,使用单个寄存器集合或包括允许数据在这两个寄存器堆之间传输而无需被写入和读回的通信路径)。

[0305]

l2高速缓存的本地子集2904是全局l2高速缓存的部分,该全局l2高速缓存被划分成多个分开的本地子集,每个处理器核对应一个本地子集。每个处理器核具有到其自身的l2高速缓存的本地子集2904的直接访问路径。由处理器核读取的数据被存储在其l2高速缓存子集2904中,并且可以与其他处理器核访问该其他处理器自身的本地l2高速缓存子集并行地被快速访问。由处理器核写入的数据被存储在该处理器核自身的l2高速缓存子集2904中,并在必要的情况下从其他子集转储清除。环形网络确保共享数据的一致性。环形网络是双向的,以允许诸如处理器核、l2高速缓存和其他逻辑块之类的代理在芯片内彼此通信。每个环形数据路径为每个方向1012位宽。

[0306]

图29b是根据本发明的各实施例的图29a中的处理器核的一部分的展开图。图29b包括l1高速缓存2904的l1数据高速缓存2906a部分,以及关于向量单元2910和向量寄存器2914的更多细节。具体而言,向量单元2910是16宽向量处理单元(vpu)(见16宽alu 2928),该单元执行整数、单精度浮点以及双精度浮点指令中的一个或多个。该vpu利用混合单元2920支持对寄存器输入的混合,利用数值转换单元2922a-b支持数值转换,并且利用复制单元2924支持对存储器输入的复制。写掩码寄存器2926允许断言所得的向量写入。

[0307]

图30是根据本发明的多个实施例可能具有多余一个的核、可能具有集成存储器控制器、以及可能具有集成图形器件的处理器3000的框图。图30的实线框图示出了处理器3000,该处理器3000具有单个核3002a、系统代理3010、一个或多个总线控制器单元的集合

3016,而可选附加的虚线框示出了替代的处理器3000,该替代的处理器3000具有多个核3002a-n、系统代理单元3010中的一个或多个集成存储器控制器单元的集合3014、以及专用逻辑3008。

[0308]

因此,处理器3000的不同实现可包括:1)cpu,其中专用逻辑3008是集成图形和/或科学(吞吐量)逻辑(其可包括一个或多个核),并且核3002a-n是一个或多个通用核(例如,通用有序核、通用乱序核、这两者的组合);2)协处理器,其中核3002a-n是旨在主要用于图形和/或科学(吞吐量)的大量专用核;以及3)协处理器,其中核3002a-n是大量通用有序核。由此,处理器3000可以是通用处理器、协处理器或专用处理器,诸如例如,网络或通信处理器、压缩引擎、图形处理器、gpgpu(通用图形处理单元)、高吞吐量的集成众核(mic)协处理器(包括30个或更多个核)、嵌入式处理器,等等。该处理器可以被实现在一个或多个芯片上。处理器3000可以是一个或多个基板的一部分,和/或可使用多种工艺技术(诸如例如,bicmos、cmos、或nmos)中的任何技术被实现在一个或多个基板上。

[0309]

存储器层级结构包括核内的一个或多个高速缓存级别、一组或一个或多个共享高速缓存单元3006、以及耦合至集成存储器控制器单元3014的集合的外部存储器(未示出)。共享高速缓存单元3006的集合可包括一个或多个中间级别的高速缓存、末级高速缓存(llc)和/或以上各项的组合,中间级别的高速缓存诸如第2级(l2)、第3级(l3)、第4级(l4)或其他级别的高速缓存。虽然在一个实施例中,基于环的互连单元3012将集成图形逻辑3008(集成图形逻辑3008是其示例,并且在本文中还被称为专用逻辑)、共享高速缓存单元的集合3006以及系统代理单元3010/(多个)集成存储器控制器单元3014互连,但是替代实施例可使用任何数量的公知技术来互连此类单元。在一个实施例中,在一个或多个高速缓存单元3006与核3002-a-n之间维持一致性。

[0310]

在一些实施例中,核3002a-n中的一个或多个能够实现多线程化。系统代理3010包括协调并操作核3002a-n的那些组件。系统代理单元3010可包括例如功率控制单元(pcu)和显示单元。pcu可以是对核3002a-n以及集成图形逻辑3008的功率状态进行调节所需的逻辑和组件,或可包括这些逻辑和组件。显示单元用于驱动一个或多个外部连接的显示器。

[0311]

核3002a-n在架构指令集方面可以是同构的或异构的;即,核3002a-n中的两个或更多个核可能能够执行相同的指令集,而其他核可能能够仅执行该指令集的子集或者执行不同的指令集。示例性计算机架构

[0312]

图31-图34是示例性计算机架构的框图。本领域中已知的对膝上型设备、台式机、手持pc、个人数字助理、工程工作站、服务器、网络设备、网络集线器、交换机、嵌入式处理器、数字信号处理器(dsp)、图形设备、视频游戏设备、机顶盒、微控制器、蜂窝电话、便携式媒体播放器、手持设备以及各种其他电子设备的其他系统设计和配置也是合适的。一般地,能够包含如本文中所公开的处理器和/或其他执行逻辑的各种各样的系统或电子设备一般都是合适的。

[0313]

现在参考图31,所示出的是根据本发明一个实施例的系统3100的框图。系统3100可包括一个或多个处理器3110、3115,这些处理器耦合至控制器中枢3120。在一个实施例中,控制器中枢3120包括图形存储器控制器中枢(gmch)3190和输入/输出中枢(ioh)3150(其可以在分开的芯片上);gmch3190包括存储器和图形控制器,存储器3140和协处理器

3145耦合到该存储器和图形控制器;ioh 3150将输入/输出(i/o)设备3160耦合到gmch 3190。或者,存储器和图形控制器中的一个或两者被集成在处理器内(如本文中所描述的),存储器3140和协处理器3145直接耦合到处理器3110以及控制器中枢3120,该控制器中枢3120与ioh 3150处于单个芯片中。

[0314]

附加处理器3115的任选性在图31中利用虚线来表示。每一处理器3110、3115可包括本文中所描述的处理核中的一个或多个,并且可以是处理器3000的某一版本。

[0315]

存储器3140可以是例如动态随机存取存储器(dram)、相变存储器(pcm)或这两者的组合。对于至少一个实施例,控制器中枢3120经由诸如前端总线(fsb)之类的多分支总线、诸如快速路径互连(qpi)之类的点对点接口、或者类似的连接3195来与(多个)处理器3110、3115进行通信。

[0316]

在一个实施例中,协处理器3145是专用处理器,诸如例如,高吞吐量mic处理器、网络或通信处理器、压缩引擎、图形处理器、gpgpu、嵌入式处理器,等等。在一个实施例中,控制器中枢3120可包括集成图形加速器。

[0317]

按照包括架构、微架构、热、功耗特征等等优点的度量谱,物理资源3110、3115之间存在各种差别。

[0318]

在一个实施例中,处理器3110执行控制一般类型的数据处理操作的指令。嵌入在这些指令内的可以是协处理器指令。处理器3110将这些协处理器指令识别为具有应当由附连的协处理器3145执行的类型。因此,处理器3110在协处理器总线或者其他互连上将这些协处理器指令(或者表示协处理器指令的控制信号)发布到协处理器3145。(多个)协处理器3145接受并执行所接收的协处理器指令。

[0319]

现在参考图32,所示为根据本发明的实施例的更具体的第一示例性系统3200的框图。如图32所示,多处理器系统3200是点对点互连系统,并且包括经由点对点互连3250而被耦合的第一处理器3270和第二处理器3280。处理器3270和3280中的每一个可以是处理器3000的某一版本。在本发明的一个实施例中,处理器3270和3280分别是处理器3110和3115,而协处理器3238是协处理器3145。在另一实施例中,处理器3270和3280分别是处理器3110、协处理器3145。

[0320]

处理器3270和3280示出为分别包括集成存储器控制器(imc)单元3272和3282。处理器3270还包括作为其总线控制器单元的一部分的点对点(p-p)接口3276和3278;类似地,第二处理器3280包括p-p接口3286和3288。处理器3270、3280可以经由使用点对点(p-p)接口电路3278、3288的p-p接口3250来交换信息。如图32中所示,imc 3272和3282将处理器耦合至相应的存储器,即存储器3232和存储器3234,这些存储器可以是本地附连到相应处理器的主存储器的部分。

[0321]

处理器3270、3280可各自经由使用点对点接口电路3276、3294、3286、3298的各个p-p接口3252、3254来与芯片组3290交换信息。芯片组3290可以任选地经由高性能接口3292来与协处理器3238交换信息。在一个实施例中,协处理器3238是专用处理器,诸如例如,高吞吐量mic处理器、网络或通信处理器、压缩引擎、图形处理器、gpgpu、嵌入式处理器,等等。

[0322]

共享高速缓存(未示出)可被包括在任一处理器中,或在这两个处理器的外部但经由p-p互连与这些处理器连接,使得如果处理器被置于低功率模式,则任一个或这两个处理器的本地高速缓存信息可被存储在共享高速缓存中。

[0323]

芯片组3290可经由接口3296耦合至第一总线3216。在一个实施例中,第一总线3216可以是外围组件互连(pci)总线、或者诸如pci快速总线或另一第三代i/o互连总线之类的总线,但是本发明的范围不限于此。

[0324]

如图32中所示,各种i/o设备3214可连同总线桥3218一起耦合至第一总线3216,该总线桥3218将第一总线3216耦合至第二总线3220。在一个实施例中,诸如协处理器、高吞吐量mic处理器、gpgpu、加速器(诸如例如,图形加速器或数字信号处理(dsp)单元)、现场可编程门阵列或任何其他处理器的一个或多个附加处理器3215耦合到第一总线3216。在一个实施例中,第二总线3220可以是低引脚计数(lpc)总线。各种设备可以被耦合至第二总线3220,在一个实施例中这些设备包括例如键盘/鼠标3222、通信设备3227以及诸如可包括指令/代码和数据3230的盘驱动器或其他大容量存储设备的存储单元3228。此外,音频i/o 3224可耦合至第二总线3220。注意,其他架构是可能的。例如,代替图32的点对点架构,系统可以实现多分支总线或其他这类架构。

[0325]

现在参考图33,所示为根据本发明的实施例的更具体的第二示例性系统3300的框图。图32和图33中的类似元件使用类似附图标记,且在图33中省略了图32的某些方面以避免混淆图33的其它方面。

[0326]

图33示出处理器3270、3280可分别包括集成存储器和i/o控制逻辑(“cl”)3272和3282。由此,cl 3272、3282包括集成存储器控制器单元,并包括i/o控制逻辑。图33图示出不仅存储器3232、3234耦合至cl 3272、3282,而且i/o设备3314也耦合至控制逻辑3272、3282。传统i/o设备3315耦合至芯片组3290。

[0327]

现在参照图34,所示出的是根据本发明的实施例的soc 3400的框图。在图30中,相似的部件具有同样的附图标记。另外,虚线框是更先进的soc上的任选的特征。在图34中,(多个)互连单元3402被耦合到:应用处理器3410,其包括一个或多个核的集合3002a-n以及(多个)共享高速缓存单元3006,一个或多个核的集合3002a-n包括高速缓存单元3004a-n;系统代理单元3010;(多个)总线控制器单元3016;(多个)集成存储器控制器单元3014;一个或多个协处理器的集合3420,其可包括集成图形逻辑、图像处理器、音频处理器和视频处理器;静态随机存取存储器(sram)单元3430;直接存储器存取(dma)单元3432;以及用于耦合到一个或多个外部显示器的显示单元3440。在一个实施例中,(多个)协处理器3420包括专用处理器,诸如例如,网络或通信处理器、压缩引擎、gpgpu、高吞吐量mic处理器、嵌入式处理器,等等。

[0328]

本文中所公开的机制的实施例可被实现在硬件、软件、固件或此类实现方式的组合中。本发明的实施例可实现为在可编程系统上执行的计算机程序或程序代码,该可编程系统包括至少一个处理器、存储系统(包括易失性和非易失性存储器和/或存储元件)、至少一个输入设备以及至少一个输出设备。

[0329]

可将程序代码(诸如,图32中所图示的代码3230)应用于输入指令,以执行本文中所描述的功能并生成输出信息。可以按已知方式将输出信息应用于一个或多个输出设备。为了本技术的目的,处理系统包括具有处理器的任何系统,该处理器诸如例如,数字信号处理器(dsp)、微控制器、专用集成电路(asic)或微处理器。

[0330]

程序代码可以用高级过程编程语言或面向对象的编程语言来实现,以便与处理系统通信。如果需要,也可用汇编语言或机器语言来实现程序代码。事实上,本文中所描述的

机制不限于任何特定的编程语言的范围。在任何情况下,该语言可以是编译语言或解释语言。

[0331]

至少一个实施例的一个或多个方面可由存储在机器可读介质上的表示处理器中的各种逻辑的表示性指令来实现,该表示性指令在由机器读取时使得该机器制造用于执行本文中所描述的技术的逻辑。被称为“ip核”的此类表示可以被存储在有形的机器可读介质上,并可被供应给各个客户或生产设施以加载到实际制造该逻辑或处理器的制造机器中。

[0332]

此类机器可读存储介质可以包括但不限于通过机器或设备制造或形成的物品的非暂态的有形安排,其包括存储介质,诸如:硬盘;任何其他类型的盘,包括软盘、光盘、紧致盘只读存储器(cd-rom)、紧致盘可重写(cd-rw)以及磁光盘;半导体器件,诸如只读存储器(rom)、诸如动态随机存取存储器(dram)和静态随机存取存储器(sram)之类的随机存取存储器(ram)、可擦除可编程只读存储器(eprom)、闪存、电可擦除可编程只读存储器(eeprom);相变存储器(pcm);磁卡或光卡;或适于存储电子指令的任何其他类型的介质。

[0333]

因此,本发明的实施例还包括非暂态的有形机器可读介质,该介质包含指令或包含设计数据,诸如硬件描述语言(hdl),它定义本文中所描述的结构、电路、装置、处理器和/或系统特征。此类实施例也可被称为程序产品。仿真(包括二进制变换、代码变形等)

[0334]

在一些情况下,指令转换器可用来将指令从源指令集转换至目标指令集。例如,指令转换器可以将指令变换(例如使用静态二进制变换、包括动态编译的动态二进制变换)、变形、仿真或以其他方式转换成要由核来处理的一个或多个其他指令。指令转换器可以用软件、硬件、固件、或其组合来实现。指令转换器可以在处理器上、在处理器外、或者部分在处理器上且部分在处理器外。

[0335]

图35是根据本发明的实施例的对照使用软件指令转换器将源指令集中的二进制指令转换成目标指令集中的二进制指令的框图。在所图示的实施例中,指令转换器是软件指令转换器,但替代地,该指令转换器可以用软件、固件、硬件或其各种组合来实现。图35示出可使用x86编译器3504来编译利用高级语言3502的程序,以生成可由具有至少一个x86指令集核的处理器3516原生执行的x86二进制代码3506。具有至少一个x86指令集核的处理器3516表示可以通过兼容地执行或以其他方式处理以下各项来执行与具有至少一个x86指令集核的英特尔处理器基本相同的功能的任何处理器:1)英特尔x86指令集核的指令集的本质部分,或2)目标为在具有至少一个x86指令集核的英特尔处理器上运行以便取得与具有至少一个x86指令集核的英特尔处理器基本相同的结果的应用或其他软件的目标代码版本。x86编译器3504表示可操作用于生成x86二进制代码3506(例如,目标代码)的编译器,该二进制代码可通过或不通过附加的链接处理在具有至少一个x86指令集核的处理器3516上执行。类似地,图35示出可以使用替代的指令集编译器3508来编译高级语言3502的程序以生成可由不具有至少一个x86指令集核的处理器3514(例如,具有执行加利福尼亚州桑尼维尔市的mips技术公司的mips指令集和/或执行加利福尼州桑尼维尔市的arm控股公司的arm指令集的核的处理器)原生地执行的替代的指令集二进制代码3510。指令转换器3512用于将x86二进制代码3506转换成可以由不具有x86指令集核的处理器3514原生执行的代码。该转换后的代码不大可能与替代的指令集二进制代码3510相同,因为能够这样做的指令转换器难以制造;然而,转换后的代码将完成一般操作,并且由来自替代指令集的指令构成。由

此,指令转换器3512通过仿真、模拟或任何其他过程来表示允许不具有x86指令集处理器或核的处理器或其他电子设备执行x86二进制代码3506的软件、固件、硬件或其组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。