1.本技术涉及半导体器件加工领域,特别是涉及一种忆阻器阵列及其制作方法。

背景技术:

2.忆阻器的全称为记忆电阻,是一种有记忆功能的非线性电阻。通过控制电流的变化可改变其阻值,如果把高阻值定义为“1”,低阻值定义为“0”,则这种电阻就可以实现存储数据的功能,具有非易失性、小尺寸、低能耗、高速等特点。忆阻器阵列可以模拟人脑的神经形态系统进行复杂的计算,目前将单个的忆阻器组成导电细丝型忆阻器阵列时,忆阻器的大小为底层电极与顶层电极交叉面积的大小,交叉面积较大,不可调控,使得忆阻器的面积较大,从而导致忆阻器阵列单位面积内忆阻器的数量较少,即器件密度较低,并且导电细丝出现的随机性较高。

3.因此,如何解决上述技术问题应是本领域技术人员重点关注的。

技术实现要素:

4.本技术的目的是提供一种忆阻器阵列及其制作方法,以提升忆阻器阵列中的器件密度,并降低导电细丝出现的随机性。

5.为解决上述技术问题,本技术提供一种忆阻器阵列,包括:

6.衬底;

7.设于所述衬底上交叉分布的底电极阵列和顶电极阵列;所述底电极阵列包括多个底电极,所述顶电极阵列包括多个顶电极;

8.设于所述底电极和所述顶电极之间的、由下至上层叠的第一绝缘层和第二绝缘层;

9.在厚度方向上贯穿所述第一绝缘层的导电连接体阵列;

10.在厚度方向上贯穿所述第二绝缘层的功能体阵列;所述功能体阵列与所述导电连接体阵列相对应。

11.可选的,所述导电连接体阵列中导电连接体的宽度与所述功能体阵列中功能体的宽度相等。

12.可选的,所述导电连接体阵列中导电连接体的宽度大于所述功能体阵列中功能体的宽度。

13.可选的,所述第一绝缘层和所述第二绝缘层的材料相同。

14.可选的,所述导电连接体阵列中导电连接体的形状为圆柱状。

15.本技术还提供一种忆阻器阵列制作方法,包括:

16.在衬底的上表面形成底电极阵列;所述底电极阵列包括多个底电极;

17.在所述底电极的上表面形成第一绝缘层以及在厚度方向上贯穿所述第一绝缘层的导电连接体阵列;

18.在所述第一绝缘层上表面形成第二绝缘层以及在厚度方向上贯穿所述第二绝缘

层的功能体阵列,且所述功能体阵列与所述导电连接体阵列相对应;

19.在所述第二绝缘层的上表面形成与所述底电极阵列交叉的顶电极阵列,形成忆阻器阵列,所述顶电极阵列包括多个顶电极。

20.可选的,所述在所述底电极的上表面形成第一绝缘层以及在厚度方向上贯穿所述第一绝缘层的导电连接体阵列包括:

21.在所述底电极阵列上表面形成第一绝缘层;

22.在所述第一绝缘层上表面涂覆光刻胶,利用光刻和刻蚀工艺在所述第一绝缘层中对应所述底电极的区域形成通孔阵列,并去除所述光刻胶;所述通孔阵列刻蚀停止至所述底电极的上表面;

23.在所述通孔阵列的通孔中填充导电材料形成导电连接体阵列,并对所述第一绝缘层和所述导电连接体阵列进行抛光处理。

24.可选的,所述对所述第一绝缘层和所述导电连接体阵列进行抛光处理包括:

25.采用化学机械抛光方式,对所述第一绝缘层和所述导电连接体阵列进行抛光处理。

26.可选的,所述在所述第一绝缘层上表面形成第二绝缘层以及在厚度方向上贯穿所述第二绝缘层的功能体阵列,且所述功能体阵列与所述导电连接体阵列相对应包括:

27.在所述第一绝缘层上表面形成功能层,并对所述功能层进行图形化处理,形成与所述导电连接体阵列相对应的功能体阵列;

28.在所述功能体阵列中填充绝缘材料形成第二绝缘层,并对所述第二绝缘层进行抛光处理,至所述功能体阵列的上表面露出。

29.可选的,所述形成忆阻器阵列之后,还包括:

30.对所述忆阻器阵列进行高温处理。

31.本技术所提供的一种忆阻器阵列,包括:衬底;设于所述衬底上交叉分布的底电极阵列和顶电极阵列;所述底电极阵列包括多个底电极,所述顶电极阵列包括多个顶电极;设于所述底电极和所述顶电极之间的、由下至上层叠的第一绝缘层和第二绝缘层;在厚度方向上贯穿所述第一绝缘层的导电连接体阵列;在厚度方向上贯穿所述第二绝缘层的功能体阵列;所述功能体阵列与所述导电连接体阵列相对应。

32.可见,本技术中的忆阻器阵列除了包括衬底、底电极阵列、顶电极阵列、功能体阵列,还包括与功能体阵列对应的导电连接体阵列,导电连接体阵列位于底电极阵列与功能体阵列之间,单个忆阻器的面积可以通过功能体阵列与导电连接体阵列的重叠面积进行调控,即通过减小功能体阵列与导电连接体阵列的重叠面积可促使底电极阵列和顶电极阵列交叉面积减小,从而达到减小忆阻器器件的面积的目的,提高了单位忆阻器阵列面积内的忆阻器器件数量,即提高了器件密度,同时,功能体阵列与导电连接体阵列的重叠面积的减小降低了导电细丝出现的随机性。

33.此外,本技术还提供一种具有上述优点的忆阻器阵列制作方法。

附图说明

34.为了更清楚的说明本技术实施例或现有技术的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单的介绍,显而易见地,下面描述中的附图仅仅是本申

请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

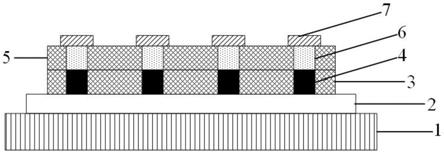

35.图1为本技术实施例所提供的一种忆阻器阵列的俯视图;

36.图2为图1所示忆阻器阵列ab线截面的剖视图;

37.图3为本技术实施例所提供的一种忆阻器阵列制作方法的流程图。

具体实施方式

38.为了使本技术领域的人员更好地理解本技术方案,下面结合附图和具体实施方式对本技术作进一步的详细说明。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

39.在下面的描述中阐述了很多具体细节以便于充分理解本发明,但是本发明还可以采用其他不同于在此描述的其它方式来实施,本领域技术人员可以在不违背本发明内涵的情况下做类似推广,因此本发明不受下面公开的具体实施例的限制。

40.正如背景技术部分所述,目前将单个的忆阻器组成导电细丝型忆阻器阵列时,忆阻器的大小为底层电极与顶层电极交叉面积的大小,交叉面积较大,不可调控,使得忆阻器的面积较大,从而导致忆阻器阵列单位面积内忆阻器的数量较少,即器件密度较低,并且导电细丝出现的随机性较高。

41.有鉴于此,本技术提供了一种忆阻器阵列,请参考图1和图2,包括:

42.衬底1;

43.设于所述衬底1上交叉分布的底电极阵列和顶电极阵列;所述底电极阵列包括多个底电极2,所述顶电极阵列包括多个顶电极7;

44.设于所述底电极2和所述顶电极7之间的、由下至上层叠的第一绝缘层3和第二绝缘层5;

45.在厚度方向上贯穿所述第一绝缘层3的导电连接体阵列;

46.在厚度方向上贯穿所述第二绝缘层5的功能体阵列;所述功能体阵列与所述导电连接体阵列相对应。

47.衬底1一般为硅衬底1。

48.本技术中对底电极2和顶电极7的形状并不做具体限定,只要保证底电极阵列和顶电极阵列相互交叉即可。例如,顶电极7和底电极2的形状可以为长方形,梯形等等。

49.为了增强底电极2与衬底1之间的黏附性能,底电极2包括黏附层和电极层,黏附层材料可以选用钛等黏附性较强的材料,电极层的材料可以选用铂、银、钽等金属材料。

50.第一绝缘层3的材料包括但不限于硼磷硅玻璃、聚酰亚胺,第二绝缘层5的材料包括但不限于硼磷硅玻璃、聚酰亚胺。可选的,所述第一绝缘层3和所述第二绝缘层5的材料相同。

51.导电连接体阵列包括多个导电连接体4,功能体阵列包括多个功能体6,导电连接体4与功能体6一一对应。每一个导电连接体4的下表面与底电极2导通。

52.为了简化导电连接体4的制作工艺,所述导电连接体阵列中导电连接体4的形状为圆柱状。当然,也可以根据需要设置成其他形状,本技术不进行具体限定。

53.导电连接体4与功能体6重叠区域的面积决定了忆阻器的面积,重叠区域的面积大小决定了底电极阵列与顶电极阵列交叉面积的最小值,底电极阵列与顶电极阵列交叉面积的大小为忆阻器的面积。需要指出的是,本技术中对导电连接体4与功能体6之间的大小关系不做限定。可选的,所述导电连接体阵列中导电连接体4的宽度与所述功能体阵列中功能体6的宽度相等,如图2所示,此时,忆阻器的面积由导电连接体4的横截面积或者功能体6的横截面积决定,也即通过减小导电连接体4的横截面积或者功能体6的横截面积,减小忆阻器的面积。或者,所述导电连接体阵列中导电连接体4的宽度大于所述功能体阵列中功能体6的宽度,此时,忆阻器的面积由功能体6的横截面积决定。

54.导电连接体4的材料一般选用金属材料,例如铂、铜、银等等。功能体6一般为金属氧化物,例如氧化钽。

55.本技术中的忆阻器阵列除了包括衬底1、底电极阵列、顶电极阵列、功能体阵列,还包括与功能体阵列对应的导电连接体阵列,导电连接体阵列位于底电极阵列与功能体阵列之间,单个忆阻器的面积可以通过功能体阵列与导电连接体阵列的重叠面积进行调控,即通过减小功能体阵列与导电连接体阵列的重叠面积可促使底电极阵列和顶电极阵列交叉面积减小,从而达到减小忆阻器器件的面积的目的,提高了单位忆阻器阵列面积内的忆阻器器件数量,即提高了器件密度,同时,功能体阵列与导电连接体阵列的重叠面积的减小降低了导电细丝出现的随机性。

56.请参考图3,本技术还提供一种忆阻器阵列制作方法,该方法包括:

57.步骤s101:在衬底的上表面形成底电极阵列;所述底电极阵列包括多个底电极。

58.具体的,在衬底上表面形成底电极层,并在底电极层上表面涂覆光刻胶,通过光刻和刻蚀工艺形成底电极阵列,并去除光刻胶。

59.可选的,在形成底电极阵列之前,还可以对衬底进行清洁。

60.步骤s102:在所述底电极的上表面形成第一绝缘层以及在厚度方向上贯穿所述第一绝缘层的导电连接体阵列。

61.可选的,作为一种具体实施方式,步骤s102包括:

62.步骤s201:在所述底电极阵列上表面形成第一绝缘层。

63.为了保证第一绝缘层的厚度均匀性,采用旋涂方式制作第一绝缘层。

64.步骤s202:在所述第一绝缘层上表面涂覆光刻胶,利用光刻和刻蚀工艺在所述第一绝缘层中对应所述底电极的区域形成通孔阵列,并去除所述光刻胶;所述通孔阵列刻蚀停止至所述底电极的上表面。

65.本实施中对通孔的形成方式不做限定,可自行选择。例如,可以选用icp(inductive coupled plasma,电感耦合等离子)刻蚀方式,或者离子束刻蚀方式。

66.步骤s203:在所述通孔阵列的通孔中填充导电材料形成导电连接体阵列,并对所述第一绝缘层和所述导电连接体阵列进行抛光处理。

67.优选地,所述对所述第一绝缘层和所述导电连接体阵列进行抛光处理包括:

68.采用化学机械抛光方式,对所述第一绝缘层和所述导电连接体阵列进行抛光处理,以降低第一绝缘层和导电连接体阵列的表面粗糙度,利于提高忆阻器阵列中的忆阻器器件的一致性。

69.可选的,作为另一种方式,还可以先在底电极阵列上表面形成底电极层,并刻蚀底

电极层形成底电极阵列,然后在底电极阵列中填充第一绝缘层,并对第一绝缘层进行抛光处理,至底电极阵列的上表面露出。

70.步骤s103:在所述第一绝缘层上表面形成第二绝缘层以及在厚度方向上贯穿所述第二绝缘层的功能体阵列,且所述功能体阵列与所述导电连接体阵列相对应。

71.可选的,作为一种具体实施方式,步骤s103包括:

72.步骤s301:在所述第一绝缘层上表面形成功能层,并对所述功能层进行图形化处理,形成与所述导电连接体阵列相对应的功能体阵列。

73.可以采用溅射工艺制备功能层,然后采用光刻工艺及电感耦合等离子刻蚀工艺对功能层进行图形化处理形成功能体阵列。

74.步骤s302:在所述功能体阵列中填充绝缘材料形成第二绝缘层,并对所述第二绝缘层进行抛光处理,至所述功能体阵列的上表面露出。

75.可以采用旋涂工艺制备第二绝缘层,以提升第二绝缘层厚度的均匀性。

76.第二绝缘层抛光处理时,可以采用化学机械抛光方式进行减薄,以降低功能体阵列和第二绝缘层的表面粗糙度,利于提高忆阻器阵列中的忆阻器器件的一致性。

77.可选的,作为另一种方式,还可以在第一绝缘层上先形成第二绝缘层,在第二绝缘层上表面涂覆光刻胶,利用光刻和刻蚀工艺在所述第二绝缘层中对应导电连接体的区域形成通孔,去除光刻胶,然后在通孔中填充功能体的材料,形成功能体阵列,并进行抛光处理。

78.步骤s104:在所述第二绝缘层的上表面形成与所述底电极阵列交叉的顶电极阵列,形成忆阻器阵列,所述顶电极阵列包括多个顶电极。

79.在第二绝缘层的上表面涂敷光刻胶,采用光刻和刻蚀工艺形成顶电极阵列图形,然后采用溅射法制备顶电极,去除光刻胶,形成顶电极阵列。

80.本技术中制作方法得到的忆阻器阵列,除了包括衬底、底电极阵列、顶电极阵列、功能体阵列,还包括与功能体阵列对应的导电连接体阵列,导电连接体阵列位于底电极阵列与功能体阵列之间,单个忆阻器的面积可以通过功能体阵列与导电连接体阵列的重叠面积进行调控,即通过减小功能体阵列与导电连接体阵列的重叠面积可促使底电极阵列和顶电极阵列交叉面积减小,从而达到减小忆阻器器件的面积的目的,提高了单位忆阻器阵列面积内的忆阻器器件数量,即提高了器件密度,同时,功能体阵列与导电连接体阵列的重叠面积的减小降低了导电细丝出现的随机性。

81.在上述实施例的基础上,在本技术的一个实施例中,忆阻器阵列制作方法在所述形成忆阻器阵列之后,还包括:

82.对所述忆阻器阵列进行高温处理,以提升功能体中的氧空位,进而提升忆阻器阵列的一致性。

83.下面以一具体情况对本技术中的忆阻器阵列制作方法进行介绍。

84.步骤1、衬底清洗:将硅衬底放入丙酮、无水乙醇和去离子水中清洗并用氮气枪吹干,最后在150℃热板上烘烤3min以去除表面水汽;

85.步骤2、底电极阵列的制备:在硅衬底上涂敷光刻胶,通过光刻和刻蚀工艺形成底电极图形(本例中为长条形),通过金属溅射工艺制备底电极ti/pt,ti、pt金属厚度分别为10nm和40nm,去除光刻胶后形成底电极阵列。

86.步骤3、第一绝缘层制备:选用硼磷硅玻璃(boro-phospho-silicate glass,bpsg)

材料作为第一绝缘层材料,高温环境下旋涂bpsg,待冷却固化后形成第一绝缘层。

87.步骤4、通孔制备:在第一绝缘层上涂敷光刻胶,采用icp(inductive coupled plasma,电感耦合等离子)刻蚀对第一绝缘层进行干法蚀刻,蚀刻至底电极位置停止,形成直径为100nm的通孔,通孔位置与底电极相对应,并去除光刻胶。

88.步骤5、导电连接体阵列制备:采用电子束蒸镀工艺在第一绝缘层上蒸镀金属pt,直至将通孔填冲完毕形成金属柱,采用cmp(chemical mechanical polishing,化学机械抛光)方式进行减薄抛光,将金属柱和第一绝缘层厚度减薄至30nm,形成导电连接体阵列。

89.步骤6、功能体阵列制备:采用溅射工艺制备功能层,溅射靶材为金属ta,并在真空度小于2

×

10-6

torr、氩气和氧气的气流量之比为12:2、溅射功率为140w的环境下磁控溅射20nm的tao

x

功能层;采用光刻工艺及icp刻蚀工艺将功能层图形化,形成功能体阵列,并与导电连接体阵列相互对应。

90.步骤7、第二绝缘层制备:选用聚酰亚胺为第二绝缘层材料,通过旋涂及烘干工艺将将功能体阵列空隙填充,并采用cmp工艺进行减薄抛光,直至将tao

x

功能层全部露出。

91.步骤8、顶电极阵列制备:涂敷光刻胶,通过光刻和刻蚀工艺形成顶电极图形(本例中为长条形),通过金属溅射工艺制备顶电极ta/pt,ta、pt金属厚度分别为40nm和60nm,去除光刻胶后形成顶电极阵列,得到忆阻器阵列。

92.步骤9、高温处理:将忆阻器阵列置于130℃环境下进行高温处理。

93.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其它实施例的不同之处,各个实施例之间相同或相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

94.以上对本技术所提供的忆阻器阵列及其制作方法进行了详细介绍。本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想。应当指出,对于本技术领域的普通技术人员来说,在不脱离本技术原理的前提下,还可以对本技术进行若干改进和修饰,这些改进和修饰也落入本技术权利要求的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。