1.本公开总体上关于转阻抗放大器(transimpedance amplifier),尤其涉及可以在大范围的频宽上工作的差分转阻抗放大器(differential transimpedance amplifier,dita)。

背景技术:

2.信号通常由一个准位可变的电压或电流来表示,准位承载某些随时间变化的信息。信号在某一时刻的准位表示信号在该时刻的状态。

3.转阻抗放大器在输入节点接收输入信号,并在输出节点输出输出信号,其中,输入节点是一个低阻抗节点,而输出节点是一个高阻抗节点。输入信号是电流,而输出信号是电压。输出信号和输入信号之间的比值是转阻抗放大器的增益。

4.差分信号是包含一第一子信号及一第二子信号的信号,其中,差分信号的值是该第一子信号与该第二子信号之间的差。该第一子信号及该第二子信号具有相同的振幅和频率,但是相位相反。

5.差分转阻抗放大器是一种转阻抗放大器,其输入信号和输出信号均为差分信号。

6.转阻抗放大器通常由配置成负反馈拓扑的运算放大器来实现,且负反馈拓扑具有反馈电阻,而反馈电阻决定转阻抗放大器的增益。然而,基于稳定性的考量,以负反馈拓扑配置的运算放大器的频宽受到限制。实际上,当采用现代互补式金属氧化物半导体(complementary metal oxide semiconductor,cmos)的工艺技术时,以配置成反馈拓扑的差分运算放大器为基础的差分转阻抗放大器最多只能工作在几兆赫兹(mega-hertz)。

7.因此需要一个可以在超过十吉赫兹(giga-hertz)的频宽上工作的差分转阻抗放大器。

技术实现要素:

8.在一个实施例中,一种差分转阻抗放大器包含:包含一第一n通道金属氧化物半导体(nmos)晶体管及一第二nmos晶体管的一第一对共栅极放大器,该第一nmos晶体管及该第二nmos晶体管通过一第一电容器和一第二电容器配置成交叉耦合拓扑;以及包含一第一p通道金属氧化物半导体(pmos)晶体管及一第二pmos晶体管的一第二对共栅极放大器,该第一pmos晶体管及该第二pmos晶体管通过一第三电容器和一第四电容器配置成交叉耦合拓扑;其中该第一对共栅极放大器的输出及该第二对共栅极放大器的输出通过一第五电容器及一第六电容器耦合。

9.在一个实施例中,一种差分转阻抗放大器(differential transimpedance amplifier)包含:包含一第一n通道金属氧化物半导体(nmos)晶体管及一第二nmos晶体管的一第一差分对、包含一第一p通道金属氧化物半导体(pmos)晶体管及一第二pmos晶体管的一第二差分对、一第一电容器、一第二电容器、一第三电容器、一第四电容器、一第五电容器、一第六电容器、一第一偏压网络、一第二偏压网络、一第三偏压网络、一第四偏压网络、

一第一负载网络、一第二负载网络、一第三负载网络,以及一第四负载网络;其中,该第一nmos晶体管的一源极、一栅极及一漏极分别连接到一第一输入节点、一第一栅极节点及一第一输出节点;该第二nmos晶体管的一源极、一栅极及一漏极分别连接到一第二输入节点、一第二栅极节点及一第二输出节点;该第一pmos晶体管的一源极、一栅极及一漏极分别连接到该第一输入节点、一第三栅极节点及一第三输出节点;该第二pmos晶体管的一源极、一栅极及一漏极分别连接到该第二输入节点、一第四栅极节点及一第四输出节点;该第一电容器将该第一栅极节点耦接到该第二输入节点;该第二电容器将该第二栅极节点耦接到该第一输入节点;该第三电容器将该第三栅极节点耦接到该第二输入节点;该第四电容器将该第四栅极节点耦接到该第一输入节点;该第五电容器将该第一输出节点耦接到该第三输出节点;该第六电容器将该第二输出节点耦接到该第四输出节点;该第一偏压网络在该第一栅极节点建立一第一直流偏压;该第二偏压网络在该第二栅极节点建立一第二直流偏压;该第三偏压网络在该第三栅极节点建立一第三直流偏压;该第四偏压网络在该第四栅极节点建立一第四直流偏压;该第一负载网络在一电源节点与该第一输出节点之间提供直流耦合;该第二负载网络在该电源节点与该第二输出节点之间提供直流耦合;该第三负载网络在一接地节点与该第三输出节点之间提供直流耦合;以及该第四负载网络在该接地节点与该第四输出节点之间提供直流耦合。

10.在一个实施例中,一种方法包含:整合(incorporating)以共栅极放大器拓扑配置的第一nmos晶体管,其中,第一nmos晶体管的源极、栅极与漏极分别连接到第一输入节点、第一栅极节点与第一输出节点;整合以共栅极放大器拓扑配置的第二nmos晶体管,其中,第二nmos晶体管的源极、栅极与漏极分别连接到第二输入节点、第二栅极节点与第二输出节点;整合以共栅极放大器拓扑配置的第一pmos晶体管,其中,第一pmos晶体管的源极、栅极与漏极分别连接到第一输入节点、第三栅极节点与第三输出节点;整合以共栅极放大器拓扑配置的第二pmos晶体管,其中,第二pmos晶体管的源极、栅极与漏极分别连接到第二输入节点、第四栅极节点与第四输出节点;使用第一电容器将第二输入节点耦接到第一栅极节点;使用第二电容器将第一输入节点耦接到第二栅极节点;使用第三电容器将第二输入节点耦接到第三栅极节点;使用第四电容器将第一输入节点耦接到第四栅极节点;使用第五电容器将第一输出节点耦接到第三输出节点;使用第六电容器将第二输出节点耦接到第四输出节点;使用第一偏压网络在第一栅极节点建立第一直流偏压;使用第二偏压网络在第二栅极节点建立第二直流偏压;使用第三偏压网络在第三栅极节点建立第三直流偏压;使用第四偏压网络在第四栅极节点建立第四直流偏压;使用第一负载网络在第一输出节点与电源节点之间提供直流耦合;使用第二负载网络在第二输出节点与电源节点之间提供直流耦合;使用第三负载网络在第三输出节点与接地节点之间提供直流耦合,以及使用第四负载网络在第四输出节点与接地节点之间提供直流耦合。

附图说明

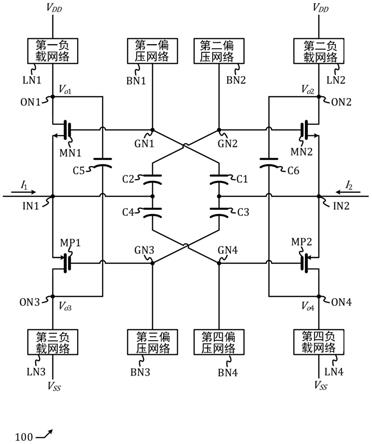

11.图1显示本公开一实施例的差分转阻抗放大器的示意图;

12.图2显示可用于图1的差分转阻抗放大器的偏压网络的示意图;

13.图3显示可用于图1的差分转阻抗放大器的负载网络的示意图;

14.图4显示输出组合网络的示意图;以及

15.图5显示本公开的方法的流程图。

16.符号说明

17.100:差分转阻抗放大器(dtia)

18.mn1、mn2、mp1、mp2:晶体管

19.c1、c2、c3、c4、c5、c6:电容器

20.in1、in2:输入节点

21.on1、on2、on3、on4:输出节点

22.ln1、ln2、ln3、ln4:负载网络

23.bn1、bn2、bn3、bn4:偏压网络

24.gn1、gn2、gn3、gn4:栅极节点

[0025]vo1

、v

o2

、v

o3

、v

o4

:输出电压

[0026]

i1、i2:电流

[0027]vdd

:电源节点

[0028]vss

:接地节点

[0029]

rg1、rg2、rg3、rg4:栅极电阻器

[0030]vb1

、v

b2

、v

b3

、v

b4

:偏压电压

[0031]

rd1、rd2、rd3、rd4:漏极电阻器

[0032]

400:输出组合网络

[0033]vco1

、v

co2

:合并输出电压

[0034]

401、402、403、404:附加电容器

[0035]

610~680:步骤

具体实施方式

[0036]

本公开涉及转阻抗放大器。虽然说明书描述了本公开中实施本发明的数个示例性的实施例,但是应当理解,本发明可以以多种方式实现,并且不限于以下描述的特定示例或是实作所述示例的任何特征的特定方式。在其他情况下,为了专注于讨论本公开的各个层面,不显示或描述众所周知的细节。

[0037]

本技术领域技术人员理解与本公开中所使用的与微电子有关的术语和基本概念,例如“电压”、“电流”、“信号”、“频率”、“电源”、“(接)地”、“互补式金属氧化物半导体(complementary metal oxide semiconductor,coms)”、“n通道金属氧化物半导体(n-channel metal oxide semiconductor,nmos)”、“p通道金属氧化物半导体(p-channel metal oxide semiconductor,pmos)”、“电容器”、“电阻器”、“放大器”、“共栅极放大器”、“差分”、“交流(ac)”、“直流(dc)”、“偏压”及“负载”。这类的术语在微电子学的领域中使用,并且相关的概念对于本技术领域技术人员而言是显而易见的,因此这里将不详细说明。

[0038]

本技术领域技术人员可以认得电容器符号、电阻器符号以及可以认得金属氧化物半导体(metal-oxide semiconductor,mos)晶体管符号(包含pmos晶体管和nmos晶体管),并且可以识别其“源极”、“栅极”和“漏极”等端点。本技术领域技术人员可以阅读包含电容器、电阻器、nmos晶体管及pmos晶体管等元件的电路的示意图,并且不需要关于在示意图中一个元件如何连接另一元件的详细描述。与mos晶体管有关的部分,为了简洁起见,以下将“源极端子”简称为“源极”、将“栅极端子”简称为“栅极”,以及将“漏极端子”简称为“漏极”。本技术领域技术人员还理解诸如“ohm(欧姆)”、“kohm(千欧姆)”、“ghz(吉赫)”、“nm(纳米)”、“ma(微安培)”以及“mm(微米)”等单位的含义。

[0039]

本公开是以工程概念做描述。例如,关于两个变量x和y,当说“x等于y”时,意味着“x大约等于y”,即“x和y之间的差小于指定的工程公差”。当说“x为零”时,表示“x约为零”,即“x小于指定的工程公差”。当说“x显著小于y”时,意味着“相对于y而言x可以忽略不计”,即“x与y的比小于工程公差,因此与y相比x可以忽略不计”。

[0040]

在整个本公开中,“v

dd”表示电源节点以及“v

ss”表示接地节点。接地节点的电压基本上是固定的且大约为0。电源节点的电压基本上是固定的且大约等于一个高于0的电源电压。在本公开中,取决于对于本技术领域技术人员来说是显而易见的上下文,有时v

dd

是指电源节点v

dd

处的电压准位。例如,很明显的,“v

dd

为1.05v”的意思是电源节点v

dd

上的电压准位为1.05v。

[0041]

一个电路是晶体管、电容器、电阻器及/或其他电子元件的集合,晶体管、电容器、电阻器及/或其他电子元件以某种方式相互连接以实现某种功能。网络是电路或电路的集合。

[0042]

第一节点和第二节点之间的交流耦合导致该第一节点处的电压瞬时变化约等于该第二节点处的电压瞬时变化,并且没有直流可以在该第一节点及该第二节点之间流动。通常使用足够大的电容器来实现交流耦合。

[0043]

第一节点和第二节点之间的直流耦合允许直流电流在该第一节点及该第二节点之间流动。

[0044]

共栅极放大器包含mos晶体管,该mos晶体管由其栅极接收控制,并且根据该控制,由其源极接收输入以及由其漏极输出输出。

[0045]

图1显示本公开一实施例的差分转阻抗放大器100(以下简称为dtia100)的示意图。dtia 100分别通过第一输入节点in1及第二输入节点in2接收第一电流i1和第二电流i2,并且分别在第一输出节点on1、第二输出节点on2、第三输出节点on3及第四输出节点on4分别输出第一输出电压v

o1

、第二输出电压v

o2

、第三输出电压v

o3

及第四输出电压v

o4

。dtia 100包含第一nmos晶体管mn1、第二nmos晶体管mn2、第一pmos晶体管mp1、第二pmos晶体管mp2、第一负载网络ln1、第二负载网络ln2、第三负载网络ln3、第四负载网络ln4、第一电容器c1、第二电容器c2、第三电容器c3、第四电容器c4、第五电容器c5、第六电容器c6、第一偏压网络bn1、第二偏压网络bn2、第三偏压网络bn3及第四偏压网络bn4。有四个栅极节点:第一栅极节点gn1、第二栅极节点gn2、第三栅极节点gn3及第四栅极节点gn4。如前面提到的,“v

dd”表示电源节点,而“v

ss”表示接地节点。

[0046]

为简洁起见,在下文中将第一(第二)nmos晶体管mn1(mn2)简称为mn1(mn2)、将第一(第二)pmos晶体管mp1(mp2)简称为mp1(mp2)、将第一(第二、第三、第四、第五、第六)电容器c1(c2、c3、c4、c5、c6)简称为c1(c2、c3、c4、c5、c6)、将第一(第二、第三、第四)偏压网络bn1(bn2、bn3、bn4)简称为bn1(bn2、bn3、bn4)、将第一(第二、第三、第四)负载网络ln1(ln2、ln3、ln4)简称为ln1(ln2、ln3、ln4)、将第一(第二、第三、第四)栅极节点gn1(gn2、gn3、gn4)简称为gn1(gn2、gn3、gn4)、将第一(第二、第三、第四)输出节点on1(on2、on3、on4)简称为on1(on2、on3、on4)、将第一(第二)输入节点in1(in2)简称为in1(in2),以及将第一(第二、

第三、第四)输出电压v

o1

(v

o2

、v

o3

、v

o4

)简称为v

o1

(v

o2

、v

o3

、v

o4

)。采用以上的简称不会造成任何不明确,因为本公开的所有标号都是唯一的。例如,在整个本公开中,除了“该第一nmos晶体管mn1”之外并没有其他“mn1”,因此,当提到“mn1”时,必定毫无疑问地是指“该第一nmos晶体管mn1”。

[0047]

mn1(mn2)的源极、栅极和漏极分别连接到in1(in2)、gn1(gn2)及on1(on2)。mp1(mp2)的源极、栅极和漏极分别连接到in1(in2)、gn3(gn4)及on3(on4)。c1(c2、c3、c4)在in2(in1、in1、in2)与gn1(gn2、gn3、gn4)之间提供交流耦合。bn1(bn2、bn3、bn4)连接到gn1(gn2、gn3、gn4),以便为mn1(mn2、mp1、mp2)建立第一(第二、第三、第四)直流偏压。ln1(ln2)在on1(on2)与电源节点之间提供直流耦合,并作为mn1(mn2)的负载。ln3(ln4)在on3(on4)与接地节点v

ss

之间提供直流耦合,并作为mp1(mp2)的负载。c5(c6)在on1(on2)与on3(on4)之间提供交流耦合。

[0048]

四个晶体管mn1、mn2、mp1及mp2全部都配置为共栅极放大器拓扑,其中偏压条件分别由bn1、bn2、bn3及bn4建立。mn1与mn2通过c1及c2交叉耦合

──

mn1的栅极通过c1耦接mn2的源极,且mn2的栅极通过c2耦接mn1的源极。mn1与mn2之间的交叉耦合相互增强了彼此的增益。同样,mp1与mp2通过c3及c4交叉耦合

──

mp1的栅极通过c3耦接mp2的源极,且mp2的栅极通过c4耦接mp1的源极。mp1与mp2之间的交叉耦合相互增强了彼此的增益。ln1和ln2被配置为从电源节点v

dd

分别为由mn1和mn2所实现的共栅极放大器提供端接(termination),ln3和ln4被配置为从接地节点v

ss

分别为由mp1和mp2所实现的共栅极放大器提供端接。

[0049]

dtia 100具有两个重要的特征。其一,使用互补差分拓扑,其中mn1与mn2形成该第一差分对,mp1与mp2形成该第二差分对,并且该第一差分对与该第二差分对是互补的,并且该第一差分对的直流电流被该第二差分对再利用。流经mn1的直流电被mp1再利用,而流经mn2的直流电被mp2再利用。重复利用电流是一种高效的能源利用方式。其二,有四个输出:v

o1

、v

o2

、v

o3

及v

o4

,但是v

o1

与v

o3

通过c5交流耦合,而v

o2

与v

o4

通过c6交流耦合。因为通过c5交流耦合,所以v

o1

与v

o3

实际上是相同的信号,其中v

o1

的瞬时变化约等于v

o3

的瞬时变化。同样地,因为通过c6交流耦合,所以v

o2

与v

o4

实际上是相同的信号。v

o1

与v

o3

通过c5互相帮助以增大输出摆幅。在没有实作c5的情况下,由于mn1没有将v

o1

拉高的能力,所以v

o1

因v

dd

所限制的宽限(headroom)而有其上限;另一方面,由于mp1没有将v

o3

拉低的能力,所以v

o3

因v

ss

所限制的宽限而有其下限。借由通过c5提供交流耦合,mp1可以通过c5拉高v

o1

,使其摆动高于上限,而mn1可以通过c5拉低v

o3

,使其摆动低于下限。同样地,v

o2

和v

o4

通过c6互相帮助以增大输出摆幅。因此,第一差分对与第二差分对是互补的,并且彼此互相帮助以增大输出摆幅。

[0050]

图2显示bn1、bn2、bn3及bn4的实施例。bn1包含第一栅极电阻器rg1,第一栅极电阻器rg1被配置为将第一偏压电压v

b1

耦接到gn1。bn2包含第二栅极电阻器rg2,第二栅极电阻器rg2被配置为将第二偏压电压v

b2

耦接到gn2。bn3包含第三栅极电阻器rg3,第三栅极电阻器rg3被配置为将第三偏压电压v

b3

耦接到gn3。bn4包含第四栅极电阻器rg4,第四栅极电阻器rg4被配置为将第四偏压电压v

b4

耦接到gn4。在一个实施例中,第一偏压电压v

b1

与第二偏压电压v

b2

相同,而第三偏压电压v

b3

与第四偏压电压v

b4

相同。

[0051]

图3显示ln1、ln2、ln3及ln4的实施例。ln1包含第一漏极电阻器rd1,第一漏极电阻器rd1被配置为耦合电源节点v

dd

至on1。ln2包含第二漏极电阻器rd2,第二漏极电阻器rd2被配置为耦合电源节点v

dd

至on2。ln3包含第三漏极电阻器rd3,第三漏极电阻器rd3被配置为

耦合接地节点v

ss

至on3。ln4包含第四漏极电阻器rd4,第四漏极电阻器rd4被配置为耦合接地节点v

ss

至on4。

[0052]

在图4所示的另一实施例中,输出组合网络400用于将v

o1

、v

o2

、v

o3

及v

o4

合并为两个合并的输出电压,包含:第一合并输出电压v

co1

及第二合并输出电压v

co2

。输出组合网络400包含四个附加电容器401、402、403及404。四个附加电容器401、402、403及404是相同的。电容器401和403实现第一均值函数(mean function),并且用于建立第一合并输出电压v

co1

(就交流成分而言,第一合并输出电压v

co1

等于v

o1

和v

o3

的平均);同样地,电容器402和404实现第二均值函数,并且用于建立第二合并输出电压v

co2

(就交流成分而言,第二合并输出电压v

co2

等于v

o2

和v

o4

的平均)。

[0053]

dtia 100可以是高速电路,因为它是速度不受稳定性限制的开回路(open-loop)电路。

[0054]

举例来说(但不以此为限),dtia 100使用28nm的cmos工艺制造;v

dd

是1.05v;v

ss

是0v;第一电流i1和第二电流i2的大小(振幅)相同(200ma)、频率相同(14.4ghz),但相位相反;四个晶体管mn1、mn2、mp1及mp2的宽度和长度分别为9.6μm和30nm;电容器c1、c2、c3及c4均为200ff;电容器c5和c6均为32ff;图2中的电阻rg1、rg2、rg3及rg4均为12kohm;图2中的v

b1

和v

b2

均为1.05v;图2中的v

b3

和v

b4

均为0v;图3中的电阻rd1、rd2、rd3及rd4均为800ohm;以及图4中的电容器401、402、403及404均为25ff。

[0055]

如图5的流程图所示,本公开的一实施例的方法包含:(步骤610)整合(incorporating)以共栅极放大器拓扑配置的第一nmos晶体管,其中,第一nmos晶体管的源极、栅极与漏极分别连接到第一输入节点、第一栅极节点与第一输出节点;(步骤620)整合以共栅极放大器拓扑配置的第二nmos晶体管,其中,第二nmos晶体管的源极、栅极与漏极分别连接到第二输入节点、第二栅极节点与第二输出节点;(步骤630)整合以共栅极放大器拓扑配置的第一pmos晶体管,其中,第一pmos晶体管的源极、栅极与漏极分别连接到第一输入节点、第三栅极节点与第三输出节点;(步骤640)整合以共栅极放大器拓扑配置的第二pmos晶体管,其中,第二pmos晶体管的源极、栅极与漏极分别连接到第二输入节点、第四栅极节点与第四输出节点;(步骤650)使用第一电容器将第二输入节点耦接到第一栅极节点、使用第二电容器将第一输入节点耦接到第二栅极节点、使用第三电容器将第二输入节点耦接到第三栅极节点,以及使用第四电容器将第一输入节点耦接到第四栅极节点;(步骤660)使用第五电容器将第一输出节点耦接到第三输出节点,以及使用第六电容器将第二输出节点耦接到第四输出节点;(步骤670)使用第一偏压网络在第一栅极节点建立第一直流偏压、使用第二偏压网络在第二栅极节点建立第二直流偏压、使用第三偏压网络在第三栅极节点建立第三直流偏压,以及使用第四偏压网络在第四栅极节点建立第四直流偏压;(步骤680)使用第一负载网络在第一输出节点与电源节点之间提供直流耦合、使用第二负载网络在第二输出节点与电源节点之间提供直流耦合、使用第三负载网络在第三输出节点与接地节点之间提供直流耦合,以及使用第四负载网络在第四输出节点与接地节点之间提供直流耦合。

[0056]

本领域技术人员将容易地观察到,在保持本公开的教导的同时,可以对装置和方法进行多种修改和变更。因此,以上公开不应被解释为仅由所附权利要求的界限来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。