1.本技术涉及一种能够降低线路层离子迁移风险的封装体、该封装体的制备方法以及应用该封装体的终端。

背景技术:

2.随着电子设备的快速发展,电子产品的封装面向轻薄短小、多功能、高性能以及低成本的方向发展,因此,对电子设备内部的半导体器件的封装要求越来越高。

3.现有的封装技术中,是将半导体集成电路(ic)芯片与封装基板电性连接形成封装产品,其中,芯片与封装基板之间通常利用重布线路层技术(rdl:redistribution layer)来实现电性连接。然而,重布线路层易发生离子迁移,造成线路短路,从而降低封装产品的良率和使用寿命。

技术实现要素:

4.本技术实施例第一方面提供了一种封装体,该封装体包括封装基体和第一隔离层,所述封装基体包括半导体衬底、形成于所述半导体衬底表面的钝化层以及形成于所述钝化层表面且与所述半导体衬底电性连接的线路层,所述线路层包括金属线路和线路开口,所述钝化层于所述线路开口露出;所述第一隔离层形成于所述金属线路的表面且延伸至所述线路开口内并覆盖露出于所述线路开口的所述钝化层,所述第一隔离层对应所述金属线路开设有第一开孔,所述金属线路于所述第一开孔露出。

5.在所述金属线路以及钝化层的表面通过形成所述第一隔离层的方式,可以有效隔绝水汽,防止所述金属线路受到水汽的影响而发生离子迁移,同时第一隔离层还能够起到隔断离子迁移路径的作用,从而提升所述封装体的性能稳定性,进而提高产品良率和寿命;另外,无需设置绝缘层,而第一隔离层的厚度相对传统绝缘层厚度薄,有利于降低封装体的总厚度。

6.在一些实施例中,所述第一隔离层的材质为具有吸水率不高于1.1%,以及电阻率不低于10^13ω

·

cm的材料。

7.采用吸水率不高于1.1%,电阻率不低于10^13ω

·

cm的材料形成第一隔离层,能够提高所述第一隔离层的隔离水汽的效果,同时起到阻断离子迁移路径的目的。

8.在一些实施例中,所述第一隔离层的材料为二氧化硅或氮化硅。

9.氮化硅或二氧化硅不易吸水,具有比较高的防水效果,能够有效防止水汽与金属线路接触,影响金属线路的电性能,同时也能防止水汽与钝化层接触,进而影响所述半导体衬底的性能。另外,氮化硅或二氧化硅的电阻率较高,能够有效阻断离子的迁移路径,提高封装体的良率和寿命。

10.在一些实施例中,所述封装体还包括形成于所述第一隔离层靠近所述钝化层一侧的第二隔离层。

11.所述第一隔离层与所述第二隔离层复合形成第一复合隔离层,其中所述第二隔离

层与所述金属线路直接接触,可以采用抗电迁移能力优良的材料,所述第一隔离层覆盖在第二隔离层的表面,可以采用抗吸湿能力优良的材料,从而提高整体第一复合隔离层的抗电迁移的能力和抗吸湿的能力,进而更好地隔离水汽与所述金属线路接触,同时阻断金属线路离子迁移的路径;另外,当所述封装体受到外部应力时,第一复合隔离层的内部会发生分层和微裂纹,吸收外部应力,可有效降低外部应力对内部的钝化层以及线路层的损伤,降低所述封装体分层和内部线路出现裂纹的风险,提高封装体的综合性能稳定性,从而提高产品的良率和寿命。

12.在一些实施例中,所述第二隔离层的材料为二氧化硅或氮化硅。

13.氮化硅或二氧化硅不吸水,具有比较高的防水效果,能够有效防止水汽与金属线路接触,影响金属线路的电性能,同时也能防止水汽与钝化层接触,进而影响所述半导体衬底的性能。另外,氮化硅或二氧化硅的电阻率较高,能够有效阻断离子的迁移路径,提高封装体的良率和寿命。

14.在一些实施例中,所述封装体还包括绝缘层,所述绝缘层位于所述第一隔离层远离所述钝化层的一侧,所述绝缘层对应所述第一开孔开设有第二开孔,所述第一开孔与所述第二开孔连通。

15.绝缘层在第一隔离层的表面,可以提高对线路层以及内部钝化层的防护效果,同时提高线路层与后续封装基板之间的绝缘效果;另外,绝缘层与第一隔离层之间即便发生分层,水汽也不会进入金属线路和钝化层的表面,因此,通过结合第一隔离层和绝缘层,能够有利于提高封装体的综合性能稳定性,进而提高产品的良率和使用寿命。

16.在一些实施例中,所述封装体还包括形成于所述第一隔离层与所述第二隔离层之间的第三隔离层,所述第三隔离层包括设于所述金属线路表面的平坦部以及设于所述线路开口内的填充部。

17.所述第二隔离层、所述第三隔离层以及所述第一隔离层由内至外依次包覆所述金属线路和所述钝化层上,形成第二复合隔离层。其中,所述第二隔离层覆盖所述金属线路和所述钝化层,有效阻断离子迁移的路径,同时降低金属线路的侧壁的密集区域出现裂纹;所述第三隔离层覆盖所述第二隔离层,尤其是所述填充部平缓化了所述第一隔离层的附着面,减少了所述填充部与所述平坦部的交界处由于挤压产生的应力,有利于第一隔离层的完全覆盖,同时所述第三隔离层能够吸收外部应力,降低外部应力对内部线路的损伤;再沉积所述第一隔离层,形成完整的第二复合隔离层,降低了第二复合隔离层的内部缺陷,提高了第二复合隔离层的隔离效率,有效降低了水汽对内层金属线路以及钝化层的影响,阻断了离子迁移路径,进一步降低了外部应力对封装体内部线路的损伤,提高了封装体的良率和寿命。

18.在一些实施例中,所述平坦部设于所述金属线路围绕所述线路开口的区域的表面。

19.仅针对线路开口及线路开口的周围设置所述第三隔离层,能够起到前述实施例的效果的同时,还能有效降低成本,有利于提升所述第二复合隔离层的结构设计的灵活性。

20.在一些实施例中,所述第三隔离层的材料为二氧化硅。

21.由于二氧化硅相较于氮化硅结构疏松程度较大,易于吸收外部应力,同时,二氧化硅的抗电迁移能力较强,位于中间层,可以提高第二复合隔离层的整体隔离效果,同时二氧

化硅与氮化硅的相容性较好,也能提高第一隔离层与第三隔离层的界面结合力。

22.本技术实施例第二方面提供了一种封装体的制备方法,该制备方法包括:提供封装基体,所述封装基体包括半导体衬底、形成于所述半导体衬底表面的钝化层以及形成于所述钝化层表面且与所述半导体衬底电性连接线路层,所述线路层包括金属线路和线路开口,所述钝化层于所述线路开口露出;以及于所述金属线路的表面形成第一隔离层,所述第一隔离层延伸至所述线路开口内并覆盖露出于所述线路开口的所述钝化层,所述第一隔离层对应所述金属线路开设有第一开孔,所述金属线路于所述第一开孔露出,从而获得所述封装体。

23.在所述金属线路以及钝化层的表面通过形成所述第一隔离层的方式,可以有效隔绝水汽,防止所述金属线路受到水汽的影响而发生离子迁移,同时第一隔离层还能够起到隔断离子迁移路径的作用,从而提升所述封装体的性能稳定性,进而提高产品良率和寿命,工艺简单,易于成型,成本低、且便于工业化生产。

24.在一些实施例中,所述第一隔离层通过物理气相沉积法、化学气相沉积法、增强化学气相沉积法或原子层沉积法形成于所述金属线路和所述钝化层的表面。

25.采用上述沉积的方式,能够使第一隔离层完整地包覆金属线路和外露的钝化层,形成良好的隔离防护层,有效隔绝水汽,同时隔断离子迁移路径,提高封装体的性能稳定性;另外,采用上述乘积的方式形成的第一隔离层的厚度易于控制,厚度均匀,且含有隔离层成分直接与附着面发生反应,从而能有效提高第一隔离层与金属线路和钝化层之间的界面结合力,降低分层风险。

26.在一些实施例中,形成所述第一隔离层之前,所述制备方法还包括:于所述金属线路和所述钝化层的表面形成第二隔离层。

27.在金属线路和钝化层的表面首先沉积第二隔离层,其中可以采用与金属线路和钝化层相容性较好同时具有较强抗电迁移能力的材料,能提高第一复合隔离层在金属线路和钝化层表面的附着力,同时,增强抗电迁移的能力。

28.在一些实施例中,所述第二隔离层通过物理气相沉积法、化学气相沉积法、增强化学气相沉积法或原子层沉积法形成于所述第一隔离层的表面。

29.采用上述沉积的方式,能够使第二隔离层完整地包覆金属线路和外露的钝化层,形成良好的隔离防护层,有效隔绝水汽,同时隔断离子迁移路径,提高封装体的性能稳定性;另外,采用上述乘积的方式形成的第二隔离层的厚度易于控制,厚度均匀,且含有隔离层成分直接与附着面发生反应,从而能有效提高第二隔离层与金属线路和钝化层之间的界面结合力,降低分层风险。

30.在一些实施例中,形成所述第二隔离层之后,所述制备方法还包括:于所述第二隔离层的表面形成第三隔离层,所述第三隔离层包括设于所述金属线路表面的平坦部以及设于所述线路开口内的填充部。

31.增加第三隔离层,尤其是填充部将第一隔离层的附着面平缓化,减少了所述填充部与所述平坦部的交界处由于挤压产生的应力,有利于第一隔离层在沉积过程中厚度控制以及覆盖程度的控制。

32.在一些实施例中,所述平坦部设于所述金属线路围绕所述线路开口的区域的表面。

60.线路开口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

32

61.第一隔离层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

4a

62.第二隔离层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

4b

63.第三隔离层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

4c

64.平坦部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

4c1

65.填充部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

4c2

66.第一开孔

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ567.绝缘层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

6,32’68.第二开孔

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ769.金属垫

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ870.第一复合隔离层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20

71.第二复合隔离层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

30

72.封装基板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀa具体实施方式

73.下面结合本技术实施例中的附图对本技术实施例进行描述。

74.如图1所示,为一种封装体100’。所述封装体100’可设置于终端的壳体中。所述终端可为手机、笔记本电脑、平板电脑等电子装置。

75.请参阅图1,所述封装体100’包括半导体衬底1’、形成于半导体衬底1’上的钝化层2’以及形成于所述钝化层2’上的线路层3’,所述线路层3’能够实现半导体衬底1’与封装基板a之间的电性连接。其中,所述线路层3’包括金属线路31’和绝缘层32’,其中绝缘层32’主要起到绝缘和保护的作用,大多采用有机材料形成,例如聚酰亚胺(pi)或半固化片(pp)等。然而,半导体衬底1’表面的钝化层2’(大多为无机材料)、金属线路31’与绝缘层32’的材质不同,热膨胀系数不同,在热应力影响下,绝缘层32’容易与金属线路31’和钝化层2’分层;而且,有机材料类的绝缘层32’易吸湿,导致绝缘层32’与金属线路31’和钝化层2’之间的界面结合力降低,同时在分层界面形成水膜易于导致金属离子迁移,从而使封装产品失效;另外,上述线路层3’中的绝缘层32’为了起到更好的绝缘保护作用,厚度通常较厚,不利于降低封装产品的总厚度。随着消费电子产品高性能及小型化的发展趋势,急需一种性能稳定及轻薄短小的封装产品。

76.请参阅图2,为了解决封装体100’的上述问题,本实施例提供一种封装体100。所述封装体100包括封装基体10、形成于所述封装基体10表面的第一隔离层4a以及形成于所述第一隔离层4a表面的绝缘层6。所述封装基体10包括一半导体衬底1、形成于所述半导体衬底1表面的钝化层2以及形成于所述钝化层2表面且与所述半导体衬底1电性连接的线路层3。所述线路层3包括金属线路31和线路开口32,所述钝化层2于所述线路开口32露出。所述第一隔离层4a形成于所述金属线路31的表面且延伸至所述线路开口32内并覆盖露出于所述线路开口32的钝化层2。所述第一隔离层4a对应所述金属线路31开设有第一开孔5,所述金属线路31于所述第一开孔5露出。所述绝缘层6形成于所述第一隔离层4a远离所述钝化层2的表面,所述绝缘层6对应所述第一开孔5开设有第二开孔7,所述第一开孔5与所述第二开孔7连通。本技术在所述封装基体10的上表面设置所述第一隔离层4a,并在所述第一隔离层

4a的表面设置所述绝缘层6,再在通过所述第一开孔5和所述第二开孔7引出连接垫(图未示),实现封装基体10与后续封装基板(图未示)的电性连接,所述第一隔离层4a可以有效隔绝水汽,防止所述金属线路31受到水汽的影响而发生离子迁移现象,同时起到阻断离子迁移路径的作用,从而提升所述封装体100的性能稳定性,进而提高产品良率和寿命。由于第一隔离层4a具有较好的隔绝水汽的作用,因此,所述第一隔离层4a的厚度可以根据实际需要设计的相对较薄,能够有效降低所述封装体100的总厚度,有利于终端的轻薄短小化。

77.如图2所示,所述半导体衬底1包括相对设置的第一表面111和第二表面112,其中所述第一表面111为所述半导体衬底1的作用面,所述钝化层2设置于所述第一表面111。

78.所述封装基体10还包括形成于所述第一表面111的金属垫8,所述钝化层2覆盖所述第一表面111和所述金属垫8,即,所述金属垫8内嵌于所述钝化层2。所述金属垫8与所述线路层3通过过孔(图未示)电性连接。

79.所述钝化层2的材料可包括无机材料,例如氮化硅、二氧化硅等,还可以包括有机材料,例如聚酰亚胺(polyimid,pi)、苯并环丁烯(benzocyclobutene,bcb)等,还可以既包括无机材料也包括有机材料,例如在无机材料层的表面形成有机材料层。具体根据实际产品和工艺需要选用所述钝化层2的材料。在形成所述钝化层2时,需要所述钝化层2完整覆盖所述金属垫8以及所述半导体衬底1的第一表面111,钝化层2的厚度均匀,覆盖效果较佳,为了降低整体封装体100的总厚度,所述钝化层2的厚度不易过厚。

80.如图2所示,所述线路层3为采用rdl技术形成于所述钝化层2表面的重布线层,通过rdl技术可以将分布密度较高的所述金属垫8的间距放大,充分利用所述半导体衬底1的表面,有利于在有限的布线面积内实现多功能化。通过所述线路层3的重布线设计,将高密度垂直分布的多个金属垫8引出,以形成均匀布局在所述绝缘层6表面的连接垫,便于与封装基板的电性连接。

81.所述金属线路31的厚度可根据实际产品和工艺需要进行设计,所述金属线路31为铜线路。所述金属线路31对应所述第一开孔5的部位线宽较宽,有利于后续与封装基板之间良好的电性连接。

82.所述线路开口32的形状可以是圆形、三角形、矩形、椭圆形、多角形、或其他的不规则形状,通过设计所述线路开口32的形状,当所述第一隔离层4a嵌入所述线路开口32后,可以增加所述第一隔离层4a与所述金属线路31的侧壁的接触面积,同时也能增加第一隔离层4a与钝化层2的接触面积,进而提高所述第一隔离层4a与所述金属线路31和所述钝化层2之间的界面结合力,降低所述第一隔离层4a与所述金属线路31和所述钝化层2之间分层的风险,有效隔断位于所述线路开口32周围的金属线路31内离子迁移,提高所述封装体100的性能稳定性,进而提高产品良率和寿命。

83.如图2所示,所述第一隔离层4a均匀覆盖于所述金属线路31的表面以及外露于所述线路开口32处的钝化层2的表面。所述第一隔离层4a的材质为具有吸水率不高于1.1%,以及电阻率不低于10^13ω

·

cm的材料,采用吸水率不高于1.1%,电阻率不低于10^13ω

·

cm的材料形成的第一隔离层4a,能够提高第一隔离层4a的隔离水汽的效果,同时起到阻断离子迁移路径的目的。所述第一隔离层4a的材料可为二氧化硅或氮化硅,具体地,所述第一隔离层4a的材料可为氮化硅,氮化硅不吸水,具有比较高的防水效果,能够有效防止水汽与金属线路31接触,影响金属线路31的电性能,同时也能防止水汽与钝化层2接触,进而影响

所述半导体衬底1的性能。另外,氮化硅的电阻率较高,能够有效阻断离子的迁移路径,提高封装体100的良率和寿命。

84.所述第一隔离层4a通过物理气相沉积法(pvd)、化学气相沉积法(cvd)、增强化学气相沉积法(pe-cvd)或原子层沉积法(ald)形成于所述金属线路31和所述钝化层2的表面。通过上述沉积法能够在所述金属线路31和所述钝化层2的表面形成厚度均匀的薄膜,能够完整地包覆所述金属线路31和外露的所述钝化层2,形成良好的隔离防护层,有效隔绝水汽,同时隔断离子迁移路径,提高所述线路层3的电性能,进而提高所述封装体100的性能稳定性。

85.如图2所示,所述绝缘层6通过涂覆绝缘材料并固化的方式形成于所述第一隔离层4a的表面,涂覆方式操作简单,便于控制绝缘层6的厚度。所述绝缘层6可以完全填满所述线路开口32,以起到良好的绝缘隔离作用,同时能够保证绝缘层6的表面平整,有利于后续与封装基板的连接。形成所述绝缘层6可以提高对线路层3以及内部钝化层2的防护效果,同时提高线路层3与后续封装基板之间的绝缘效果,增加的绝缘层6与第一隔离层4a之间即便发生分层,水汽也不会进入金属线路31和钝化层2的表面,因此,通过结合第一隔离层4a和绝缘层6,能够有利于提高封装体100的综合性能稳定性,进而提高产品的良率和使用寿命。

86.所述绝缘层6的材质可以选自环氧树脂(epoxy resin)、半固化片(prepreg,pp)、bt树脂、聚苯醚(polyphenylene oxide,ppo)、聚酰亚胺(polyimide,pi)、聚对苯二甲酸乙二醇酯(polyethylene terephthalate,pet)以及聚萘二甲酸乙二醇酯(polyethylene naphthalate,pen)等树脂中的一种。具体地,本实施例中,所述绝缘层6为pi。

87.所述第二开孔7通过覆膜、曝光、显影以及蚀刻的方式形成于所述绝缘层6,第二开孔7通过干法蚀刻所述第二开孔7对应的第一隔离层4a形成。后续可以通过在第一开孔5和第二开孔7内电镀形成导体的方式引出连接垫,进而实现与封装基板的电性连接,其中电镀形成的导体与所述金属线路31的连接稳定,能够提高连接垫与所述金属线路31的电连接的稳定性,工艺简单,便于实现,且成本低廉;另外,通过电镀的方式可以根据实际需要设计电镀导体的位置和结构形式,局限性小。其他实施例中,还可以通过在所述第一开孔5和第二开孔7内填充导电膏并固化形成导体,通过填充导电膏并固化的方式形成导体,工艺简单,操作方便,且成本低。

88.其他实施方式中,所述钝化层2可以选用与所述第一隔离层4a相同或相近的材料,相同或相近的材料之间的相容性更好,能提高所述第一隔离层4a与所述钝化层2之间的界面结合力。具体地,所述钝化层2的材料可以是氮化硅或二氧化硅。

89.本实施例提供的所述封装体100中,通过在所述线路层3和所述钝化层2的表面形成所述第一隔离层4a,由于所述第一隔离层4a具有较低的吸水率和较高的电阻率,能够有效抑制水汽与所述线路层3接触,能够隔断所述线路层3离子迁移的通道,进而降低所述线路层3的离子迁移,提供所述封装体100的性能稳定性,进而提高产品良率和寿命;另外,通过rdl技术形成的所述线路层3厚度较薄,又由于第一隔离层4a的存在,可以将绝缘层6的涂覆厚度设计的较薄,从而有效降低整体封装体100的总厚度。

90.请参阅图3,结合参阅图2,为本技术另一实施例的封装体200,其与前述实施例中的封装体100的结构区别在于:本实施例中的封装体200中并未在所述第一隔离层4a的表面形成所述绝缘层6。

91.随着电子产品向着多功能化以及轻薄短小化的方向发展,在有限的所述半导体衬底1的空间布局面积内需要布局更高密度的线路,因此,线路层3的线路开口32的间距越来越小,此时绝缘层6已无法有效填充进所述线路开口32并且无法提供可靠的电气隔离作用,而单独采用所述第一隔离层4a便可以实现有效的防水汽,以及电隔离的作用,提供所述封装体200的性能稳定性,进而提高产品良率和寿命。而且,省略所述绝缘层6,单独采用所述第一隔离层4a,还可以有效降低整体封装体200的总厚度,有利于封装体200向着轻薄短小化发展。

92.请参阅图4,为本技术另一实施例的封装体300,其与前述实施例中的封装体100的结构区别在于:本实施例中的封装体300在第一隔离层4a与所述金属线路31以及露出于线路开口32的所述钝化层2之间增加了第二隔离层4b。所述第一隔离层4a与所述第二隔离层4b复合形成第一复合隔离层20,所述第二隔离层4b与所述金属线路31直接接触,可以采用抗电迁移能力优良的材料,所述第一隔离层4a覆盖在第二隔离层4b的表面,可以采用抗吸湿能力优良的材料,从而提高整体第一复合隔离层20的抗电迁移的能力和抗吸湿的能力,进而更好地隔离水汽与所述金属线路31接触,同时阻断金属线路31离子迁移的路径。

93.所述第二隔离层4b的材料为二氧化硅或氮化硅,具体地,所述第二隔离层4b的材料为二氧化硅,同时所述第一隔离层4a的材料为氮化硅,其中二氧化硅的抗电迁移能力优良,氮化硅的抗吸湿能力优良,二者复合形成第一复合隔离层20,可获得最佳的抗湿气和抗电迁移的性能。

94.所述第二隔离层4b可通过pvd、cvd、pe-cvd或ald形成于所述金属线路31和所述钝化层2的表面。

95.与前述实施例相比,所述封装体300通过在线路层3和钝化层2的表面形成第一复合隔离层20,从而提高整体第一复合隔离层20的抗电迁移的能力和抗吸湿的能力;另外,当所述封装体300受到外部应力时,第一复合隔离层20的内部会发生分层和微裂纹,吸收外部应力,可有效降低外部应力对内部的钝化层2以及线路层3的损伤,降低所述封装体300分层和内部线路出现裂纹的风险,提高封装体300的综合性能稳定性,从而提高产品的良率和寿命。

96.请参阅图5,为本技术另一实施例的封装体400,其与前述实施例中的封装体300的结构区别在于:本实施例中的封装体400中并未在所述第一隔离层4a的表面形成所述绝缘层6。

97.通过所述第二隔离层4b与所述第一隔离层4a形成第一复合隔离层20,能够赋予所述封装体400较佳地抗吸湿和抗电迁移的能力,同时第一复合隔离层20也能起到良好的绝缘和保护作用。另外,随着电子产品向着多功能化以及轻薄短小化的方向发展,在有限的所述半导体衬底1的空间布局面积内需要布局更高密度的线路,因此,线路层3的线路开口32的间距越来越小,此时绝缘层6已无法有效填充进所述线路开口32并且无法提供可靠的电气隔离作用,因此,本实施例中在第一复合隔离层20的表面不设置绝缘层6,也能够实现相应的绝缘和保护效果。而且,省略所述绝缘层6,单独采用第一复合隔离层20,还可以有效降低整体封装体400的总厚度,有利于封装体400向着轻薄短小化发展。

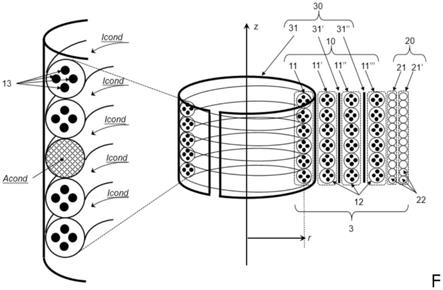

98.请参阅图6,为本技术另一实施例的封装体500,其与前述实施例中的封装体400的结构区别在于:本实施例中的封装体500在所述第一隔离层4a与第二隔离层4b之间增加了

第三隔离层4c,所述第三隔离层4c包括对应所述金属线路31设置的平坦部4c1以及对应所述线路开口32设置的填充部4c2。所述第二隔离层4b、所述第三隔离层4c以及所述第一隔离层4a由内至外依次包覆所述金属线路32和所述钝化层2上,形成一第二复合隔离层30。

99.所述填充部4c2连接所述第一隔离层4a的侧壁可以是斜面、弧面或其他形状的曲面,所述填充部4c2可以部分填充所述线路开口32,也可以填满所述线路开口32。所述线路开口32的顶部开口边缘和靠近所述钝化层2的底部的死角均可能存在应力集中现象,在形成所述第一隔离层4a后,由于应力集中会使所述第一隔离层4a易于分层脱落,另外,也可能存在第一隔离层4a覆盖不完全的现象,从而影响隔离效果。通过增加第三隔离层4c,尤其是在所述线路开口32处设置填充部4c2,能够有效将所述第一隔离层4a在所述线路开口32内的附着面平缓化,有利于所述第一隔离层4a的完全覆盖,降低在所述线路开口32底部死角位置出现覆盖不全的现象,以及应力集中造成的第一隔离层4a易于分层脱落等问题。

100.所述第三隔离层4c的材料可以是二氧化硅,由于二氧化硅相较于氮化硅结构疏松程度较大,易于吸收外部应力,同时,二氧化硅的抗电迁移能力较强,位于中间层,可以提高第二复合隔离层30的整体隔离效果,同时二氧化硅与氮化硅的相容性较好,也能提高第一隔离层4a与第三隔离层4c的界面结合力。

101.与前述实施例相比,所述第二隔离层4b覆盖所述金属线路31和所述钝化层2,有效阻断离子迁移的路径,同时降低金属线路31的侧壁的密集区域出现裂纹;所述第三隔离层4c覆盖所述第二隔离层4b,尤其是所述填充部4c2平缓化了所述第一隔离层4a的附着面,减少了所述填充部4c2与所述平坦部4c1的交界处由于挤压产生的应力,有利于第一隔离层4a的完全覆盖,同时所述第三隔离层4c能够吸收外部应力,降低外部应力对内部线路的损伤;再沉积所述第一隔离层4a,形成完整的第二复合隔离层30,降低了第二复合隔离层30的内部缺陷,提高了第二复合隔离层30的隔离效率,有效降低了水汽对内层金属线路31以及钝化层2的影响,阻断了离子迁移路径,进一步降低了外部应力对封装体500内部线路的损伤,提高了封装体500的良率和寿命。

102.请参阅图7,为本技术另一实施例的封装体600,其与前述实施例中的封装体500的结构区别在于:本实施例中的封装体600所述第三隔离层4c包括平坦部4c1和填充部4c2,其中所述平坦部4c1设于所述金属线路31围绕所述线路开口32的区域的表面,所述填充部4c2设于所述线路开口32内。

103.仅针对线路开口32内和线路开口32的边缘设置所述第三隔离层4c,能够起到前述实施例的效果的同时,还能有效降低成本,有利于提升所述第二复合隔离层30的结构设计的灵活性。

104.本技术一实施例还提供上述封装体100的制备方法,其包括如下步骤。

105.s11:如图8所示,提供一封装基体10,所述封装基体10包括半导体衬底1、形成于所述半导体衬底1表面的钝化层2以及形成于所述钝化层2表面且与所述半导体衬底1电性连接线路层3,所述线路层3包括金属线路31和线路开口32,所述钝化层2于所述线路开口32露出。

106.所述半导体衬底1的第一表面111形成有金属垫8,所述钝化层2覆盖所述金属垫8和所述第一表面111。所述线路层3采用rdl技术形成与所述钝化层2的表面,在形成所述线路层3之前,可以通过打磨的方式将部分所述钝化层2打磨掉,进而使所述金属垫8由所述钝

化层2的表面露出,再在露出的所述金属垫8的表面形成镀层,以便所述线路层3与所述半导体衬底1的电性连接。打磨后的钝化层2的表面更平整,有利于提高所述线路层3与所述钝化层2之间的结合力。可以理解的是,还可以通过在所述钝化层2对应所述金属垫8的位置打孔再电镀或填充导电膏等实现与所述线路层3的电性连接。

107.s12:如图9所示,于所述金属线路31的表面形成第一隔离层4a,所述第一隔离层4a延伸至所述线路开口32内并覆盖所述钝化层2。

108.所述第一隔离层4a通过物理气相沉积法(pvd)、化学气相沉积法(cvd)、增强化学气相沉积法(pe-cvd)或原子层沉积法(ald)等形成于所述金属线路31和所述钝化层2的表面。以pe-cvd镀氮化硅/氧化硅为例,借助微波或射频等方式使含有镀层成分原子的气体发生电离,在所述金属线路31和所述钝化层2的表面形成等离子体,等离子体化学活性很强,很容易发生反应,因此能够在所述金属线路31和所述钝化层2的表面上沉积出一层厚度均匀的薄膜。通常在衬底温度350℃左右就可以沉积出厚度均匀,性能良好的氮化硅/氧化硅薄膜。通过上述物理或化学沉积的方式,能够使所述第一隔离层4a完整地包覆所述金属线路31和外露的所述钝化层2,形成良好的隔离防护层,有效隔绝水汽,同时隔断离子迁移路径,提高所述线路层3的电性能,进而提高所述封装体100的性能稳定性。

109.沉积的所述第一隔离层4a的厚度可以根据实际产品需求和工艺条件调整,具体地,所述第一隔离层4a的厚度可以在20埃-50000埃之间,优选1000埃-10000埃,进一步优选2000埃-8000埃,更进一步优选2500埃-5000埃,在这一厚度范围内,所述第一隔离层4a能够起到较佳的隔离防护效果,同时不会影响封装体100的总厚度。

110.s13,结合参阅图2所示,于所述第一隔离层4a远离所述钝化层2的一侧形成绝缘层6。

111.所述绝缘层6通过涂覆绝缘材料并固化的方式形成于所述第一隔离层4a的表面,涂覆方式操作简单,便于控制绝缘层6的厚度,能够保证绝缘层6完全覆盖所述第一隔离层4a。所述绝缘层6可以完全填满所述线路开口32,以起到良好的绝缘隔离作用,同时能够保证绝缘层6的表面平整,有利于后续与封装基板的连接。

112.所述绝缘层6的材质可以选自环氧树脂(epoxy resin)、半固化片(prepreg,pp)、bt树脂、聚苯醚(polyphenylene oxide,ppo)、聚酰亚胺(polyimide,pi)、聚对苯二甲酸乙二醇酯(polyethylene terephthalate,pet)以及聚萘二甲酸乙二醇酯(polyethylene naphthalate,pen)等树脂中的一种。具体地,本实施例中,所述绝缘层6为pi。

113.由于存在所述第一隔离层4a,能够有效起到隔离防水,以及阻断金属线路31的离子迁移路径,因此,所述绝缘层6的厚度可以适当减薄,有利于整体封装体100的轻薄短小化。

114.另外,还可以通过打磨的方式将所述绝缘层6的表面进行平整化,适当减薄所述绝缘层6的厚度,同时进一步提高所述绝缘层6的表面平整度,有利于后续与封装基板的连接。

115.s14,结合参阅图2所示,于所述绝缘层6上开设第二开孔7,并于所述第一隔离层4a对应所述第二开孔7处开设所述第一开孔5,所述第一开孔5与所述第二开孔7连通,从而获得所述封装体100。

116.所述第二开孔7通过覆膜、曝光、显影以及蚀刻的方式形成于所述绝缘层6,第二开孔7通过干法蚀刻所述第二开孔7对应的第一隔离层4a形成,第一开孔5和第二开孔7能够的

成孔方式简单,易于实现,操作方便,且成本低。

117.后续可以通过在第一开孔5和第二开孔7内电镀形成导体的方式引出连接垫,进而实现与封装基板的电性连接,其中电镀形成的导体与所述金属线路31的连接稳定,能够提高连接垫与所述金属线路31的电连接的稳定性,工艺简单,便于实现,且成本低廉;另外,通过电镀的方式可以根据实际需要设计电镀导体的位置和结构形式,局限性小。其他实施例中,还可以通过在所述第一开孔5和第二开孔7内填充导电膏并固化形成导体,通过填充导电膏并固化的方式形成导体,工艺简单,操作方便,成本低、且便于工业化生产。

118.请结合参阅图3与图2,本技术另一实施例还提供了一种封装体200的制备方法,本实施例的所述封装体200的制备方法与前述实施例中封装体100的制备方法的区别在于:无需在所述第一隔离层4a的表面设置所述绝缘层6,因此,在形成所述第一隔离层4a后便可直接在所述第一隔离层4a上通过干法蚀刻的方式形成所述第一开孔5,便得到所述封装体200。

119.由于省略了所述绝缘层6,为了起到更好的隔离防护作用,所述第一隔离层4a的厚度可以适当加厚。

120.请结合参阅图4与图2,本技术又一实施例还提供了一种封装体300的制备方法,本实施例的所述封装体300的制备方法与前述实施例中封装体100的制备方法的区别在于以下步骤:

121.步骤s31,结合参阅图8所示,提供一封装基体10,所述封装基体10的具体结构参上。

122.步骤s32,如图10所示,于所述金属线路31与外露的所述钝化层2的表面形成第二隔离层4b。

123.所述第二隔离层4b通过pvd、cvd、pe-cvd或ald形成于所述金属线路31和所述钝化层2的表面。

124.所述第二隔离层4b的材料为二氧化硅或氮化硅,具体地,所述第二隔离层4b的材料为二氧化硅。

125.步骤s33,结合参阅图4所示,于所述第二隔离层4b的表面形成第一隔离层4a。所述第二隔离层4b与所述第一隔离层4a构成一第一复合隔离层20。

126.所述第一隔离层4a的形成方法参上。

127.后续绝缘层6、第一开孔5和第二开孔7的成型方法参上。其中第一开孔5在成孔过程中需要将第一隔离层4a和第二隔离层4b连通,由于第一隔离层4a与第二隔离层4b的材料相似,因此采用同一的成孔方式便可一次成型出所述第一开孔5。

128.请结合参阅图5与图4,本技术另一实施例还提供了一种封装体400的制备方法,本实施例的所述封装体400的制备方法与前述实施例中封装体300的制备方法的区别在于:无需在所述第一隔离层4a的表面设置所述绝缘层6,因此,在形成所述第一隔离层4a后便可直接在所述第一隔离层4a和第二隔离层4b上通过干法蚀刻的方式形成所述第一开孔5,便得到所述封装体400。

129.由于第二隔离层4b与第一隔离层4a构成第一复合隔离层20,省略了所述绝缘层6,也起到良好的隔离防护作用,同时有利于降低封装体400的总厚度。

130.请结合参阅图6与图5,本技术又一实施例还提供了一种封装体500的制备方法,本

实施例的所述封装体500的制备方法与前述实施例中封装体400的制备方法的区别在于以下步骤:

131.步骤s51,结合参阅图8所示,提供一封装基体10,所述封装基体10的具体结构参上。

132.步骤s52,结合参阅图10所示,于所述金属线路31与外露的所述钝化层2的表面形成第二隔离层4b。所述第二隔离层4b的成型方法参上。

133.步骤s53,如图11所示,于所述第二隔离层4b的表面形成第三隔离层4c,所述第三隔离层4c包括对应所述金属线路31设置的平坦部4c1以及对应所述线路开口32设置的填充部4c2。

134.所述第三隔离层4c通过pvd、cvd、pe-cvd或ald形成于所述第二隔离层4b的表面。

135.增加第三隔离层4c,尤其是填充部将后续第一隔离层4a的附着面平缓化,减少了所述填充部4c2与所述平坦部4c1的交界处由于挤压产生的应力,有利于第一隔离层4a在沉积过程中厚度控制以及覆盖程度的控制。

136.步骤s54,结合参阅图6所示,于所述第三隔离层4c的表面形成第一隔离层4a。所述第二隔离层4b、所述第三隔离层4c以及所述第一隔离层4a由内至外依次包覆所述金属线路31和所述钝化层2上,形成一第二复合隔离层30。所述第一隔离层4a的成型方法参上。

137.请结合参阅图7与图6,本技术又一实施例还提供了一种封装体600的制备方法,本实施例的所述封装体600的制备方法与前述实施例中封装体500的制备方法的区别在于:所述第三隔离层4c仅设置在所述线路开口32内和线路开口32的周围,局部设置所述第三隔离层4c,能够起到前述实施例中第二复合隔离层30的效果的同时,还能有效降低成本,有利于提升所述第二复合隔离层30的结构设计的灵活性。

138.需要说明的是,以上仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内;在不冲突的情况下,本技术的实施方式及实施方式中的特征可以相互组合。因此,本技术的保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。