1.本发明的名称是“支持条件分支的直接存储器访问通道链的芯片电路设计”,介绍了对系统级芯片(soc)设计中的直接存储器访问(dma)的一种特殊设计方式,是一种可以快速实现数据搬移并能够通过外部条件的状态判断来形成结构可变的dma通道链的效果,使得dma用来搬移数据的各通道之间的衔接顺序可以根据触发条件的变化来产生先后次序的调整。

2.本发明的目的是让整个dma通道链的功能在实现传统的数据搬移功能的基础上,还可以根据硬件的条件判断更加快速灵活地调整数据搬移操作的顺序以达到代替软件实现条件跳转指令执行的效果,从而提高了芯片并行工作的效率。另外在soc芯片的低功耗应用领域中,即使cpu停止了工作,也可以靠唤醒dma独立工作来承担本属于软件唤醒中断服务的工作,而这期间cpu则可以继续保持处于休眠状态。这样做的效果可以提高系统响应速度,并进一步降低系统功耗。

背景技术:

3.传统应用中dma是用来搬移数据块的,并且一般soc芯片中可能一个dma控制器可以支持多个dma通道(dma channel),每个dma通道都是可以独立激活来将指定的源地址中的数据块搬移到目标地址区域去,并且这些dma通道可以通过触发条件的设置来组合出dma通道链(dma channel chain)。比如一个dma通道完成数据块的搬移之后,可以产生一个触发信号给下一个dma通道来继续搬移下一个指定的数据块。但是目前的设计基本都是不够灵活的,比如软件配置好dma的通道级联顺序之后,就会按照固定的顺序在前级通道工作完成后依次触发后级通道来完成后续数据的搬移。整个链路属于一种单线衔接的结构。

4.本发明根据额外的条件信息来实现组合触发,使得dma通道的组合连接顺序可以根据不同的条件做出改变。这样做的目的是可以改变数据搬移的顺序,使得单线形式的dma通道链可以根据条件约束的定义变成了一种树状分叉结构的链路。比如dma的一个通道首先被设置为对某个寄存器做写入操作,但是下一步的寄存器写入操作需要根据外界不同的条件来决定写入不同的内容,甚至是根据外部不同的条件要写不同的寄存器。这样的应用需求在传统的dma通道链设计中就无法实现,而软件程序中却存在很多这样的需求。因此,传统的dma很难代替软件的操作效果,仅作为搬移数据来使用。本发明的作用就是使得dma有了指令执行的效果,可以代替软件实现灵活的控制。

5.具体的实现方法是在前级dma通道工作完成后,通常都会输出一个表示完成的标志信号,这个信号可以和外界的其他条件作为组合来作为下一个dma通道的触发信号。比如,有一段软件程序需要对寄存器a做写操作,然后再读入外部某个引脚p的状态来决定对寄存器b或者寄存器c写操作,如果外界引脚为高电平,就对b寄存器写操作,反之就对c寄存器写操作。本发明的带条件分支的dma通道链就可以代替实现这样的软件操作行为,首先配置dma通道一来执行对寄存器a的数据搬移写入,配置dma通道二来执行对寄存器b的数据搬移写入,配置dma通道三来执行对寄存器c的数据搬移写入。然后配置dma通道二的触发条件

为dma通道一工作完成并且同时外界需要判断的那个引脚p为高电平,两个条件同时满足的情况下dma通道二就会被触发开始执行搬移数据来操作寄存器b; 配置dma通道三的触发条件为dma通道一工作完成并且同时外界需要判断的那个引脚p为低电平,两个条件同时满足的情况下dma通道三就会被触发开始执行搬移数据来操作寄存器c。这样的dma控制效果就可以等效了前述的整个软件操作行为,实现了条件跳转的效果。通过类似的更多通道就可以组合出更加复杂的dma通道链来等价实现更复杂的软件方案。

6.本发明具有很好的实用性,使得dma的应用领域得到了拓展,提高了soc系统的并行处理能力。另外,在低功耗应用场合中,cpu经常会处于睡眠状态,在某些特定条件满足的情况下cpu会被唤醒并产生中断,软件会跳转到对应的中断入口执行中断服务程序。这个过程中,存储程序的可能是flash这样的非易失记忆体,这种存储器在低功耗模式唤醒过程中需要一定的启动时间,并且系统也需要做进出中断所需的诸如压栈出栈等配套保护操作,这些都增加了唤醒工作的响应时间;另外软件从flash取指的过程以及做条件判断的执行行为都需要额外的时间开销。本发明使得dma通道链可以等价实现软件的中断服务并且节省了上述各类时间开销。而且,在低功耗模式唤醒的过程中,soc系统还需要切换内部电源管理模块(pmu)的工作状态,来提供驱动能力更强的电源以保证soc从低功耗模式恢复到正常的全速运行模式,这个过程也需要花费一定的时间并增加更多的功耗,本发明可以使得dma具备直接处理外部唤醒事件的能力,同时cpu可以继续维持在睡眠状态,在更低的功耗模式下更快地完成等效的工作。

7.针对目前国内外的soc芯片产品现状,以具有代表性的mcu产品为例,目前并不支持本发明所述的支持条件分支的dma通道链功能。本发明基于作者自身平时的学习研究积累总结,并根据当前的soc芯片发展需求以及所存在的局限性从理论上做了充分的思考论证,具备创造性,实用性和新颖性。

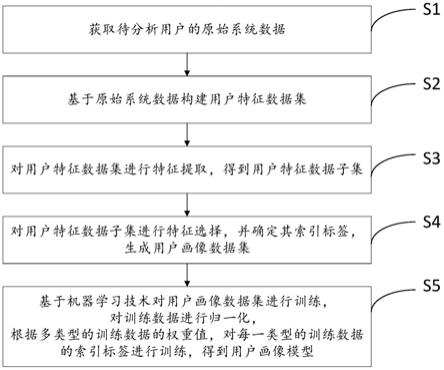

技术实现要素:

8.本发明在通常的dma通道链结构下增加了硬件条件判断功能,使得系统在前级dma通道完成任务后可以根据当前的特定条件来选择触发下一个dma通道,从而扩展了dma通道链的应用领域,使得某些通常必须由软件来实现的操作可以用支持条件分支的dma通道链来代替实现。

9.本发明所述的判断条件可以由前级dma通道传输完成的状态、某个或某一些外部引脚的电平状态或者边沿变化的发生、定时器或者计数器的状态达到设定的目标值或者处于特定的阈值范围、某个特定地址中的某些比特位内容达到了期望的某个状态或者处于特定的阈值范围、某个电路模块的某些信号满足了一定的逻辑状态等一系列条件所产生的逻辑组合定义。每个通道的触发条件均可以通过软件编程配置的方式提前设定好条件组合,以实现带条件分支的树叉状dma通道链。

10.本发明可以在传统dma通道链电路上做适当修改增加可编程的触发条件组合即可实现,在设计上非常简单方便,但是带来的应用方式却是完全崭新的。可以想象低功耗设备的待机时间会更长,系统工作的响应速度和处理速度都会更快,soc系统软硬件的设计方案也会越来越灵活多样。

技术特征:

1.支持条件分支的直接存储器访问通道链(dma channel chain)的芯片电路设计,可以通过硬件自动判断当前条件来决定各dma通道之间的工作衔接顺序。2.根据权利要求1所述的电路,相关dma通道的触发条件均可以通过软件独立配置。3.根据权利要求1和2所述的电路,各dma通道的触发条件可以由前级dma通道传输完成的状态、某个或某一些外部引脚的电平状态或者边沿变化的发生、定时器或者计数器的状态达到设定的目标值或者处于特定的阈值范围、某个特定地址中的某些比特位内容达到了期望的某个状态或者处于特定的阈值范围,某个电路模块的某些信号满足了一定的逻辑状态等一系列条件所产生的逻辑组合定义。

技术总结

本发明的名称是“支持条件分支的直接存储器访问通道链的芯片电路设计”,介绍了对系统级芯片(SOC)设计中DMA通道之间的新型链接方式。本发明在通常的直接存储器访问通道链(DMA Channel Chain)结构下增加了硬件条件判断功能,使得系统在前级DMA通道完成任务后可以根据当前的特定条件来选择触发下一个DMA通道,从而扩展了DMA通道链的应用领域,使得某些通常必须由软件来实现的操作可以用支持条件分支的DMA通道链来代替实现。从而达到降低系统功耗,并提高系统响应速度和执行速度的效果。本发明所述的硬件判断条件可以通过软件配置的方式对DMA的各个通道分别做出组合定义。的方式对DMA的各个通道分别做出组合定义。

技术研发人员:ꢀ(51)Int.Cl.G06F30/32

受保护的技术使用者:孙骏

技术研发日:2020.08.30

技术公布日:2022/2/28

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。