3d nand闪速存储器件及其集成方法

1.本技术是针对申请日为2020年05月20日,申请号为202080001324.0,发明名称为3d nand闪速存储器件及其集成方法的专利的分案申请。

技术领域

2.本技术实施例涉及3d nand闪速存储器件及其集成方法,涉及但不限于一种能够改善存储空间和读/写性能的3d nand闪速存储器件及其集成方法。

背景技术:

3.为了提供固态盘(ssd)的更好性能,在常规ssd实现方式中广泛利用了单级单元(slc)nand闪速存储器和3d三级单元(tlc)nand闪速存储器的组合结构。常常被读/写的热数据存储在slc nand闪存中,不常被读/写的冷数据存储在3d tlc nand闪存中。然而,以上组合结构利用的3d tlc nand闪速存储器降低了存储密度并且提高了ssd的成本。另外,组合结构的slc nand的读/写性能不令人满意。因此,对现有技术做出改进是必要的。

技术实现要素:

4.本公开实施例提供了一种3d nand闪速存储器件及其制造方法,以改善存储空间和读/写性能。本技术实施例提供一种3d nand闪速存储器件及其制造方法。

5.本公开的实施例公开了一种用于3d nand闪速存储器件的集成方法,包括:在cmos管芯上设置多个3d三级单元(tlc)nand闪速存储器;在所述3d nand闪速存储器件的所述cmos管芯上设置至少一个nor闪速存储器;以及将所述至少一个nor闪速存储器连接到所述3d nand闪速存储器件的开放nand闪存接口(onfi);其中所述至少一个nor闪速存储器设置于所述cmos管芯的未使用区域上。

6.本公开的另一实施例公开了一种集成于cmos管芯上的3d nand闪速存储器件,包括:设置于cmos管芯上的多个3d三级单元(tlc)nand闪速存储器;以及设置于所述cmos管芯上的至少一个nor闪速存储器,所述至少一个nor闪速存储器连接到所述3d nand闪速存储器的开放nand闪存接口(onfi);其中,所述至少一个nor闪速存储器设置于所述cmos管芯的未使用区域上。

7.在阅读各附图所示的优选实施例的以下详细描述之后,本领域的普通技术人员将毫无疑问得地明了本公开实施例的这些和其它目的。

附图说明

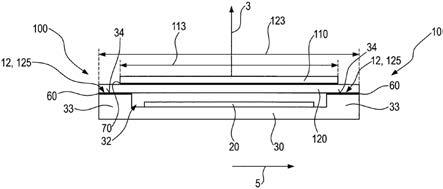

8.在附图(其不一定是按比例绘制的)中,相似的附图标记可在不同的视图中描述相似的部件。具有不同字母后缀的相似附图标记可表示相似部件的不同示例。附图以示例而非限制的方式大体示出了本文中所讨论的各个实施例。

9.图1是根据本公开实施例的用于3d nand闪速存储器件的集成工艺的示意图;

10.图2-图3是根据本公开实施例的应用所述集成工艺的3d nand闪速存储器件的示

意图。

具体实施方式

11.图1是根据本公开实施例的用于3d nand闪速存储器件的集成工艺10的示意图。用于3d nand闪速存储器件的集成工艺10包括以下步骤:

12.步骤102:开始。

13.步骤104:在cmos管芯上设置多个3d三级单元(tlc)nand闪速存储器。

14.步骤106:在所述3d nand闪速存储器件的所述cmos管芯上设置至少一nor闪速存储器。

15.步骤108:将所述至少一nor闪速存储器连接到所述3d nand闪速存储器件的开放nand闪存接口(onfi)。

16.步骤110:在所述3d nand闪速存储器件的所述至少一nor闪速存储器与所述onfi之间连接数据通路逻辑单元。

17.步骤112:结束。

18.为了解释集成工艺10,请还参考图2和图3,图2和图3是根据本公开实施例的应用集成工艺10的3d nand闪速存储器件20的示意图。如图2中所示,3d nand闪速存储器件20包括嵌入有多个3d tlc nand闪速存储器204的cmos管芯202。

19.根据集成工艺10,在步骤104中,将3d tlc nand闪速存储器204设置于cmos管芯202上,每个3d tlc nand闪速存储器204彼此不重叠,从而在cmos管芯202上形成在每个3d tlc nand闪速存储器204之间的间隙。

20.在步骤106中,在3d nand闪速存储器件20的cmos管芯202上设置至少一nor闪速存储器,其中,所述至少一nor闪速存储器设置于cmos管芯202的未使用区域上,cmos管芯202的未使用区域可以是在3d tlc nand闪速存储器204中的每一者之间的间隙、cmos管芯202的冗余或空白区域。同样地,如图3所示,在cmos管芯202的未使用区域中设置多个nor闪速存储器206,使得随着nor闪速存储器206的设置,3d nand闪速存储器件20的存储空间增大,并且改善3d nand闪速存储器件20的灵活性。要指出的是,nor闪速存储器206的量不限于图2和图3中所示的四个,根据其它要求可以在cmos管芯202的未使用区域中设置其它量的一定部署密度的nor闪速存储器。

21.在步骤108中,将nor闪速存储器206连接到3d nand闪速存储器件20的onfi,其中,onfi是用于对3d nand闪速存储器件20的管脚分配和命令进行标准化的接口,所述onfi连接3d tlc nand闪速存储器204。在步骤110中,连接在nor闪速存储器206于onfi之间的数据通路逻辑单元。在步骤108中将nor闪速存储器206的数据通路逻辑单元连接到onfi之后,可以指示nor闪速存储器206根据onfi的管脚分配和命令来读/写数据。亦即,nor闪速存储器206可以与3d tlc nand闪速存储器204共享onfi,以经由onfi读/写数据,或者直接经由onfi读/写数据。

22.由于nor闪速存储器206支持随机读和随机写,所以在写入多条小数据时,改善了3d nand闪速存储器件20的读取时间的性能和写入时间的性能。另外,将3d nand闪速存储器件20的控制器用于执行针对存储在3d tlc nand闪速存储器204中的数据的错误控制编码过程。然而,nor闪速存储器206处理的数据没有错误控制编码,这样降低了3d nand闪速

存储器件20的控制器的复杂性并且改善3d nand闪速存储器件20的性能。

23.本公开实施例设置有nor闪速存储器206的3d nand闪速存储器件20可以应用于常规固态磁盘(ssd)产品中以改善读/写性能。另外,通过在cmos管芯202的未使用区域中设置nor闪速存储器206,维持了3d nand闪速存储器件20的制造成本。

24.如图3中所示,应用集成方法10集成在本公开实施例的cmos管芯202上的3d nand闪速存储器件20包括3d tlc nand闪速存储器204和nor闪速存储器206。3d tlc nand闪速存储器204设置于cmos管芯202上,并且nor闪速存储器206设置于cmos管芯的未使用区域上。另外,由于nor闪速存储器206的数据通路逻辑单元连接到onfi,onfi对3d nand闪速存储器件20的管脚分配和命令进行标准化,3d nand闪速存储器件20的复杂性降低,并且读/写性能得到提高,而不会增大3d nand闪速存储器件20的制造成本。

25.要指出的是,上述实施例例示了本公开的概念,本领域的技术人员可以相应地作出适当修改并且不限于此。

26.概括地说,本公开提供了一种3d nand闪速存储器件及其集成方法,改善了存储空间、读/写性能而不提高制造成本。

27.本领域的技术人员将容易发现,可以对所述装置和方法做出多种修改和更改同时保持本公开的教导。因此,应当将以上公开解释为仅受所附权利要求的范围限制。

28.应理解,说明书通篇中提到的“一个实施例”或“一实施例”意味着与实施例有关的特定特征、结构或特性包括在本技术的至少一个实施例中。因此,在整个说明书各处出现的“在一个实施例中”或“在一实施例中”未必一定指相同的实施例。此外,这些特定的特征、结构或特性可以任意适合的方式结合在一个或多个实施例中。应理解,在本技术的各种实施例中,上述各过程的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本技术实施例的实施过程构成任何限定。上述本技术实施例序号仅仅为了描述,不代表实施例的优劣。

29.需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

30.以上所述,仅为本技术的实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。