1.本发明涉及信道解码技术领域,特别是涉及一种支持码字同步的伴随式计算方法及计算电路。

背景技术:

2.现有rs码字在进行解码的过程中,首先需要对其进行伴随式的计算,如:一个(528,514)的rs码字,其包括了528个10bit的码元,其中528表示该rs码字长度,514表示该rs码字中的信息长度,设第j个码元为r

j-1

,则该rs码字可表示为[r0,r1,r2,

…

,r

526

,r

527

],该rs码字共有14个伴随式,其中第i个伴随式si的计算为:

[0003][0004]rj-1

为rs码字的第j个码元,其中0≤j≤527;ai为有限域中的第i个元素,其中0≤i≤13;n为rs码字长度;

[0005]

则(528,514)的rs码字的伴随式的为:

[0006]

s0=r0 r1·

(a0)1 r2·

(a0)2 r3·

(a0)3 ... r

527

·

(a0)

527

[0007]

s1=r0 r1·

(a1)1 r2·

(a1)2 r3·

(a1)3 ... r

527

·

(a1)

527

[0008]

…

[0009]s13

=r0 r1·

(a

13

)1 r2·

(a

13

)2 r3·

(a

13

)3 ... r

527

·

(a

13

)

527

[0010]

如图1所示为现有技术中160bit位宽(528,514)rs码字的伴随式计算的硬件实现框架示意图,计算一个rs码字的伴随式需要接收到完整的码字后才可以得到,通过判断伴随式以进行码字同步,在寻找rs码字起始的准确位置时,计算速度慢,耗时长,效率低。

技术实现要素:

[0011]

基于此,本发明提供了一种支持码字同步的伴随式计算方法,解决了使用伴随式计算模块支持码字同步时,计算速度慢,耗时长,效率低,迭代提升同步速度的问题。本发明还提供了一种支持码字同步的伴随式计算电路,也可解决上述问题。

[0012]

本发明实施例提供了一种支持码字同步的伴随式计算方法,所述方法包括:

[0013]

接收(n,k)rs码字,并存储到数据寄存器;

[0014]

每个(n,k)rs码字划分为n个数据块,每个数据块的数据位宽为其中,n为rs码字长度,k为rs码字中的信息长度,m为码元速率;

[0015]

以上一个(n,k)rs码字的第1个数据块的0bit为起始位置,以上一个(n,k)rs码字的第n个数据块的为终止位置,获取第一组伴随式;

[0016]

由所述数据块与所述第一组伴随式迭代处理,获取两个(n,k)rs码字对应的n组伴

随式。

[0017]

进一步地,所述获取第一组伴随式,具体包括:

[0018]

将(n,k)rs码字的当前数据块中的码元,分别与当前数据块中码元对应的有限域中的元素相乘,获取相乘结果;

[0019]

将当前数据块中的所述相乘结果相加,得到当前数据块的相加结果;

[0020]

当前数据块的相加结果,累计上一个数据块中间结果升次后得到的结果作为当前数据块的中间结果;其中第1个数据块相加结果中累加零;

[0021]

依次重复,得到n个数据块的相加结果与中间结果;

[0022]

则第一个(n,k)rs码字的第n个中间结果为所述的第一组伴随式。

[0023]

进一步地,所述上一个数据块中间结果升次,具体为:

[0024]

对所述上一个数据块的中间结果乘有限域元素的次方,其中,第n-1个数据块的中间结果乘有限域元素的次方。

[0025]

进一步地,所述迭代处理包括:

[0026]

以上一个(n,k)rs码字的第n个数据块的0bit为起始位置,以下一个(n,k)rs码字的第n-1个数据块的为终止位置;

[0027]

上一个(n,k)rs码字的第n-1个数据块的相加结果升次,然后累加下一个(n,k)rs码字的第n-1个数据块的相加结果降次,再累加第n-1个伴随式的升次结果,累加的最终结果为第n组伴随式。

[0028]

进一步地,所述上一个(n,k)rs码字的第n-1个数据块的相加结果升次,包括:上一个(n,k)rs码字的第n-1个数据块的相加结果乘有限域元素的n-1次方。

[0029]

进一步地,所述下一个(n,k)rs码字的第n-1个数据块的相加结果降次,包括:下一个(n,k)rs码字的第n-1个数据块的相加结果乘有限域元素的-1次方。

[0030]

进一步地,所述第n-1个伴随式的升次,包括:

[0031]

第n-1个伴随式乘有限域元素的次方。

[0032]

本发明实施例还提供了一种支持码字同步的伴随式计算电路,所述计算电路包括:

[0033]

输入节点,输入输入信号;

[0034]

输出节点,输出输出信号;

[0035]

第一乘法器,所述第一乘法器的输入端口连接于所述输入节点;

[0036]

第一加法器,所述第一加法器的输入端口连接于所述第一乘法器的输出端口;

[0037]

第一寄存器,所述第一寄存器的输入端口连接于所述第一加法器的其中一个输出端口;以及

[0038]

第二寄存器,所述第二寄存器的输入端口连接于所述第一加法器的另一个输出端口;

[0039]

第二乘法器,所述第二乘法器的输入端口连接于所述第一寄存器的输出端口;

[0040]

第二加法器,所述第二加法器的其中一个输入端口连接于所述第二乘法器的输出端口;所述第二加法器的另一个输入端口连接于所述第一加法器的其中一个输出端口;

[0041]

第三寄存器,所述第三寄存器的输入端口连接于所述第二加法器的输出端口;

[0042]

mux选择器,所述mux选择器的其中一个输入端口连接于所述第三寄存器的输出端口;

[0043]

第三乘法器,所述第三乘法器的输入端口连接于所述mux选择器的输出端口;

[0044]

第三加法器,所述第三加法器的其中一个输入端口连接于所述第三乘法器的输出端口;

[0045]

第四加法器,所述第四加法器的其中一个输入端口连接于所述第三加法器的输入端口;所述第四加法器的其中一个输出端口连接于所述输出节点;

[0046]

第四乘法器,连接于所述第一加法器与所述第三加法器之间,所述第四加法器的输入端连接所述第一加法器的其中一个输出端口,所述第四加法器的输出端口连接所述第三加法器的另一个输入端口;

[0047]

第五乘法器,连接于所述第四加法器与所述第二寄存器之间;所述第五乘法器的输入端连接所述第二寄存器的输出端口,所述第五乘法器的输出端口连接所述第四加法器的输入端口;

[0048]

第四寄存器,连接于所述mux选择器与所述第四加法器之间;所述第四寄存器的输入端口连接所述第四加法器的另一个输出端口,所述第四寄存器的输出端口连接所述mux选择器的另一个输入端口。

[0049]

进一步地,所述计算电路还包括:

[0050]

计数器,用于对输入数据块计数,控制所述寄存器数据的读写位置。

[0051]

本发明实施例提供的一种支持码字同步的伴随式计算方法,大幅提升搜寻初始位置的速度,使计算速度提升,节省了逻辑单元和存储空间;本发明实施例提供的一种支持码字同步的伴随式计算电路,增加伴随式计算模块功能,可支持码字同步。

附图说明

[0052]

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0053]

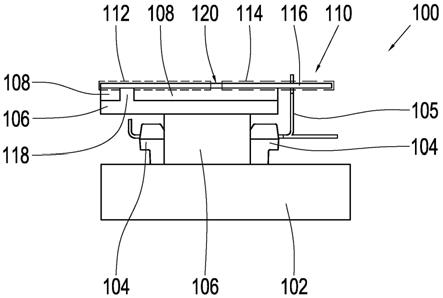

图1为背景技术中160bit位宽(528,514)rs码的伴随式计算的硬件实现框架示意图;

[0054]

图2为本发明实施例提供的一种支持码字同步的伴随式计算方法时迭代的示意图;

[0055]

图3为本发明实施例提供的一种支持码字同步的伴随式计算方法进行迭代计算参考时序的示意图;

[0056]

图4为本发明实施例提供的一种支持码字同步的伴随式计算电路的框架示意图;

[0057]

图5为图4电路中一组伴随式计算电路的框架示意图。

[0058]

图中,1、第一乘法器,2、第一加法器,3、第一寄存器,4、第二寄存器,5、第二乘法器,6、第二加法器,7、第三寄存器,8、mux选择器,9、第三乘法器,10、第三加法器,11、第四加法器,12、第四乘法器,13、第五乘法器,14、第四寄存器。

具体实施方式

[0059]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0060]

本技术中的术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”、“第三”的特征可以明示或者隐含地包括至少一个该特征。本技术的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。本技术实施例中所有方向性指示(诸如上、下、左、右、前、后

……

)仅用于解释在某一特定姿态(如附图所示)下各部件之间的相对位置关系、运动情况等,如果该特定姿态发生改变时,则该方向性指示也相应地随之改变。此外,术语“包括”和“具有”以及它们任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可选地还包括没有列出的步骤或单元,或可选地还包括对于这些过程、方法、产品或设备固有的其它步骤或单元。

[0061]

在本文中提及“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本技术的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合。

[0062]

本发明实施例提供的一种支持码字同步的伴随式计算方法,如图2所示,为两个(528,514)rs码字,每个rs码字由33个数据块(block)组成,每个block的数据位宽为160bit,以输入的第一个rs码字的第1个block的0bit作为起始位置,以第一个rs码字的第33个block的159bit作为终止位置,计算第一个伴随式具体为:

[0063]

构建一个合适的有限域元素矩阵,在每个有效标志(valid)下并行计算16个码元的数据,以输入的第一个rs码字,计算伴随式设r

527

是一个rs码字中最早发送同时也是最早接收到的码元,r0是最晚发送也是最晚接收到的码元。

[0064]

由第1个有效valid数据位宽160bit的数据得到:

[0065]r527

αi×

16

r

526

αi×

15

r

525

αi×

14

r

524

αi×

13

... r

514

αi×3 r

513

αi×2 r

512

αi×1=r0 0=j0[0066]

由第2个有效valid数据位宽160bit的数据得到:

[0067]

[r

511

αi×

16

r

510

αi×

15

r

509

αi×

14

r

508

αi×

13

... r

498

αi×3 r

497

αi×2 r

496

αi×1] j0×

αi×

16

=r1 j0×

αi×

16

=j1[0068]

由第3个有效valid数据位宽160bit的数据得到:

[0069]

[r

495

αi×

16

r

494

αi×

15

r

493

αi×

14

r

492

αi×

13

... r

482

αi×3 r

481

αi×2 r

480

αi×1] j1×

αi×

16

=r2 j1×

αi×

16

=r2 (r1 r0×

αi×

16

)αi×

16

=j2

[0070]

依次类推,由第33个有效valid数据位宽160bit的数据,对预存的有限域元素矩阵降次,得到:

[0071]

[r

15

αi×

15

r

14

αi×

14

r

13

αi×

13

r

12

αi×

12

... r2αi×2 r1αi×1 r0αi×0] j

31

×

αi×

15

=r

32

j

31

×

αi×

15

=r

32

(r

31

...(r2 (r1 r0×

αi×

16

)αi×

16

)...)αi×

15

=j

32

=r

527

αi×

527

r

526

αi×

526

r

525

αi×

525

r

524

αi×

524

... r2αi×2 r1αi×1 r0αi×0[0072]

其中r为每个有效valid的16个码元数据计算得到的结果;j则为每个有效valid的结果累加上一个时钟的结果后的中间结果;α为有限域中的元素;

[0073]

将每个有效valid计算的r0,r1,

…

,r

32

存储,则j

32

为以输入的第一个码字的第1个block的0bit作为起始位置所计算出的伴随式

[0074]

可以理解,伴随式还可以由第一rs码字通过现有的伴随式计算公式得到。

[0075]

然后以输入的第一个rs码字的第2个block的0bit作为起始位置,以输入的第二个rs码字的第1个block的159bit作为终止位置,计算出伴随式则当第34个有效valid时,开始计算第二个rs码字的伴随式,其计算公式为:

[0076]

r-1

αi×

16

r-2

αi×

15

r-3

αi×

14

r-4

αi×

13

... r-14

αi×3 r-15

αi×2 r-16

αi×1=r

33

0=j

33

[0077]

由于r0是第一个rs码字的最低位码元,则r-1

为第二个rs码字的最高位码元,即首先收到的第二个rs码字的第一个block的最高位码元。则迭代伴随式的计算模型为:

[0078]si1

=r

33

αi×

(-1)

s

i0

αi×

16-r0αi×

527

[0079]

=r-1

αi×

15

r-2

αi×

14

r-3

αi×

13

r-4

αi×

12

... r-14

αi×2 r-15

αi×1 r-16

αi×0 r

527

αi×

(527 16)

r

526

αi×

(526 16)

... r

512

αi×

(512 16)

r

511

αi×

(511 16)

... r1αi×

17

r0αi×

16-r

527

αi×

(16 527)

r

526

αi×

(15 527)

r

525

αi×

(14 527)

... r

513

αi×

(2 527)

r

512

αi×

(1 527)

[0080]

=r-16

αi×0 r-15

αi×1 r-14

αi×2 r-13

αi×3 ... r0αi×

16

... r

509

αi×

525

r

510

αi×

526

r

511

αi×

527

[0081]si1

即为以第一个rs码字第二个有效valid的第0bit为起始位置,以第二个rs码字第一个有效valid的第159bit为终止位置得到的伴随式,即为[r-16

,r-15

,r-14

,

…

,r

510

,r

511

]码元的伴随式。

[0082]

则当第35个有效valid时,以输入的第一个rs码字的第三个block的0bit为起始位置,以输入的第二个rs码字的第二个block的159bit作为终止位置,计算出的伴随式则迭代伴随式的计算模型为:

[0083]si2

=r

34

αi×

(-1)

s

i1

αi×

16-r1αi×

527

[0084]

=r-17

αi×

15

r-18

αi×

14

r-19

αi×

13

r-20

αi×

12

... r-30

αi×2 r-31

αi×1 r-32

αi×0 r

511

αi×

(527 16)

r

510

αi×

(526 16)

... r

496

αi×

(512 16)

r

495

αi×

(511 16)

... r-15

αi×

17

r-16

αi×

16-r

511

αi×

(16 527)

r

510

αi×

(15 527)

r

509

αi×

(14 527)

... r

497

αi×

(2 527)

r

496

αi×

(1 527)

[0085]

=r-32

αi×0 r-31

αi×1 r-30

αi×2 r-29

αi×3 ... r-16

αi×

16

... r

493

αi×

525

r

494

αi×

526

r

495

αi×

527

[0086]

以此类推,以输入的第一个rs码字的第33个block的0bit作为起始位置,以输入的第二个rs码字的第32个block的159bit作为终止位置,计算出伴随式综上,利用遍历2

个rs码字得到33组伴随式,分别以一个rs码字中不同时钟下的160bit数据的第0bit为起始位,即以输入的rs码字的0bit,160bit,320bit,

…

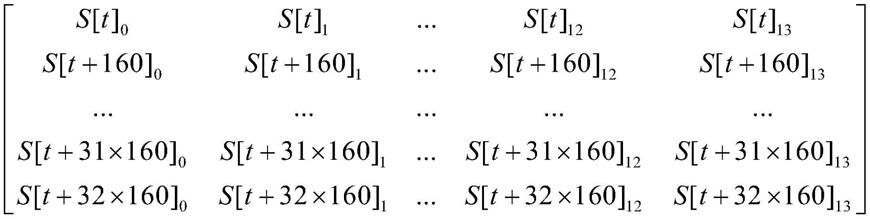

,5120bit为起始位置,则可以得到如下矩阵:

[0087][0088]

其中,t表示所得伴随式的起始bit位置。

[0089]

rs码字在解码时需要数据已经同步,即准确的找到每个码字的起始位置,因此在进行解码前需要先通过同步码的搜寻以找到准确位置。而当rs码位置准确且码字没有传输错误时,其计算出的14个伴随式全部为0,根据该特性,通过伴随式的计算结果进行码字是否同步完成的判断。

[0090]

一个(528,514)的rs码字中包括了528个10bit的码元,现有伴随式算法计算一个rs码字的伴随式需要一个完整的码字周期t(如果数据valid为bus型,则为33个clk,需要遍历5280个可能起始位置至少需要5280

×

t个clk。本技术实施例的技术方案如遍历5280bit位置,则t需要取160次,则共需时间为160

×2×

t(t为一个码字的周期),计算速度大大提快,节省了逻辑单元和存储空间,并加速了对起始位置的搜寻。

[0091]

伴随式模块进行迭代计算的参考时序示意图如图3所示,为两个rs码字的并行迭代计算伴随式的示意图,其中每个码字实际各有33个block,clock为时钟波形,data-in是在电路中数据位宽160bit,即16个码元,eocw为码字的结束标志位,sdm_vld为现有算法所得的伴随式的valid,sdm_vld_ite为本技术实施例并行迭代算法所得伴随式的valid,将两种信号取mux,则可以得到通过这两个码字得到的33个以不同bit作为初始位置计算出的码字伴随式。

[0092]

如图4所示为本发明实施例的一种支持码字同步的伴随式计算电路框架示意图,图5为图4电路中一组伴随式计算电路的框架示意图,所述计算电路包括:

[0093]

输入节点,输入输入信号;

[0094]

输出节点,输出输出信号;

[0095]

第一乘法器1,所述第一乘法器1的输入端口连接于所述输入节点;

[0096]

第一加法器2,所述第一加法器2的输入端口连接于所述第一乘法器1的输出端口;

[0097]

第一寄存器3,所述第一寄存器3的输入端口连接于所述第一加法器2的其中一个输出端口;以及

[0098]

第二寄存器4,所述第二寄存器4的输入端口连接于所述第一加法器2的另一个输出端口;

[0099]

第二乘法器5,所述第二乘法器5的输入端口连接于所述第一寄存器3的输出端口;

[0100]

第二加法器6,所述第二加法器6的其中一个输入端口连接于所述第二乘法器5的输出端口;所述第二加法器6的另一个输入端口连接于所述第一加法器2的其中一个输出端口;

[0101]

第三寄存器7,所述第三寄存器7的输入端口连接于所述第二加法器6的输出端口;

[0102]

mux选择器8,所述mux选择器8的其中一个输入端口连接于所述第三寄存器7的输出端口;

[0103]

第三乘法器9,所述第三乘法器9的输入端口连接于所述mux选择器8的输出端口;

[0104]

第三加法器10,所述第三加法器10的其中一个输入端口连接于所述第三乘法器9的输出端口;

[0105]

第四加法器11,所述第四加法器11的其中一个输入端口连接于所述第三加法器10的输入端口;所述第四加法器11的其中一个输出端口连接于所述输出节点;

[0106]

第四乘法器12,连接于所述第一加法器2与所述第三加法器10之间,所述第四加法器12的输入端连接所述第一加法器2的其中一个输出端口,所述第四加法器12的输出端口连接所述第三加法器10的另一个输入端口;

[0107]

第五乘法器13,连接于所述第四加法器11与所述第二寄存器4之间;所述第五乘法器13的输入端连接所述第二寄存器4的输出端口,所述第五乘法器13的输出端口连接所述第四加法器11的输入端口;

[0108]

第四寄存器14,连接于所述mux选择器8与所述第四加法器11之间;所述第四寄存器14的输入端口连接所述第四加法器11的另一个输出端口,所述第四寄存器14的输出端口连接所述mux选择器8的另一个输入端口。

[0109]

可以理解,在本发明实施例中计算中间结果s0,s1,

…

,s

13

时增加了一个乘法器,可以将当前时钟下的r0(数据与矩阵的计算结构)单独存储,避免了与上一个时钟下的r0复用。同时,增加了寄存器,将码字内除了最后一个block的r0,r1,

…

,r

13

均存储下来,即每个block的结果为16

×

10=160bit,共需存储32个。另外,选用计数器对输入valid进行技术,以此来控制寄存器数据的读写位置。构建了新的计算逻辑单元,以当前时钟下计算的结果、前一个block作为初始位置计算的伴随式结果、之前存储的数据进行迭代。增加了mux选择器,迭代计算中使用上一个block下的伴随式进行计算,在第一次迭代时选取的是正常算法下得出的伴随式,而之后则选取迭代后计算出的伴随式,使同步码的搜寻在找到准确位置时的效率显著提升。

[0110]

所述计算电路还包括:

[0111]

计数器,用于对输入数据块计数,控制所述寄存器数据的读写位置。

[0112]

本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的计算机程序可寄存于一非易失性计算机可读取寄存介质中,该计算机程序在执行时,可包括如上述各方法的实施例的流程。其中,本技术所提供的各实施例中所使用的对寄存器、寄存、数据库或其它介质的任何引用,均可包括非易失性和/或易失性寄存器。非易失性寄存器可包括只读寄存器(rom)、可编程rom(prom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)或闪存。易失性寄存器可包括随机存取寄存器(ram)或者外部高速缓冲寄存器。作为说明而非局限,ram以多种形式可得,诸如静态ram(sram)、动态ram(dram)、同步dram(sdram)、双数据率sdram(ddrsdram)、增强型sdram(esdram)、同步链路(synchlink)dram(sldram)、寄存器总线(rambus)直接ram(rdram)、直接寄存器总线动态ram(drdram)、以及寄存器总线动态ram(rdram)等。

[0113]

所属领域的技术人员可以清楚地了解到,为了描述的方便和简洁,仅以上述各功

能单元、模块的划分进行举例说明,实际应用中,可以根据需要而将上述功能分配由不同的功能单元、模块完成,即将所述装置的内部结构划分成不同的功能单元或模块,以完成以上描述的全部或者部分功能。

[0114]

以上所述实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。