1.本技术涉及电子设备技术领域,尤其涉及一种阵列基板、阵列基板的制作方法、显示面板和电子设备。

背景技术:

2.随着科技的进步以及需求的日益提高,客户对产品的亮度需求不断提高,但随着背光亮度的大幅度提升,会导致产品亮度不均一的问题增加,不良率高达90%以上。

3.现有技术中为了避免高亮背光下薄膜晶体管的特性异常,采用遮挡层进行遮光设计,遮挡层设置在多晶硅层的正下方,起到对栅极沟道的遮光作用,如图所示,最大可能的降低高亮背光对薄膜晶体管特性的影响。

4.然而,但在产品实际测试中,增加遮挡层后,仍存在亮度不均等不良现象,经分析其不良原因为源漏层上的信号极易受到遮挡层耦合电容的影响,引起正负两帧的像素电压不同,画面亮度明暗交替,导致亮度漂移。即单纯增加遮挡层无法大幅度改善产品的亮度不均一的问题。因此,如何改善产品亮度不均一的问题成为亟待解决的问题。

技术实现要素:

5.本技术实施例的目的是提供一种产品亮度不均一的问题,以使产品在背光亮度大幅度提升的情况下,产品亮度均一,降低产品的不良率。

6.为解决上述技术问题,本技术实施例提供如下技术方案:

7.本技术第一方面提供一种阵列基板,包括:

8.多个功能区域,多个功能区域之间间隔设置;

9.每个功能区域均包括遮挡层,相邻两个功能区域中的遮挡层相互连接,

10.且多个所述遮挡层中的一个与接地区域连接。

11.在该技术方案中,多个功能区域包括连接区域;

12.所述连接区域还包括:

13.玻璃基板,所述玻璃基板设置在所述遮挡层下方;

14.缓冲层,所述缓冲层设置在所述遮挡层上方;

15.钝化多晶硅绝缘层,所述钝化多晶硅绝缘层设置在所述缓冲层上方;

16.层间介质层,所述层间介质层设置在所述钝化多晶硅绝缘层上方;

17.源漏层,所述源漏层设置在所述层间介质层上方,所述源漏层通过原有的接地走线与所述接地区域连接,所述源漏层与所述遮挡层通过遮挡层的金属走线连接。

18.在该技术方案中,所述接地走线外设置有静电环,所述接地走线包括所述遮挡层的金属走线和所述源漏层的原有的接地走线。

19.在该技术方案中,所述连接区域的所述层间介质层具有过孔,所述过孔穿透所述钝化多晶硅绝缘层和所述缓冲层,所述遮挡层的金属走线通过所述层间介质层的过孔与所述源漏层连接。

20.在该技术方案中,多个功能区域包括:

21.接地绑定区域;

22.所述接地绑定区域还包括:

23.玻璃基板,所述玻璃基板设置在所述遮挡层下方;

24.缓冲层,所述缓冲层设置在所述遮挡层上方;

25.钝化多晶硅绝缘层,所述钝化多晶硅绝缘层设置在所述缓冲层上方;

26.层间介质层,所述层间介质层设置在所述钝化多晶硅绝缘层上方;

27.源漏层,所述源漏层设置在所述层间介质层上方,所述源漏层通过原有的接地走线与接地区域连接,所述源漏层与所述遮挡层通过遮挡层的金属走线连接。

28.在该技术方案中,所述接地绑定区域的层间介质层具有过孔,所述过孔穿透所述钝化多晶硅绝缘层和所述缓冲层,以使所述遮挡层的金属走线将所述源漏层与所述遮挡层连接。

29.在该技术方案中,接地走线上设置有静电环,所述接地走线包括所述遮挡层的金属走线和所述源漏层的原有的接地走线。

30.在该技术方案中,所述遮挡层为挡光金属层,遮挡层的厚度大于1000a。

31.在该技术方案中,多个功能区域还包括显示区域、goa区域和数据选择器区域,所述goa区域位于所述显示区域两侧,所述数据选择区域与所述显示区域相对设置。

32.本技术第二方面提供一种阵列基板的制作方法,包括:

33.设置多个功能区域;

34.在每个功能区域均形成有遮挡层;

35.将相邻两个功能区域中的遮挡层相互连接;

36.将多个所述遮挡层中的一个与接地区域连接。

37.本技术第三方面提供一种显示面板,包括如前所述的阵列基板和柔性电路板,述柔性电路板接地,所述阵列基板的遮挡层与所述柔性电路板连接。

38.本技术第四方面提供一种电子设备,包括如前所述的显示面板。

39.相较于现有技术,本技术第一方面提供的阵列基板、阵列基板的制作方法、显示面板和电子设备,其中,阵列基板包括多个功能区域,多个功能区域之间间隔设置,每个功能区域设置有遮光板,相邻两个功能区域的遮光板相互连接,从而相对于现有技术中,相邻的tft开关下的功能区域相互独立,均为漂移状态,这种情况下遮挡层并不能起到传输信号的作用,源漏层上的信号极易受到遮挡层耦合电容的影响,引起正负两帧的像素电压不同,画面亮度明暗交替,导致亮度不均一,状态漂移。本技术将多个功能区域中相邻的两个功能区域的遮挡层进行连接,从而使得多个功能区域变成连接的金属网,且多个遮挡层中的一个与接地区域连接,从而实现遮挡层的接地,而多个功能区域的遮挡层相互连接,即多个功能区域的遮挡层均实现接地,通过遮挡层接地的设置改变遮挡层原有的漂移状态,从而使得遮挡层不再影响源漏层上的信号的耦合电容,从而从根本上解决了因源漏层与遮挡层耦合导致的亮度不均一的不良问题,进而改善因遮挡层漂移导致的电子设备等超高亮背光产品的亮度不均等不良问题。

附图说明

40.通过参考附图阅读下文的详细描述,本技术示例性实施方式的上述以及其他目的、特征和优点将变得易于理解。在附图中,以示例性而非限制性的方式示出了本技术的若干实施方式,相同或对应的标号表示相同或对应的部分,其中:

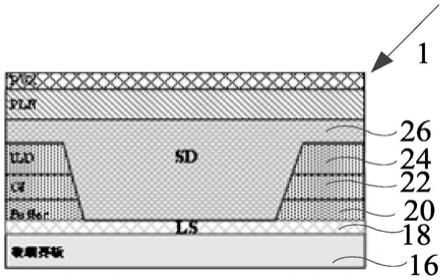

41.图1示意性地示出了现有技术中阵列基板的结构示意图;

42.图2示意性地示出了本技术中连接区域的截面示意图;

43.图3示意性地示出了本技术中连接区域的平面示意图;

44.图4示意性地示出了本技术中接地绑定区域与柔性电路板连接的平面示意图;

45.图5示意性地示出了本技术中柔性电路板的截面示意图;

46.现有技术附图标号如下:阵列基板1',遮挡层12',多晶硅层14',源漏层16';

47.本技术附图标号说明:

48.阵列基板1,静电环122,接地绑定区域14,玻璃基板16,遮挡层18,缓冲层20,钝化多晶硅绝缘层22,层间介质层24,过孔242,源漏层26,绝缘层30,栅极层32,柔性电路板2。

具体实施方式

49.下面将参照附图更详细地描述本公开的示例性实施方式。虽然附图中显示了本公开的示例性实施方式,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施方式所限制。相反,提供这些实施方式是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

50.需要注意的是,除非另有说明,本技术使用的技术术语或者科学术语应当为本技术所属领域技术人员所理解的通常意义。

51.现有技术中,对mos开关进行薄膜晶体管在正常情况下和背光开启情况下的特性测试,在2wnit的高亮背光下,薄膜晶体管开关的背光开启情况下亮度特性比正常情况下亮度会上升约40~60倍,背光开启情况下薄膜晶体管漏电流远远高于正常情况下的水平。在这种高亮背光下,亮度太高会导致薄膜晶体管开关无法正常关闭。

52.为了避免高亮背光下薄膜晶体管特性异常,改善亮度不均一的不良问题,不仅在显示区域设置有遮挡层12',在外围电路区域也都增加了遮挡层12'。遮挡层12'设置在多晶硅层14'的正下方,起到对栅极沟道的遮光作用,阵列基板1'的膜层结构示意图如图1所示,但不同于栅极层和源漏层16',遮挡层12'在设计上一直处于漂移的状态,并不起到传输信号的作用。

53.与显示区域的薄膜晶体管相比,外围电路区域的薄膜晶体管开关的w/l较大,从而驱动能力较强。而当其下方均有遮挡层12'设计时,遮挡层12'与多晶硅或源漏层16'的正对面积较大,两者之间存在的耦合电容就会影响信号,进而影响整体显示效果。如图2所示,在膜层截面示意图中,可以看到在层间介质层过孔位置,遮挡层12'与源漏层16'仅间隔缓冲层,缓冲层膜层厚度仅3000a左右,即源漏层16'极易受到遮挡层12'的耦合影响,导致了源漏层16'信号的不稳定。当源漏层16'切换信号时(如0v

→

5v/-5v),同时遮挡层12'处于漂移状态,源漏层16'与遮挡层12'发生耦合,源漏层16'电压被耦合到约 2v/-2v,导致源漏层16'受到影响无法有效切换至 5v/-5v。该耦合会导致源漏层16'信号整体不稳定,充电不完全,显示效果为存在亮度不均一的不良现象。

54.而为了改善该不良现象主要有以下两种方法。方法一为增加缓冲层的膜层厚度,从而使得源漏层16'与遮挡层12'的距离更远,因为电容与两者的距离成反比,进而降低两者间的耦合电容。但缓冲层膜层厚度的增加,整体透过率会大大降低,改善效果较差。方法二为减少遮挡层12'及栅极层的耦合正对面积,即减小遮挡层12'的cd大小,但产品的背光亮度需求范围从几万到十几万,单纯减小遮挡层12'的cd大小,会大大降低高亮背光下的遮挡有效性,会导致亮度不均一,使得不良率大大增加,从工艺上无法从根本上完全解决这一难题。

55.本技术提供了一种阵列基板1,包括:

56.多个功能区域,多个功能区域之间间隔设置;

57.每个功能区域均包括遮挡层,相邻两个功能区域中的遮挡层相互连接,且多个所述遮挡层中的一个与接地区域连接。

58.如图2所示,在本技术实施例中,本技术第一方面提供的阵列基板1,包括多个功能区域,多个功能区域之间间隔设置,每个功能区域设置有遮光板,相邻两个功能区域的遮光板相互连接,从而相对于现有技术中,相邻的tft开关下的功能区域相互独立,均为漂移状态。本技术将多个功能区域中相邻的两个功能区域的遮挡层18进行连接,从而使得多个功能区域变成连接的金属网,且多的一个个遮挡层中与接地区域连接,从而实现遮挡层18的接地,而多个功能区域的遮挡层18相互连接,即多个功能区域的遮挡层18均实现接地,通过遮挡层18接地的设置改变遮挡层18原有的漂移状态,从而使得遮挡层18不再影响源漏层26上的信号的耦合电容,从而从根本上解决了因源漏层26与遮挡层18耦合导致的亮度不均一的不良问题,从而本技术提供的阵列基板1,在不降低透过率和静电释放的情况下,改善因遮挡层18漂移导致的电子设备等超高亮背光产品的亮度不均等不良问题。

59.在本技术的一个实施例中,

60.多个功能区域包括连接区域;

61.所述连接区域还包括:

62.玻璃基板,所述玻璃基板设置在所述遮挡层下方;

63.缓冲层,所述缓冲层设置在所述遮挡层上方;

64.钝化多晶硅绝缘层,所述钝化多晶硅绝缘层设置在所述缓冲层上方;

65.层间介质层,所述层间介质层设置在所述钝化多晶硅绝缘层上方;

66.源漏层,所述源漏层设置在所述层间介质层上方,所述源漏层通过原有的接地走线与所述接地区域连接,所述源漏层与所述遮挡层通过遮挡层的金属走线连接。

67.如图3所示,在该实施例中,多个功能区域包括显示区域和外围电路区域,外围电路区域包括连接区域,连接区域的遮挡层用于与柔性电路板连接,而柔性线路板与接地区域连接,从而实现连接区域遮挡层的接地,连接区域的接地走线采用源漏层26金属走线设计,绕电子设备一周,在接口侧接地走线连接到柔性电路板,柔性电路板接地,从而实现连接区域的接地,连接区域包括玻璃基板16、遮挡层18、缓冲层20、钝化多晶硅绝缘层22、层间介质层24和源漏层26,其中,遮挡层18层叠设置在玻璃基板16上方,遮挡层18层叠设置有缓冲层20,缓冲层20上层叠设置有钝化多晶硅绝缘层22,钝化多晶硅绝缘层22上层叠设置有源漏层26,源漏层与遮挡层连接,从而实现遮挡层的接地,通过遮挡层18接地的设置改变遮挡层18原有的漂移状态,从而使得遮挡层18不再影响源漏层26上的信号的耦合电容,从而

从根本上解决了因源漏层26与遮挡层18耦合导致的亮度不均一的不良问题,从而本技术提供的阵列基板1,在不降低透过率和静电释放的情况下,改善因遮挡层18漂移导致的电子设备等超高亮背光产品的亮度不均等不良问题。

68.在本技术的一个实施例中,所述层间介质层具有过孔,所述过孔穿透所述钝化多晶硅绝缘层和所述缓冲层,以使所述遮挡层的金属走线将所述源漏层与所述遮挡层连接。

69.如图3所示,在该实施例中,通过改变接地走线的路径,将层间介质层24设置有过孔242,使得遮挡层金属走线能够跳线到源漏层26上,从而实现遮挡层的接地,多个功能区域包括显示区域和外围电路区域,外围电路区域包括连接区域,连接区域用于与接地区域柔性电路板连接,以实现接地,连接区域的接地走线采用源漏层26金属走线设计,绕电子设备一周,在接口侧接地走线连接到柔性电路板,柔性电路板接地,从而实现连接区域的接地,连接区域包括玻璃基板16、遮挡层18、缓冲层20、钝化多晶硅绝缘层22、层间介质层24和源漏层26,其中,遮挡层18层叠设置在玻璃基板16上方,遮挡层18层叠设置有缓冲层20,缓冲层20上层叠设置有钝化多晶硅绝缘层22,钝化多晶硅绝缘层22上层叠设置有源漏层26,连接区域中层间介质层24具有过孔242,过孔242穿透钝化多晶硅绝缘层22和缓冲层20,从而源漏层26与遮挡层通过过孔242可以进行连接,遮挡层的金属走线通过层间介质层24的过孔242跳线到源漏层26的接地走线上,从而实现了遮挡层的接地。通过遮挡层18接地的设置改变遮挡层18原有的漂移状态,从而使得遮挡层18不再影响源漏层26上的信号的耦合电容,从而从根本上解决了因源漏层26与遮挡层18耦合导致的亮度不均一的不良问题,从而本技术提供的阵列基板1,在不降低透过率和静电释放的情况下,改善因遮挡层18漂移导致的电子设备等超高亮背光产品的亮度不均等不良问题。

70.如图3所示,在本技术的一个实施例中,所述接地走线外设置有静电环122,所述接地走线包括所述遮挡层的金属走线和所述源漏层26的原有的接地走线。

71.在该实施例中,遮挡层的金属走线与原本的接地走线连接后,遮挡层的金属走线也是接地走线的一部分,在接地走线外设置有静电环122,能够防止新增的遮挡层的金属走线部分可能造成的静电释放不良的问题,进而有效预防新增的接地走线的静电击穿的风险。

72.在本技术的一个实施例中,多个功能区域包括:

73.接地绑定区域14;

74.接地绑定区域;

75.所述接地绑定区域还包括:

76.玻璃基板,所述玻璃基板设置在所述遮挡层下方;

77.缓冲层,所述缓冲层设置在所述遮挡层上方;

78.钝化多晶硅绝缘层,所述钝化多晶硅绝缘层设置在所述缓冲层上方;

79.层间介质层,所述层间介质层设置在所述钝化多晶硅绝缘层上方;

80.源漏层,所述源漏层设置在所述层间介质层上方,所述源漏层通过原有的接地走线与接地区域连接,所述源漏层与所述遮挡层通过遮挡层的金属走线连接。

81.如图2和图4所示,在该实施例中,多个功能层包括接地绑定区域14,即本技术相对于现有技术新增了接地绑定区域,接地绑定区域包括玻璃基板16、遮挡层18、缓冲层20、钝化多晶硅绝缘层22、层间介质层24和源漏层26,接地绑定区域14的源漏层26与其它功能区

域的源漏层26连接,接地绑定区域14的源漏层26还与柔性电路板2上的源漏层26连接,柔性电路板2接地,从而使得新增的接地绑定区域14接地,且接地绑定区域14中源漏层与遮挡层连接,从而实现遮挡层的接地。通过遮挡层18接地的设置改变遮挡层18原有的漂移状态,从而使得遮挡层18不再影响源漏层26上的信号的耦合电容,从而从根本上解决了因源漏层26与遮挡层18耦合导致的亮度不均一的不良问题,从而本技术提供的阵列基板1,在不降低透过率和静电释放的情况下,改善因遮挡层18漂移导致的电子设备等超高亮背光产品的亮度不均等不良问题。

82.如图2和4所示,在本技术的一个实施例中,所述层间介质层24具有过孔,所述过孔穿透所述钝化多晶硅绝缘层和所述缓冲层,以使所述遮挡层的金属走线将所述源漏层与所述遮挡层连接。

83.在该实施例中,多个功能层包括接地绑定区域14,即本技术相对于现有技术新增了接地绑定区域,接地绑定区域包括玻璃基板16、遮挡层18、缓冲层20、钝化多晶硅绝缘层22、层间介质层24和源漏层26,接地绑定区域14的源漏层26与其它功能区域的源漏层26连接,接地绑定区域14的源漏层26还与柔性电路板2上的源漏层26连接,柔性电路板2接地,从而使得新增的接地绑定区域14接地,且接地绑定区域14中层间介质层24具有过孔242,过孔242穿透钝化多晶硅绝缘层22和缓冲层20,以使遮挡层18的金属走线能够与源漏层26连接,从而实现遮挡层18的接地。其中,接地绑定区域14不包括栅极层32。另外,中层间介质层24形成过孔242的方式为,在对层间介质层24干刻时减少干刻时间,确保中层间介质层24上形成过孔242,并且该过孔242一次性穿过层间介质层24、钝化多晶硅绝缘层22和缓冲层20,从而实现源漏层26和遮挡层18的连接。

84.在本技术的一个实施例中,所述接地绑定区域14还包括:

85.绝缘层30,所述绝缘层30设置在所述源漏层26上方。

86.在该实施例中,接地绑定区域14还包括绝缘层30,绝缘层30设置在源漏层26上方,此时,绝缘层30不需要如现有技术那样进行开孔设计,也无需进行铟锡氧化物半导体透明导电膜的图案设计。

87.在本技术的一个实施例中,接地走线上设置有静电环,所述接地走线包括所述遮挡层的金属走线和所述源漏层的原有的接地走线。

88.在该实施例中,遮挡层的金属走线与原本的接地走线连接后,遮挡层的金属走线也是接地走线的一部分,在接地走线外设置有静电环122,能够防止新增的遮挡层的金属走线部分可能造成的静电释放不良的问题,进而有效预防新增的接地走线的静电击穿的风险。

89.在本技术的一个实施例中,所述遮挡层18为挡光金属层,遮挡层18的厚度大于1000a。

90.在该实施例中,遮挡层18为挡光金属层,一般采用金属钼,遮挡层18厚度为1000a以上,当金属钼形成的遮挡层18的厚度为500a时,光学密度为2.48,当金属钼形成的遮挡层18的厚度达到1000a时,光学密度可以达到4.25,遮挡效果好,从而遮挡层18的厚度要大于1000a,此时遮挡层18的遮挡效果较好。

91.在本技术的一个实施例中,所述遮挡层18的金属走线沿栅线或源极漏极金属线延伸,且所述遮挡层18的金属走线与所述栅线或源极漏极金属线上下交叠设置。

92.在该实施例中,在相邻两个功能区域的遮挡层18连接时,遮挡层18的金属走线沿栅线或源极漏极金属线延伸,且挡层的金属走线与所述栅线或源极漏极金属线上下交叠设置,从而遮挡层18金属走线的设置不会影响周边区域的透过率。

93.在本技术的一个实施例中,多个功能区域还包括显示区域、goa区域和数据选择器区域,所述goa区域位于所述显示区域两侧,所述数据选择区域与所述显示区域相对设置。

94.在该实施例中,多个功能区域包括显示区域、goa区域和数据选择器区域,其中,显示区域的两侧设置有goa区域,数据选择器区域与显示区域相对设置的,功能区域还包括静电释放等区域,用于释放静电,以上这些区域以及其它的功能区域均具有遮挡层18,且相连两个功能区域的遮挡层18相互连接,从而使得阵列基板1形成相互关联的金属网。

95.另一方面,本技术还提供一种阵列基板的制作方法,包括:

96.设置多个功能区域;

97.在每个功能区域均形成有遮挡层;

98.将相邻两个功能区域中的遮挡层相互连接;

99.将多个所述遮挡层中的一个与接地区域连接。

100.在该实施例中,阵列基板的制作方法包括设置多个功能区域,在每个功能区域均设置有遮挡层,将相邻两个功能区域中的遮挡层相互连接,并将多个所述遮挡层中的一个与接地区域连接,从而相对于现有技术中,相邻的tft开关下的功能区域相互独立,均为漂移状态。本技术将多个功能区域中相邻的两个功能区域的遮挡层18进行连接,从而使得多个功能区域变成连接的金属网,且多的一个个遮挡层中与接地区域连接,从而实现遮挡层18的接地,而多个功能区域的遮挡层18相互连接,即多个功能区域的遮挡层18均实现接地,通过遮挡层18接地的设置改变遮挡层18原有的漂移状态,从而使得遮挡层18不再影响源漏层26上的信号的耦合电容,从而从根本上解决了因源漏层26与遮挡层18耦合导致的亮度不均一的不良问题,从而本技术提供的阵列基板的制作方法,在不降低透过率和静电释放的情况下,改善因遮挡层18漂移导致的电子设备等超高亮背光产品的亮度不均等不良问题。

101.其中,在本技术的一个实施例中,将多个所述遮挡层中的一个与接地区域连接具体包括:

102.多个功能区域包括连接区域,

103.在连接区域中,在遮挡层下方设置有玻璃基板;

104.在遮挡层上方设置有缓冲层;

105.在缓冲层上方设置有钝化多晶硅绝缘层;

106.在钝化多晶硅绝缘层上设置层间介质层;

107.在层间介质层上设置源漏层,通过接地走线将源漏层与接地区域连接;

108.在层间介质层上设置过孔,所述过孔穿透所述钝化多晶硅绝缘层和所述缓冲层,以通过所述遮挡层的金属走线将所述源漏层与所述遮挡层连接。

109.在该实施例中,通过改变接地走线的路径,将层间介质层设置有过孔,使得遮挡层金属走线能够跳线到源漏层上,从而实现遮挡层的接地,多个功能区域包括显示区域和外围电路区域,外围电路区域包括连接区域,连接区域用于与接地区域柔性电路板连接,以实现接地,连接区域的接地走线采用源漏层金属走线设计,绕电子设备一周,在接口侧接地走线连接到柔性电路板,柔性电路板接地,从而实现连接区域的接地,连接区域包括玻璃基

板、遮挡层、缓冲层、钝化多晶硅绝缘层、层间介质层和源漏层,其中,遮挡层层叠设置在玻璃基板上方,遮挡层层叠设置有缓冲层,缓冲层上层叠设置有钝化多晶硅绝缘层,钝化多晶硅绝缘层上层叠设置有源漏层,连接区域中层间介质层具有过孔,过孔穿透钝化多晶硅绝缘层和缓冲层,从而源漏层与遮挡层通过过孔可以进行连接,遮挡层的金属走线通过层间介质层的过孔跳线到源漏层的接地走线上,从而实现了遮挡层的接地。通过遮挡层接地的设置改变遮挡层原有的漂移状态,从而使得遮挡层不再影响源漏层上的信号的耦合电容,从而从根本上解决了因源漏层与遮挡层耦合导致的亮度不均一的不良问题,从而本技术提供的阵列基板的制作方法,在不降低透过率和静电释放的情况下,改善因遮挡层漂移导致的电子设备等超高亮背光产品的亮度不均等不良问题。

110.在本技术的另一个实施例中,将多个所述遮挡层中的一个与接地区域连接具体包括:

111.多个功能区域包括接地绑定区域,

112.在接地绑定区域中,在遮挡层下方设置有玻璃基板;

113.在遮挡层上方设置有缓冲层;

114.在缓冲层上方设置有钝化多晶硅绝缘层;

115.在钝化多晶硅绝缘层上设置层间介质层;

116.在层间介质层上设置源漏层,通过原有的接地走线源漏层与接地区域连接;

117.在层间介质层上设置过孔,所述过孔穿透所述钝化多晶硅绝缘层和所述缓冲层,以通过所述遮挡层的金属走线将所述源漏层与所述遮挡层连接。

118.在该实施例中,多个功能层包括接地绑定区域,即本技术相对于现有技术新增了接地绑定区域,接地绑定区域包括玻璃基板、遮挡层、缓冲层、钝化多晶硅绝缘层、层间介质层和源漏层,接地绑定区域的源漏层与其它功能区域的源漏层连接,接地绑定区域的源漏层还与柔性电路板上的源漏层连接,柔性电路板接地,从而使得新增的接地绑定区域接地,且接地绑定区域中层间介质层具有过孔,过孔穿透钝化多晶硅绝缘层和缓冲层,以使遮挡层的金属走线能够与源漏层连接,从而实现遮挡层的接地。其中,接地绑定区域不包括栅极层。另外,中层间介质层形成过孔的方式为,在对层间介质层干刻时减少干刻时间,确保中层间介质层上形成过孔,并且该过孔一次性穿过层间介质层、钝化多晶硅绝缘层和缓冲层,从而实现源漏层和遮挡层的连接。

119.再一方面,本技术还提供一种显示面板,包括如前所述的阵列基板和柔性电路板2,所述柔性电路板接地,所述阵列基板的遮挡层与所述柔性电路板2连接。

120.在该实施例中,显示面板包括阵列基板和柔性电路板2,阵列基板包括多个功能区域,多个功能区域之间间隔设置,每个功能区域设置有遮光板,相邻两个功能区域的遮光板相互连接,从而使得多个功能区域变成连接的金属网,且多个遮挡层中的一个与柔性电路板2连接,柔性电路板2接地,从而实现遮挡层18的接地,而多个功能区域的遮挡层18相互连接,即多个功能区域的遮挡层18均实现接地,通过遮挡层18接地的设置改变遮挡层18原有的漂移状态,从而使得遮挡层18不再影响源漏层26上的信号的耦合电容,从而从根本上解决了因源漏层26与遮挡层18耦合导致的亮度不均一的不良问题,从而本技术提供的显示面板,在不降低透过率和静电释放的情况下,改善因遮挡层18漂移导致的电子设备等超高亮背光产品的亮度不均等不良问题。

121.如图5所示,其中,柔性电路板2包括玻璃基板16;缓冲层20,所述缓冲层20设置在所述玻璃基板16上方;钝化多晶硅绝缘层22,所述钝化多晶硅绝缘层22设置在所述缓冲层20上方;栅极层32,所述栅极层32设置在所述钝化多晶硅绝缘层22上方;层间介质层24,所述层间介质层24设置在所述钝化多晶硅绝缘层22上方;源漏层26,所述源漏层26设置在所述层间介质层24上方;绝缘层30,绝缘层30设置在源漏层26上方。

122.又一方面,本技术还提供一种电子设备,包括如前所述的显示面板,从而包括如前所述的显示面板的全部技术特征和有益技术效果,在此不再赘述。

123.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。