1.各种实施方式一般地涉及高速电平移位器,并且更具体地,涉及将低电压转换为高电压的高速电平移位器。

背景技术:

2.最近,家用电器配置为包括用于电子控制的微控制单元。

3.微控制单元配置为与家用电器的各种外部组件电连接,并执行必要的控制。例如,微控制单元配置为从诸如传感器的信号源接收信号,对所接收的信号执行数字信号处理,并将数字信号处理结果输出到外部。

4.微控制单元可以设计成使用低电压用于低功耗。

5.在微控制单元中进行数字信号处理的信号可以限定为逻辑信号,并且可以使用低电压来驱动该逻辑信号。例如,逻辑信号可以具有低电压范围,其使用作为低电压的1.2v的驱动电压。

6.不同于微控制单元,与微控制单元电连接的外部部件可以配置成使用高电压操作。高电压可以例示为5v,并且外部部件可以配置为使用5v的驱动电压接收高电压范围的信号。

7.出于该原因,为了与外部部件连接,微控制单元需要将逻辑信号从低电压范围转换到高电压范围并输出输出信号。

8.为此,可以在微控制单元中配置能够将逻辑信号从低电压范围转换到高电压范围的电平移位器。

9.通常,电平移位器输出具有与输入信号的电流成比例的电流量的输出信号,并且使用工作在高电压范围内的高电压晶体管来配置。

10.电平移位器需要具有足够的输入电流量的输入信号来驱动高电压晶体管以用于正常输出和高速操作。

11.微控制单元中的逻辑信号具有如上所述的低电压范围。因此,逻辑信号可能不具有足够的电流量用于电平移位器的正常输出和高速操作。

12.因此,电平移位器可能存在这样的问题,即电平移位器可能由于低电压范围的逻辑信号的输入而出现故障,或者由于逻辑信号的电流量不足而难以执行高速操作并且操作速度受到限制。

技术实现要素:

13.各种实施方式涉及高速电平移位器,当诸如微控制单元的电子设备在响应于低电压范围的逻辑信号输出高电压范围的输出信号时,该高速电平移位器可以防止出现故障并且能够进行高速操作。

14.此外,各种实施方式涉及高速电平移位器,该高速电平移位器可以通过使用低功率晶体管来防止出现故障,并且能够在通过使用低电压范围的输入信号输出高电压范围的

输出信号时进行高速操作,并且可以防止低功率晶体管被高电压损坏。

15.在实施方式中,高速电平移位器可以包括:输出电路,配置为响应于低电压范围的输入信号输出高电压范围的输出信号;输入电路,配置为响应于输入信号来控制输出信号的输出;以及连接电路,连接输出电路和输入电路,其中,输出电路工作在高电压范围内,其中,输入电路工作在低电压范围内,并且其中,连接电路降低从输出电路施加到输入电路的电压。

16.当诸如微控制单元的电子设备响应于低电压范围的输入信号输出高电压范围的输出信号时,根据本公开的实施方式的高速电平移位器可以防止出现故障并且能够进行高速操作以输出高电压范围的输出信号。

17.此外,根据本公开的实施方式的高速电平移位器可以防止配置为接收低电压范围的输入信号的低电压晶体管被损坏,并且可以保护低电压晶体管的漏极电压不受高电压的影响,这使得可以实现改进的可靠性并确保操作稳定性。

18.因此,使用根据本公开的实施方式的高速电平移位器的显示驱动设备可以以低功率驱动其中配置有输出缓冲器的每个输出通道,这使得可以降低芯片单元中的功耗。

附图说明

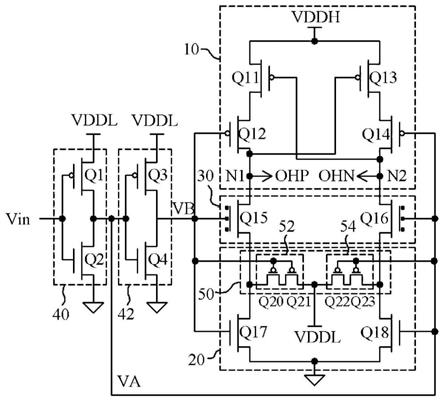

19.图1是示出根据本公开的实施方式的高速电平移位器的电路图。

20.图2是示出根据本公开的另一实施方式的高速电平移位器的电路图。

21.图3是示出根据本公开的又一实施方式的高速电平移位器的电路图。

具体实施方式

22.本公开公开了配置在执行数字信号处理的电子设备(诸如,微控制单元)中的高速电平移位器。

23.根据本公开的高速电平移位器被实施为响应于低电压范围的输入信号输出高电压范围的输出信号。

24.本公开的实施方式可以使用工作在低电压范围内的低电压晶体管来充分识别具有小的电流量的低电压范围的输入信号,而不会出现故障。

25.此外,本公开的实施方式可以包括用于防止低电压晶体管被用于驱动输出信号的高电压范围的输出驱动电压损坏的配置。此外,本公开的实施方式可以包括用于实现用于保护低电压晶体管的漏极电压的钳位功能的配置。

26.为了描述本公开的实施方式,低电压范围可以例示为0v至1.2v,并且低电压范围的驱动电压可以理解为1.2v。在实施方式的描述中,低电压范围的驱动电压被称为输入驱动电压。工作在低电压范围内的晶体管被称为低电压晶体管。

27.为了描述本公开的实施方式,高电压范围可以例示为0v至5v,并且高电压范围的驱动电压可以理解为5v。在实施方式的描述中,高电压范围的驱动电压被称为输出驱动电压。工作在高电压范围内的晶体管被称为高电压晶体管。

28.为了描述本公开的实施方式,中等电压范围可以例示为0v至3v,并且工作在中等电压范围内的晶体管被称为中等电压晶体管。

29.此外,为了描述本公开的实施方式,低电压晶体管的阈值电压可以例示为具有

0.2v至0.3v的电平,并且高电压晶体管的阈值电压可以例示为具有0.6v的电平。

30.根据本公开的实施方式的中等电压晶体管可以使用这样的晶体管,该晶体管的阈值电压具有基本上0v的电平并且充当将5v的输出驱动电压划分为3v的负载。为此,中等电压晶体管例如可以使用本征晶体管。

31.此外,为了描述本公开的实施方式,用于低电压范围和高电压范围的接地电压可以例示为0v,但是可以根据制造商的意图而不同地设置。

32.参照图1,根据本公开的实施方式的高速电平移位器配置为包括输出电路10、输入电路20和连接电路30。

33.根据本公开的实施方式的高速电平移位器配置为接收通过串联连接的两级反相器40和42提供的反相的输入信号va和非反相的输入信号vb。

34.反相器40配置为包括具有公共漏极的pmos晶体管q1和nmos晶体管q2。低电压范围的输入驱动电压vddl被施加到pmos晶体管q1的源极,并且低电压范围的接地电压被施加到nmos晶体管q2的源极。反相器40的pmos晶体管q1和nmos晶体管q2是低电压晶体管,共同接收输入信号vin,并通过公共漏极输出反相的输入信号va。输入信号vin可以理解为微控制单元的逻辑信号,并且反相器40通过使低电压范围的输入信号vin反相来输出低电压范围的反相的输入信号va。

35.反相器42配置为包括具有公共漏极的pmos晶体管q3和nmos晶体管q4。低电压范围的输入驱动电压vddl被施加到pmos晶体管q3的源极,并且低电压范围的接地电压被施加到nmos晶体管q4的源极。反相器42的pmos晶体管q3和nmos晶体管q4是低电压晶体管,共同接收反相器40的输出(即反相的输入信号va),并通过公共漏极输出非反相的输入信号vb。换言之,反相器42通过使低电压的反相的输入信号va反相来输出低电压的非反相的输入信号vb。

36.从反相器40和42输出的反相的输入信号va和非反相的输入信号vb被用于驱动高速电平移位器。

37.参照图1,反相的输入信号va和非反相的输入信号vb被提供给输出电路10、输入电路20和连接电路30。

38.输出电路10工作在高电压范围内,并且配置为响应于低电压范围的输入信号通过输出端子输出高电压范围的输出信号。

39.更详细地,输出电路10配置为包括作为高电压晶体管的pmos晶体管q11、q12、q13和q14以及输出端子。输出端子配置为包括并联配置的第一输出端子n1和第二输出端子n2。第一输出端子n1可以理解为输出第一输出信号ohp的节点或端子,并且第二输出端子n2可以理解为输出第二输出信号ohn的节点或端子。

40.输出驱动电压vddh被施加到pmos晶体管q11和q13的源极,pmos晶体管q12配置为通过pmos晶体管q11接收输出驱动电压vddh,pmos晶体管q14配置为通过pmos晶体管q13接收输出驱动电压vddh,pmos晶体管q12的漏极连接到输出第一输出信号ohp的第一输出端子n1,并且pmos晶体管q14的漏极连接到输出第二输出信号ohn的第二输出端子n2。

41.pmos晶体管q11的栅极连接到第二输出端子n2(即pmos晶体管q14的漏极),并且pmos晶体管q13的栅极连接到第一输出端子n1(即pmos晶体管q12的漏极)。pmos晶体管q12配置为使得非反相的输入信号vb被施加到其栅极,并且pmos晶体管q14配置为使得反相的

输入信号va被施加到其栅极。

42.当输入低电平的非反相的输入信号vb时,pmos晶体管q12导通,并且输出电路10输出通过pmos晶体管q11、pmos晶体管q12和第一输出端子n1传输的输出驱动电压vddh作为第一输出信号ohp。此时,pmos晶体管q11通过第二输出端子n2的具有低电平的第二输出信号ohn保持导通。当输入高电平的非反相的输入信号vb时,pmos晶体管q12截止,并且输出电路10的第一输出端子n1的电平被输入电路20控制到低电平。此时,pmos晶体管q11通过第二输出端子n2的具有高电平的第二输出信号ohn截止。

43.当输入低电平的反相的输入信号va时,pmos晶体管q14导通,并且输出电路10输出通过pmos晶体管q13、pmos晶体管q14和第二输出端子n2传输的输出驱动电压vddh作为第二输出信号ohn。此时,pmos晶体管q13通过第一输出端子n1的具有低电平的第一输出信号ohp保持导通。当输入高电平的反相的输入信号va时,pmos晶体管q14截止,并且输出电路10的第二输出端子n2的电平被输入电路20控制到低电平。此时,pmos晶体管q13通过第一输出端子n1的具有高电平的第一输出信号ohp截止。

44.换言之,输出电路10通过第一输出端子n1输出与非反相的输入信号vb相对应的第一输出信号ohp,并通过第二输出端子n2输出与反相的输入信号va相对应的第二输出信号ohn。

45.在以上配置中,pmos晶体管q12可以理解为工作在高电压范围内,并通过其栅极的非反相的输入信号vb选择性地将输出驱动电压vddh传输到第一输出端子n1,而pmos晶体管q14可以理解为工作在高电压范围内,并通过其栅极的反相的输入信号va选择性地将输出驱动电压vddh传输到第二输出端子n2。

46.连接电路30配置为将输出电路10的第一输出端子n1和第二输出端子n2连接到输入电路20,并且配置为降低从第一输出端子n1和第二输出端子n2中的每个施加到输入电路20的电压。

47.为此,连接电路30可以配置为响应于输入信号(即反相的输入信号va和非反相的输入信号vb)选择性地执行第一输出端子n1和第二输出端子n2到输入电路20的连接。

48.更详细地,连接电路30可以配置为包括连接晶体管q15和连接晶体管q16,连接晶体管q15将输出电路10的第一输出端子n1(即pmos晶体管q12的漏极)连接到输入电路20,连接晶体管q16将输出电路10的第二输出端子n2(即pmos晶体管q14的漏极)连接到输入电路20。连接晶体管q15可以由nmos晶体管配置,并且可以配置为使得其源极连接到下文将描述的输入电路20的nmos晶体管q17的漏极。连接晶体管q16可以由nmos晶体管配置,并且可以配置为使得其源极连接到下文将描述的输入电路20的nmos晶体管q18的漏极。

49.在图1的实施方式中,连接晶体管q15配置为使得非反相的输入信号vb被施加到其栅极,并且连接晶体管q16配置为使得反相的输入信号va被施加到其栅极。即,连接晶体管q15通过高电平的非反相的输入信号vb导通,并且连接晶体管q16通过高电平的反相的输入信号va导通。

50.连接电路30的连接晶体管q15和q16可以由中等电压晶体管配置。因此,连接电路30可以通过施加在具有中等电压晶体管特性的连接晶体管q15和q16中的每个的漏极与源极之间的电压来降低从输出电路10的第一输出端子n1或第二输出端子n2施加到输入电路20的电压。

51.连接电路30的电压降低程度可以由作为中等电压晶体管的连接晶体管q15和q16的物理特性来确定。连接电路30可以具有电压降低特性,使得由第一输出信号ohp和第二输出信号ohn施加在输入电路20上的电压可以具有包括在低电压范围内的电平。

52.通过以上描述,可以理解的是,连接电路30的连接晶体管q15和q16工作在中等电压范围内,该中等电压范围低于高电压范围并且高于低电压范围。然而,如果需要,连接电路30的连接晶体管q15和q16可以根据制造商的意图配置为低电压晶体管。

53.输入电路20工作在低电压范围内并且被配置为响应于输入信号来控制通过输出端子的输出信号的输出。换言之,输入电路20配置为响应于非反相的输入信号vb来控制第一输出端子n1的第一输出信号ohp的输出,并且响应于反相的输入信号va来控制第二输出端子n2的第二输出信号ohn的输出。

54.更详细地,输入电路20可以包括nmos晶体管q17和q18,它们是低电压晶体管。nmos晶体管q17工作在低电压范围内,并通过其栅极的非反相的输入信号vb选择性地将第一输出端子n1控制到接地电平,并且nmos晶体管q18工作在低电压范围内,并通过其栅极的反相的输入信号va选择性地将第二输出端子n2控制到接地电平。

55.nmos晶体管q17配置为使得接地电压被施加到源极,非反相的输入信号vb被施加到栅极,并且漏极连接到连接晶体管q15的源极。nmos晶体管q18配置为使得接地电压被施加到源极,反相的输入信号va被施加到栅极,并且漏极连接到连接晶体管q16的源极。

56.输入电路20可以包括钳位电路50,其配置在nmos晶体管q17的漏极与nmos晶体管q18的漏极之间。

57.当nmos晶体管q17或nmos晶体管q18截止时,钳位电路50将nmos晶体管q17或nmos晶体管q18的漏极钳位到恒定电压,并通过钳位来保护nmos晶体管q17或nmos晶体管q18的漏极电压。钳位电路50可以配置为使用输入驱动电压vddl作为恒定电压。

58.更详细地,钳位电路50可以包括用于保护nmos晶体管q17的漏极电压的第一钳位电路52和用于保护nmos晶体管q18的漏极电压的第二钳位电路54。

59.第一钳位电路52配置为,当nmos晶体管q17截止时,响应于非反相的输入信号vb而导通,并且从而将输入驱动电压vddl作为恒定电压提供给nmos晶体管q17的漏极。因此,第一钳位电路52可以保护nmos晶体管q17的漏极电压,使得nmos晶体管q17即使在截止时也具有恒定的电压。第二钳位电路54配置为,当nmos晶体管q18截止时,响应于反相的输入信号va而导通,并且从而将输入驱动电压vddl作为恒定电压提供给nmos晶体管q18的漏极。因此,第二钳位电路54可以保护nmos晶体管q18的漏极电压,使得nmos晶体管q18即使在截止时也具有恒定的电压。

60.上述第一钳位电路52可以包括串联连接的至少两个pmos晶体管,例如pmos晶体管q20和q21。pmos晶体管q20和q21具有共同施加有非反相的输入信号vb的栅极,并且串联连接在施加有恒定电压的端子与nmos晶体管q17的漏极之间。pmos晶体管q20和q21可以响应于低电平的非反相的输入信号vb而导通,并且从而可以将输入驱动电压vddl传输到nmos晶体管q17的漏极。

61.上述第二钳位电路54可以包括串联连接的至少两个pmos晶体管,例如pmos晶体管q22和q23。pmos晶体管q22和q23具有共同施加有反相的输入信号va的栅极,并且串联连接在施加有恒定电压的端子与nmos晶体管q18的漏极之间。pmos晶体管q22和q23可以响应于

低电平的反相的输入信号va而导通,并且从而可以将输入驱动电压vddl传输到nmos晶体管q18的漏极。

62.如上所述,在图1的实施方式中,使用作为低功率晶体管的nmos晶体管q17和q18来配置输入电路20。由于满足nmos晶体管q17和q18的工作范围的低电压范围的输入信号va和vb被施加到nmos晶体管q17和q18的栅极,因此nmos晶体管q17和q18可以通过足够的电流量来工作。因此,输出电路10也可以通过输入电路20的操作而具有正常输出并且可以高速操作,该输入电路20通过如上所述的满足其操作范围的足够的电流量来操作。

63.因此,可以防止图1的高速电平移位器出现故障,并且可以预期该高速电平移位器具有能够执行高速操作的效果。

64.此外,在图1的高速电平移位器中,连接电路30的电压降低可以防止施加到输出端子的高电压范围的高电压输出驱动电压vddh直接影响由低功率晶体管配置的输入电路20。因此,可以防止输入电路20的低电压晶体管被高电压损坏。

65.此外,在图1的高速电平移位器中,输入电路20的低电压晶体管的漏极电压可以由钳位电路50保护。因此,根据本公开的实施方式的高速电平移位器可以确保操作稳定性。

66.图1的实施方式配置成使得连接电路30的nmos晶体管q15和q16由反相的输入信号va和非反相的输入信号vb开关。

67.然而,连接电路30可以配置为使得nmos晶体管q15和q16的导通由图2中所示出的恒定电压vc来保持。图2与图1的不同之处仅在于连接电路30的配置,并且图2的其它配置与图1的配置相同,并且因此,将省略对其的重复描述。

68.换言之,图2的连接电路30被实施为配置为使得输出端子与输入电路20之间的连接由恒定电压vc保持。

69.恒定电压vc可以具有在输出驱动电压vddh与输入驱动电压vddl之间的电平,并且更具体地,可以具有在输出驱动电压vddh与输入驱动电压vddl之间的中等电平。可选地,根据制造商的意图,恒定电压vc可以具有输入驱动电压vddl。

70.图1和图2的实施方式被实施为使得钳位电路50包括在输入电路20中。然而,根据制造商的意图,本公开的实施方式可以被实施为使得从输入电路20中去除钳位电路50的配置,如图3中所示。图3与图2的不同之处仅在于,在输入电路20中去除钳位电路50的配置,并且图3的其它配置与图2的配置相同,并且因此,将省略对其的重复描述。

71.当诸如微控制单元的电子设备响应于具有逻辑电平的低电压范围的输入信号输出高电压范围的输出信号时,根据本公开的实施方式的如图1至图3中所示被实施的高速电平移位器可以防止出现故障并且能够高速操作以输出高电压范围的输出信号。

72.此外,在根据本公开的实施方式的如图1至图3中所示被实施的高速电平移位器中,可以防止对配置在输入电路中的低电压晶体管的损坏,并且可以保护低电压晶体管的漏极电压。因此,根据本公开的实施方式的高速电平移位器可以具有改进的可靠性并且确保操作稳定性。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。