具有集成的肖特基二极管的功率晶体管

背景技术:

1.sic(碳化硅)功率器件易受双极退化(bipolar degradation)影响,这导致归因于电子-空穴复合(recombination)所触发的缺陷生长的电阻随时间增加。这发生在功率器件的体二极管接通(turn on)时例如sic功率mosfet(金属氧化物半导体场效应晶体管)的双极操作期间。为了避免双极操作,肖特基二极管可以与功率mosfet器件并联使用。集成的肖特基二极管使能抑制双极接通的器件设计,并且此外,减少所需的总有源区域,因为二极管和功率mosfet共享相同的漂移区带(drift-zone)层,这对于具有大阻塞电压(例如,3.3 kv或6.5 kv或更高)的sic mosfet特别有吸引力,对于其,对静态损耗的漂移区带贡献是主导性的。然而,由于对于这种器件而言,漂移区带掺杂相当低,所以附加的jfet电阻在某种程度上损害了性能,因为与没有集成的肖特基二极管的功率mosfet相比,电流必须在p掺杂的屏蔽区下横向扩展到更大的间距(pitch)。

2.具有大阻塞电压的sic mosfet可以利用超结(sj)结构,其基本上减少了漂移区带电阻。sj结构的n型和p型导电柱的较大掺杂有助于减少jfet电阻。然而,基于sj的sic mosfet仍然遭受双极退化。通过使用外部sic肖特基二极管或具有低于sic的约2.7 v的内建电压的阈值电压的任何其他二极管,可以避免基于sj的sic mosfet的双极操作。该方法类似于具有轻掺杂(n-)的漂移区带层的任何其他标准sic mosfet。然而,使用诸如外部sic肖特基二极管之类的外部部件增加了封装复杂性和总成本。

3.因此,存在对于改进的基于sj的sic mosfet的需要,改进的基于sj的sic mosfet更免于双极退化。

技术实现要素:

4.根据半导体器件的实施例,半导体器件包括:集成在半导体衬底中的肖特基二极管和晶体管;以及超结结构,包括在晶体管的源极和本体下方以及在肖特基二极管的肖特基金属区下方在半导体衬底中形成的n型和p型半导体材料的交替区,其中,形成于晶体管的本体中的沟道区和肖特基金属区通过半导体衬底的n型半导体材料互连而不被超结结构的p型区中断,其中,互连沟道区和肖特基金属区的n型半导体材料包括超结结构的n型区。

5.根据半导体器件的另一实施例,半导体器件包括:形成在半导体衬底中的多个器件单元,每个器件单元包括晶体管结构和肖特基二极管结构;以及超结结构,包括形成在半导体衬底中的第一导电类型和第二导电类型的交替区,其中,对于每个晶体管结构,晶体管结构的沟道区和肖特基二极管结构的相邻一个的肖特基金属区通过第一导电类型的半导体材料互连而不被超结结构的第二导电类型的区中的任何区中断,第一导电类型的半导体材料包括超结结构的第一导电类型的区中的一个或多个。

6.本领域技术人员在阅读以下详细描述时并查看附图时将认识到附加特征和优势。

附图说明

7.附图中的元素不一定相对于彼此按照比例。相同的参考数字表示相应的类似部

分。各种所示实施例的特征可以组合,除非它们彼此排斥。在附图中描绘并在随后的描述中详细描述实施例。

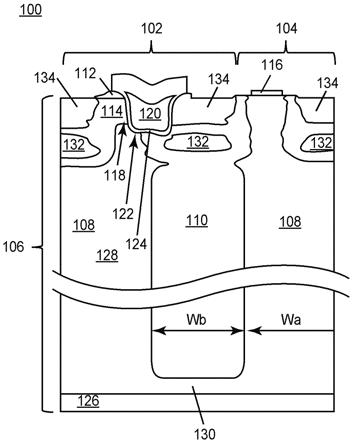

8.图1示出了具有集成在相同半导体衬底中的肖特基二极管结构和晶体管结构的半导体器件的实施例的部分截面图。

9.图2示出了具有集成在相同半导体衬底中的肖特基二极管结构和晶体管结构的半导体器件的另一实施例的部分截面图。

10.图3示出了具有集成在相同半导体衬底中的肖特基二极管结构和晶体管结构的半导体器件的另一实施例的部分截面图。

11.图4示出了具有集成在相同半导体衬底中的肖特基二极管结构和晶体管结构的半导体器件的另一实施例的部分截面图。

12.图5a至11c示出了半导体器件的另外的实施例并且其中器件单元是条形形状的部分平面图和相应的截面图。

13.图12a至19b示出了半导体器件的另外的实施例并且其中器件单元是二次型(quadratic)或六边形形状的部分平面图和相应的截面图。

具体实施方式

14.本文描述的是一种半导体器件,其具有集成在相同半导体衬底中的并联肖特基二极管和晶体管。晶体管可以具有平面栅极或沟槽栅极设计。在任一情况下,半导体器件还包括超结(sj)结构,该超结结构包括形成于半导体衬底中的n型和p型半导体材料的交替区。超结结构使得器件能够通过由相反导电类型(例如,对于n沟道器件的p型)的相邻定位的区平衡漂移区带中的附加电荷(例如,对于n沟道器件的n电荷)来阻塞其全电压,虑及在设置器件的导通状态电阻和阻塞电压中的至少两个自由度。

15.晶体管的沟道和肖特基二极管的肖特基金属区通过第一导电类型的半导体材料(电)互连,而不被超结结构的第二导电类型的区中的任何区中断。利用这种器件构造,与漂移区带不在晶体管和并联肖特基二极管之间共享的常规基于超结的器件相比,通过共享相同的漂移区带节省了总的有源区域。此外,晶体管的双极接通电压被移动到更大的电压,并且在双极操作中,在漂移区带的上半部中减少了空穴(对于n沟道器件)或电子(对于p沟道器件)的密度。随着超结结构的n型和p型区的增加的掺杂,由于漂移区带区中的电流扩散而导致的jfet(结fet)电阻减少了。

16.接下来更详细地描述的是具有集成在相同半导体衬底中的肖特基二极管结构和晶体管的基于超结的半导体器件的各种实施例。

17.图1示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件100的实施例的部分截面图。半导体衬底106可以是si(硅)衬底或宽带隙半导体衬底。这里使用的术语“宽带隙半导体”是指具有大于1.5 ev的带隙的任何半导体材料。例如,半导体衬底106可以包括sic(碳化硅)。在另一示例中,半导体衬底106可以包括gan(氮化镓)。诸如掺杂的金刚石(diamond)之类的其他宽带隙半导体材料可用于衬底106。在每种情况下,半导体衬底106可以包括基底半导体和在基底半导体上生长的一个或多个外延层。

18.半导体器件100还包括超结结构,该超结结构包括形成在半导体衬底106中的相反

(第一和第二)导电类型的交替(alternating)区108、110。在一个实施例中,半导体器件100是竖直功率mosfet,并且超结结构形成在晶体管结构102的源极112和本体114下方以及肖特基二极管结构104的肖特基金属区116下方。肖特基势垒(barrier)高度取决于用于形成整流(rectifying)肖特基势垒的金属和半导体材料的组合。例如,对于sic或gan衬底106,肖特基金属区116可包括pt、ti、ni、cr、mo、w、wsi和/或au。其他金属及/或金属合金组合可以用于肖特基金属区116。

19.图1中所示的竖直功率mosfet还包括沟道区118,当适当的电压施加到晶体管结构102的栅极电极120时,该沟道区118形成在晶体管结构102的本体114中。在图1中,栅极电极120设置在沟槽122中并且通过栅极电介质124与周围的半导体材料绝缘。竖直功率mosfet的漏极或集电极126设置在与源极112相对的半导体衬底106的一侧处。

20.当存在沟道区118时,电流通过器件100的漂移区带128在源极112和漏极/集电极126之间竖直地流动。晶体管结构102和肖特基二极管结构104并联地耦合,并且肖特基二极管结构104有助于抑制晶体管结构102的双极接通。在正常的正向操作中,电子从源极112流向漏极126。在体二极管操作中,电子从漏极126流向源极112。因此,电流主要由一种载流子(carrier)类型(空穴或电子)承载。

21.超结结构使得器件100能够阻塞其全电压。例如,可以通过生长一种导电类型的多个外延层并通过掩模(masked)注入步骤形成另一种导电类型的sj列(column)来形成超结结构。替代地,可对外延层进行低掺杂并且通过掩模来注入任一导电类型的sj列。形成超结结构的其他示例包括蚀刻沟槽的外延再生长和用p型epi填充蚀刻沟槽,或者使用沟道化离子注入来创建深柱。可以采用n掺杂和p掺杂sj条的宽度和掺杂浓度是相等的的对称的sj条设计。在每种情况下,与源极112相同导电类型的sj条(电)互连到晶体管沟道区118和二极管肖特基金属区116两者。

22.通过相反导电类型的相邻定位的超结区110实现了器件100的漂移区带128提供的附加电荷的平衡。漂移区带128可被认为是相同导电类型的超结区108的一部分。例如,在n沟道器件的情况下,超结结构的漂移区带128和第一区108是n型的,并且超结结构的第二区110是p型的。在p沟道器件的情况下,超结结构的漂移区带128和第一区108是p型的,并且超结结构的第二区110是n型的。

23.在任一情况下,晶体管结构102的沟道区118和肖特基二极管结构104的肖特基金属区116通过相同导电类型的半导体材料130(电)互连,而不被超结结构的相反掺杂的区110中断。该互连允许在晶体管结构102和肖特基二极管结构104之间的漂移区带128的共享,这导致总有源区域的减少并有助于避免双极操作。这对于高电压应用(例如,600v或以上)尤其有益。

24.在图1中,互连晶体管结构102的沟道区118和肖特基二极管结构104的肖特基金属区116的半导体衬底106的半导体材料130包括超结结构的第一区108。对于n沟道器件,超结结构的源极112、漏极/集电极126、漂移区带128、互连半导体材料130和第一区108将是n型的,并且超结结构的本体114和第二区110将是p型的。对于n沟道器件,肖特基金属区116是二极管104的阳极,并且半导体衬底106是阴极。对于p沟道器件,超结结构的源极112、漏极/集电极126、漂移区带128、互连半导体材料130和第一区108将是p型的,并且超结结构的本体114和第二区110将是n型的。对于p沟道器件,肖特基金属区116是二极管104的阴极,并且

半导体衬底106是阳极。

25.在任一情况下,在超结结构的相反掺杂的半导体区108、110之间提供电荷平衡,以虑及漂移区带128的较低电阻(较高掺杂)。例如,漂移区带128可以具有1e

16

/cm3至5e

17

/cm3的平均掺杂浓度。可以通过调整超结结构的第一和第二区108、110的尺寸、形状和/或掺杂浓度来实现电荷平衡。在图1中,sj柱设计被选择为是不对称的,其中,超结结构的第二区110比超结结构的第一区110(宽度“wa”)窄(宽度“wb”)。对于完美电荷平衡的器件以及因此的理想情况,设计不对称性可以通过超结结构的第一和第二区108、110(na、nb)的掺杂浓度的不相等加权来平衡,使得nb

·

wb = na

·

wa。如果例如归因于过程变化,电荷不平衡出现,则可以将器件100设计为具有某种程度的故意的电荷不平衡。例如,在特定的水平截面中,nb

·

wb可以等于na

·

wa*f,其中,f是在0.66至1.5,例如0.9至1.1的范围内的因子。因子f可以取决于进行水平切割的位置。然而,这仅是小的电荷不平衡,不同于顶部单元结构。这里,p掺杂远远超过n掺杂,例如可能超过到10倍(by a factor of 10)。

26.半导体器件100还可以包括与超结结构的第二区110相同导电类型的屏蔽区132和接触区134,即,用于n沟道器件的p型屏蔽区132和接触区134,或者用于p沟道器件的n型屏蔽区132和接触区134。屏蔽区132屏蔽栅极电介质124免受过度的电场电势。接触区134比屏蔽区132更重地掺杂,例如,以提供到诸如金属之类的接触的欧姆接触。如图1中所示,屏蔽区132和接触区134可与相同导电类型的超结结构的第二区110竖直对准。为了便于说明,没有示出与源极112、肖特基金属区116、栅极电极120、漏极/集电极126和接触区134的接触,但是可以使用任何标准的接触结构。

27.图2示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件200的另一实施例的部分截面图。图2中所示的实施例类似于图1中所示的实施例,然而,不同之处在于,晶体管结构102是平面栅极晶体管,具有设置在半导体衬底106上方并通过栅极电介质124与半导体衬底106绝缘的栅极电极120。电流从源极112通过形成在本体114中的沟道区118水平地流向与源极112相同的导电类型的电流扩散区129,并且然后通过漂移区带128竖直地流向漏极/集电极126。

28.图3示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件300的另一实施例的部分截面图。图3中所示的实施例与图1中所示的实施例相似。然而,不同之处在于sj柱设计在半导体衬底106的下部中是对称的,但是超结结构的第二区110在衬底106的上部中逐渐变细(taper off),从而将第二sj区110连接到屏蔽区132。也就是说,超结结构的第二区110的宽度在竖直(电流流动)方向上变化。超结结构的第二区110具有更靠近屏蔽区132的较小的宽度w1,以及在半导体衬底106中更深的较大的宽度w2。在超结结构的第二区110的较宽部分w2处,超结结构的第一和第二区108、110可具有相同的宽度。无论超结结构的第一和第二区108、110的形状如何,都在第一和第二区108、110之间维持电荷平衡,以例如通过调整超结结构的第一和第二区108、110的掺杂浓度来确保充分的阻塞。

29.图4示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件400的另一实施例的部分截面图。图4中所示的实施例与图2中所示的实施例相似,相似之处在于晶体管是平面栅极器件。然而,与图3中所示的实施例类似,超结结构的第二区110的宽度在竖直(电流流动)方向上变化。如上面结合图3所解释的,超结结构

的第一和第二区108、110在超结结构的第二区110的较宽部分w2处可具有相同的宽度。

30.图1至图4中所示的半导体器件100、200、300、400可以包括形成在半导体衬底106中的多个器件单元,其中,图1至图4中的每个示出了单个器件单元的一个晶体管结构102和相邻的肖特基二极管结构104。器件单元可以被复制10次、100次、1000次或甚至更多次,以形成相应的晶体管和与晶体管并联的肖特基二极管。晶体管可以是如上所述的功率mosfet、igbt(绝缘栅极双极晶体管)、jfet等。器件单元可以是条形形状、二次型形状、六边形形状等。接下来描述的是各种单元类型的附加实施例,其中,在每种情况下并且对于每个晶体管结构102,晶体管结构的沟道区118和相邻肖特基二极管结构104的肖特基金属区116通过第一导电类型的半导体材料130互连,而不被超结结构的第二导电类型的区110中的任何区中断。在以下实施例中,对于n沟道器件,第一导电是n型的并且第二导电类型是p型的,并且对于p沟道器件,第一导电是p型的并且第二导电类型是n型的。

31.图5a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件500的另一实施例的部分俯视平面图。晶体管结构102和肖特基二极管结构104是相同器件单元的部分,并且半导体器件500具有10个、100个、1000个或甚至更多个的器件单元。图5a中示出了单个器件单元用于每个图示。根据该实施例,条形形状晶体管结构102的沟道区118和不止一个肖特基二极管结构104的肖特基金属区116在相同的半导体台面内相间错杂(interdigitate),并且超结结构的相反掺杂的半导体区108、110平行于(图5a中的y方向) 栅极沟槽122伸展。图5a至5d中所示的单元布局允许晶体管结构102和肖特基二极管结构104共享用于导电的第一导电类型的相同sj条/列108,而同时允许实现窄sj间距。

32.图5a中的俯视平面图的部分将超结结构的相反掺杂的半导体区108、110示为虚线框,因为它们被覆盖并且因此否则将完全在图5a中的视图之外。图5b是沿图5a中标记为“1”的线截取的半导体器件500的截面图。图5c是沿图5a中标记为“2”和“4”的线截取的半导体器件500的截面图。图5d是沿着图5a中标记为“3”的线截取的半导体器件500的截面图。

33.根据图5a至5d中所示的实施例,晶体管结构102是条形形状的,并且超结结构的第一导电类型的区108也是条形形状的。超结结构的第一导电类型的条形形状区108在图5a中的y方向上与条形形状晶体管结构102平行地伸展。超结结构的第二导电类型的区110也可以是条形形状的。

34.对于每个条形形状晶体管结构102,条形形状晶体管结构102的源极区112沿着条形形状晶体管结构104的长度(图5a中的y方向)被肖特基二极管结构104中的至少一个中断,并且超结结构的第一导电类型的条形形状区108中的单个一个设置在条形形状晶体管结构102的源极区112下方,并且将条形形状晶体管结构102的沟道区118和包括在相同器件单元中的每个肖特基二极管结构的肖特基金属区116互连,而不被超结结构的第二导电类型的区110中的任何区中断。

35.图6a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件600的另一实施例的部分俯视平面图。图6b是沿图6a中标记为“1”的线截取的半导体器件600的截面图。图6c是沿图6a中标记为“2”和“4”的线截取的半导体器件600的截面图。图6d是沿图6a中标记为“3”的线截取的半导体器件600的截面图。图6e是沿图6a中标记为“5”的线截取的半导体器件600的截面图。

36.图6a至6e中所示的实施例与图5a至5d中所示的实施例相似。然而,不同的是,源极区112沿着沟槽122的两个侧壁而不是仅沿着一个侧壁延伸,从而每个器件单元提供更高的电流。而且,条形形状晶体管结构102的源极区112可以具有比肖特基二极管结构104的肖特基金属区116更大的沿着条形形状晶体管结构102的纵向延伸(图6a中的x方向)测量的尺寸。

37.图7a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件700的另一实施例的部分俯视平面图。图7b是沿图7a中标记为“1”的线截取的半导体器件700的截面图。

38.图7a和7b中所示的实施例与图5a至5d中所示的实施例相似。然而,不同的是,对于每个条形形状晶体管结构102:肖特基二极管结构104中的至少一个横向地邻接条形形状晶体管结构102,而不是中断源极区112。因此,源极区112沿着条形形状晶体管结构102的长度(图7a中的y方向)不中断地伸展,并且通过栅极沟槽122与每个横向邻接的肖特基二极管结构104的肖特基金属区116分离。

39.超结结构的第二导电类型的条形形状区110中的第一个110'插入在源极区112与每个横向邻接肖特基二极管结构104的肖特基金属区116之间。超结结构的第一导电类型的条形形状区108中的第一个108'设置在源极区112下方。超结结构的第一导电类型的条形形状区108的第二个108”设置在每个横向邻接肖特基二极管结构104的肖特基金属区116下方。进一步根据图7a和7b中所示的实施例,超结结构的第一导电类型的条形形状区108中的第一个108'和第二个108”经由第一导电类型的互连区130(电)互连条形形状晶体管结构102的沟道区118和每个横向邻接的肖特基二极管结构104的肖特基金属区116,而不被超结结构的第二导电类型的区110中的第一个110'中断。

40.图8a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件800的另一实施例的部分俯视平面图。图8b是沿图8a中标记为“1”的线截取的半导体器件800的截面图。图8c是沿图8a中标记为“2”的线截取的半导体器件800的截面图。

41.图8a至8c中所示的实施例与图5a至5d中所示的实施例相似。然而,不同的是,超结结构的第一导电类型的条形形状区108横断(transverse)(图8a中的x方向)伸展,例如垂直于条形形状晶体管结构104伸展。超结结构的第二导电类型的区110也可以是条形形状的并且横断于(图8a中的x方向)条形形状晶体管结构104伸展。根据该实施例,晶体管沟道区118和每个横向邻接的肖特基二极管结构104的肖特基金属区116之间的接触密度被限制为沟道区118和每个肖特基金属区116的仅一部分。

42.进一步根据图8a至8c中所示的实施例,并且对于每个条形形状晶体管结构102:至少一个肖特基二极管结构104横向邻接条形形状晶体管结构102,使得源极区112沿着条形形状晶体管结构102的长度(图8a中的y方向)不中断地伸展,并且通过栅极沟槽122与每个横向邻接的肖特基二极管结构104的肖特基金属区116分离。超结结构的第一导电类型的条形形状区108经由第一导电类型的互连区130互连条形形状晶体管结构102的沟道区118和每个横向邻接的肖特基二极管结构104的肖特基金属区116,而不被超结结构的第二导电类型的区110中断。

43.图9a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管

结构104的半导体器件900的另一实施例的部分俯视平面图。图9b是沿图9a中标记为“1”的线截取的半导体器件900的截面图。图9c是沿图9a中标记为“2”的线截取的半导体器件900的截面图。

44.图9a至9c中所示的实施例与图8a至8c中所示的实施例相似。然而,不同的是,并且为了避免沟道密度的损失,使用棋盘设计而不是条形设计来实现晶体管结构102的源极区112。源极区112沿纵向延伸(图9a中的y方向)被相反导电类型的半导体材料132、134中断,其中,形成超结结构的第二导电类型的条形区110。因此,源极区112垂直(图9a中的x方向)于栅极沟槽122的纵向延伸而延长(prolong),使得两个沟槽侧壁都用于沟道区118。接触区134也垂直于沟槽方向加宽并且在该方向上中断,类似于源极区112。为了充分屏蔽栅极电介质124,屏蔽区132沿超结结构的第二导电类型的整个条形区110延伸,如图9c中所示。因此,栅极电介质124不仅如图8a到8c中被屏蔽于侧面而且被屏蔽于顶部和底部。

45.对于根据图9a到9c中所示的实施例实现的每个条形形状晶体管结构104:源极区112沿着栅极沟槽122的相对侧设置。超结结构的第一导电类型的条形形状区109设置在条形形状晶体管结构104的源极区112下方,并且经由第一导电类型的互连区130将条形形状晶体管结构102的沟道区118和相同器件单元的每个肖特基二极管结构104的肖特基金属区116互连,而不被超结结构的第二导电类型的区110中的任何区中断。进一步根据该实施例,超结结构的第二导电类型的区110延伸至相对于条形形状晶体管结构102的源极区112的半导体衬底106的一侧处的半导体器件900的漏极/集电极126。

46.图10a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件1000的另一实施例的部分俯视平面图。图10b是沿图10a中标记为“1”的线截取的半导体器件1000的截面图。图10c是沿图10a中标记为“2”的线截取的半导体器件1000的截面图。

47.图10a至10c中所示的实施例与图8a至8c中所示的实施例相似。然而,不同的是,沿超结结构的第一导电类型的条形形状区108的长度(图10a中的x方向),超结结构的第一导电类型的条形形状区108中的相邻的条形形状区通过第一导电类型的本体连接区130'互连,本体连接区130'在横断于超结结构的第一导电类型的条形形状区108的纵向延伸的方向上(图10a中的y方向)延伸穿过超结结构的第二导电类型的区110。第一导电类型的本体连接区130'与条形形状晶体管结构102的本体区114竖直接触,从而允许沟道电流到达超结结构的第一导电类型的条形形状区108。沟道电流具有图10c的横截面“2”中的竖直分量以及图10b的横截面“1”中的横向或水平分量。此外,如图10c中所示,超结结构的第二导电类型的区110是条形形状,并且比第一导电类型的本体连接区130'更深地延伸到半导体衬底106中,并且不被本体连接区130'的终端点(termination point)1002下方的第一导电类型的本体连接区130'中断。

48.图11a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件1100的另一实施例的部分俯视平面图。图11b是沿图11a中标记为“1”的线截取的半导体器件1100的截面图。图11c是沿图11a中标记为“2”的线截取的半导体器件1100的截面图。

49.图11a至11c中所示的实施例与图10a至10c中所示的实施例相似。然而,不同的是,第一导电类型的本体连接区130'比超结结构的第二导电类型的区110更深地延伸到半导体

衬底106中,使得超结结构的第二导电类型的每个区110沿着超结结构的第一导电类型的条形形状区108的纵向延伸(图11a中的x方向)被分割成多个横向间隔开的柱。因此,超结结构的第二导电类型的区110被相反导电类型的本体连接区130'中断并且因此具有比条形形状更像柱的形状。该设计的附加优势是与后一种设计相比,不需要牺牲肖特基接触区域。

50.图8a-8c和11a-11c的实施例可以被组合,使得直接在沟道112和肖特基金属区118下方,超结结构的第二导电类型的区110被中断。在该情况下,没有沟道和二极管区域被牺牲。同时,第二导电类型的柱状区110仅被提供在半导体衬底106的上部中,但是衬底106的较深部分可以利用第二导电类型的完整条,例如,如图10a-10c中所示。

51.根据图5a至11c中所示的实施例,超结结构的第一导电类型的区108和晶体管结构102中的每个都是条形形状。超结结构的第二导电类型的区110也可以是条形形状的,如图5a至图11c中所示。

52.下面描述的是各种单元类型的另外的实施例,其中,在每种情况下,晶体管结构102具有二次型或六边形形状,并且肖特基二极管结构104的肖特基金属区116设置在器件单元的中心或外围。在以下实施例中,对于n沟道器件,第一导电类型是n型并且第二导电类型是p型,并且对于p沟道器件,第一导电类型是p型并且第二导电类型是n型。

53.图12a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件1200的另一实施例的局部俯视平面图。晶体管结构102和肖特基二极管结构104是相同器件单元的部分,并且半导体器件1200具有10个、100个、1000个或更多个器件单元。图12a中示出了单个器件单元用于每个说明。

54.仅为了便于说明,图12a中的俯视平面图示出了与器件单元并排的超结结构的相反掺杂的半导体区108、110。实际上,超结结构的相反掺杂的半导体区108、110形成在晶体管结构102的源极和本体区112、114下方和肖特基二极管结构104的肖特基金属区116下方的半导体衬底106中。图12b是沿图12a中标记为“1”的线截取的半导体器件1200的截面图。

55.根据图12a和12b中所示的实施例,所示器件单元的晶体管结构102具有二次型形状,并且形成器件单元的部分的肖特基二极管结构104的肖特基金属区116设置在器件单元的中心处。在二次型单元中,在每个栅极沟槽的顶部处提供到栅极电极120的连接。为了便于说明,在图12和12b中没有示出该连接。

56.图13a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件1300的另一实施例的部分俯视平面图。图13b是沿图13a中标记为“1”的线截取的半导体器件1300的截面图。

57.图13a和13b中所示的实施例与图12a和12b中所示的实施例相似。然而,不同的是,超结结构的第二导电类型的区110设置在器件单元的中心处。栅极沟槽122限定了器件单元的外围。如果需要较大的二极管电流密度,则肖特基金属区116可位于器件单元外部。

58.图14a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件1400的另一实施例的部分俯视平面图。图14b是沿图14a中标记为“1”的线截取的半导体器件1400的截面图。

59.图14a和14b中所示的实施例与图12a和12b中所示的实施例相似。然而,不同的是,超结结构的相反掺杂的半导体区108、110是条形形状的。

60.图15a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管

结构104的半导体器件1500的另一实施例的部分俯视平面图。图15b是沿着图15a中标记为“1”的线截取的半导体器件1500的截面图。

61.图15a和15b中所示的实施例与图13a和13b中所示的实施例相似。然而,不同的是,形成器件单元的部分的肖特基二极管结构104的肖特基金属区116设置在器件单元的外围处而不是单元中心处。源极区112在图15a和15b中被示出为是沿着栅极沟槽122的内侧壁和外侧壁两者形成的,但是替代地也可以沿着栅极沟槽122的仅内侧壁或仅外侧壁设置。

62.图16a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件1600的另一实施例的部分俯视平面图。图16b是沿着图16a中标记为“1”的线截取的半导体器件1600的截面图。

63.图16a和16b中所示的实施例与图12a和12b中所示的实施例相似。然而,不同的是,包括在器件单元中的晶体管结构102是平面栅极器件,具有设置在半导体衬底106上方并通过栅极电介质124与半导体衬底106绝缘的栅极电极120。如上面结合图2和3所解释的,电流通过形成在本体114中的沟道区118从源极112向与源极112相同导电类型的电流扩散区129水平流动,并且然后通过漂移区带128向漏极/集电极126竖直流动。在图16a和16b中,栅极电介质124被示出为在电流扩展区129的部分之上横向(水平)延伸并且在到达相邻接触区134之前终止。然而,栅极电介质124可以在电流扩展区129之上以及在相邻接触区134的全部或部分之上横向延伸。

64.图17a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件1700的另一实施例的部分俯视平面图。图17b是沿着图17a中标记为“1”的线截取的半导体器件1700的截面图。

65.图17a和17b中所示的实施例与图16a和16b中所示的实施例相似。然而,不同的是,源极区112和电流扩展区129的位置是相反的。因此,源极区112被设置成比电流扩展区129更靠近器件单元的外围。电流流的水平分量向内朝向器件单元的中心去往电流扩展区129,并且然后通过漂移区带128竖直去往漏极/集电极126。

66.图18a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件1800的另一实施例的部分俯视平面图。图18b是沿图18a中标记为“1”的线截取的半导体器件1800的截面图。

67.图18a和18b中所示的实施例与图16a和16b中所示的实施例相似。然而,不同的是,形成器件单元的部分的肖特基二极管结构104的肖特基金属区116设置在器件单元的周边而不是单元中心处。超结结构的第二导电类型的区110也设置在器件单元的中心处。在图17a-17b和18a-18b中,示出了栅极电介质124在电流扩展区129的部分之上横向(水平)延伸并在到达相邻肖特基金属区116之前终止。然而,栅极电介质124可以在电流扩展区129之上以及在相邻肖特基金属区116的全部或部分之上横向延伸。在该情况下,电介质和金属共享相同的n区129而在之间没有p区。然而,小的p区136可以靠近将栅极电介质124和相邻肖特基金属区116分离的表面形成。

68.对于图12a至18b中所示的每个二次型单元实施例,超结结构的第二导电类型的区110可具有均匀的宽度或随深度改变的宽度。例如,超结结构的第二导电类型的区110可以在朝向漏极/集电极126的方向上加宽,例如类似于图3和4中所示的。另外或作为替代,屏蔽区132的深度可以适于栅极电介质124的最佳屏蔽。另外或作为替代,任何二次型单元布局

可以替代地是六边形形状。

69.图19a示出了具有集成在相同半导体衬底106中的晶体管结构102和肖特基二极管结构104的半导体器件1900的另一实施例的局部俯视平面图。图19b是沿图19a中标记为“1”的线截取的半导体器件1900的截面图。

70.图19a和19b中所示的实施例与图12a和12b中所示的实施例相似。然而,不同的是,包括在器件单元中的晶体管结构102具有六边形形状而不是二次型形状。

71.尽管本公开不限于此,但以下编号的示例展示了本公开的一个或多个方面。

72.示例1.一种半导体器件,包括:集成在半导体衬底中的晶体管和肖特基二极管;以及超结结构,包括在晶体管的源极和本体下方以及在肖特基二极管的肖特基金属区下方在半导体衬底中形成的n型和p型半导体材料的交替区,其中,形成在晶体管的本体中的沟道区和肖特基金属区通过半导体衬底的n型半导体材料互连而不被超结结构的p型区中断,其中,互连沟道区和肖特基金属区的n型半导体材料包括超结结构的n型区。

73.示例2.示例1的半导体器件,其中,半导体衬底是sic衬底。

74.示例3.示例1或2的半导体器件,其中,晶体管是具有设置在形成在半导体衬底中的多个沟槽中的栅极电极的沟槽栅极晶体管。

75.示例4.示例1或2中的任何示例的半导体器件,其中,晶体管是具有设置在半导体衬底上方并与半导体衬底绝缘的栅极电极的平面栅极晶体管。

76.示例5.一种半导体器件,包括:多个器件单元,形成在半导体衬底中,每个器件单元包括晶体管结构和肖特基二极管结构;以及超结结构,包括形成在半导体衬底中的第一导电类型和第二导电类型的交替区,其中,对于每个晶体管结构,晶体管结构的沟道区和肖特基二极管结构中的相邻一个的肖特基金属区通过第一导电类型的半导体材料互连而不被超结结构的第二导电类型的区中的任何区中断,第一导电类型的半导体材料包括超结结构的第一导电类型的区中的一个或多个。

77.示例6.示例5的半导体器件,其中,晶体管结构是条形形状的,并且其中,超结结构的第一导电类型的区是条形形状的。

78.示例7.示例6的半导体器件,其中,超结结构的第一导电类型的条形形状区与条形形状晶体管结构平行地伸展。

79.示例8.示例7的半导体器件,其中,对于每个条形形状晶体管结构:条形形状晶体管结构的源极区被沿着条形形状晶体管结构的长度的肖特基二极管结构中的至少一个中断;并且超结结构的第一导电类型的条形形状区中的单个一个设置在条形形状晶体管结构的源极区下方,并且互连条形形状晶体管结构的沟道区和至少一个肖特基二极管结构的肖特基金属区,而不被超结结构的第二导电类型的区中的任何区中断。

80.示例9.示例7的半导体器件,其中,对于每个条形形状晶体管结构:肖特基二极管结构中的至少一个横向邻接条形形状晶体管结构;条形形状晶体管结构的源极区沿着条形形状晶体管结构的长度不中断伸展,并且通过栅极沟槽与至少一个横向邻接的肖特基二极管结构的肖特基金属区分离;超结结构的第二导电类型的条形形状区中的第一个被插入在源极区与至少一个横向邻接肖特基二极管结构的肖特基金属区之间;超结结构的第一导电类型的条形形状区中的第一个设置在源极区下方;超结结构的第一导电类型的条形形状区中的第二个设置在至少一个横向邻接肖特基二极管结构的肖特基金属区下方;并且超结结

构的第一导电类型的条形形状区中的第一个和第二个互连条形形状晶体管结构的沟道区和至少一个横向邻接肖特基二极管结构的肖特基金属区,而不被超结结构的第二导电类型的区中的第一个中断。

81.示例10.示例9的半导体器件,其中,超结结构的第二导电类型的区中的第一个是条形形状的。

82.示例11.示例6至10中的任何示例的半导体器件,其中,超结结构的第一导电类型的条形形状区横断于条形形状晶体管结构而伸展。

83.示例12.示例11的半导体器件,其中,对于每个条形形状晶体管结构:肖特基二极管结构中的至少一个横向邻接条形形状晶体管结构;条形形状晶体管结构的源极区沿着条形形状晶体管结构的长度不中断伸展,并且通过栅极沟槽与至少一个横向邻接的肖特基二极管结构的肖特基金属区分离;并且超结结构的第一导电类型的条形形状区互连条形形状晶体管结构的沟道区和至少一个横向邻接肖特基二极管结构的肖特基金属区,而不被超结结构的第二导电类型的区中断。

84.示例13.示例12的半导体器件,其中,超结结构的第二导电类型的区是条形形状的。

85.示例14.示例12或13的半导体器件,其中,沿着超结结构的第一导电类型的条形形状区的长度,超结结构的第一导电类型的条形形状区中的相邻的区通过第一导电类型的连接区而互连,第一导电类型的连接区在横断于超结结构的第一导电类型的条形形状区的纵向延伸的方向上延伸穿过超结结构的第二导电类型的区,并且其中,第一导电类型的连接区与条形形状晶体管结构的本体区竖直接触。

86.示例15.示例14的半导体器件,其中,超结结构的第二导电类型的区是条形形状的,并且其中,超结结构的第二导电类型的条形形状区比第一导电类型的连接区更深地延伸到半导体衬底中,并且不被第一导电类型的连接区的终端点下方的第一导电类型的连接区中断。

87.示例16.示例14或15的半导体器件,其中,第一导电类型的连接区比超结结构的第二导电类型的区更深地延伸到半导体衬底中,使得超结结构的第二导电类型的每个区沿着超结结构的第一导电类型的条形形状区的纵向延伸被分割成多个横向间隔开的柱。

88.示例17.示例11至16中的任何示例的半导体器件,其中,对于每个条形形状晶体管结构:条形形状晶体管结构的源极区沿着栅极沟槽的相对侧设置;并且超结结构的第一导电类型的条形形状区设置在条形形状晶体管结构的源极区下方,并且互连条形形状晶体管结构的沟道区和至少一个肖特基二极管结构的肖特基金属区,而不被超结结构的第二导电类型的区中的任何区中断。

89.示例18.示例17的半导体器件,其中,超结结构的第二导电类型的区延伸到在相对于条形形状晶体管结构的源极区的半导体衬底的一侧处的半导体器件的漏极或集电极。

90.示例19.示例6至18中的任何示例的半导体器件,其中,条形形状晶体管结构的源极区具有比肖特基二极管结构的肖特基金属区更大的沿着条形形状晶体管结构的纵向延伸测量的尺寸。

91.示例20.示例5的半导体器件,其中,器件单元具有二次型或六边形形状。

92.诸如“第一”、“第二”以及诸如此类的术语用于描述各种元素、区、部分等,并且也

不旨在是限制性的。相同的术语贯穿说明书指代相同的元素。

93.如本文中所用的,术语“具有”、“含有”、“包含”、“包括”以及诸如此类是开放式术语,其指示了所述元素或特征的存在,但不排除附加的元素或特征。冠词“一”、“一个”和“该”旨在包括复数以及单数,除非上下文另有明确指示。

94.尽管在本文中已经示出和描述了具体实施例,但是本领域普通技术人员将理解,在不偏离本发明的范围的情况下,多种替代和/或等同实现可以替代所示出和描述的具体实施例。本技术旨在覆盖本文中讨论的具体实施例的任何修改或变化。因此,本发明旨在仅由权利要求书和其等同物来限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。