射频切换电路和多级缓冲器

1.相关申请的交叉引用

2.本技术要求于2020年5月28日提交的、标题为“用于射频开关的偏置的多级缓冲器”的美国临时专利申请no.62/704,795的优先权,其全部内容通过引用合并于此。

技术领域

3.本公开的实施方案涉及电子系统,更具体地,涉及射频开关的偏置。

背景技术:

4.射频(rf)通信系统可以包括用于各种目的的rf开关。

5.在一个示例中,rf通信系统可以包括使用rf开关实现的天线开关模块(asm)。另外,天线开关模块可用于将天线电连接到系统的特定发送或接收路径,从而允许多个组件访问天线。在另一示例中,rf通信系统可以包括数字步进衰减器(dsa),并且dsa可以包括被接通或断开以控制由dsa提供的衰减量的rf开关。

技术实现要素:

6.根据本公开的一个方面,提供了一种射频切换电路,该射频切换电路包括:包括栅极的场效应晶体管(fet)的开关;阻抗;和多级缓冲器,具有通过所述阻抗连接到fet的栅极的输出端子,其中所述多级缓冲器包括:第一反相器,被配置为接收第一时钟信号相位,并由第一电源电压和小于所述第一电源电压的第二电源电压供电;第二反相器,被配置为接收第二时钟信号相位,并由所述第二电源电压和小于所述第二电源电压的第三电源电压供电;第三反相器,被配置为接收第三时钟信号相位,并由所述第一反相器的输出和所述第二反相器的输出供电;和第一输出开关,连接在所述输出端子和所述第三反相器的输出之间。

7.根据一个实施例,所述多级缓冲器被配置为响应于控制信号从截止状态到导通状态的转变而产生开关控制电压的导通脉冲。

8.根据一个实施例,所述多级缓冲器被配置为通过在所述导通脉冲的持续时间内用所述第一电源电压控制所述开关控制电压来产生所述导通脉冲,然后通过用所述第二电源电压控制所述开关控制电压来达到稳定状态导通电压。

9.根据一个实施例,所述第一输出开关是具有由所述第二反相器的输出控制的栅极的p型fet。

10.根据一个实施例,所述多级缓冲器还包括:第四反相器,被配置为接收第四时钟信号相位,并由所述第二电源电压和所述第三电源电压供电;以及第二输出开关,连接到所述输出端子,并由所述第四反相器的输出控制。

11.根据一个实施例,所述多级缓冲器还包括:第五反相器,被配置为接收第五时钟信号相位,并由所述第三电源电压和小于所述第三电源电压的第四电源电压供电;以及第六反相器,被配置为接收第六时钟信号相位,并由所述第四反相器的输出和所述第五反相器的输出供电,其中所述第六反相器的输出通过所述第二输出开关连接到所述输出端子。

12.根据一个实施例,所述第二输出开关是具有由所述第四反相器的输出控制的栅极的n型fet。

13.根据一个实施例,所述多级缓冲器被配置为响应于所述控制信号从导通状态到截止状态的转变而产生开关控制电压的截止脉冲。

14.根据一个实施例,所述多级缓冲器被配置为通过在所述截止脉冲的持续时间内用第四电源电压控制所述开关控制电压来产生所述截止脉冲,然后通过用所述第三电源电压控制所述开关控制电压来达到稳定状态截止电压,其中所述第四电源电压小于所述第三电源电压。

15.根据一个实施例,所述多级缓冲器还包括:第一电平移位器,被配置为驱动所述第一反相器的输入;以及第二电平移位器,被配置为驱动所述第五反相器的输入。

16.根据一个实施例,使用多个fet来实现所述第一反相器、所述第二反相器、所述第三反相器和所述第一输出开关。

17.根据一个实施例,所述第一电源电压和所述第三电源电压之间的电压差超过所述多个fet的额定电压。

18.根据一个实施例,所述fet的开关是n型金属氧化物半导体nmos 开关或p型金属氧化物半导体pmos开关。

19.根据一个实施例,所述阻抗包括栅极电阻器。

20.根据一个实施例,所述多级缓冲器还包括定时电路,所述定时电路被配置为接收控制信号,并产生包括所述第一时钟信号相位、所述第二时钟信号相位和所述第三时钟信号相位的多个时钟信号相位。

21.根据本公开的另一方面,提供了一种多级缓冲器,该多级缓冲器用于驱动晶体管栅极,该多级缓冲器包括:输出端子;第一反相器,被配置为接收第一时钟信号相位,并由第一电源电压和小于所述第一电源电压的第二电源电压供电;第二反相器,被配置为接收第二时钟信号相位,并由所述第二电源电压和小于所述第二电源电压的第三电源电压供电;第三反相器,被配置为接收第三时钟信号相位,并由所述第一反相器的输出和所述第二反相器的输出供电;和第一输出开关,连接在所述输出端子和所述第三反相器的输出之间。

22.根据一个实施例,所述第一输出开关是具有由所述第二反相器的输出控制的栅极的p型fet。

23.根据一个实施例,所述多级缓冲器还包括:第四反相器,被配置为接收第四时钟信号相位,并由所述第二电源电压和所述第三电源电压供电;以及第二输出开关,连接到所述输出端子,并由所述第四反相器的输出控制。

24.根据一个实施例,所述多级缓冲器还包括:第五反相器,被配置为接收第五时钟信号相位,并由所述第三电源电压和小于所述第三电源电压的第四电源电压供电,以及第六反相器,被配置为接收第六时钟信号相位,并由所述第四反相器的输出和所述第五反相器的输出供电,其中所述第六反相器的输出通过所述第二输出开关连接到所述输出端子。

附图说明

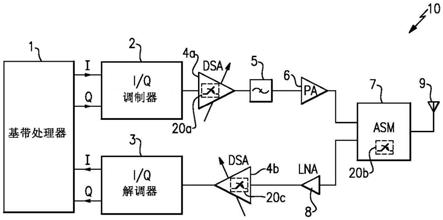

25.图1是根据本文的教导的可以包括一个或多个rf切换电路的射频 (rf)系统的一个示例的示意图。

26.图2a是根据一个实施例的rf切换电路的电路图。

27.图2b是图2a的rf切换电路的时序图的一个例子。

28.图2c是用于rf切换电路中的rf开关的另一示例。

29.图3a是用于驱动rf开关的多级缓冲器的一个实施例的示意图。

30.图3b是用于驱动rf开关的多级缓冲器的另一实施例的示意图。

31.图4a是用于驱动rf开关的多级缓冲器的另一实施例的示意图。

32.图4b是描述图4a的多级缓冲器的操作的一个示例的表。

33.图5a是处于第一操作状态的图4a的多级缓冲器的示意图。

34.图5b是处于第二操作状态的图4a的多级缓冲器的示意图。

35.图5c是处于第三操作状态的图4a的多级缓冲器的示意图。

36.图5d是处于第四操作状态的图4a的多级缓冲器的示意图。

37.图6是根据一个实施例的用于多级缓冲器的时序图。

38.图7是根据一个实施例的rf切换电路的时序图。

具体实施方式

39.实施例的以下详细描述呈现了本公开的特定实施例的各种描述。在该描述中,参考附图,其中相似的附图标记可以指示相同或功能相似的元件。将理解的是,附图中示出的元件不必按比例绘制。此外,将理解的是,某些实施例可以包括比附图中示出的元件更多的元件和/或附图中示出的元件的子集。此外,一些实施例可以结合来自两个或更多个附图的特征的任何合适的组合。

40.射频(rf)通信系统通过无线发送和接收rf信号进行通信。这样的 rf通信系统可以包括一个或多个rf开关,以提供对rf信号的路由,组件或电路之间的连接性的控制,和/或提供各种其他开关功能。具有一个或多个rf开关的rf通信系统的示例包括但不限于基站,移动设备(例如,智能手机或手机)、膝上型计算机、平板电脑、物联网(iot)设备和/或可穿戴电子产品。

41.某些rf切换电路包括一个场效应晶体管(fet)开关和一个开关偏置电路,该偏置电路控制开关的栅极电压,从而改变开关的沟道阻抗并调节开关的电导率。例如,开关偏置电路可以将栅极电压控制到第一电平以关断fet开关,使得沟道阻抗高并且rf信号不通过fet开关。另外,开关偏置电路可以将栅极电压控制到第二电平以导通fet开关,以使沟道阻抗低并且rf信号通过fet开关。因此,开关偏置电路用于打开或关闭fet 开关,以控制rf信号的通过。

42.rf信号可以通过fet开关的寄生栅极-漏极电容(cgd)和/或寄生栅极-源极电容(cgs)耦合到fet开关的栅极。为了提供隔离,可以在开关偏置电路的输出和fet开关的栅极之间包括栅极电阻器。

43.栅极电阻器的大电阻值可带来多种好处,例如低损耗和/或低截止频率以提供宽带操作。然而,使栅极电阻器的电阻值变大也不利地延长了fet 开关的接通时间和断开时间。例如,当开关偏置电路改变fet开关的栅极电压时,基于由栅极电阻器和fet开关的栅极电容引起的电阻器(rc) 时间常数,会有不希望的开关延迟。开关的延迟导致开关的接通时间和断开时间的增加。

44.因此,尽管以高电阻实现栅极电阻器具有许多好处,但它也会降低fet 开关的开关性能。

45.为了实现短切换时间,rf系统可以包括:rf开关,其具有控制rf 开关的阻抗的控制输入;多级缓冲器,被配置为接收用于选择性地激活rf 开关的控制信号;以及电阻器,其被电连接在多级缓冲器的输出和rf开关的控制输入之间。另外,多级缓冲器在输出处产生开关控制电压,并且响应于控制信号的转变而对开关控制电压进行脉冲化,从而缩短了切换rf 开关的延迟。

46.因此,不是直接将开关控制电压从导通电压转换为截止电压,反之亦然,而是在将开关控制电压控制为稳态电压电平之前对其进行脉冲化。通过以这种方式对开关控制电压施加脉冲,可以更快地在rf开关的控制输入端进行充电或放电,从而缩短了rf开关的开关延迟。

47.本文提供了用于驱动rf开关的多级缓冲器的实施例。

48.在某些实施方式中,多级缓冲器不仅用稳态开关导通电压(例如,高电源电压)和稳态开关截止电压(例如,低电源电压或接地电压)来控制 rf开关,还用高于稳态开关导通电压的高电压和低于稳态开关截止电压的低电压来控制rf开关。

49.例如,当打开n型场效应晶体管(nfet)开关时,多级缓冲器使用高压控制nfet开关的栅极电压一段时间,然后通过稳态开关导通电压控制栅极电压。另外,当关断nfet开关时,多级缓冲器使用低电压来控制 nfet开关的栅极电压一段时间,然后利用稳态开关截止电压来控制栅极电压。结果是加快了nfet开关的导通和关断时间。

50.在某些实施方式中,脉冲的电压电平超过开关可以可靠地工作的击穿电压,例如,超过fet开关的最大栅-源电压。因此,如果将脉冲电压电平用于将开关控制在稳态下,则出于可靠性考虑,它将损坏开关。然而,通过经由电阻器或其他阻抗施加脉冲,直接在开关的控制输入上的电压保持在电压范围内,以实现可靠的操作。因此,在不损坏开关的情况下获得了快速切换时间的好处。

51.在某些实施方式中,还使用不能可靠地处理脉冲的全电压的标准电压 fet来实现多级缓冲器。但是,通过堆叠使用不同时钟信号相位运行的反相器,可以以不超过最大栅极到源极电压、最大栅极到漏极电压和/或最大漏极到源极电压的方式控制fet的结电压。因此,多级缓冲器在使用标准电压fet的同时在可靠性规格内操作,从而避免了对提供高耐压晶体管的制造过程的成本和/或复杂性的需求。

52.脉冲开关控制电压可提高开关速度,而对rf开关的其他性能特征(如线性,功率处理能力和/或插入损耗)的影响很小甚至没有影响。例如,开关控制电压可以被脉冲化,而无需沿着通过开关的rf信号路径或在rf 开关的控制输入端包括附加电路。因此,无需增加诸如电阻旁路开关之类的电路即可提高开关速度,该电路可能会通过寄生加载rf开关而降低性能。

53.图1是根据本文的教导的rf通信系统10的一个示例的示意图,该系统可以包括一个或多个rf切换电路。

54.尽管rf通信系统10示出了可以包括一个或多个rf切换电路的电子系统的一个示例,但是本文描述的rf切换电路可以在电子系统的其他配置中使用。

55.此外,尽管在图1中示出了组件的特定配置,但是rf通信系统10可以以多种方式进

行适配和修改。例如,rf通信系统10可以包括更多或更少的接收路径和/或发送路径。另外,可以将rf通信系统10修改为包括更多或更少的组件和/或组件的不同布置,包括例如rf切换电路的不同布置。

56.在所示的配置中,rf通信系统10包括基带处理器1、i/q调制器2、 i/q解调器3、第一数字步进衰减器4a、第二数字步进衰减器4b、滤波器 5、功率放大器6、天线开关模块7、低噪声放大器8和天线9。

57.如图1所示,基带处理器1生成同相(i)传输信号和正交相(q)发送信号,这些信号被提供给i/q调制器2。此外,基带处理器1从i/q解调器3接收i接收信号和q接收信号。i和q发送信号对应于特定幅度、频率和相位的发送信号的信号分量。例如,i发送信号和q发送信号分别表示同相正弦分量和正交相正弦分量,并且可以是发送信号的等效表示。另外,i和q接收信号对应于具有特定幅度,频率和相位的接收信号的信号分量。

58.在某些实施方式中,i发送信号,q发送信号,i接收信号和q接收信号是数字信号。另外,基带处理器1可以包括用于处理数字信号的数字信号处理器、微处理器或其组合。

59.i/q调制器2从基带处理器1接收i和q发送信号,并对它们进行处理以产生调制的rf信号。在某些配置中,i/q调制器2可以包括:被配置为将i和q发送信号转换成模拟格式的dac;用于将i和q传输信号上转换为射频的混频器;以及用于将上变频后的i和q信号组合成调制的rf 信号的信号组合器。

60.第一数字阶跃衰减器4a接收调制的rf信号,并且使调制的rf信号衰减以生成衰减的rf信号。第一数字步进衰减器4a可以帮助获得与传输相关联的期望增益和/或功率水平。在所示的配置中,第一数字步进衰减器 4a包括第一rf切换电路20a。第一数字步进衰减器4a示出了根据本文的教导的电路的一个示例,该电路可以包括一个或多个rf切换电路。例如,第一数字步进衰减器4a可以包括级联的衰减器级,每个衰减器级可以使用 rf切换电路被旁路以帮助提供数字可调节的衰减量。

61.滤波器5从第一数字阶跃衰减器4a接收衰减的rf信号,并且将滤波后的rf信号提供给功率放大器6的输入。在某些配置中,滤波器5可以是被配置为提供频带滤波的带通滤波器。然而,取决于应用,滤波器5可以是低通滤波器、带通滤波器、陷波滤波器、高通滤波器或其组合。

62.功率放大器6可以放大滤波后的rf信号以生成放大的rf信号,该放大的rf信号被提供给天线开关模块7。天线开关模块7还电连接到天线9 和低噪声放大器8的输入。天线开关模块7可以用于将天线9选择性地连接到功率放大器6的输出或低噪声放大器8的输入。在某些实施方式中,天线开关模块7可以提供许多其他功能,包括但不限于频带切换、发射和接收之间的切换和/或不同功率模式之间的切换。

63.在所示的配置中,天线开关模块7包括第二rf切换电路20b。天线开关模块7示出了根据本文的教导的电路的另一示例,该电路可以包括一个或多个rf切换电路。例如,天线开关模块7可以包括实现为单刀多掷开关的rf切换电路。尽管图1示出了其中天线开关模块7用作单刀双掷开关的配置,但是天线开关模块7可以适于包括附加的杆和/或掷。

64.lna8从天线开关模块7接收天线接收信号,并产生放大的天线接收信号,该信号被提供给第二数字步进衰减器4b。第二数字步进衰减器4b 可以以数字可控制的衰减量来衰减放大的天线接收信号。如图1所示,第二数字阶跃衰减器4b产生衰减的接收信号,该信号

被提供给i/q解调器 3。包括第二数字阶跃衰减器4b可以帮助向i/q解调器3提供一个信号,以便具有期望的幅度和/或功率水平。在所示的配置中,第二数字步进衰减器4b包括第三rf切换电路20c。第二数字步进衰减器4b示出了根据本文的教导的电路的另一示例,该电路可以包括一个或多个rf切换电路。

65.如前所述,i/q解调器3可用于产生i接收信号和q接收信号。在某些配置中,i/q解调器3可以包括一对混频器,用于将衰减后的接收信号与一对大约异相90度的时钟信号进行混合。此外,混频器可以生成下变频信号,可以将其提供给用于生成i和q接收信号的adc。

66.rf切换电路20a-20c可用于使用各种通信标准来处理rf信号,包括例如全球移动通信系统(gsm)、码分多址(cdma)、宽带cdma (w-cdma)、长期演进(lte)、用于gsm演进(edge)、3g、4g和/ 或5g的增强数据速率,以及其他专有和非专有通信标准。

67.此外,rf切换电路20a-20c可以控制各种频率的信号切换,这些信号不仅包括100mhz和7ghz之间的rf信号,而且还可以切换到更高的频率,例如x波段(大约7ghz至12ghz),ku频段(约12ghz至18ghz), k频段(约18ghz至27ghz),ka频段(约27ghz至40ghz),v频段 (约40ghz至75ghz)和/或w波段(大约75ghz至110ghz)。因此,本文的教导可适用于包括微波通信系统在内的各种rf通信系统。

68.在rf通信系统的发送或接收路径中提供rf开关会影响系统的性能。例如,rf开关的线性、功率处理能力和插入损耗不仅会影响系统的操作,而且瞬态性能特征(例如开启时间、关闭时间和/或稳定时间)可能会对性能产生影响。可以使用本文中的教导来改善rf开关的瞬态性能特性,而对rf开关的其他性能特性(诸如线性、功率处理能力和/或插入损耗)影响很小或没有影响。

69.图2a是根据一个实施例的rf切换电路20的电路图。rf切换电路 20包括n型场效应晶体管(nfet)开关21、多级缓冲器22(在本文中也称为开关偏置电路)和栅极偏置电阻器31。

70.如图2a所示,多级缓冲器22接收控制信号ctl,该控制信号ctl 用于指示应由多级缓冲器22将nfet开关21接通还是断开。因此,控制信号ctl用于选择性地激活nfet开关21。多级缓冲器22还接收电源高电源电压v

dd

、地或电源低电源电压v

ss

、大于电源高电源电压v

dd

的高电压v

high

和低于电源低电源电压v

ss

的低电压v

low

。

71.尽管图2a示出了其中多级缓冲器22用于控制一个fet开关的配置,但是多级缓冲器22可以被配置为偏置一个或多个另外的fet开关。在这样的配置中,多级缓冲器22可以包括附加的开关控制输入,例如与每个 fet开关相关联的控制信号。但是,其他配置也是可能的,例如其中使用控制信号来控制多个fet开关的实现。例如,在某些实施方式中,使用多级缓冲器来控制串联fet开关以及并联fet开关。另外,串联fet开关和并联fet开关可以由公共控制信号控制,使得当串联fet开关打开时,并联fet开关关闭,反之亦然。

72.在示出的配置中,nfet开关21的源极电连接到rf输入rf

in

,并且 nfet开关21的漏极电连接到rf输出rf

out

。尽管其中rf开关连接在 rf输入端子与rf输出端子之间的示例,但是其他配置也是可能的,诸如其中rf开关连接在双向的第一rf端子与第二rf端子之间的实施方式。

73.如图2a所示,栅极偏置电阻器31电连接在多级缓冲器22的栅极偏置输出和nfet开关21的栅极之间。栅极偏置电阻器31可以增强多级缓冲器22的栅极偏置输出和nfet开关21

的栅极之间的隔离。例如,高频信号分量可以通过寄生增益-漏极和/或栅极到源极电容耦合到nfet开关 21的栅极,并且栅极偏置电阻器31可以提供阻止高频信号分量到达多级缓冲器22的栅极偏置输出的电阻。

74.尽管图2a示出了通过电阻器31将多级缓冲器22的输出连接至nfet 开关21的栅极,但是可以在多级缓冲器22的输出与nfet的栅极之间连接任何合适的阻抗。例如,在另一实施例中,电感器或电感器和电阻器的组合被连接在多级缓冲器的输出与rf开关的控制输入之间。

75.nfet开关21可以以多种方式实现。在一个实施例中,nfet开关21 被实现为包括电浮置的主体的绝缘体上硅(soi)金属氧化物半导体(mos) 晶体管。如本文中所使用的,并且如本领域普通技术人员将理解的那样, mos晶体管可以具有由非金属材料(例如,多晶硅)制成的栅极,并且可以具有不仅由氧化硅实现的介电区域,而且还可以由其他介电层例如高k 电介质实现。

76.尽管图2a示出了使用n型晶体管的配置,但是本文的教导可适用于使用p型晶体管或n型和p型晶体管的组合的配置。此外,此处的教导适用于其他类型的rf开关,包括用于控制rf开关阻抗的控制输入。

77.rf切换电路20可以在电子系统内以多种配置使用。例如,nfet开关21可以在诸如图1的rf通信系统10之类的rf通信系统的发送信号路径或接收信号路径中操作。

78.继续参考图2a,多级缓冲器22接收用于选择性地激活nfet开关21 的控制信号ctl。特别地,控制信号ctl指示多级缓冲器22是应该导通 nfet开关21还是关闭nfet开关21。

79.多级缓冲器22在栅极偏置输出处产生开关控制电压,并且响应于控制信号ctl的转变而对开关控制电压进行脉冲化,从而缩短了nfet开关 21的开关延迟。

80.因此,不是直接将开关控制电压从导通电压转换到关断电压,反之亦然,而是在将开关控制电压控制到稳态电压电平之前暂时对其进行脉冲化。通过以这种方式对开关控制电压进行脉冲化,可以缩短nfet开关21 的开关延迟。

81.当接通nfet开关21以提高接通速度时和/或当断开nfet开关21以改善关断速度时,可以施加脉冲。尽管本文的各个实施例都提供了用于on 到off转换以及off到on转换的脉冲,但是本文的教导也适用于仅为 on到off转换提供脉冲或仅提供off到off的脉冲的实施方式。过渡时。在这样的实施方式中,多级缓冲器可以包括用于提供期望的脉冲的相应电路,同时省略了对于提供期望的脉冲不需要的其他电路。

82.在某些实施方式中,当将nfet开关21从off状态切换到on状态时,多级缓冲器22首先将开关控制电压从稳态开关off电压(例如v

ss

) 更改为高电压v

high

,然后从高电压v

high

到稳态开关on电压(例如v

dd

)。因此,当接通nfet开关21时,多级缓冲器22使开关控制电压脉冲化。

83.通过以这种方式对开关控制电压进行脉冲化,可以缩短nfet开关21 的接通时间。

84.在某些实施方式中,当将nfet开关21从导通状态切换到截止状态时,多级缓冲器22首先将开关控制电压从稳态开关导通电压(例如v

dd

) 更改为低电压v

low

,然后从低电压v

low

到稳态开关off电压(例如v

ss)

。因此,当关断nfet开关21时,多级缓冲器22对开关控制电压进行脉冲化,从而缩短了关断时间。脉冲的持续时间可以以多种方式控制,包括通过逻辑

电路配置,该逻辑电路被配置为基于延迟控制单个ctl的边沿来生成用于对多级缓冲器22进行定时的时钟信号相位。

85.可以以多种方式提供高电压v

high

和/或低电压v

low

,包括但不限于在引脚上接收电压或使用电荷泵或其他稳压器产生电压。同样,可以以多种方式提供v

dd

和/或v

ss

,包括但不限于接收引脚上的电压或从其他电压(例如,从v

high

和/或v

low

)产生的电压。

86.在某些实施方式中,出于晶体管可靠性的考虑,高电压v

high

或低电压v

low

中的至少一个超过击穿电压,例如,超过制造nfet开关21所使用的处理技术所允许的最大或最小栅极至源极电压。因此,由于晶体管可靠性的限制,以稳定状态下的高电压v

high

和/或低电压v

low

控制nfet 开关21的栅极将潜在地损坏rf开关21。

87.然而,通过将脉冲开关控制电压施加到栅极电阻器31的与连接到 nfet开关21的栅极的一端相对的另一端,直接在栅极处的电压保持在对于nfet的可靠操作可接受的电压范围内。因此,当在nfet开关21的电压限制或限制内操作时,实现了快速切换时间的益处。

88.图2b是图2a的rf切换电路20的时序图的一个示例。时序图包括由多级缓冲器22输出的开关控制电压的第一曲线图11与时间的关系,以及nfet开关21的栅极电压的第二曲线图12与时间的关系。时序图包括第一时间t1和第二时间t2,在第一时间t1,控制信号ctl转变以将nfet 开关21从截止状态转变为导通状态;在第二时间t2,控制信号ctl转变以将nfet开关21从导通状态切换到截止状态。

89.如图2b所示,在该实施例中,当接通开关以及断开开关时,多级缓冲器22对开关控制电压产生脉冲。例如,当nfet开关21在时间t1导通时,多级缓冲器22产生导通脉冲13,该导通脉冲13与首先将开关控制电压从v

ss

转变为v

high

,然后从v

high

转变为v

dd

相关。另外,当nfet开关21在时间t2关断时,多级缓冲器22产生截止脉冲14,该截止脉冲14 与首先将开关控制电压从v

dd

转换到v

low

,然后从v

low

转换到v

ss

相关。

90.导通脉冲13的持续时间15和关闭脉冲14的持续时间16可以以多种方式控制。在第一示例中,多级缓冲器22包括对输入控制信号及其延迟版本执行逻辑运算的逻辑电路,以生成设置持续时间15和持续时间16的时钟信号相位。

91.如图2b所示,导通脉冲13和截止脉冲14具有相反的极性。例如,导通脉冲13在稳定到较低电压电平之前具有升高的电压电平,而截止脉冲14在稳定到较高电压电平之前具有减小的电压电平。在某些实施方式中,多级缓冲器响应于rf开关的从on到off的转变而产生第一脉冲,并且响应于rf开关的从off到on的转变而产生第二脉冲,以及第一和第二脉冲具有相反的极性。

92.图2c是用于rf切换电路中的rf开关50的另一示例。

93.rf开关50包括第一nfet开关21a、第二nfet开关21b、第三nfet 开关21c、第一栅极偏置电阻器31a、第二栅极偏置电阻器31b、第三栅极偏置电阻器31c、第一沟道偏置电阻器32a、第二通道偏置电阻器32b、第三通道偏置电阻器32c、第四通道偏置电阻器32d、第一dc隔离电容器 41和第二dc隔离电容器42。尽管在图2c中显示了rf开关的一个实施例,本文的教导适用于以多种方式实现的rf开关。

94.在所示的实施例中,第一nfet开关21a、第二nfet开关21b和第三nfet开关21c彼此串联。串联包含多个fet开关组件可以提高rf开关的功率处理能力。尽管示出了具有三个串联的fet开关的示例,但是可以包括更多或更少的fet开关以实现所需的性能。如图2c所示,

栅极偏置电阻器31a-31c分别电连接在栅极偏置端子gate

bias

(由多级缓冲器驱动)和nfet开关21a-21c的栅极之间。

95.沟道偏置电阻器32a-32d共同操作以控制nfet开关21a-21c的源极和漏极的偏置电压,从而帮助控制晶体管的栅极-源极和栅极-漏极偏置特性。尽管示出了沟道偏置的一个示例,但是沟道偏置的其他实施方式也是可能的,包括但不限于使用与一个或多个nfet开关的沟道并联的电阻器的实施方式。

96.第一dc阻断电容器41和第二dc阻断电容器42提供dc阻断,以允许nfet开关21a-21c的源极和漏极在与rf输入rf

in

和rf输出rf

out

不同的dc电压电平下操作。然而,本文的教导也可适用于在没有隔直电容器的情况下操作的rf开关。

97.尽管示出了具有nfet开关的rf开关的一个示例,但是也可以使用 p型fet(pfet)开关或nfet开关和pfet开关的组合来实现rf开关。

98.图3a是用于驱动rf开关的多级缓冲器60的一个实施例的示意图。多级缓冲器60在电源v

high

、v

dd

、v

ss

和v

low

上操作,其中v

high

》v

dd

》 v

ss

》v

low

(例如,如图2b所示)。多级缓冲器60接收控制信号ctl,并且包括用于通过阻抗(例如,栅极电阻器)驱动rf开关(例如,栅极偏置端子)的控制输入的输出端子out。

99.在所示的实施例中,多级缓冲器60包括由第一时钟信号相位控制的第一反相器51、由第二时钟信号相位控制的第二反相器52、由第三时钟信号相位控制的第三反相器53、由第四时钟信号相位控制的第四反相器54、由第五时钟信号相位控制的第五反相器55、由第六时钟信号相位控制的第六反相器56、第一输出开关(在此示例中为pfet 57)、第二输出开关(在此示例中为nfet 58)和定时电路59。

100.如图3a所示,第一反相器51由v

high

和v

dd

供电,而第二反相器52 由v

dd

和v

ss

供电。因此,第一反相器51和第二反相器52电堆叠在v

high

和v

ss

电源之间。另外,第三反相器53由第一反相器51的输出和第二反相器52的输出供电。第三反相器53的输出通过pfet 57的沟道连接到输出端子out,而第二反相器52的输出控制pfet 57的栅极。

101.继续参考图3a,第四反相器54由v

dd

和v

ss

供电,而第五反相器55 由v

ss

和v

low

供电。因此,第四反相器54和第五反相器55电堆叠在v

dd

和v

low

电源之间。另外,第六反相器56由第四反相器54的输出和第五反相器55的输出供电。第六反相器56的输出通过nfet 58的沟道连接到输出端子out,而第四反相器54的输出控制nfet 58的栅极。

102.在所示的实施例中,第一至第六时钟信号相位由定时电路59 产生,定时电路59接收控制信号ctl。在某些实施方式中,控制信号ctl 的边缘在定时电路59内被延迟,并且定时电路59对控制信号ctl和/或其延迟版本执行逻辑运算以生成时钟信号相位。以这种方式实现定时电路 59避免了对振荡器的需求,该振荡器可以在振荡频率处产生噪声,该噪声会干扰rf信令的操作。然而,定时电路的其他实施方式也是可能的。

103.图3b是用于驱动rf开关的多级缓冲器80的另一实施例的示意图。图3b的多级缓冲器80包括与图3a的多级缓冲器60相似的定时电路59、 pfet输出开关57、nfet输出开关58和反相器的配置,不同之处在于在图3b中,每个反相器都是使用连接为cmos反相器的pfet和nfet专门实现的。

104.例如,第一反相器包括第一pfet mp1和第一nfet mn1,而第二反相器包括第二

pfet mp2和第二nfet mn2。另外,第三反相器包括第三 pfet mp3和第三nfet mn3,而第四反相器包括第四pfet mp4和第四 nfet mn4。此外,第五反相器包括第五pfet mp5和第五nfet mn5,而第六反相器包括第六pfet mp6和第六nfet mn6。

105.另外,图3b的多级缓冲器80还包括用于驱动第一反相器的第一电平移位器71和用于驱动第五反相器的第二电平移位器72。第一电平移位器 71在与v

dd

和v

ss

相关的电压域中移位第一时钟信号以在与v

high

和 v

dd

相关的电压域中产生时钟信号另外,第二电平移位器72在与v

dd

和v

ss

相关的电压域中移位第五时钟信号以在与v

ss

和v

low

相关的电压域中产生时钟信号任何类型的电平移位器都可以用于提供电平转换。

106.左分支包括两个堆叠的反相器,分别在v

high

:v

dd

和v

dd

:v

ss

之间工作。就可靠性而言,左分支本质上是安全的。左上反相器定义左中支的供电电压,而左下反相器定义左中支的接地电压。左上分支使用在v

high

和 v

dd

之间操作的第一电平移位器71。

107.右分支包括两个堆叠的反相器,分别在v

dd

:v

ss

和v

ss

:v

low

之间工作。就可靠性而言,正确的分支本质上是安全的。右上反相器定义右中分支的电源电压,而左下反相器定义中右分支的接地电压。右下分支使用在v

ss

和v

low

之间操作的第二电平移位器72。

108.中心分支用于隔离左分支或右分支之一,同时生成所需的输出电压。

109.图4a是用于驱动rf开关的多级缓冲器100的另一实施例的示意图。图4a的多级缓冲器100包括pfet输出开关57、nfet输出开关58以及为图4a的多级缓冲器80示出的六个反相器。尽管未示出,但是图3b的定时电路59以及电平移位器71和72可以被包括在多级缓冲器100中。如图4a所示,用于特定电源电压电平的注释(v

high

=2*v

dd

,v

ss

=0v,并且v

low

=-v

dd

)。

110.图4b是描述图4a的多级缓冲器80的操作的一个示例的表。描绘了用于实现四个输出电压电平中的每个电平的时钟信号值。

111.参考图4a和4b,多级缓冲器100不需要高压晶体管,并且在没有任何可靠性问题的情况下进行操作。因此,多级缓冲器的所有fet可以是额定为v

dd

的标准电压晶体管。此外,多级缓冲器能够产生四个输出电压电平(2*v

dd

(v

high

),v

dd

,gnd(v

ss

)和-v

dd

(v

low

)),每个晶体管仅在v

dd

范围内工作,同时产生所有所需的电压(包括2*v

dd

,-v

dd

)。此外,多级缓冲器100以低负载电流工作,这在其中使用调节器或电荷泵产生一个或多个电源电压的应用中是特别有利的。

112.继续参考图4a和4b,多级缓冲器具有较高的动态范围,例如,在2* v

dd

和-v

dd

之间的操作可实现3*v

dd

的动态范围。可以使用标准电压晶体管来实现所有晶体管,例如,标准(3v)nmos和pmos器件,而无需任何高压器件。在该示例中,根据时钟相位信号(至),输出电压可以为2*v

dd

、v

dd

、0或

–vdd

,因此,在某些实施方式中,多级缓冲器 100可以进行数字操作。

113.为了在不产生任何可靠性问题的情况下产生高于v

dd

且低于gnd的电压,控制时钟信号相位和

114.在第一个示例中,从

–vdd

到2*v

dd

的转换使用(第一个最后一个)。

115.在第二个示例中,从2*v

dd

到v

dd

的转换使用

116.在第三个示例中,从v

dd

到

–vdd

的转换使用

117.当将这些时序排序规则(优先级规则)应用于时钟相位时,所有晶体管的电压差(栅极至源极电压或vgs、栅极至漏极电压或vgd以及栅极至漏极电压或vds)始终低于v

dd

。

118.图示的实施例提供了-v

dd

的低电压。在另一实施例中,通过插入由另一控制信号控制的另一开关来获得甚至更低的电压(例如,-2*v

dd

)。

119.图5a是处于第一操作状态的图4a的多级缓冲器100的示意图,其中输出电压为2

×vdd

。

120.如图5a所示,要获得2*v

dd

的输出电压,的输出电压,

121.图5b是处于第二操作状态的图4a的多级缓冲器100的示意图,其中输出电压是v

dd

。

122.如图5b所示,为了获得v

dd

的输出电压,的输出电压,

123.图5c是处于第三操作状态的图4a的多级缓冲器100的示意图,其中输出电压是gnd。

124.如图5c所示,要获得gnd的输出电压,如图5c所示,要获得gnd的输出电压,

125.图5d是处于第四操作状态的图4a的多级缓冲器100的示意图,其中输出电压是-v

dd

。

126.如图5d所示,要获得-v

dd

的输出电压,的输出电压,

127.图6是根据一个实施例的用于多级缓冲器的时序图。时序图描绘了各种时钟信号相位,用于生成用于驱动rf开关的升压脉冲。特别地,示出了用于out、和的示例电压。在此特定仿真中,将out控制为仅三个不同的电压电平,而不是四个。

128.图7是根据一个实施例的rf切换电路的时序图。该时序图比较了使用升压和不使用升压时rf开关处的栅极电压。如图7所示,使用升压时可实现更快的开启时间。

129.提供用于射频(rf)开关的偏置的多级缓冲器。在某些实施方案中,rf 切换电路包括场效应晶体管(fet)开关、阻抗和通过阻抗向fet的栅极提供开关控制电压的多级缓冲器。多级缓冲器接收控制信号以导通或截止 fet开关。另外,多级缓冲器用堆叠的反相器来实现,该堆叠的反相器使用不同的时钟信号相位来操作以响应于控制信号的转变而对开关控制电压进行脉冲化,从而缩短对fet开关的切换的延迟。通过堆叠使用不同时钟信号相位操作的反相器,以不超过最大栅极-源极电压、最大栅极-漏极电压和/或最大漏极-源极电压的方式控制晶体管结电压。

130.在一方面,提供射频(rf)切换电路。rf切换电路包括:包括栅极的场效应晶体管(fet)开关;阻抗;和输出端子通过所述阻抗连接到fet 的栅极的多级缓冲器。多级缓冲器

包括:第一反相器,被配置为接收第一时钟信号相位,并由第一电源电压和小于该第一电源电压的第二电源电压供电;第二反相器,被配置为接收第二时钟信号相位,并由第二电源电压和小于该第二电源电压的第三电源电压供电;第三反相器,被配置为接收第三时钟信号相位,并由所述第一反相器的输出和所述第二反相器的输出供电;和连接在所述输出端子和所述第三反相器的输出之间的第一输出开关。

131.在另一方面,提供一种用于驱动晶体管栅极的多级缓冲器。多级缓冲器包括:输出端子;第一反相器,被配置为接收第一时钟信号相位,并由第一电源电压和小于该第一电源电压的第二电源电压供电;第二反相器,被配置为接收第二时钟信号相位,并由第二电源电压和小于该第二电源电压的第三电源电压供电;第三反相器,被配置为接收第三时钟信号相位,并由所述第一反相器的输出和所述第二反相器的输出供电;和连接在所述输出端子和所述第三反相器的输出之间的第一输出开关。

132.在另一方面,提供一种射频(rf)切换方法。该方法包括:将第一时钟信号相位提供给由第一电源电压和小于该第一电源电压的第二电源电压供电的第一反相器的输入;将第二时钟信号相位提供给由第二电源电压和小于该第二电源电压的第三电源电压供电的第二反相器的输入;将第三时钟信号相位提供给由所述第一反相器的输出和所述第二反相器的输出供电的第三反相器的输入;使用连接在所述输出端子和所述第三反相器的输出之间的第一输出开关来控制输出端子处的输出电压;和通过阻抗将所述输出电压提供给场效应晶体管(fet)的栅极。

133.应用

134.可以将采用上述方案的设备实现为各种电子设备。电子设备的示例包括但不限于rf通信系统、消费类电子产品、电子测试设备、通信基础设施等。例如,具有快速切换功能的rf开关可用于各种rf通信系统,包括 (但不限于)基站,移动设备(例如,智能手机或手机),膝上型计算机,平板电脑,物联网(iot)设备和/或可穿戴电子设备。本文的教导适用于在宽范围的频率和频带上操作的rf通信系统,包括使用时分双工(tdd) 和/或频分双工(fdd)的那些。

135.结论

136.前述描述可以将元件或特征称为“连接”或“耦合”在一起。如本文所使用的,除非另有明确说明,否则“连接”是指一个元件/特征直接或间接地连接至另一元件/特征,并且不一定是机械地。同样地,除非另有明确说明,否则“耦合”是指一个元件/特征直接或间接地耦合至另一元件/特征,并且不一定是机械地。因此,尽管在附图中示出的各种示意图描绘了元件和组件的示例布置,但是在实际的实施例中可以存在附加的中间元件、设备、特征或组件(假设所描绘的电路的功能没有受到不利影响)。

137.尽管已经根据某些实施例描述了本公开,但是对于本领域普通技术人员来说显而易见的其他实施例,包括未提供本文阐述的所有特征和优点的实施例,也在本公开的范围内。而且,可以将上述各种实施例组合以提供其他实施例。另外,在一个实施例的上下文中示出的某些特征也可以被结合到其他实施例中。因此,本公开的范围仅通过参考所附权利要求来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。