1.本实用新型涉及网络安全领域,特别涉及一种多形态安全防护系统。

背景技术:

2.vpn产品可为智能终端提供vpn接入和防火墙功能。目前,vpn产品分为vpn终端软件与vpn网关。vpn终端软件是安装在pc或智能终端上,为用户提供vpn连接功能。vpn网关通过rj45形态的网口为智能终端提供vpn接入服务。

3.但是,vpn网关为智能终端提供的连接方式单一,基本以网口为主,无法满足物联网、工控网络等多场景需求。vpn网关的形态单一,只能为客户提供整机产品的形式进行使用,产品灵活性低。并且,vpn软件是以客户硬件设备系统为基础进行安装。一旦用户硬件设备系统受到网络攻击,vpn也变得不再可靠。vpn网关虽然是以硬件形态提供服务,但是仅提供访问权限限制等安全防护能力,抗网络攻击能力一般。由此可见,现有的vpn网关存在灵活性差、防护能力一般等问题,大大影响了其实用性。

技术实现要素:

4.本实用新型所要解决的技术问题是:提供一种多形态安全防护系统,使用起来更加灵活,具有很高的实用性。

5.为了解决上述问题,本实用新型采用的方案为:

6.一种多形态安全防护系统,包括主板控制芯片、usb集线控制电路、第一tf卡接口电路、第一rj45接口电路、第一pcie接口电路、第一rs485接口电路和第一供电电路;

7.所述主板控制芯片与所述usb集线控制电路、所述第一pcie接口电路、所述第一rj45接口电路和所述第一rs485接口电路相连,所述usb集线控制电路分别与所述第一tf卡接口电路、所述第一rs485接口电路和所述第一pcie接口电路相连;

8.所述第一供电电路分别与所述主板控制芯片、所述usb集线控制器、所述第一tf卡接口电路、所述第一rj45接口电路、所述第一pcie接口电路和所述第一rs485接口电路相连。

9.进一步地,所述usb集线控制电路包括usb集线控制芯片、第一晶振、第一电容、第二电容、第三电容、第四电容、第五电容、第一电阻、第二电阻、第三电阻、第四电阻、第五电阻、第六电阻、第七电阻、第八电阻、第九电阻、第十电阻和第一旁路电容;

10.所述usb集线控制芯片的供电输入引脚与所述第一供电电路的第一供电输出端相连,所述usb集线控制芯片的使能数据输入引脚与所述主板控制芯片的usb数据传输引脚相连,所述usb集线控制芯片的复位引脚同时与所述第一电容的一端和所述第一电阻的一端相连,所述第一电阻的另一端与所述第一供电电路的第一供电输出端相连,所述集线控制芯片的外部时钟输入第一引脚同时与所述第二电容的一端和所述第一晶振的第一引脚相连,所述集线控制芯片的外部时钟输入第二引脚同时与所述第三电容的一端和所述第一晶振的第二引脚相连;

11.所述usb集线控制芯片的第一dm数据传输引脚和第一dp数据传输引脚分别通过所述第二电阻和所述第三电阻与所述第一pcie接口电路相连,所述usb集线控制芯片的第二dm数据传输引脚和第二dp数据传输引脚分别通过所述第四电阻和所述第五电阻与所述第一tf卡接口电路相连,所述usb集线控制芯片的第一表带可选引脚和第二表带可选引脚分别对应通过所述第六电阻和所述第七电阻接地;所述usb集线控制芯片的第一配置引脚和第二配置引脚分别对应通过所述第八电阻和所述第九电阻接地;

12.所述usb集线控制芯片的偏执电阻外接引脚通过所述第十电阻接地,所述usb集线控制芯片的锁相滤波引脚通过所述第四电容接地,所述usb集线控制芯片的继电器滤波引脚通过所述第四电容接地,所述第一电容的另一端、所述第二电容的另一端、所述第三电容的另一端和所述第一晶振的接地引脚均接地,所述第一旁路电容的一端同时与所述第一供电电路的第一供电输出端和所述usb集线控制芯片的供电输入引脚相连且另一端接地。

13.进一步地,所述第一pcie接口电路包括卡边缘连接器、pcie接口、第六电容、第十一电阻、第十二电阻和第二旁路电容;

14.所述卡边缘连接器的供电电压输入引脚同时与所述第一供电电路的第一供电输出端和所述第二旁路电容的一端相连;

15.所述卡边缘连接器的dm数据传输引脚与所述第二电阻远离所述usb集线控制芯片的一端相连,所述卡边缘连接器的dp数据传输引脚与所述第三电阻远离所述usb集线控制芯片的一端相连;

16.所述卡边缘连接器的sim卡供电输出引脚同时与所述第六电容的一端和所述pcie接口的供电输入引脚相连,所述卡边缘连接器的sim卡复位控制引脚与所述pcie接口的复位信号输入引脚相连,所述卡边缘连接器的sim卡时钟控制引脚与所述pcie接口的时钟信号输入引脚相连,所述卡边缘连接器的sim卡数据传输引脚与所述pcie接口的数据传输引脚相连;

17.所述卡边缘连接器的低电平复位引脚通过所述第十一电阻与所述主板控制芯片的第一串行输入输出引脚相连,所述卡边缘连接器的停机控制引脚通过所述第十二电阻与所述主板控制芯片的第二串行输入输出引脚相连,所述卡边缘连接器的扩展总线时钟信号引脚与所述主板控制芯片的扩展总线时钟信号引脚相连,所述卡边缘连接器的扩展总线数据发送引脚与所述主板控制芯片的数据接收引脚相连,所述卡边缘连接器的扩展总线数据接收引脚与所述主板控制芯片的数据发送引脚相连;

18.所述卡边缘连接器的接地引脚、所述第六电容的另一端、所述第二旁路电容的另一端以及所述pcie接口的接地引脚均接地。

19.进一步地,所述第一tf卡接口电路包括读卡器芯片、tf芯片、第十三电阻、第十四电阻、第十五电阻、第七电容、第八电容、第九电容、第十电容、第十一电容和第一发光二极管;

20.所述读卡器芯片的第一供电输入引脚同时与所述第七电容的一端和所述第一供电电路的第二供电输出端相连,所述读卡器芯片的第二供电输入引脚同时与所述第八电容的一端和所述第一供电电路的第一供电输出端相连,所述读卡器芯片的模拟电源输入引脚同时与所述第九电容的一端和所述第十三电阻的一端相连,所述第十三电阻的另一端与所述第一供电电路的第一供电输出端相连,所述读卡器芯片的串行输入输出引脚同时与所述

第十四电阻和所述tf芯片的数据监测引脚相连,所述第十四电阻的另一端与所述第一供电电路的第一供电输出端相连;

21.所述读卡器芯片的指示灯驱动引脚与所述第一发光二极管的正极相连,所述第一发光二极管的负极通过所述第十五电阻接地,所述读卡器芯片的dm数据传输引脚与所述第四电阻远离所述usb集线控制芯片的一端相连,所述读卡器芯片的dp数据传输引脚与所述第五电阻远离所述usb集线控制芯片的一端相连,所述读卡器芯片的时钟信号引脚与所述tf芯片的时钟信号引脚相连,所述读卡器芯片的命令和响应多路复用引脚与所述tf芯片的命令和响应多路复用引脚相连,所述读卡器芯片的数据传输引脚与所述tf芯片的数据传输引脚相连;

22.所述tf芯片的供电输入引脚同时与所述第十电容的一端、所述第十一电容的一端和所述第一供电电路的第一供电输出端相连;

23.所述读卡器芯片的接地引脚、所述第七电容的另一端、所述第八电容的另一端、所述第九电容的另一端、所述tf芯片的接地引脚、所述第十电容的另一端和所述第十一电容的另一端均接地。

24.进一步地,所述第一rj45接口电路包括以太网芯片、第二晶振、第一参考电压、第二参考电压、第十六电阻、第十七电阻、第十八电阻、第十二电容、第十三电容、第十四电容、第十五电容、第三旁路电容、第四旁路电容和第五旁路电容;

25.所述以太网芯片的供电电压输入引脚同时与所述第三旁路电容的一端和所述第一供电电路的第二供电输出端相连,所述以太网芯片的外部时钟输入第一引脚同时与所述第二晶振的第一引脚和所述第十二电容的一端相连,所述以太网芯片的外部时钟输入第二引脚同时与所述第二晶振的第二引脚和所述第十三电容的一端相连,所述以太网芯片的远端唤醒引脚和串行输入输出引脚分别通过所述第十六电阻和所述第十七电阻与所述第一参考电压相连,所述以太网芯片的参考电压输入第一引脚与所述第一参考电压相连,所述以太网芯片的参考电压输入第二引脚与所述第二参考电压相连,所述以太网芯片的复位信号输入引脚通过所述第十八电阻接地,所述以太网芯片的不间断电源输入引脚同时与所述第十四电容的一端和所述第十五电容的一端相连,所述第一参考电压与所述第四旁路电容的一端相连,所述第二参考电压的与所述第五旁路电容的一端相连,所述以太网芯片的手动数据输入引脚与手动数据输出引脚与所述主板控制芯片的数据发送引脚和数据接收引脚对应相连;

26.所述以太网芯片的接地引脚、所述第十二电容的另一端、所述第十三电容的另一端、所述第二晶振的接地引脚、所述第十四电容的另一端、第十五电容的另一端、所述第三旁路电路的另一端、所述第四旁路电容的另一端和所述第五旁路电容的另一端均接地。

27.进一步地,所述第一rs485接口电路包括异步收发器、rs485芯片、第十六电容、第十七电容、第十八电容、第十九电阻、第二十电阻、第二十一电阻、第二十二电阻、第二十三电阻、第二十四电阻、第二十五电阻、第二十六电阻、第二十七电阻、第二十八电阻、第二十九电阻、第三十电阻、第二发光二极管、第三发光二极管和第六旁路电容;

28.所述异步收发器的dp数据传输引脚与所述usb集线控制芯片的第三dp数据传输引脚相连,所述异步收发器的dm数据传输引脚与所述usb集线控制芯片的第三dm数据传输引脚相连,所述异步收发器的供电电压输入引脚同时与所述第一供电电路的第二供电输出端

和所述第十六电容的一端相连,所述异步收发器的内存控制器电压引脚与电压输出引脚均与所述第一供电电路的第一供电输出端相连,所述异步收发器的串口数据发送引脚通过所述第十九电阻与所述rs485芯片的驱动器输入引脚相连,所述异步收发器的串口数据接收引脚通过所述第二十电阻与所述rs485芯片的接收器输出引脚相连,所述异步收发器的第一可配置输出引脚与所述第二十一电阻的一端相连,所述第二十一电阻的另一端同时与所述rs485芯片和接收使能引脚、发送使能引脚和所述第二十二电阻的一端相连并通过所述第二十三电阻连接所述主板控制芯片的第三串行输入输出引脚;

29.所述异步收发器的第二可配置输出引脚通过所述第二十四电阻与所述第二发光二极管的负极相连,所述异步收发器的第三可配置输出引脚通过所述第二十五电阻与所述第三发光二极管的负极相连,所述第二发光二极管的正极和所述第三发光二极管的正极均与所述第一供电电路的第一供电输出端相连,所述异步收发器的复位引脚同时与所述第二十六电阻的一端、第二十七电阻的一端以及所述第十七电容的一端相连,所述第二十六电阻的另一端与所述第一供电电路的第二供电输出端相连;

30.所述rs485芯片的供电输入引脚同时与所述第十八电容的一端和所述第一供电电路的第二供电输出端相连,所述rs485芯片的差分信号发送引脚同时与所述第二十八电阻的一端和所述第二十九电阻的一端相连,所述rs485芯片的差分信号接收引脚同时与所述第二十九电阻的另一端和所述第三十电阻的一端相连,所述第三十电阻的另一端与所述第一供电电路的第一供电输出端相连;

31.所述第一供电电路的第一供电输出端通过所述第六旁路电容接地,所述异步收发器的接地引脚、所述第十六电容的另一端、所述第十七电容的另一端、所述第二十七电阻的另一端、所述rs485芯片的接地引脚、所述第二十二电阻的另一端、所述第二十七电阻的另一端和所述第十八电容的另一端均接地。

32.进一步地,所述第一供电电路包括电源管理芯片、电感、第三十一电阻、第三十二电阻、第三十三电阻、第三十四电阻、第三十五电阻、第三十六电阻、第十九电容、第二十电容、第二十一电容、第二十二电容、第二十三电容、第二十四电容、第二十五电容和外部电源;

33.所述外部电源的电压输出端同时与所述第十九电容的一端、所述第二十电容的一端、所述第三十一电阻的一端、所述第三十二电阻的一端和所述电源管理芯片的电压输入引脚相连,所述第三十二电阻的另一端与所述电源管理芯片的使能引脚相连,所述电源管理芯片的供电输入引脚与所述第二十一电容的一端相连,所述电源管理芯片的软启动引脚与所述第二十二电容的一端相连;

34.所述电源管理芯片的自举升压引脚与所述第三十三电阻的一端相连,所述第三十三电阻的另一端与所述二十三电容的一端相连,所述第二十三电容的另一端同时与所述电源管理芯片的转换引脚和所述电感的一端相连,所述电感的另一端同时与所述第三十四电阻的一端、所述第二十四电容的一端和所述第二十五电容的一端相连,所述第三十四电阻的另一端同时与所述第三十五电阻的一端、所述三十六电阻的一端和所述第二十四电容的另一端相连,所述第三十五电阻的另一端与所述电源管理芯片的反馈引脚相连;

35.所述第十九电容的另一端、所述第二十电容的另一端、所述第三十一电阻的另一端、所述第二十一电容的另一端、所述第二十二电容的另一端、所述电源管理芯片的接地引

脚、所述三十六电阻的另一端和所述二十五电容的另一端均接地;

36.所述第三十四电阻与所述第二十五电容的连接处为所述第一供电电路的第一供电输出端,所述外部电源的电压输出端为所述第一供电电路的第二供电输出端。

37.进一步地,还包括数据排座、子板控制芯片、rs485接口、第二rj45接口电路、第二pcie接口电路、第二供电电路和rs232接口电路;

38.所述主板控制芯片通过所述数据排座与所述子板控制芯片相连,所述子板控制芯片分别与所述rs232接口电路和所述第二rj45接口电路相连,所述rs485接口通过所述数据排座与所诉后第一rs485接口电路相连,所述usb集线控制电路通过所述数据排座与所述第二pcie接口电路相连;

39.所述第二供电电路分别与所述rs232接口电路、第二rj45接口电路、第二pcie接口电路和所述子板控制芯片相连。

40.进一步地,还包括微型usb接口电路、第二tf卡接口电路和开关控制电路;

41.所述usb集线控制电路通过所述数据排座与所述开关控制电路相连,所述开关控制电路分别与所述微型usb接口电路和所述第二tf卡接口电路相连;

42.所述第二供电电路分别与所述微型usb接口电路、所述第二tf卡接口电路和所述开关控制电路相连。

43.进一步地,所述rs232接口电路包括rs232芯片、第三十七电阻、第三十八电阻、第二十六电容、第二十七电容、第二十八电容、第二十九电容、第三十电容、第一静电二极管和第二静电二极管;

44.所述rs232芯片的供电电压输入引脚同时与所述第二十六电容的一端和所述第二供电电路的供电输出端相连,所述rs232芯片的第一外接电容正极引脚与所述第二十七电容的一端相连,所述第二十七电容的另一端与所述rs232芯片的第一外接电容负极引脚相连,所述rs232芯片的第二外接电容正极引脚与所述第二十八电容的一端相连,所述第二十八电容的另一端与所述rs232芯片的第二外接电容负极引脚相连,所述rs232芯片的电源输出正极引脚与所述第二十九电容的一端相连,所述rs232芯片的电源输出负极与所述第三十电容的一端相连;

45.所述rs232芯片的ttl数据输入引脚与所述第三十七电阻的一端相连,所述第三十七电阻的另一端与所述子板控制芯片的串口通信数据发送引脚相连,所述rs232芯片的ttl数据输出引脚与所述第三十八电阻的一端相连,所述第三十八电阻的另一端与所述子板控制芯片的串口通信数据接收引脚相连,所述rs232芯片的rs232数据输出引脚与所述第一静电二极管的一端相连,所述rs232芯片的rs232数据输入引脚与所述第二静电二极管的一端相连;

46.所述第二十六电容的另一端、所述rs232芯片的接地引脚、所述第二十九电容的另一端、所述第三十电容的另一端、所述第一静电二极管的另一端和第二静电二极管的另一端均接地。

47.综上所述,本实用新型的有益效果在于:提供一种多形态安全防护系统。在网关设备的主板控制芯片上接入usb集线控制电路,以此扩展了第一tf卡接口电路、第一rj45接口电路以及第一pcie接口电路等多种通讯接口,实现多种不同的网络数据传输,还能够适用于仅依靠rj45传输的物联网终端或工控网络的应用场景,与不同的用户硬件设备相适配,

实现了网关设备的形态多样化和连接方式多样化。

附图说明

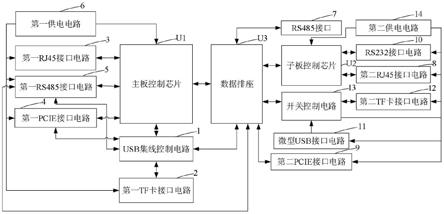

48.图1为本实用新型实施例的一种多形态安全防护系统的系统框图;

49.图2为本实用新型实施例的一种多形态安全防护系统的主板控制芯片的引脚定义图;

50.图3为本实用新型实施例的一种多形态安全防护系统的usb集线控制电路的电路连接图;

51.图4为本实用新型实施例的一种多形态安全防护系统的第一pcie接口电路的电路连接图;

52.图5为本实用新型实施例的一种多形态安全防护系统的第一tf卡接口电路的电路连接图;

53.图6为本实用新型实施例的一种多形态安全防护系统的第一rj45接口电路的电路连接图;

54.图7为本实用新型实施例的一种多形态安全防护系统的第一rs485接口电路的电路连接图;

55.图8为本实用新型实施例的一种多形态安全防护系统的第一供电电路的电路连接图;

56.图9为本实用新型实施例的一种多形态安全防护系统的子板控制芯片的引脚定义图;

57.图10为本实用新型实施例的一种多形态安全防护系统的rs232接口电路的电路连接图。

58.标号说明:

59.1、usb集线控制电路;2、第一tf卡接口电路;3、第一rj45接口电路;4、第一pcie接口电路;5、第一rs485接口电路;6、第一供电电路;7、rs485接口;8、第二rj45接口电路;9、第二pcie接口电路;10、rs232接口电路;11、微型usb接口电路;12、第二tf卡接口电路;13、开关控制电路;14、第二供电电路;

60.c1、第一电容;c2、第二电容;c3、第三电容;c4、第四电容;c5、第五电容;c6、第六电容;c7、第七电容;c8、第八电容;c9、第九电容;c10、第十电容;c11、第十一电容;c12、第十二电容;c13、第十三电容;c14、第十四电容;c15、第十五电容;c16、第十六电容;c17、第十七电容;c18、第十八电容;c19、第十九电容;c20、第二十电容;c21、第二十一电容;c22、第二十二电容;c23、第二十三电容;c24、第二十四电容;c25、第二十五电容;c26、第二十六电容;c27、第二十七电容;c28、第二十八电容;c29、第二十九电容;c30、第三十电容;c31~c37、第一旁路电容;c38~c43、第二旁路电容;44~c45、第三旁路电容;c46~c48、第四旁路电容;c49~c51、第五旁路电容;c52~c53、第六旁路电容;

61.d1、第一发光二极管;d2、第二发光二极管;d3、第三发光二极管;d4、第一静电二极管;d5、第二静电二极管;dvdd33、第一参考电压;dvdd12、第二参考电压;

62.l1、电感;

63.r1、第一电阻;r2、第二电阻;r3、第三电阻;r4、第四电阻;r5、第五电阻;r6、第六电

阻;r7、第七电阻;r8、第八电阻;r9、第九电阻;r10、第十电阻;r11、第十一电阻;r12、第十二电阻;r13、第十三电阻;r14、第十四电阻;r15、第十五电阻;r16、第十六电阻;r17、第十七电阻;r18、第十八电阻;r19、第十九电阻;r20、第二十电阻;r21、第二十一电阻;r22、第二十二电阻;r23、第二十三电阻;r24、第二十四电阻;r25、第二十五电阻;r26、第二十六电阻;r27、第二十七电阻;r28、第二十八电阻;r29、第二十九电阻;r30、第三十电阻;r31、第三十一电阻;r32、第三十二电阻;r33、第三十三电阻;r34、第三十四电阻;r35、第三十五电阻;r36、第三十六电阻;r37、第三十七电阻;r38、第三十八电阻;

64.u1、主板控制芯片;u2、子板控制芯片;u3、数据排座;u4、usb集线控制芯片;u5、卡边缘连接器;u6、pcie接口;u7、读卡器芯片;u8、tf芯片;u9、以太网芯片;u10、异步收发器;u11、rs485芯片;u12、电源管理芯片;u13、rs232芯片;

65.vcc、外部电源;

66.z1、第一晶振;z2、第二晶振。

具体实施方式

67.为详细说明本实用新型的技术内容、所实现目的及效果,以下结合实施方式并配合附图予以说明。

68.请参照图1至图10,一种多形态安全防护系统,包括主板控制芯片u1、usb集线控制电路1、第一tf卡接口电路2、第一rj45接口电路3、第一pcie接口电路4、第一rs485接口电路5和第一供电电路6;

69.所述主板控制芯片u1与所述usb集线控制电路1、所述第一pcie接口电路4、所述第一rj45接口电路3和所述第一rs485接口电路5相连,所述usb集线控制电路1分别与所述第一tf卡接口电路2、所述第一rs485接口电路5和所述第一pcie接口电路4相连;

70.所述第一供电电路6分别与所述主板控制芯片u1、所述usb集线控制器、所述第一tf卡接口电路2、所述第一rj45接口电路3、所述第一pcie接口电路4和所述第一rs485接口电路5相连。

71.从上述描述可知,本实用新型的有益效果在于:提供一种多形态安全防护系统。在网关设备的主板控制芯片u1上接入usb集线控制电路1,以此扩展了第一tf卡接口电路2、第一rj45接口电路3以及第一pcie接口电路4等多种通讯接口,实现多种不同的网络数据传输,还能够适用于仅依靠rj45传输的物联网终端或工控网络的应用场景,与不同的用户硬件设备相适配,实现了网关设备的形态多样化和连接方式多样化。

72.进一步地,所述usb集线控制电路1包括usb集线控制芯片u4、第一晶振z1、第一电容c1、第二电容c2、第三电容c3、第四电容c4、第五电容c5、第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5、第六电阻r6、第七电阻r7、第八电阻r8、第九电阻r9、第十电阻r10和第一旁路电容;

73.所述usb集线控制芯片u4的供电输入引脚与所述第一供电电路6的第一供电输出端相连,所述usb集线控制芯片u4的使能数据输入引脚与所述主板控制芯片u1的usb数据传输引脚相连,所述usb集线控制芯片u4的复位引脚同时与所述第一电容c1的一端和所述第一电阻r1的一端相连,所述第一电阻r1的另一端与所述第一供电电路6的第一供电输出端相连,所述集线控制芯片的外部时钟输入第一引脚同时与所述第二电容c2的一端和所述第

一晶振z1的第一引脚相连,所述集线控制芯片的外部时钟输入第二引脚同时与所述第三电容c3的一端和所述第一晶振z1的第二引脚相连;

74.所述usb集线控制芯片u4的第一dm数据传输引脚和第一dp数据传输引脚分别通过所述第二电阻r2和所述第三电阻r3与所述第一pcie接口电路4相连,所述usb集线控制芯片u4的第二dm数据传输引脚和第二dp数据传输引脚分别通过所述第四电阻r4和所述第五电阻r5与所述第一tf卡接口电路2相连,所述usb集线控制芯片u4的第一表带可选引脚和第二表带可选引脚分别对应通过所述第六电阻r6和所述第七电阻r7接地;所述usb集线控制芯片u4的第一配置引脚和第二配置引脚分别对应通过所述第八电阻r8和所述第九电阻r9接地;

75.所述usb集线控制芯片u4的偏执电阻外接引脚通过所述第十电阻r10接地,所述usb集线控制芯片u4的锁相滤波引脚通过所述第四电容c4接地,所述usb集线控制芯片u4的继电器滤波引脚通过所述第四电容c4接地,所述第一电容c1的另一端、所述第二电容c2的另一端、所述第三电容c3的另一端和所述第一晶振z1的接地引脚均接地,所述第一旁路电容的一端同时与所述第一供电电路6的第一供电输出端和所述usb集线控制芯片u4的供电输入引脚相连且另一端接地。

76.从上述描述可知,usb集线控制芯片u4适用于外部扩展端口的需求设计,其传输速度快、功耗低,还能够灵活配置。

77.进一步地,所述第一pcie接口电路4包括卡边缘连接器u5、pcie接口u6、第六电容c6、第十一电阻r11、第十二电阻r12和第二旁路电容;

78.所述卡边缘连接器u5的供电电压输入引脚同时与所述第一供电电路6的第一供电输出端和所述第二旁路电容的一端相连;

79.所述卡边缘连接器u5的dm数据传输引脚与所述第二电阻r2远离所述usb集线控制芯片u4的一端相连,所述卡边缘连接器u5的dp数据传输引脚与所述第三电阻r3远离所述usb集线控制芯片u4的一端相连;

80.所述卡边缘连接器u5的sim卡供电输出引脚同时与所述第六电容c6的一端和所述pcie接口u6的供电输入引脚相连,所述卡边缘连接器u5的sim卡复位控制引脚与所述pcie接口u6的复位信号输入引脚相连,所述卡边缘连接器u5的sim卡时钟控制引脚与所述pcie接口u6的时钟信号输入引脚相连,所述卡边缘连接器u5的sim卡数据传输引脚与所述pcie接口u6的数据传输引脚相连;

81.所述卡边缘连接器u5的低电平复位引脚通过所述第十一电阻r11与所述主板控制芯片u1的第一串行输入输出引脚相连,所述卡边缘连接器u5的停机控制引脚通过所述第十二电阻r12与所述主板控制芯片u1的第二串行输入输出引脚相连,所述卡边缘连接器u5的扩展总线时钟信号引脚与所述主板控制芯片u1的扩展总线时钟信号引脚相连,所述卡边缘连接器u5的扩展总线数据发送引脚与所述主板控制芯片u1的数据接收引脚相连,所述卡边缘连接器u5的扩展总线数据接收引脚与所述主板控制芯片u1的数据发送引脚相连;

82.所述卡边缘连接器u5的接地引脚、所述第六电容c6的另一端、所述第二旁路电容的另一端以及所述pcie接口u6的接地引脚均接地。

83.从上述描述可知,通过卡边缘连接器u5实现sim卡接口扩展,使得系统能够通过移动数据进行网络通讯。

84.进一步地,所述第一tf卡接口电路2包括读卡器芯片u7、tf芯片u8、第十三电阻r13、第十四电阻r14、第十五电阻r15、第七电容c7、第八电容c8、第九电容c9、第十电容c10、第十一电容c11和第一发光二极管d1;

85.所述读卡器芯片u7的第一供电输入引脚同时与所述第七电容c7的一端和所述第一供电电路6的第二供电输出端相连,所述读卡器芯片u7的第二供电输入引脚同时与所述第八电容c8的一端和所述第一供电电路6的第一供电输出端相连,所述读卡器芯片u7的模拟电源输入引脚同时与所述第九电容c9的一端和所述第十三电阻r13的一端相连,所述第十三电阻r13的另一端与所述第一供电电路6的第一供电输出端相连,所述读卡器芯片u7的串行输入输出引脚同时与所述第十四电阻r14和所述tf芯片u8的数据监测引脚相连,所述第十四电阻r14的另一端与所述第一供电电路6的第一供电输出端相连;

86.所述读卡器芯片u7的指示灯驱动引脚与所述第一发光二极管d1的正极相连,所述第一发光二极管d1的负极通过所述第十五电阻r15接地,所述读卡器芯片u7的dm数据传输引脚与所述第四电阻r4远离所述usb集线控制芯片u4的一端相连,所述读卡器芯片u7的dp数据传输引脚与所述第五电阻r5远离所述usb集线控制芯片u4的一端相连,所述读卡器芯片u7的时钟信号引脚与所述tf芯片u8的时钟信号引脚相连,所述读卡器芯片u7的命令和响应多路复用引脚与所述tf芯片u8的命令和响应多路复用引脚相连,所述读卡器芯片u7的数据传输引脚与所述tf芯片u8的数据传输引脚相连;

87.所述tf芯片u8的供电输入引脚同时与所述第十电容c10的一端、所述第十一电容c11的一端和所述第一供电电路6的第一供电输出端相连;

88.所述读卡器芯片u7的接地引脚、所述第七电容c7的另一端、所述第八电容c8的另一端、所述第九电容c9的另一端、所述tf芯片u8的接地引脚、所述第十电容c10的另一端和所述第十一电容c11的另一端均接地。

89.从上述描述可知,在系统中接入读卡器芯片u7和tf芯片u8,用于提供国密密码运算能力,同时也可以提供存储功能,可为用户局域网存储提供扩展空间。

90.进一步地,所述第一rj45接口电路3包括以太网芯片u9、第二晶振z2、第一参考电压dvdd33、第二参考电压dvdd12、第十六电阻r16、第十七电阻r17、第十八电阻r18、第十二电容c12、第十三电容c13、第十四电容c14、第十五电容c15、第三旁路电容、第四旁路电容和第五旁路电容;

91.所述以太网芯片u9的供电电压输入引脚同时与所述第三旁路电容的一端和所述第一供电电路6的第二供电输出端相连,所述以太网芯片u9的外部时钟输入第一引脚同时与所述第二晶振z2的第一引脚和所述第十二电容c12的一端相连,所述以太网芯片u9的外部时钟输入第二引脚同时与所述第二晶振z2的第二引脚和所述第十三电容c13的一端相连,所述以太网芯片u9的远端唤醒引脚和串行输入输出引脚分别通过所述第十六电阻r16和所述第十七电阻r17与所述第一参考电压dvdd33相连,所述以太网芯片u9的参考电压输入第一引脚与所述第一参考电压dvdd33相连,所述以太网芯片u9的参考电压输入第二引脚与所述第二参考电压dvdd12相连,所述以太网芯片u9的复位信号输入引脚通过所述第十八电阻r18接地,所述以太网芯片u9的不间断电源输入引脚同时与所述第十四电容c14的一端和所述第十五电容c15的一端相连,所述第一参考电压dvdd33与所述第四旁路电容的一端相连,所述第二参考电压dvdd12的与所述第五旁路电容的一端相连,所述以太网芯片u9的

手动数据输入引脚与手动数据输出引脚与所述主板控制芯片u1的数据发送引脚和数据接收引脚对应相连;

92.所述以太网芯片u9的接地引脚、所述第十二电容c12的另一端、所述第十三电容c13的另一端、所述第二晶振z2的接地引脚、所述第十四电容c14的另一端、第十五电容c15的另一端、所述第三旁路电路的另一端、所述第四旁路电容的另一端和所述第五旁路电容的另一端均接地。

93.从上述描述可知,通过以太网芯片u9实现usb接口至网口的转化,实现扩展网络接口,从而应用至更多的网络传输场景之中,提高系统使用的灵活性。

94.进一步地,所述第一rs485接口电路5包括异步收发器u10、rs485芯片u11、第十六电容c16、第十七电容c17、第十八电容c18、第十九电阻r19、第二十电阻r20、第二十一电阻r21、第二十二电阻r22、第二十三电阻r23、第二十四电阻r24、第二十五电阻r25、第二十六电阻r26、第二十七电阻r27、第二十八电阻r28、第二十九电阻r29、第三十电阻r30、第二发光二极管d2、第三发光二极管d3和第六旁路电容;

95.所述异步收发器u10的dp数据传输引脚与所述usb集线控制芯片u4的第三dp数据传输引脚相连,所述异步收发器u10的dm数据传输引脚与所述usb集线控制芯片u4的第三dm数据传输引脚相连,所述异步收发器u10的供电电压输入引脚同时与所述第一供电电路6的第二供电输出端和所述第十六电容c16的一端相连,所述异步收发器u10的内存控制器电压引脚与电压输出引脚均与所述第一供电电路6的第一供电输出端相连,所述异步收发器u10的串口数据发送引脚通过所述第十九电阻r19与所述rs485芯片u11的驱动器输入引脚相连,所述异步收发器u10的串口数据接收引脚通过所述第二十电阻r20与所述rs485芯片u11的接收器输出引脚相连,所述异步收发器u10的第一可配置输出引脚与所述第二十一电阻r21的一端相连,所述第二十一电阻r21的另一端同时与所述rs485芯片u11和接收使能引脚、发送使能引脚和所述第二十二电阻r22的一端相连并通过所述第二十三电阻r23连接所述主板控制芯片u1的第三串行输入输出引脚;

96.所述异步收发器u10的第二可配置输出引脚通过所述第二十四电阻r24与所述第二发光二极管d2的负极相连,所述异步收发器u10的第三可配置输出引脚通过所述第二十五电阻r25与所述第三发光二极管d3的负极相连,所述第二发光二极管d2的正极和所述第三发光二极管d3的正极均与所述第一供电电路6的第一供电输出端相连,所述异步收发器u10的复位引脚同时与所述第二十六电阻r26的一端、第二十七电阻r27的一端以及所述第十七电容c17的一端相连,所述第二十六电阻r26的另一端与所述第一供电电路6的第二供电输出端相连;

97.所述rs485芯片u11的供电输入引脚同时与所述第十八电容c18的一端和所述第一供电电路6的第二供电输出端相连,所述rs485芯片u11的差分信号发送引脚同时与所述第二十八电阻r28的一端和所述第二十九电阻r29的一端相连,所述rs485芯片u11的差分信号接收引脚同时与所述第二十九电阻r29的另一端和所述第三十电阻r30的一端相连,所述第三十电阻r30的另一端与所述第一供电电路6的第一供电输出端相连;

98.所述第一供电电路6的第一供电输出端通过所述第六旁路电容接地,所述异步收发器u10的接地引脚、所述第十六电容c16的另一端、所述第十七电容c17的另一端、所述第二十七电阻r27的另一端、所述rs485芯片u11的接地引脚、所述第二十二电阻r22的另一端、

所述第二十七电阻r27的另一端和所述第十八电容c18的另一端均接地。

99.从上述描述可知,第一rs485接口电路5主要由异步收发器u10和rs485芯片u11组成,实现rs485双工通信,适用于一些物联网终端或工控网络终端的应用场景。

100.进一步地,所述第一供电电路6包括电源管理芯片u12、电感l1、第三十一电阻r31、第三十二电阻r32、第三十三电阻r33、第三十四电阻r34、第三十五电阻r35、第三十六电阻r36、第十九电容c19、第二十电容c20、第二十一电容c21、第二十二电容c22、第二十三电容c23、第二十四电容c24、第二十五电容c25和外部电源vcc;

101.所述外部电源vcc的电压输出端同时与所述第十九电容c19的一端、所述第二十电容c20的一端、所述第三十一电阻r31的一端、所述第三十二电阻r32的一端和所述电源管理芯片u12的电压输入引脚相连,所述第三十二电阻r32的另一端与所述电源管理芯片u12的使能引脚相连,所述电源管理芯片u12的供电输入引脚与所述第二十一电容c21的一端相连,所述电源管理芯片u12的软启动引脚与所述第二十二电容c22的一端相连;

102.所述电源管理芯片u12的自举升压引脚与所述第三十三电阻r33的一端相连,所述第三十三电阻r33的另一端与所述二十三电容的一端相连,所述第二十三电容c23的另一端同时与所述电源管理芯片u12的转换引脚和所述电感l1的一端相连,所述电感l1的另一端同时与所述第三十四电阻r34的一端、所述第二十四电容c24的一端和所述第二十五电容c25的一端相连,所述第三十四电阻r34的另一端同时与所述第三十五电阻r35的一端、所述三十六电阻的一端和所述第二十四电容c24的另一端相连,所述第三十五电阻r35的另一端与所述电源管理芯片u12的反馈引脚相连;

103.所述第十九电容c19的另一端、所述第二十电容c20的另一端、所述第三十一电阻r31的另一端、所述第二十一电容c21的另一端、所述第二十二电容c22的另一端、所述电源管理芯片u12的接地引脚、所述三十六电阻的另一端和所述二十五电容的另一端均接地;

104.所述第三十四电阻r34与所述第二十五电容c25的连接处为所述第一供电电路6的第一供电输出端,所述外部电源vcc的电压输出端为所述第一供电电路6的第二供电输出端。

105.从上述描述可知,电源管理芯片u12能够对供电网络中的电能起到分配、检测等作用,以便于得到适用与本系统中的其他期器件使用的电压输出。

106.进一步地,还包括数据排座u3、子板控制芯片u2、rs485接口、第二rj45接口电路8、第二pcie接口电路9、第二供电电路14和rs232接口电路10;

107.所述主板控制芯片u1通过所述数据排座u3与所述子板控制芯片u2相连,所述子板控制芯片u2分别与所述rs232接口电路10和所述第二rj45接口电路8相连,所述rs485接口通过所述数据排座u3与所诉后第一rs485接口电路5相连,所述usb集线控制电路1通过所述数据排座u3与所述第二pcie接口电路9相连;

108.所述第二供电电路14分别与所述rs232接口电路10、第二rj45接口电路8、第二pcie接口电路9和所述子板控制芯片u2相连。

109.从上述描述可知,除了主板控制芯片u1外,本系统还通过数据排座u3和子板控制芯片u2扩展了本系统的外部接口,使得本系统能够接入更多数量和更多种类的接口。同时,同种接口之间还可根据实际需求来选择接入和实现主从互备,增加系统使用的便利性和可靠性。

110.进一步地,还包括微型usb接口电路11、第二tf卡接口电路12和开关控制电路13;

111.所述usb集线控制电路1通过所述数据排座u3与所述开关控制电路13相连,所述开关控制电路13分别与所述微型usb接口电路11和所述第二tf卡接口电路12相连;

112.所述第二供电电路14分别与所述微型usb接口电路11、所述第二tf卡接口电路12和所述开关控制电路13相连。

113.从上述描述可知,本系统中,在第二tf卡接口电路12上引入了开关控制电路13和微型usb接口电路11,以方便于在需要时通过开关控制电路13将第二tf卡接口脱离系统,并对接入的tf卡进行读写操作。

114.进一步地,所述rs232接口电路10包括rs232芯片u13、第三十七电阻r37、第三十八电阻r38、第二十六电容c26、第二十七电容c27、第二十八电容c28、第二十九电容c29、第三十电容c30、第一静电二极管d4和第二静电二极管d5;

115.所述rs232芯片u13的供电电压输入引脚同时与所述第二十六电容c26的一端和所述第二供电电路14的供电输出端相连,所述rs232芯片u13的第一外接电容正极引脚与所述第二十七电容c27的一端相连,所述第二十七电容c27的另一端与所述rs232芯片u13的第一外接电容负极引脚相连,所述rs232芯片u13的第二外接电容正极引脚与所述第二十八电容c28的一端相连,所述第二十八电容c28的另一端与所述rs232芯片u13的第二外接电容负极引脚相连,所述rs232芯片u13的电源输出正极引脚与所述第二十九电容c29的一端相连,所述rs232芯片u13的电源输出负极与所述第三十电容c30的一端相连;

116.所述rs232芯片u13的ttl数据输入引脚与所述第三十七电阻r37的一端相连,所述第三十七电阻r37的另一端与所述子板控制芯片u2的串口通信数据发送引脚相连,所述rs232芯片u13的ttl数据输出引脚与所述第三十八电阻r38的一端相连,所述第三十八电阻r38的另一端与所述子板控制芯片u2的串口通信数据接收引脚相连,所述rs232芯片u13的rs232数据输出引脚与所述第一静电二极管d4的一端相连,所述rs232芯片u13的rs232数据输入引脚与所述第二静电二极管d5的一端相连;

117.所述第二十六电容c26的另一端、所述rs232芯片u13的接地引脚、所述第二十九电容c29的另一端、所述第三十电容c30的另一端、所述第一静电二极管d4的另一端和第二静电二极管d5的另一端均接地。

118.从上述描述可知,扩展rs232接口电路10,以便于进一步地提升系统对不同工控网络的适配程度,提升用户的使用体验。

119.请参照图1,本实用新型的实施例一为:

120.一种多形态安全防护系统,如图1所示,包括主板控制芯片u1、usb集线控制电路1、第一tf卡接口电路2、第一rj45接口电路3、第一pcie接口电路4、第一rs485接口电路5和第一供电电路6。其中,主板控制芯片u1与usb集线控制电路1、第一pcie接口电路4、第一rj45接口电路3和第一rs485接口电路5相连,usb集线控制电路1分别与第一tf卡接口电路2、第一rs485接口电路5和第一pcie接口电路4相连。第一供电电路6分别与主板控制芯片u1、usb集线控制器、第一tf卡接口电路2、第一rj45接口电路3、第一pcie接口电路4和第一rs485接口电路5相连。

121.在本实施例中,主板控制芯片u1以及第一rs485接口电路5等的接口电路在获取第一供电电路6的供电电源时,可通过jack形态和凤凰端子形态的电源接口来获取。

122.在本实施例及以下实施例中,各芯片的型号及其引脚名称详见附图,本技术再次不再赘述。

123.请参照图2至图7,本实用新型的实施例二为:

124.一种多形态安全防护系统,在上述实施例一的基础上,如图2和图3所示,usb集线控制电路1包括usb集线控制芯片u4、第一晶振z1、第一电容c1、第二电容c2、第三电容c3、第四电容c4、第五电容c5、第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5、第六电阻r6、第七电阻r7、第八电阻r8、第九电阻r9、第十电阻r10和第一旁路电容。其中,usb集线控制芯片u4的供电输入引脚与第一供电电路6的第一供电输出端相连,usb集线控制芯片u4的使能数据输入引脚与主板控制芯片u1的usb数据传输引脚相连,usb集线控制芯片u4的复位引脚同时与第一电容c1的一端和第一电阻r1的一端相连,第一电阻r1的另一端与第一供电电路6的第一供电输出端相连,集线控制芯片的外部时钟输入第一引脚同时与第二电容c2的一端和第一晶振z1的第一引脚相连,集线控制芯片的外部时钟输入第二引脚同时与第三电容c3的一端和第一晶振z1的第二引脚相连。usb集线控制芯片u4的第一dm数据传输引脚和第一dp数据传输引脚分别通过第二电阻r2和第三电阻r3与第一pcie接口电路4相连,usb集线控制芯片u4的第二dm数据传输引脚和第二dp数据传输引脚分别通过第四电阻r4和第五电阻r5与第一tf卡接口电路2相连,usb集线控制芯片u4的第一表带可选引脚和第二表带可选引脚分别对应通过第六电阻r6和第七电阻r7接地;usb集线控制芯片u4的第一配置引脚和第二配置引脚分别对应通过第八电阻r8和第九电阻r9接地。usb集线控制芯片u4的偏执电阻外接引脚通过第十电阻r10接地,usb集线控制芯片u4的锁相滤波引脚通过第四电容c4接地,usb集线控制芯片u4的继电器滤波引脚通过第四电容c4接地,第一电容c1的另一端、第二电容c2的另一端、第三电容c3的另一端和第一晶振z1的接地引脚均接地,第一旁路电容的一端同时与第一供电电路6的第一供电输出端和usb集线控制芯片u4的供电输入引脚相连且另一端接地。

125.如图4所示,第一pcie接口电路4包括卡边缘连接器u5、pcie接口u6、第六电容c6、第十一电阻r11、第十二电阻r12和第二旁路电容。其中,卡边缘连接器u5的供电电压输入引脚同时与第一供电电路6的第一供电输出端和第二旁路电容的一端相连。卡边缘连接器u5的dm数据传输引脚与第二电阻r2远离usb集线控制芯片u4的一端相连,卡边缘连接器u5的dp数据传输引脚与第三电阻r3远离usb集线控制芯片u4的一端相连;

126.并且,卡边缘连接器u5的sim卡供电输出引脚同时与第六电容c6的一端和pcie接口u6的供电输入引脚相连,卡边缘连接器u5的sim卡复位控制引脚与pcie接口u6的复位信号输入引脚相连,卡边缘连接器u5的sim卡时钟控制引脚与pcie接口u6的时钟信号输入引脚相连,卡边缘连接器u5的sim卡数据传输引脚与pcie接口u6的数据传输引脚相连。卡边缘连接器u5的低电平复位引脚通过第十一电阻r11与主板控制芯片u1的第一串行输入输出引脚相连,卡边缘连接器u5的停机控制引脚通过第十二电阻r12与主板控制芯片u1的第二串行输入输出引脚相连,卡边缘连接器u5的扩展总线时钟信号引脚与主板控制芯片u1的扩展总线时钟信号引脚相连,卡边缘连接器u5的扩展总线数据发送引脚与主板控制芯片u1的数据接收引脚相连,卡边缘连接器u5的扩展总线数据接收引脚与主板控制芯片u1的数据发送引脚相连。卡边缘连接器u5的接地引脚、第六电容c6的另一端、第二旁路电容的另一端以及pcie接口u6的接地引脚均接地。并且,在本实施例中,通过pcie接口u6扩展实现sim卡接口,

接入sim卡,使得系统能够通过移动数据联网使用。

127.如图5所示,第一tf卡接口电路2包括读卡器芯片u7、tf芯片u8、第十三电阻r13、第十四电阻r14、第十五电阻r15、第七电容c7、第八电容c8、第九电容c9、第十电容c10、第十一电容c11和第一发光二极管d1。读卡器芯片u7的第一供电输入引脚同时与第七电容c7的一端和第一供电电路6的第二供电输出端相连,读卡器芯片u7的第二供电输入引脚同时与第八电容c8的一端和第一供电电路6的第一供电输出端相连,读卡器芯片u7的模拟电源输入引脚同时与第九电容c9的一端和第十三电阻r13的一端相连,第十三电阻r13的另一端与第一供电电路6的第一供电输出端相连,读卡器芯片u7的串行输入输出引脚同时与第十四电阻r14和tf芯片u8的数据监测引脚相连,第十四电阻r14的另一端与第一供电电路6的第一供电输出端相连。读卡器芯片u7的指示灯驱动引脚与第一发光二极管d1的正极相连,第一发光二极管d1的负极通过第十五电阻r15接地,读卡器芯片u7的dm数据传输引脚与第四电阻r4远离usb集线控制芯片u4的一端相连,读卡器芯片u7的dp数据传输引脚与第五电阻r5远离usb集线控制芯片u4的一端相连,读卡器芯片u7的时钟信号引脚与tf芯片u8的时钟信号引脚相连,读卡器芯片u7的命令和响应多路复用引脚与tf芯片u8的命令和响应多路复用引脚相连,读卡器芯片u7的数据传输引脚与tf芯片u8的数据传输引脚相连。tf芯片u8的供电输入引脚同时与第十电容c10的一端、第十一电容c11的一端和第一供电电路6的第一供电输出端相连。读卡器芯片u7的接地引脚、第七电容c7的另一端、第八电容c8的另一端、第九电容c9的另一端、tf芯片u8的接地引脚、第十电容c10的另一端和第十一电容c11的另一端均接地。

128.如图6所示,第一rj45接口电路3包括以太网芯片u9、第二晶振z2、第一参考电压dvdd33、第二参考电压dvdd12、第十六电阻r16、第十七电阻r17、第十八电阻r18、第十二电容c12、第十三电容c13、第十四电容c14、第十五电容c15、第三旁路电容、第四旁路电容和第五旁路电容。以太网芯片u9的供电电压输入引脚同时与第三旁路电容的一端和第一供电电路6的第二供电输出端相连,以太网芯片u9的外部时钟输入第一引脚同时与第二晶振z2的第一引脚和第十二电容c12的一端相连,以太网芯片u9的外部时钟输入第二引脚同时与第二晶振z2的第二引脚和第十三电容c13的一端相连,以太网芯片u9的远端唤醒引脚和串行输入输出引脚分别通过第十六电阻r16和第十七电阻r17与第一参考电压dvdd33相连,以太网芯片u9的参考电压输入第一引脚与第一参考电压dvdd33相连,以太网芯片u9的参考电压输入第二引脚与第二参考电压dvdd12相连,以太网芯片u9的复位信号输入引脚通过第十八电阻r18接地,以太网芯片u9的不间断电源输入引脚同时与第十四电容c14的一端和第十五电容c15的一端相连,第一参考电压dvdd33与第四旁路电容的一端相连,第二参考电压dvdd12的与第五旁路电容的一端相连,以太网芯片u9的手动数据输入引脚与手动数据输出引脚与主板控制芯片u1的数据发送引脚和数据接收引脚对应相连。以太网芯片u9的接地引脚、第十二电容c12的另一端、第十三电容c13的另一端、第二晶振z2的接地引脚、第十四电容c14的另一端、第十五电容c15的另一端、第三旁路电路的另一端、第四旁路电容的另一端和第五旁路电容的另一端均接地。

129.如图7所示,第一rs485接口电路5包括异步收发器u10、rs485芯片u11、第十六电容c16、第十七电容c17、第十八电容c18、第十九电阻r19、第二十电阻r20、第二十一电阻r21、第二十二电阻r22、第二十三电阻r23、第二十四电阻r24、第二十五电阻r25、第二十六电阻

r26、第二十七电阻r27、第二十八电阻r28、第二十九电阻r29、第三十电阻r30、第二发光二极管d2、第三发光二极管d3和第六旁路电容。其中,异步收发器u10的dp数据传输引脚与usb集线控制芯片u4的第三dp数据传输引脚相连,异步收发器u10的dm数据传输引脚与usb集线控制芯片u4的第三dm数据传输引脚相连,异步收发器u10的供电电压输入引脚同时与第一供电电路6的第二供电输出端和第十六电容c16的一端相连,异步收发器u10的内存控制器电压引脚与电压输出引脚均与第一供电电路6的第一供电输出端相连,异步收发器u10的串口数据发送引脚通过第十九电阻r19与rs485芯片u11的驱动器输入引脚相连,异步收发器u10的串口数据接收引脚通过第二十电阻r20与rs485芯片u11的接收器输出引脚相连,异步收发器u10的第一可配置输出引脚与第二十一电阻r21的一端相连,第二十一电阻r21的另一端同时与rs485芯片u11和接收使能引脚、发送使能引脚和第二十二电阻r22的一端相连并通过第二十三电阻r23连接主板控制芯片u1的第三串行输入输出引脚。异步收发器u10的第二可配置输出引脚通过第二十四电阻r24与第二发光二极管d2的负极相连,异步收发器u10的第三可配置输出引脚通过第二十五电阻r25与第三发光二极管d3的负极相连,第二发光二极管d2的正极和第三发光二极管d3的正极均与第一供电电路6的第一供电输出端相连,异步收发器u10的复位引脚同时与第二十六电阻r26的一端、第二十七电阻r27的一端以及第十七电容c17的一端相连,第二十六电阻r26的另一端与第一供电电路6的第二供电输出端相连。

130.并且,rs485芯片u11的供电输入引脚同时与第十八电容c18的一端和第一供电电路6的第二供电输出端相连,rs485芯片u11的差分信号发送引脚同时与第二十八电阻r28的一端和第二十九电阻r29的一端相连,rs485芯片u11的差分信号接收引脚同时与第二十九电阻r29的另一端和第三十电阻r30的一端相连,第三十电阻r30的另一端与第一供电电路6的第一供电输出端相连。第一供电电路6的第一供电输出端通过第六旁路电容接地,异步收发器u10的接地引脚、第十六电容c16的另一端、第十七电容c17的另一端、第二十七电阻r27的另一端、rs485芯片u11的接地引脚、第二十二电阻r22的另一端、第二十七电阻r27的另一端和第十八电容c18的另一端均接地。

131.请参照图8,本实用新型的实施例三为:

132.一种多形态安全防护系统,在上述实施例一或二的基础上,如图8所示,第一供电电路6包括电源管理芯片u12、电感l1、第三十一电阻r31、第三十二电阻r32、第三十三电阻r33、第三十四电阻r34、第三十五电阻r35、第三十六电阻r36、第十九电容c19、第二十电容c20、第二十一电容c21、第二十二电容c22、第二十三电容c23、第二十四电容c24、第二十五电容c25和外部电源vcc。其中,外部电源vcc的电压输出端同时与第十九电容c19的一端、第二十电容c20的一端、第三十一电阻r31的一端、第三十二电阻r32的一端和电源管理芯片u12的电压输入引脚相连,第三十二电阻r32的另一端与电源管理芯片u12的使能引脚相连,电源管理芯片u12的供电输入引脚与第二十一电容c21的一端相连,电源管理芯片u12的软启动引脚与第二十二电容c22的一端相连。电源管理芯片u12的自举升压引脚与第三十三电阻r33的一端相连,第三十三电阻r33的另一端与二十三电容的一端相连,第二十三电容c23的另一端同时与电源管理芯片u12的转换引脚和电感l1的一端相连,电感l1的另一端同时与第三十四电阻r34的一端、第二十四电容c24的一端和第二十五电容c25的一端相连,第三十四电阻r34的另一端同时与第三十五电阻r35的一端、三十六电阻的一端和第二十四电容

c24的另一端相连,第三十五电阻r35的另一端与电源管理芯片u12的反馈引脚相连;

133.并且,第十九电容c19的另一端、第二十电容c20的另一端、第三十一电阻r31的另一端、第二十一电容c21的另一端、第二十二电容c22的另一端、电源管理芯片u12的接地引脚、三十六电阻的另一端和二十五电容的另一端均接地。第三十四电阻r34与第二十五电容c25的连接处为第一供电电路6的第一供电输出端,外部电源vcc的电压输出端为第一供电电路6的第二供电输出端。

134.请参照图1、图9和图10,本实用新型的实施例四为:

135.一种多形态安全防护系统,在上述实施例一、二或三的基础上,如图1所示,还包括数据排座u3、子板控制芯片u2、rs485接口、第二rj45接口电路8、第二pcie接口电路9、rs232接口电路10、微型usb接口电路11、第二tf卡接口电路12、第二供电电路14和开关控制电路13。其中,主板控制芯片u1通过数据排座u3与子板控制芯片u2相连,子板控制芯片u2分别与rs232接口电路10和第二rj45接口电路8相连,rs485接口通过数据排座u3与所诉后第一rs485接口电路5相连,usb集线控制电路1通过数据排座u3与第二pcie接口电路9相连。usb集线控制电路1通过数据排座u3与开关控制电路13相连,开关控制电路13分别与微型usb接口电路11和第二tf卡接口电路12相连。第二供电电路14分别与rs232接口电路10、第二rj45接口电路8、第二pcie接口电路9、微型usb接口电路11、第二tf卡接口电路12、开关控制电路13相连和子板控制芯片u2相连。

136.如图9和图10所示,具体地,rs232接口电路10包括rs232芯片u13、第三十七电阻r37、第三十八电阻r38、第二十六电容c26、第二十七电容c27、第二十八电容c28、第二十九电容c29、第三十电容c30、第一静电二极管d4和第二静电二极管d5。rs232芯片u13的供电电压输入引脚同时与第二十六电容c26的一端和第二供电电路14的供电输出端相连,rs232芯片u13的第一外接电容正极引脚与第二十七电容c27的一端相连,第二十七电容c27的另一端与rs232芯片u13的第一外接电容负极引脚相连,rs232芯片u13的第二外接电容正极引脚与第二十八电容c28的一端相连,第二十八电容c28的另一端与rs232芯片u13的第二外接电容负极引脚相连,rs232芯片u13的电源输出正极引脚与第二十九电容c29的一端相连,rs232芯片u13的电源输出负极与第三十电容c30的一端相连。rs232芯片u13的ttl数据输入引脚与第三十七电阻r37的一端相连,第三十七电阻r37的另一端与子板控制芯片u2的串口通信数据发送引脚相连,rs232芯片u13的ttl数据输出引脚与第三十八电阻r38的一端相连,第三十八电阻r38的另一端与子板控制芯片u2的串口通信数据接收引脚相连,rs232芯片u13的rs232数据输出引脚与第一静电二极管d4的一端相连,rs232芯片u13的rs232数据输入引脚与第二静电二极管d5的一端相连。第二十六电容c26的另一端、rs232芯片u13的接地引脚、第二十九电容c29的另一端、第三十电容c30的另一端、第一静电二极管d4的另一端和第二静电二极管d5的另一端均接地。

137.综上所述,本实用新型公开了一种多形态安全防护系统。在网关设备的主板控制芯片上接入usb集线控制电路,以此扩展了第一tf卡接口电路、第一rj45接口电路以及第一pcie接口电路等多种通讯接口,实现多种不同的网络数据传输,还能够适用于仅依靠rj45传输的物联网终端或工控网络的应用场景,与不同的用户硬件设备相适配,实现了网关设备的形态多样化和连接方式多样化。

138.以上所述仅为本实用新型的实施例,并非因此限制本实用新型的专利范围,凡是

利用本实用新型说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术领域,均同理包括在本实用新型的专利保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。