rs485中继电路

技术领域

1.本实用新型涉及通讯技术领域,具体地,涉及一种rs485中继电路,尤其是一种低成本低时延高可靠性rs485中继电路。

背景技术:

2.中继器是连接网络线路的一种装置,常用于两个网络节点之间物理信号的双向转发工作,通过对数据信号的重新发送或者转发,以延长网络的传输距离。rs485中继器是rs485总线的数据中继通信产品,可以中继延长rs485总线网络的通信距离,增强rs485总线网络设备的数目,其在工业控制自动化、工业集散分布系统、道路交通控制自动化等领域均有应用。

3.随着现场控制精度要求的不断提高及数据网络设备站点的扩充,数据流、系统范围和规模不断的扩大,保证现场网络数据的稳定性、完整性及安全性变得更大重要,其直接关系到现场生产及控制情况。

4.公开号为cn205092859u的专利文献公开了一种rs485中继电路,包括:用于接收、处理数据并发送控制信号的pld,用于数据输入和输出的数据传输电路,用于防止共模电压干扰的光耦隔离单元,用于数据收发方之间的rs485协议通信的rs485接口通讯芯片组,用于切换数据传输模式以及调节数据通讯速率的拨码开关组。其中光耦隔离单元与所述pld相连接,rs485接口通讯芯片组连接在光耦隔离单元和数据传输电路之间且与pld相连接,拨码开关组与rs485接口通讯组和pld相连接。但是该专利文献仍然存在数据信号不完整和高时延的缺陷。

技术实现要素:

5.针对现有技术中的缺陷,本实用新型的目的是提供一种rs485中继电路。

6.根据本实用新型提供的一种rs485中继电路,包括rs485总线收发器电路、第一接收信号滤波延时电路、第二接收信号滤波延时电路及发送信号控制电路;

7.所述rs485总线收发器电路的第一引脚连接所述第一接收信号滤波延时电路的第一引脚,所述rs485总线收发器电路的第二引脚连接所述发送信号控制电路的第一引脚,所述rs485总线收发器电路的第三引脚连接所述发送信号控制电路的第二引脚,所述rs485总线收发器电路的第四引脚连接所述第二接收信号滤波延时电路的第一引脚;

8.所述第一接收信号滤波延时电路的第二引脚连接所述发送信号控制电路的第三引脚,所述第二接收信号滤波延时电路的第二引脚连接所述发送信号控制电路的第四引脚。

9.优选的,所述rs485总线收发器电路包括rs485收发器u3和rs485收发器u6,所述rs485收发器u3和所述rs485收发器u6用于两条总线的数据接收和发送。

10.优选的,所述第一接收信号滤波延时电路包括施密特输入或非门u1d、施密特输入非门u2d、施密特输入非门u2e、施密特输入非门u2f、滤波延时电阻r1及电容c1;

11.所述施密特输入或非门u1d的第一输入端连接所述第一接收信号滤波延时电路的第二引脚,所述施密特输入或非门u1d的第二输入端接地;

12.所述施密特输入或非门u1d的输出端连接所述滤波延时电阻r1的一端,所述滤波延时电阻r1的另一端分别连接所述电容c1的一端和所述施密特输入非门u2f的输入端;

13.所述电容c1的另一端接地;

14.所述施密特输入非门u2f的输出端连接所述施密特输入非门u2e的输入端,所述施密特输入非门u2e的输出端连接所述施密特输入非门u2d的输入端;

15.所述施密特输入非门u2d的输出端连接所述第一接收信号滤波延时电路的第一引脚。

16.优选的,所述施密特输入或非门u1d的型号为sn74hc7002n。

17.优选的,所述施密特输入非门u2d的型号为sn74hc14d、所述施密特输入非门u2e的型号为sn74hc14d,所述施密特输入非门u2f的型号为sn74hc14d。

18.优选的,所述第二接收信号滤波延时电路包括施密特输入或非门u1a、施密特输入非门u2a、施密特输入非门u2b、施密特输入非门u2c、滤波延时电路r12及电容c8;

19.所述施密特输入或非门u1a的第一输入端连接所述第二接收信号滤波延时电路的第二引脚,所述施密特输入或非门u1a的第二输入端接地;

20.所述施密特输入或非门u1a的输出端连接所述滤波延时电阻r12的一端,所述滤波延时电阻r12的另一端分别连接所述电容c8的一端和所述施密特输入非门u2a的输入端;

21.所述电容c8的另一端接地;

22.所述施密特输入非门u2a的输出端连接所述施密特输入非门u2b的输入端,所述施密特输入非门u2b的输出端连接所述施密特输入非门u2c的输入端;

23.所述施密特输入非门u2c的输出端连接所述第二接收信号滤波延时电路的第一引脚。

24.优选的,所述施密特输入或非门u1a的型号为sn74hc7002n。

25.优选的,所述施密特输入非门u2a的型号为sn74hc14d,所述施密特输入非门u2b的型号为sn74hc14d,所述施密特输入非门u2c的型号为sn74hc14d。

26.优选的,所述发送信号控制电路包括单稳态触发器u4a、单稳态触发器u4b、与门u5a、与门u5b、施密特输入或非门u1b、施密特输入或非门u1c、延时电路r6、电容c4、延时电阻r7、电容c6、延时电阻r2、电容c3、延时电阻r9及电容c7;

27.所述单稳态触发器u4a的第一引脚分别连接所述施密特输入或非门u1b的第一输入端、所述延时电阻r7的一端、所述电容c6的一端及所述发送信号控制电路的第四引脚;

28.所述单稳态触发器u4a的第二引脚分别连接所述与门u5a的第一输入端;

29.所述单稳态触发器u4a的第三引脚分别连接所述延时电阻r9的一端和所述电容c7的一端;

30.所述延时电阻r7的另一端连接外部电压,所述电容c6的另一端接地;

31.所述延时电阻r9的另一端连接外部电压,所述电容c7的另一端接地;

32.所述单稳态触发器u4b的第一引脚分别连接所述施密特输入或非门u1c的第一输入端、所述延时电阻r6的一端、所述电容c4的一端及所述发送信号控制电路的第三引脚;

33.所述单稳态触发器u4b的第二引脚分别连接所述与门u5b的第一输入端;

34.所述单稳态触发器u4a的第三引脚分别连接所述延时电阻r2的一端和所述电容c3的一端;

35.所述延时电阻r6的另一端连接外部电压,所述电容c4的另一端接地;

36.所述延时电阻r2的另一端连接外部电压,所述电容c3的另一端接地;

37.所述施密特输入或非门u1b的第二输入端分别连接所述施密特输入或非门u1c的输出端和所述与门u5b的第二输入端;所述施密特输入或非门u1b的输出端分别连接所述施密特输入或非门u1c的第二输入端和所述与门u5a的第二输入端;

38.所述与门u5a的输出端连接所述发送信号控制电路的第二引脚,所述与门u5b的输出端连接所述发送信号控制电路的第一引脚。

39.优选的,所述单稳态触发器u4a的型号为dm74ls123m,所述单稳态触发器u4b的型号为dm74ls123m;

40.所述与门u5a的型号为sn74hc08d,所述与门u5b的型号为sn74hc08d;

41.所述施密特输入或非门u1b的型号为sn74hc7002n,所述施密特输入或非门u1c的型号为sn74hc7002n。

42.与现有技术相比,本实用新型具有如下的有益效果:

43.1、本实用新型通过采用两个接收信号滤波延时电路对接收信号进行延时,延时电阻r6和电容c4,延时电阻r7和电容c6,对rs485收发器的发送控制信号de-1和de-2进行时序控制,保证了数据信号完整性和低时延;

44.2、本实用新型通过采用单稳态触发器,解决了rs485的分支总线由于总线失效总成的整个网络长时间失效的问题,增加了稳定性;

45.3、本实用新型通过采用逻辑门电路实现,未采用mcu控制模式,降低了成本。

附图说明

46.通过阅读参照以下附图对非限制性实施例所作的详细描述,本实用新型的其它特征、目的和优点将会变得更明显:

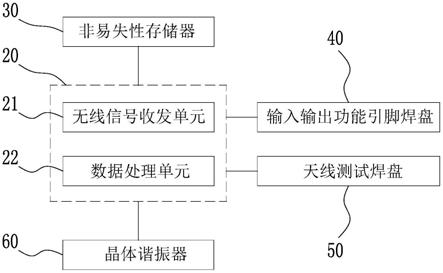

47.图1为本实用新型的rs485中继电路的结构原理图;

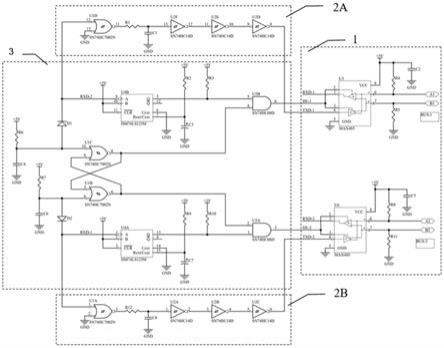

48.图2为本实用新型的rs485中继电路的原理图。

49.图中示出:

50.rs485总线收发器电路1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二接收信号滤波延时电路2b

51.第一接收信号滤波延时电路2a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

发送信号控制电路4

具体实施方式

52.下面结合具体实施例对本实用新型进行详细说明。以下实施例将有助于本领域的技术人员进一步理解本实用新型,但不以任何形式限制本实用新型。应当指出的是,对本领域的普通技术人员来说,在不脱离本实用新型构思的前提下,还可以做出若干变化和改进。这些都属于本实用新型的保护范围。

53.如图1和图2所示,本实用新型提供的一种rs485中继电路,包括rs485总线收发器电路、第一接收信号滤波延时电路、第二接收信号滤波延时电路及发送信号控制电路,rs485总线收发器电路的第一引脚连接第一接收信号滤波延时电路的第一引脚,rs485总线

收发器电路的第二引脚连接发送信号控制电路的第一引脚,rs485总线收发器电路的第三引脚连接发送信号控制电路的第二引脚,rs485总线收发器电路的第四引脚连接第二接收信号滤波延时电路的第一引脚,第一接收信号滤波延时电路的第二引脚连接发送信号控制电路的第三引脚,第二接收信号滤波延时电路的第二引脚连接发送信号控制电路的第四引脚。rs485总线收发器电路包括rs485收发器u3和rs485收发器u6,rs485收发器u3和rs485收发器u6用于两条总线的数据接收和发送。

54.发送信号控制电路包括单稳态触发器u4a、单稳态触发器u4b、与门u5a、与门u5b、施密特输入或非门u1b、施密特输入或非门u1c、延时电路r6、电容c4、延时电阻r7、电容c6、延时电阻r2、电容c3、延时电阻r9及电容c7,单稳态触发器u4a的第一引脚分别连接施密特输入或非门u1b的第一输入端、延时电阻r7的一端、电容c6的一端及发送信号控制电路的第四引脚,单稳态触发器u4a的第二引脚分别连接与门u5a的第一输入端,单稳态触发器u4a的第三引脚分别连接延时电阻r9的一端和电容c7的一端,延时电阻r7的另一端连接外部电压,电容c6的另一端接地,延时电阻r9的另一端连接外部电压,电容c7的另一端接地,单稳态触发器u4b的第一引脚分别连接施密特输入或非门u1c的第一输入端、延时电阻r6的一端、电容c4的一端及发送信号控制电路的第三引脚,单稳态触发器u4b的第二引脚分别连接与门u5b的第一输入端,单稳态触发器u4a的第三引脚分别连接延时电阻r2的一端和电容c3的一端,延时电阻r6的另一端连接外部电压,电容c4的另一端接地,延时电阻r2的另一端连接外部电压,电容c3的另一端接地,施密特输入或非门u1b的第二输入端分别连接施密特输入或非门u1c的输出端和与门u5b的第二输入端,施密特输入或非门u1b的输出端分别连接施密特输入或非门u1c的第二输入端和与门u5a的第二输入端,与门u5a的输出端连接发送信号控制电路的第二引脚,与门u5b的输出端连接发送信号控制电路的第一引脚。单稳态触发器u4a的型号为dm74ls123m,单稳态触发器u4b的型号为dm74ls123m,与门u5a的型号为sn74hc08d,与门u5b的型号为sn74hc08d,施密特输入或非门u1b的型号为sn74hc7002n,施密特输入或非门u1c的型号为sn74hc7002n。

55.第一接收信号滤波延时电路包括施密特输入或非门u1d、施密特输入非门u2d、施密特输入非门u2e、施密特输入非门u2f、滤波延时电阻r1及电容c1,施密特输入或非门u1d的第一输入端连接第一接收信号滤波延时电路的第二引脚,施密特输入或非门u1d的第二输入端接地,施密特输入或非门u1d的输出端连接滤波延时电阻r1的一端,滤波延时电阻r1的另一端分别连接电容c1的一端和施密特输入非门u2f的输入端,电容c1的另一端接地,施密特输入非门u2f的输出端连接施密特输入非门u2e的输入端,施密特输入非门u2e的输出端连接施密特输入非门u2d的输入端,施密特输入非门u2d的输出端连接第一接收信号滤波延时电路的第一引脚。施密特输入或非门u1d的型号为sn74hc7002n,施密特输入非门u2d的型号为sn74hc14d、施密特输入非门u2e的型号为sn74hc14d,施密特输入非门u2f的型号为sn74hc14d。

56.第二接收信号滤波延时电路包括施密特输入或非门u1a、施密特输入非门u2a、施密特输入非门u2b、施密特输入非门u2c、滤波延时电路r12及电容c8,施密特输入或非门u1a的第一输入端连接第二接收信号滤波延时电路的第二引脚,施密特输入或非门u1a的第二输入端接地,施密特输入或非门u1a的输出端连接滤波延时电阻r12的一端,滤波延时电阻r12的另一端分别连接电容c8的一端和施密特输入非门u2a的输入端,电容c8的另一端接

地,施密特输入非门u2a的输出端连接施密特输入非门u2b的输入端,施密特输入非门u2b的输出端连接施密特输入非门u2c的输入端,施密特输入非门u2c的输出端连接第二接收信号滤波延时电路的第一引脚。施密特输入或非门u1a的型号为sn74hc7002n,施密特输入非门u2a的型号为sn74hc14d,施密特输入非门u2b的型号为sn74hc14d,施密特输入非门u2c的型号为sn74hc14d。

57.实施例:

58.rs485中继器,包括:rs485总线收发器电路1,接收信号滤波延时电路2a和2b,发送信号控制电路3。其中rs485收发器u3,u6分别与外部2条rs485通信总线(bus-1和bus-2)相连。

59.rs485总线收发器电路1包括:2个rs485收发器,负责2条总线的数据接收和发送。

60.rs485收发器u3的接收信号rxd-1,与信号接收滤波延时电路2b中的u1a的引脚1相连,同时rxd-1还与发送信号控制电路3中的u4a的引脚1相连。rs485收发器u3的发送信号txd-1,与信号接收滤波延时电路2a中的u2d的引脚8相连。rs485收发器u3的发送控制信号de-1,与发送信号控制电路3中的u5b的引脚6相连。

61.rs485收发器u6的接收信号rxd-2,与信号接收滤波延时电路2a中的u1d的引脚12相连,同时rxd-2还与发送信号控制电路3中的u4b的引脚9相连。rs485收发器u6的发送信号txd-2,与信号接收滤波延时电路2b中的u2c的引脚6相连。rs485收发器u6的发送控制信号de-2,与发送信号控制电路3中的u5a的引脚3相连。

62.接收信号滤波延时电路2a包括:1个施密特输入或非门u1d(sn74hc7002n),3个施密特输入非门u2d、u2e、u2f(sn74hc14d),及滤波延时电路r1和c1,产生1us的延时。由于u1d的13脚为0(以下低电平简写为0,高电平简写为1),u1d的状态由12脚的状态决定,成为非门。当rxd-2(u1d的12脚)为0,u1d的输出脚11为1,通过r1对c1进行充电,当c1的电压超过u2f的门限电压(1.9v)时,u2f的输出为0,经过u2e和u2d后的输出为0。当u1d的12脚为1,u1d的输出脚11为0,通过r1对c1进行放电,当c1的电压低于u2f的门限电压(1.2v)时,u2f的输出为1,经过u2e和u2d后的输出为1。

63.接收信号滤波延时电路2b包括:1个施密特输入或非门u1a(sn74hc7002n),3个施密特输入非门u2a、u2b、u2c(sn74hc14d),及滤波延时电路r12和c8,产生1us的延时。控制原理同接收信号滤波延时电路2a。

64.发送信号控制电路3包括:2个可重复触发单稳态触发器u4a,u4b(dm74ls123m),2个与门u5a,u5b(sn74hc08d),2个由施密特输入或非门u1b和u1c(sn74hc7002n)组成的rs触发器,延时电路r6和c4(产生40us的延时),延时电路r7和c6(产生40us的延时),延时电路r2和c3(产生2.5s的延时),延时电路r9和c7(产生2.5s的延时)。

65.工作原理:

66.初始上电情况下,当2条rs485总线没有数据时,rxd-1和rxd-2均为1,此时单稳态触发器u4a,u4b的低电平输入脚a(u4a的引脚1,u4b的引脚9)也为1,由于单稳态触发器u4a,u4b的输入脚b(u4a的引脚2,u4b的引脚10)和复位引脚clr(u4a的引脚3,u4b的引脚11)都接入高电平,则单稳态触发器输出q(u4a的引脚13,u4b的引脚5)为0。电容c4和c6,经过电阻短暂充电40us后处于高电平,则由u1b和u1c组成的rs触发器的输入(u1b的引脚4,u1c的引脚10)均为1,输出(u1b的引脚6,u1c的引脚8)均为0。由于与门u5a和u5b的输入脚(u5a的引脚1

和2,u5b的引脚4和5)均为0,则输出(u5a的引脚3,u5b的引脚6)均为0。rs485收发器的发送控制信号de-1和de-2均为0,收发器处于接收禁止发送状态。rs485收发器接收到数据时,以u3为例。u3由总线bus-1的接收到数据,当rxd-1为负跳变为低电平时,可重复单稳态触发器u4a被触发,输出2.5s的高电平脉冲。同时电容c6经二极管d2快速放电至低电平,由u1b和u1c组成的rs触发器的输出(u1b的引脚6)输出为1,经过与门u5a输出1,de-2为1,u6开始发送数据。由于接收信号滤波延时电路2b的延时作用,发送信号txd-2经过1us后才会变为低电平,保证了数据低电平的前沿的完整性。当rxd-1为正跳变为高电平时,可重复单稳态触发器未被触发,继续输出高电平脉冲,直到最后一个rxd-1的负跳变2.5后,输出为0,防止了由于rs485分支总线的失效,导致整个网络长时间失效。同时电容c6经r7充电40us至高电平,由u1b和u1c组成的rs触发器的输出(u1b的引脚6)输出为0,经过与门u5a输出0,de-2为0,u6停止发送数据,保证了数据低电平的后沿的完整性。

67.本实用新型采用逻辑门电路产生低时延控制信号,确保rs485总线数据的安全传输。

68.在本技术的描述中,需要理解的是,术语“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

69.以上对本实用新型的具体实施例进行了描述。需要理解的是,本实用新型并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变化或修改,这并不影响本实用新型的实质内容。在不冲突的情况下,本技术的实施例和实施例中的特征可以任意相互组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。