1.本发明涉及一种封装结构及其制造方法,尤其涉及一种集成多个芯片的封装结构及其制造方法。

背景技术:

2.为了使得电子产品能达到轻薄短小的设计,半导体封装技术亦跟着日益进展,以发展出符合小体积、重量轻、高密度以及在市场上具有高竞争力等要求的产品。因此,如何集成多个芯片,以提升封装结构的效能,实已成重要的课题之一。

技术实现要素:

3.本发明提供一种封装结构,其具有更好的质量。

4.本发明提供一种封装结构的制造方法,其具有更好的良率或较低的成本。

5.本发明的封装结构包括桥接芯片、硅穿孔芯片、第一模封体、第一有源芯片、第二有源芯片、第二模封体以及重布线路结构。第一模封体覆盖硅穿孔芯片及桥接芯片。第一有源芯片电连接于桥接芯片及硅穿孔芯片。第二有源芯片电连接于桥接芯片。第二模封体覆盖第一有源芯片及第二有源芯片。重布线路结构电连接于硅穿孔芯片。硅穿孔芯片位在第一有源芯片及重布线路结构之间。

6.本发明的封装结构的制造方法包括以下步骤。提供硅穿孔芯片及桥接芯片。形成覆盖硅穿孔芯片及桥接芯片的第一模封体。形成电连接于硅穿孔芯片的重布线路结构。配置电连接于桥接芯片及硅穿孔芯片的第一有源芯片。配置电连接于桥接芯片的第二有源芯片。形成覆盖第一有源芯片及第二有源芯片的第二模封体。在形成重布线路结构的步骤及配置第一有源芯片的步骤之后,硅穿孔芯片位在第一有源芯片及重布线路结构之间。

7.基于上述,本发明的封装结构可以集成(integrated)多个有源芯片。多个有源芯片之间可以通过桥接芯片彼此电连接,且有源芯片可以通过硅穿孔芯片与重布线路结构电连接。如此一来,可以提升封装结构的质量。并且,在封装结构的制造方法上,可以先将桥接芯片与硅穿孔芯片以第一模封体,再配置电连接至桥接芯片或硅穿孔芯片的有源芯片。如此一来,封装结构的制造良率可以提升,或可以使封装结构的制造成本降低

8.本发明提供一种封装结构及其制造方法,其可以具有较佳的效能。

9.本发明的封装结构包括第一芯片、第二芯片、模封体、阻挡结构、透光片、导电连接件、第一线路层以及导电端子。第一芯片包括第一有源面以及相对于第一有源面的第一背面。第一有源面具有感测区。第二芯片包括第二有源面以及相对于第二有源面的第二背面。第二芯片以其第二背面面向第一芯片的第一背面的方式配置。模封体覆盖第二芯片。模封体具有第一模封面及相对于第一模封面的第二模封面。阻挡结构位于第一模封面上且暴露出第一芯片的感测区。透光片位于阻挡结构上。导电连接件贯穿模封体。第一线路层位于第二模封面上。第一芯片经由导电连接件及第一线路层电连接第二芯片。导电端子配置于第一线路层上。

10.本发明的封装结构的制造方法包括以下步骤:提供晶圆,其包括有源面,其中有源面具有感测区;形成阻挡结构于晶圆的有源面上;配置透光片于阻挡结构上;对晶圆形成穿硅导通孔,且于晶圆相对于有源面的背面上形成电连接穿硅导通孔的线路层;形成覆盖穿硅导通孔的介电层;于介电层上形成导电连接件;于介电层上配置第二芯片;于介电层上形成覆盖第二芯片的模封体;于模封体上形成第一线路层,且第一芯片经由导电连接件及第一线路层电连接第二芯片;以及形成导电端子于第一线路层上。

11.本发明的封装结构的制造方法包括以下步骤:于载板上形成导电连接件;于载板上配置第一芯片,其包括第一有源面以及相对于第一有源面的第一背面,其中第一有源面具有感测区,且第一芯片以其第一有源面面向载板的方式配置;于第一芯片上配置第二芯片,其包括第二有源面以及相对于第二有源面的第二背面,且第二芯片以其第二背面面向第一芯片的第一背面的方式配置;于载板上形成模封体,其覆盖第一芯片及第二芯片;于模封体上形成第二线路层;于形成模封体之后,使载板与第一芯片分离,以暴露出第一有源面;于模封体上形成阻挡结构,且阻挡结构暴露出感测区;以及配置透光片于阻挡结构上。

12.基于上述,本发明的制造方法及对应的结构可以将适于感测的第一芯片及适于数据处理的第二芯片集成于一封装结构中。如此一来,可以提升封装结构的感测处理效能。

附图说明

13.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

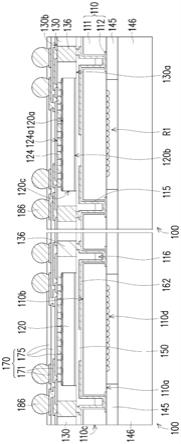

14.图1a至图1h是依照本发明的第一实施例的一种封装结构的制造方法的部分剖视示意图;

15.图2a至图2h是依照本发明的第二实施例的一种封装结构的制造方法的部分剖视示意图。

16.附图标号说明

17.100、200:封装结构;

18.119、119’:晶圆;

19.110、120、210:芯片;

20.110a、110b、110c、120a、120b、120c、210a、210b:面;

21.110d、210d:感测区;

22.111、111’、121:基材;

23.112、122、212:芯片连接垫;

24.123:芯片绝缘层;

25.124:芯片连接件;

26.124a:表面;

27.115:穿硅导通孔;

28.115e:绝缘层;

29.115f、162f:导电层;

30.116:气隙;

31.130:模封体;

32.130a、130b:模封面;

33.136:导电连接件;

34.145:阻挡结构;

35.146:透光片;

36.150:介电层;

37.170:重布线路结构;

38.171:线路层或导电层;

39.175:绝缘层;

40.162、262:线路层;

41.181、281:黏着材;

42.186:导电端子;

43.r1、r2:封闭空间;

44.91、93:载板;

45.92、94:离型层。

具体实施方式

46.除非另有明确说明,本文所使用的方向用语(例如,上、下、右、左、前、后、顶部、底部)仅作为参看所绘附图使用且不意欲暗示绝对定向。另外,为求清楚表示,在附图中可能省略示出了部分的膜层或构件。

47.除非另有明确说明,否则本文所述任何方法绝不意欲被解释为要求按特定顺序执行其步骤。

48.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。然而,本发明亦可以各种不同的形式体现,而不应限于本文中所述的实施例。附图中的层或区域的厚度、尺寸或大小会为了清楚起见而放大。相同或相似的附图标号表示相同或相似的组件,以下段落将不再一一赘述。

49.图1a至图1h是依照本发明的第一实施例的一种封装结构的制造方法的部分剖视示意图。

50.请参照图1a,提供晶圆119’。晶圆119’可以被置于载板(未示出)上,但本发明不限于此。

51.晶圆119’可以包括硅基材111’以及多个芯片连接垫(die pad)112。芯片连接垫112例如是铝垫、铜垫或其他适宜的金属垫,但本发明不限于此。

52.基材111’的一侧具有组件区(未示出),而组件区所位于的表面可以被称为有源面(active surface)110a。芯片连接垫112可以位于有源面110a上。在一般芯片设计中,组件区内的组件(如:晶圆119’中组件区内的组件)可以经由对应的后段金属内联机(back end of line interconnect;beol interconnect)电连接于对应的芯片连接垫(如:晶圆119’中的部分芯片连接垫112)。有源面110a具有感测区110d。感测区110d中可以具有对应的感测组件。感测组件例如是互补式金属氧化物半导体图像传感器(cmos image sensor;cis),但本发明不限于此。

53.请继续参照图1a,形成绝缘的阻挡结构145于晶圆119’的有源面110a上。阻挡结构

145可以经由涂布、印刷、光刻或其他适宜的方式形成,在本发明并不加以限制。

54.请参照图1a至图1b,配置透光片146于阻挡结构145上。

55.在本实施例中,配置透光片146于阻挡结构145上的步骤可以于第一环境气压下进行。举例而言,配置透光片146于阻挡结构145上的步骤可以于腔体(未示出)内进行,而腔体内具有对应的第一环境气压。

56.在一实施例中,第一环境气压小于一大气压。如此一来,在后续的步骤或结构中,可以经由气压差而使透光片146与阻挡结构145之间的接触更为紧密。

57.请参照图1b至图1c,对晶圆119(标示于图1c)形成穿硅导通孔(through silicon via;tsv)115,且于晶圆119相对于有源面110a的背面110b上形成电连接穿硅导通孔115的线路层162。

58.在本实施例中,可以对晶圆119’的硅基材111’(标示于图1b)进行薄化工艺,然后,从薄化后的硅基材111(标示于图1c)的背面110b上形成穿硅导通孔115及对应的线路层162(可以被称为:第二线路层)。

59.举例而言,可以先对硅基材111’(标示于图1b)进行薄化工艺。然后,可以经由蚀刻或其他适宜的方式,从薄化后的硅基材111(标示于图1c)的背面110b形成暴露出芯片连接垫112的开口。然后,可以经由沉积、蚀刻和/或其他适宜的方式,以形成对应的绝缘层115e。绝缘层115e可以覆盖基材111的背面110b以及开口的侧壁,且绝缘层115e可以暴露出芯片连接垫112。然后,可以经由沉积、镀覆、蚀刻和/或其他适宜的方式,以形成对应的导电层115f、162f。导电层115f、162f例如包括对应的种子层及对应的镀覆层,但本发明不限于此。位于开口内的部分导电层115f及对应的绝缘层115e可以被称为穿硅导通孔115。位于基材111的背面110b上的部分导电层162f可以被称为线路层162。也就是说,穿硅导通孔115中可以导电的一部分及线路层162中可以导电的一部分可以为相同的膜层。另外,线路层162中的版图设计(layout design)可以依据设计上的需求而加以调整,在本发明并不加以限定。

60.在本实施例中,绝缘层115e及导电层115f未完全地填满暴露出芯片连接垫112的开口。

61.请参照图1c至图1d,形成介电层150。介电层150可以覆盖穿硅导通孔115且暴露出部分的线路层162。在本实施例中,可以经由涂布的方式于基材111的背面110b上形成对应的有机介电材(如:聚酰亚胺(polyimide;pi),但不限)。然后,可以经由适当的固化方式(如:照光、加热和/或静置一段时间),以使前述的有机介电材形成图案化的介电层150。

62.在本实施例中,图案化的介电层150可以部分地填入且未完全地填满基材111的开口。也就是说,至少一气隙(gas gap)116嵌于穿硅导通孔115内。举例而言,形成覆盖穿硅导通孔115的介电层150的步骤(如:于基材的背面上形成有机介电材的步骤)可以于第二环境气压下进行,且第二环境气压例如为室压(如:约一大气压)。如此一来,可以较为容易且/或快速地形成介电层150。也就是说,经由上述的方式,气隙116的压力也大致上约为第二环境气压。

63.在一实施例中,用于形成介电层150的有机介电材可能被溶于适宜的溶剂中;或是,在适宜的溶剂中进行适当的反应(如:缩合聚合)而成。前述的溶剂例如为二甲基甲酰胺(dimethylformamide)、二甲基亚砜(dimethyl sulfoxide;dmso)或其他适宜的有机溶剂。因此,在形成介电层150的过程中(如:进行前述的固化步骤时),部分的有机溶剂分子可能

会留存于气隙116内。

64.在一实施例中,介电层150可以被称为钝化层(passivation layer),但本发明不限于此。

65.请继续参照图1d,在介电层150上形成导电连接件136。导电连接件136可以电连接于线路层162中对应的线路。

66.在一实施例中,导电连接件136可以经由适宜的方式(如:光刻及镀覆,但不限)形成,但本发明不限于此。在一实施例中,导电连接件136可以是预先成形(pre-formed)的导电件。

67.请参照图1e,在介电层150上配置第二芯片120。在本实施例中,第二芯片120可以包括硅基材121、多个芯片连接垫122、芯片绝缘层123以及多个芯片连接件124。硅基材121的一侧具有组件区(未示出),而组件区所位于的表面可以被称为第二有源面120a。相对于第二有源面120a的表面可以被称为第二背面120b。第二芯片120以其第二背面120b面向晶圆119的方式配置。芯片连接垫122可以位于第二有源面120a上。芯片连接件124例如是金属凸块(metal bumps),但本发明不限于此。芯片连接件124位于对应的芯片连接垫122上且与其电连接。芯片绝缘层123可以覆盖芯片连接垫122,且芯片绝缘层123暴露出芯片连接垫122的一部分。在芯片设计中,组件区内的组件(如:第二芯片120的组件区内的组件)可以经由对应的后段金属内联机电连接于对应的芯片连接垫(如:第二芯片120的部分芯片连接垫122)。

68.在一实施例中,第二芯片120可以包括图像信号处理器(image signal processor;isp),但本发明不限于此。

69.值得注意的是,在所示出的实施例中,是先于介电层150上形成导电连接件136,然后,在介电层150上配置第二芯片120,但本发明不限于此。在一未示出的实施例中,可以先于介电层150上配置第二芯片120,然后,在介电层150上形成导电连接件136。

70.在一实施例中,第二芯片120的第二背面120b上可以具有黏着材181。黏着材181可以包括晶粒黏着膜(die attached film;daf),但本发明不限于此。

71.请参照图1e至图1f,在介电层150上形成模封体130。模封体130可以覆盖第二芯片120。

72.在一实施例中,可以于介电层150上形成模封材料(molding material;未示出)。并且,在将模封材料固化之后,可以进行平整化工艺,以形成模封体130。平整化工艺例如可以是研磨(grinding)、抛光(polishing)或其他适宜的平整化步骤。模封体130可以暴露出第二芯片120的芯片连接件124的上表面124a。也就是说,模封体130的模封面130b可以与第二芯片120的芯片连接件124的上表面124a共面(coplanar)。

73.在一实施例中,由于第二芯片120的第二有源面120a上具有芯片连接件124,因此,在进行前述平整化步骤时可以降低对第二芯片120的第二有源面120a造成损伤的可能。

74.请参照图1f至图1g,在模封体130上形成重布线路结构170。重布线路结构170包括对应的导电层171(可以被称为第一线路层)及对应的绝缘层175。贯穿部分绝缘层175的部分导电层171可以被称为导电孔(conductive via)。导电层171所构成的线路的版图设计(layout design)可以依据设计上的需求而加以调整,在本发明并不加以限定。晶圆119中的电子组件与第二芯片120之间可以经由重布线路结构170中对应的线路、对应的导电连接

件136及第一线路层171中对应的线路而电连接。

75.请参照图1g至图1h,形成导电端子186于第一线路层171上且与第一线路层171中对应的线路电连接。导电端子186可以包括焊球,但本发明不限于此。

76.请继续参照图1g至图1h,可以进行单一化(singulation)工艺,以获得多个第一芯片110。切单工艺例如包括以旋转刀片或激光束对晶圆119(标示于图1g)进行切割。在一实施例中,前述的单一化工艺还可以对重布线路结构170、模封体130、阻挡结构145和/或透光片146进行。

77.值得注意的是,在进行单一化工艺之后,相似的组件符号将用于单一化后的组件。举例而言,晶圆119中对应的结构(如图1g中的感测区110d、硅导通孔115、气隙116或其他类似物)于单体化后可以为多个第一芯片110中对应的结构(如图1h中的感测区110d、硅导通孔115、气隙116或其他类似物),第二芯片120(如图1g所示)于单体化后可以为多个第二芯片120(如图1h所示),模封体130(如图1g所示)于单体化后可以为多个模封体130(如图1h所示),阻挡结构145(如图1g所示)于单体化后可以为多个阻挡结构145(如图1h所示),透光片146(如图1g所示)于单体化后可以为多个透光片146(如图1h所示),诸如此类。其他单体化后的组件将依循上述相同的组件符号规则,在此不加以赘述。另外,为求清楚表示,在图1h中并未一一地标示所有的组件。

78.值得注意的是,在所示出的实施例中,是先形成导电端子186,然后,进行前述的单一化工艺,但本发明不限于此。在一未示出的实施例中,可以先进行前述的单一化工艺,然后,形成导电端子186。

79.请参照图1h,经过上述工艺后即可大致上完成本实施例的封装结构100的制作。封装结构100包括第一芯片110、第二芯片120、模封体130、阻挡结构145、透光片146、导电连接件136、第一线路层171以及导电端子186。第一芯片110包括第一有源面110a、第一背面110b以及第一侧面110c。第一背面110b相对于第一有源面110a。第一侧面110c连接第一有源面110a及第一背面110b。第一有源面110a具有感测区110d。第二芯片120包括第二有源面120a、第二背面120b以及第二侧面120c。第二背面120b相对于第二有源面120a。第二侧面120c连接第二有源面120a及第二背面120b。第二芯片120以其第二背面120b面向第一芯片110的第一背面110b的方式配置。模封体130覆盖第二芯片120的第二侧面120c和/或部分的第二有源面120a。模封体130具有第一模封面130a及相对于第一模封面130a的第二模封面130b。阻挡结构145位于第一模封面130a上,或是,还位于第一芯片110的第一有源面110a上。阻挡结构145暴露出第一芯片110的感测区110d。透光片146位于阻挡结构145上。导电连接件136贯穿模封体130。第一线路层171位于第二模封面130b上。第一芯片110经由导电连接件136及第一线路层171电连接第二芯片120。导电端子186,配置于第一线路层171上。

80.在本实施例中,第二芯片120的第二有源面120a上还具有芯片连接件124。芯片连接件124的表面124a与第二模封面130b共面。

81.在本实施例中,封装结构100还包括第二线路层162。第二线路层162位于第一模封面130a上。第一芯片110经由第二线路层162、导电连接件136及第一线路层171电连接第二芯片120。

82.在本实施例中,第一芯片110还包括穿硅导通孔115,且第一芯片110的穿硅导通孔115电连接于第二线路层162。

83.在本实施例中,第二线路层162还位于第一芯片110及第二芯片120之间。

84.在本实施例中,封装结构100还包括介电层150。介电层150位于线路层上且覆盖穿硅导通孔115。至少一气隙116嵌于穿硅导通孔115内。在一实施例中,位于不同的穿硅导通孔115内的气隙116可以具有不同的大小和/或形貌。

85.在本实施例中,第一芯片110、阻挡结构145及透光片146构成封闭空间r1。在一实施例中,气隙116内的气压大于或等于一封闭空间r1内的气压。在一实施例中,封闭空间r1内的气压小于一大气压。

86.图2a至图2h是依照本发明的第二实施例的一种封装结构的制造方法的部分剖视示意图。

87.请参照图2a,提供第一载板91。本发明对于第一载板91并无特别的限制,只要第一载板91可以适于承载形成于其上膜层或配置于其上的组件即可。

88.在本实施例中,第一载板91上可以具有离型层92,但本发明不限于此。离型层92例如是光热转换(light to heat conversion;lthc)黏着层或其他类似的膜层,但本发明不限于此。

89.请继续参照图2a,在第一载板91上形成导电连接件136。

90.请继续参照图2a,在第一载板91上配置第一芯片210。第一芯片210包括第一有源面210a以及相对于第一有源面210a的第一背面210b。第一有源面210a具有感测区210d。第一芯片210可以包括硅基材211以及多个芯片连接垫212。芯片连接垫212可以位于有源面210a上。第一芯片210以其第一有源面210a面向第一载板91的方式配置。

91.值得注意的是,本发明并未限定形成导电连接件136的步骤及配置第一芯片210的步骤的先后顺序。

92.请参照图2a至图2b,在第一芯片210上配置第二芯片120。第二芯片120以其第二背面120b面向第一芯片210的第一背面210b的方式配置。

93.在一实施例中,第一芯片210的第一背面210b与第二芯片120的第二背面120b之间可以具有黏着材281。黏着材281可以包括晶粒黏着膜,但本发明不限于此。

94.值得注意的是,本发明并未限定形成导电连接件136的步骤及配置第二芯片120的步骤的先后顺序。

95.值得注意的是,在所示出的实施例中,是先形成导电连接件136,然后,在第一芯片210上配置第二芯片120,但本发明不限于此。在一未示出的实施例中,可以先于第一芯片210上配置第二芯片120,然后,形成导电连接件136。

96.请参照图2b至图2c,在第一载板91上形成模封体130,其覆盖第一芯片210及第二芯片120。模封体130可以暴露出第二芯片120的芯片连接件124的上表面124a。

97.值得注意的是,在所示出的实施例中,是先形成导电连接件136,然后,形成覆盖第一芯片210及第二芯片120的模封体130,但本发明不限于此。在一未示出的实施例中,可以先形成覆盖第一芯片210及第二芯片120的模封体130,然后,例如经由钻孔/蚀刻以及镀覆的方式形成贯穿模封体130的导电连接件136。

98.请参照图2c至图2d,在模封体130上形成重布线路结构170。重布线路结构170中对应的线路可以电连接于对应的导电连接件136和/或第二芯片120。

99.请参照图2d至图2e,在形成模封体130之后,可以不限顺序地将图2d所示出的结构

上下翻转及置于第二载板93(标示于图2e)上,然后,使第一载板91(标示于图2d)与第一芯片210分离,以暴露出第一芯片210的第一有源面210a,而构成如图2e所示出的结构。

100.本发明对于第二载板93并无特别的限制,只要第二载板93可以适于承载形成于其上膜层或配置于其上的组件即可。在本实施例中,第二载板93上可以具有离型层94,但本发明不限于此。

101.请继续参照图2e,在模封体130上形成第二线路层262。第二线路层262的对应线路可以电连接于对应的芯片连接垫212。因此,第一芯片210及第二芯片120之间可以经由重布线路结构170中对应的线路、导电连接件136及第二线路层262而电连接。

102.请参照图2e至图2f,在模封体130上形成阻挡结构145。阻挡结构145暴露出第一有源面210a中的感测区210d。

103.请参照图2f至图2g,配置透光片146于阻挡结构145上,然后,使第二载板93与重布线路结构分离。

104.值得注意的是,在所示出的实施例中,是先将透光片146配置于阻挡结构145上,然后,使第二载板93与重布线路结构分离,但本发明不限于此。

105.请参照图2g至图2h,形成导电端子186于第一线路层171上且与第一线路层171中对应的线路电连接。

106.请参照图2g至图2h,可以至少对图2g所示出的结构进行单一化工艺。值得注意的是,在进行单一化工艺之后,相似的组件符号将用于单一化后的组件,在此不加以赘述。另外,为求清楚表示,在图2h中并未一一地标示所有的组件。

107.值得注意的是,本发明并未限定形成导电端子186的步骤及进行单一化工艺的先后顺序。

108.值得注意的是,在所示出的实施例中,可以是先使第二载板93与重布线路结构分离,然后,进行单一化工艺,但本发明不限于此。在一未示出的实施例中,可以先进行单一化工艺,然后,使第二载板93与单一化后的多个结构分离。

109.请参照图2h,经过上述工艺后即可大致上完成本实施例的封装结构200的制作。封装结构200包括第一芯片210、第二芯片120、模封体130、阻挡结构145、透光片146、导电连接件136、第一线路层171以及导电端子186。第一芯片210包括第一有源面210a、第一背面210b以及第一侧面210c。第一背面210b相对于第一有源面210a。第一侧面210c连接第一有源面210a及第一背面210b。第一有源面210a具有感测区210d。第二芯片120以其第二背面120b面向第一芯片210的第一背面210b的方式配置。模封体130覆盖第一芯片210及第二芯片120。阻挡结构145暴露出第一芯片210的感测区210d。第一芯片210经由导电连接件136及第一线路层171电连接第二芯片120。导电端子186,配置于第一线路层171上。

110.在本实施例中,封装结构200还包括第二线路层262。第二线路层262位于第一模封面130a上。阻挡结构145可以更暴露出第二线路层262。第一芯片210经由第二线路层262、导电连接件136及第一线路层171电连接所述第二芯片120。第一芯片210、第二线路层262、阻挡结构145及透光片146构成封闭空间r2。

111.综上所述,本发明的制造方法及对应的结构可以将适于感测的第一芯片及适于数据处理的第二芯片集成于一封装结构中。如此一来,可以提升封装结构的感测处理效能。

112.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽

管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。