1.本公开涉及计算机技术领域,尤其涉及一种数据处理方法及装置以及相关产品。

背景技术:

2.随着人工智能技术的不断发展,需要处理的数据量和数据维度都在不断增大。在相关技术中,处理器通常通过获取指令的参数来确定数据地址,然后根据数据地址完成数据的读取和使用。这就要求技术人员在设计参数时设定数据存取的相关参数(例如数据之间或数据维度之间的相互关系等),在判断指令之间的数据冲突时,需要经过换算,该方式降低了处理器的处理效率。

技术实现要素:

3.有鉴于此,本公开提出了一种数据处理技术方案。

4.根据本公开的一方面,提供了一种数据处理方法,包括:获取第一处理指令操作数中的第一描述符,所述第一描述符包括第一内容,所述第一内容用于指示张量的形状;

5.根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令;

6.在确定不执行所述第一处理指令时,阻塞或缓存所述第一处理指令。

7.根据本公开的另一方面,提供了一种数据处理装置,包括:描述符获取电路,用于获取第一处理指令操作数中的第一描述符,所述第一描述符包括第一内容,所述第一内容用于指示张量的形状;

8.确定电路,用于根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令;

9.执行电路,用于在确定不执行所述第一处理指令时,阻塞或缓存所述第一处理指令。根据本公开的另一方面,提供了一种神经网络芯片,所述芯片包括如上所述的数据处理装置。

10.根据本公开的另一方面,提供了一种电子设备,所述电子设备包括如上所述的神经网络芯片。

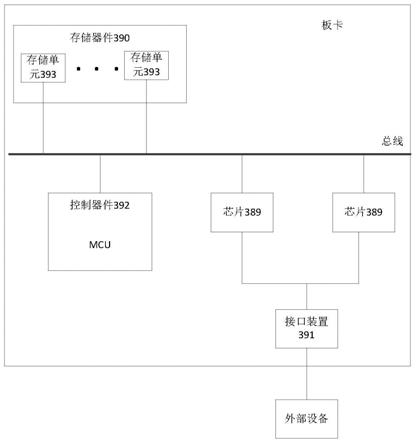

11.根据本公开的另一方面,提供了一种板卡,所述板卡包括:存储器件、接口装置和控制器件以及如上所述的神经网络芯片;其中,所述神经网络芯片与所述存储器件、所述控制器件以及所述接口装置分别连接;所述存储器件,用于存储数据;所述接口装置,用于实现所述神经网络芯片与外部设备之间的数据传输;所述控制器件,用于对所述神经网络芯片的状态进行监控。

12.根据本公开的实施例,通过引入指示张量形状的描述符,能够快速判断指令之间是否存在数据冲突,高效快速地实现指令乱序功能,提高处理器的处理效率。

13.根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

附图说明

14.包含在说明书中并且构成说明书的一部分的附图与说明书一起示出了本公开的示例性实施例、特征和方面,并且用于解释本公开的原理。

15.图1示出根据本公开实施例的数据处理装置的数据存储空间的示意图。

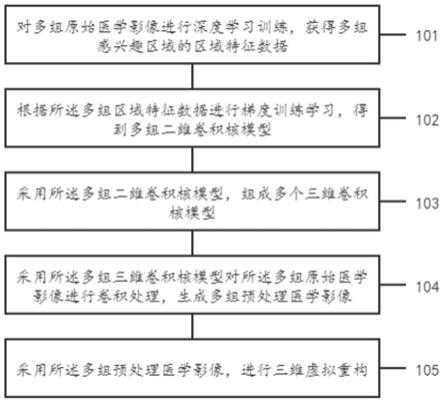

16.图2示出根据本公开实施例的数据处理方法的流程图。

17.图3示出根据本公开实施例的数据处理装置的框图。

18.图4示出根据本公开实施例的板卡的结构框图。

具体实施方式

19.以下将参考附图详细说明本公开的各种示例性实施例、特征和方面。附图中相同的附图标记表示功能相同或相似的元件。尽管在附图中示出了实施例的各种方面,但是除非特别指出,不必按比例绘制附图。

20.在这里专用的词“示例性”意为“用作例子、实施例或说明性”。这里作为“示例性”所说明的任何实施例不必解释为优于或好于其它实施例。

21.另外,为了更好的说明本公开,在下文的具体实施方式中给出了众多的具体细节。本领域技术人员应当理解,没有某些具体细节,本公开同样可以实施。在一些实例中,对于本领域技术人员熟知的方法、手段、元件和电路未作详细描述,以便于凸显本公开的主旨。

22.在一种可能的实现方式中,可以用描述符指示n维的张量数据的形状,n为正整数,例如n=1、2或3。其中,张量可以包含多种形式的数据组成方式,张量可以是不同维度的,比如标量可以看作是0维张量,向量可以看作1维张量,而矩阵可以是2维或2维以上的张量。张量的形状包括张量的维度、张量各个维度的尺寸等信息。举例而言,对于张量:

[0023][0024]

该张量的形状可以被描述符描述为(2,4),也即通过两个参数表示该张量为二维张量,且该张量的第一维度(列)的尺寸为2、第二维度(行)的尺寸为4。需要说明的是,本技术对于描述符指示张量形状的方式并不做限定。

[0025]

在一种可能的实现方式中,n的取值可根据张量数据的维数(阶数)来确定,也可以根据张量数据的使用需要进行设定。例如,在n的取值为3时,张量数据为三维的张量数据,描述符可用来指示该三维的张量数据在三个维度方向上的形状(例如偏移量、尺寸等)。应当理解,本领域技术人员可以根据实际需要对n的取值进行设置,本公开对此不作限制。

[0026]

在一种可能的实现方式中,所述描述符可包括描述符的标识和/或描述符的内容。其中,描述符的标识用于对描述符进行区分,例如描述符的标识可以为其编号;描述符的内容可以包括表示张量数据的形状的至少一个形状参数。例如,张量数据为3维数据,在该张量数据的三个维度中,其中两个维度的形状参数固定不变,其描述符的内容可包括表示该张量数据的另一个维度的形状参数。

[0027]

在一种可能的实现方式中,描述符的标识和/或内容可存储在描述符存储空间(内部存储器),例如寄存器、片上的sram或其他介质缓存等。描述符所指示的张量数据可存储在数据存储空间(内部存储器或外部存储器),例如片上缓存或片下存储器等。本公开对描述符存储空间及数据存储空间的具体位置不作限制。

[0028]

在一种可能的实现方式中,描述符的标识、内容以及描述符所指示的张量数据可以存储在内部存储器的同一块区域,例如,可使用片上缓存的一块连续区域来存储描述符的相关内容,其地址为addr0-addr1023,其中,可将地址addr0-addr63作为描述符存储空间,存储描述符的标识和内容,地址addr64-addr1023作为数据存储空间,存储描述符所指示的张量数据。在描述符存储空间中,可用地址addr0-addr31存储描述符的标识,地址addr32-addr63存储描述符的内容。应当理解,地址addr并不限于1位或一个字节,此处用来表示一个地址,是一个地址单位。本领域技术人员可以实际情况确定描述符存储空间、数据存储空间以及其具体地址,本公开对此不作限制。

[0029]

在一种可能的实现方式中,描述符的标识、内容以及描述符所指示的张量数据可以存储在内部存储器的不同区域。例如,可以将寄存器作为描述符存储空间,在寄存器中存储描述符的标识及内容,将片上缓存作为数据存储空间,存储描述符所指示的张量数据。

[0030]

在一种可能的实现方式中,在使用寄存器存储描述符的标识和内容时,可以使用寄存器的编号来表示描述符的标识。例如,寄存器的编号为0时,其存储的描述符的标识设置为0。当寄存器中的描述符有效时,可根据描述符所指示的张量数据的大小在缓存空间中分配一块区域用于存储该张量数据。

[0031]

在一种可能的实现方式中,描述符的标识及内容可存储在内部存储器,描述符所指示的张量数据可存储在外部存储器。例如,可以采用在片上存储描述符的标识及内容、在片下存储描述符所指示的张量数据的方式。

[0032]

在一种可能的实现方式中,与各描述符对应的数据存储空间的数据地址可以是固定地址。例如,可以为张量数据划分单独的数据存储空间,每个张量数据在数据存储空间的起始地址与描述符一一对应。在这种情况下,执行电路根据描述符即可确定与操作数对应的数据在数据存储空间中的数据地址,然后执行处理指令。

[0033]

在一种可能的实现方式中,在与描述符对应的数据存储空间的数据地址为可变地址时,所述描述符还可用于指示n维的张量数据的地址,其中,所述描述符的内容还可包括表示张量数据的地址的至少一个地址参数。例如,张量数据为3维数据,在描述符指向该张量数据的地址时,描述符的内容可包括表示该张量数据的地址的一个地址参数,例如张量数据的起始物理地址,也可以包括该张量数据的地址的多个地址参数,例如张量数据的起始地址 地址偏移量,或张量数据基于各维度的地址参数。本领域技术人员可以根据实际需要对地址参数进行设置,本公开对此不作限制。

[0034]

在一种可能的实现方式中,所述张量数据的地址参数可以包括所述描述符的数据基准点在所述张量数据的数据存储空间中的基准地址。其中,基准地址可根据数据基准点的变化而不同。本公开对数据基准点的选取不作限制。

[0035]

在一种可能的实现方式中,所述基准地址可包括所述数据存储空间的起始地址。在描述符的数据基准点是数据存储空间的第一个数据块时,描述符的基准地址即为数据存储空间的起始地址。在描述符的数据基准点是数据存储空间中第一个数据块以外的其他数据时,描述符的基准地址即为该数据块在数据存储空间中的地址。

[0036]

在一种可能的实现方式中,所述张量数据的形状参数包括以下至少一种:所述数据存储空间在n个维度方向的至少一个方向上的尺寸、所述存储区域在n个维度方向的至少一个方向上的尺寸、所述存储区域在n个维度方向的至少一个方向上的偏移量、处于n个维

度方向的对角位置的至少两个顶点相对于所述数据基准点的位置、所述描述符所指示的张量数据的数据描述位置与数据地址之间的映射关系。其中,数据描述位置是描述符所指示的张量数据中的点或区域的映射位置,例如,张量数据为3维数据时,描述符可使用三维空间坐标(x,y,z)来表示该张量数据的形状,该张量数据的数据描述位置可以是使用三维空间坐标(x,y,z)表示的、该张量数据映射在三维空间中的点或区域的位置。

[0037]

应当理解,本领域技术人员可以根据实际情况选择表示张量数据的形状参数,本公开对此不作限制。

[0038]

通过在数据存取过程中使用描述符,可建立数据之间的关联,从而降低数据存取的复杂度,提高指令处理效率。

[0039]

在一种可能的实现方式中,可根据所述描述符的数据基准点在所述张量数据的数据存储空间中的基准地址、所述数据存储空间的n个维度方向的至少一个方向上的尺寸、所述存储区域在n个维度方向的至少一个方向上的尺寸和/或所述存储区域在n个维度方向的至少一个方向上的偏移量,确定所述张量数据的描述符的内容。图1示出根据本公开实施例的数据处理装置的数据存储空间的示意图。如图1所示,数据存储空间21采用行优先的方式存储了一个二维数据,可通过(x,y)来表示(其中,x轴水平向右,y轴垂直向下),x轴方向上的尺寸(每行的尺寸)为ori_x(图中未示出),y轴方向上的尺寸(总行数)为ori_y(图中未示出),数据存储空间21的起始地址pa_start(基准地址)为第一个数据块22的物理地址。数据块23是数据存储空间21中的部分数据,其在x轴方向上的偏移量25表示为offset_x,在y轴方向上的偏移量24表示为offset_y,在x轴方向上的尺寸表示为size_x,在y轴方向上的尺寸表示为size_y。

[0040]

在一种可能的实现方式中,使用描述符来定义数据块23时,描述符的数据基准点可使用数据存储空间21的第一个数据块,可以约定描述符的基准地址为数据存储空间21的起始地址pa_start。然后可以结合数据存储空间21在x轴的尺寸ori_x、在y轴上的尺寸ori_y,以及数据块23在y轴方向的偏移量offset_y、x轴方向上的偏移量offset_x、x轴方向上的尺寸size_x以及y轴方向上的尺寸size_y来确定数据块23的描述符的内容。

[0041]

在一种可能的实现方式中,可以使用下述公式(1)来表示描述符的内容:

[0042][0043]

应当理解,虽然上述示例中,描述符的内容表示的是二维空间,但本领域技术人员可以根据实际情况对描述符的内容表示的具体维度进行设置,本公开对此不作限制。

[0044]

在一种可能的实现方式中,可约定所述描述符的数据基准点在所述数据存储空间中的基准地址,在基准地址的基础上,根据处于n个维度方向的对角位置的至少两个顶点相对于所述数据基准点的位置,确定所述张量数据的描述符的内容。

[0045]

举例来说,可以约定描述符的数据基准点在数据存储空间中的基准地址pa_base,例如,可以在数据存储空间21中选取一个数据(例如,位置为(2,2)的数据)作为数据基准点,将该数据在数据存储空间中的物理地址作为基准地址pa_base。可以根据对角位置的两个顶点相对于数据基准点的位置,确定出图1中数据块23的描述符的内容。首先,确定数据

块23的对角位置的至少两个顶点相对于数据基准点的位置,例如,使用左上至右下方向的对角位置顶点相对于数据基准点的位置,其中,左上角顶点的相对位置为(x_min,y_min),右下角顶点的相对位置为(x_max,y_max),然后可以根据基准地址pa_base、左上角顶点的相对位置(x_min,y_min)以及右下角顶点的相对位置(x_max,y_max)确定出数据块23的描述符的内容。

[0046]

在一种可能的实现方式中,可以使用下述公式(2)来表示描述符的内容(基准地址为pa_base):

[0047][0048]

应当理解,虽然上述示例中使用左上角和右下角两个对角位置的顶点来确定描述符的内容,但本领域技术人员可以根据实际需要对对角位置的至少两个顶点的具体顶点进行设置,本公开对此不作限制。

[0049]

在一种可能的实现方式中,可根据所述描述符的数据基准点在所述数据存储空间中的基准地址,以及所述描述符所指示的张量数据的数据描述位置与数据地址之间的映射关系,确定所述张量数据的描述符的内容。其中,数据描述位置与数据地址之间的映射关系可以根据实际需要进行设定,例如,描述符所指示的张量数据为三维空间数据时,可是使用函数f(x,y,z)来定义数据描述位置与数据地址之间的映射关系。

[0050]

在一种可能的实现方式中,可以使用下述公式(3)来表示描述符的内容:

[0051][0052]

在一种可能的实现方式中,所述第一描述符和第二描述符还用于指示n维的张量数据的地址,其中,所述第一描述符和第二描述符的内容还包括表示张量数据的地址的至少一个地址参数。

[0053]

第一描述符或第二描述符还可以包括表示张量数据的地址的至少一个地址参数,例如第一内容或第二内容可以是:

[0054][0055]

其中pa为第一内容或第二内容的地址参数。地址参数可以是逻辑地址,也可以是物理地址。描述符解析电路可以以pa为向量形状的顶点、中间点或预设点中的任意一个,结合x方向和y方向的形状参数得到对应的数据地址。

[0056]

在一种可能的实现方式中,所述张量数据的地址参数包括所述描述符的数据基准点在所述张量数据的数据存储空间中的基准地址,所述基准地址包括所述数据存储空间的起始地址。

[0057]

在一种可能的实现方式中,第一描述符或第二描述符还可以包括表示张量数据的地址的至少一个地址参数,例如第一内容或第二内容可以是:

[0058][0059]

其中pa_start为基准地址参数,不再赘述。

[0060]

应当理解,本领域技术人员可以根据实际情况对数据描述位置与数据地址之间的映射关系进行设定,本公开对此不作限制。

[0061]

在一种可能的实现方式中,可以在一个任务中设定约定的基准地址,此任务下指令中的描述符均使用此基准地址,描述符内容中的内容可以包括基于此基准地址的形状参数。可以通过设定此任务的环境参数的方式确定此基准地址。基准地址的相关描述和使用方式可参见上述实施例。此种实现方式下,描述符的内容可以更快速的被映射为数据地址。

[0062]

在一种可能的实现方式中,可以在各描述符的内容中包含基准地址,则各描述符的基准地址可不同。相对于利用环境参数设定共同的基准地址的方式,此种方式中的各描述符可以更加灵活的描述数据,并使用更大的数据地址空间。

[0063]

在一种可能的实现方式中,可根据描述符的内容,确定与处理指令的操作数对应的数据在数据存储空间中的数据地址。其中,数据地址的计算由硬件自动完成,且描述符的内容的表示方式不同时,数据地址的计算方法也会不同。本公开对数据地址的具体计算方法不作限制。

[0064]

例如,操作数中描述符的内容是使用公式(1)表示的,描述符所指示的张量数据在数据存储空间中的偏移量分别为offset_x和offset_y,尺寸为size_x*size_y,那么,该描述符所指示的张量数据在数据存储空间中的起始数据地址pa1

(x,y)

可以使用下述公式(4)来确定:

[0065]

pa1

(x,y)

=pa_start (offset_y-1)*ori_x offset_x

ꢀꢀ

(4)

[0066]

根据上述公式(4)确定的数据起始地址pa1

(x,y)

,结合偏移量offset_x和offset_y,以及存储区域的尺寸size_x和size_y,可确定出描述符所指示的张量数据在数据存储空间中的存储区域。

[0067]

在一种可能的实现方式中,当操作数还包括针对描述符的数据描述位置时,可根据描述符的内容以及数据描述位置,确定操作数对应的数据在数据存储空间中的数据地址。通过这种方式,可以对描述符所指示的张量数据中的部分数据(例如一个或多个数据)进行处理。

[0068]

例如,操作数中描述符的内容是使用公式(1)表示的,描述符所指示的张量数据在数据存储空间中偏移量分别为offset_x和offset_y,尺寸为size_x*size_y,操作数中包括的针对描述符的数据描述位置为(x

q

,y

q

),那么,该描述符所指示的张量数据在数据存储空间中的数据地址pa2

(x,y)

可以使用下述公式(5)来确定:

[0069]

pa2

(x,y)

=pa_start (offset_y y

q-1)*ori_x (offset_x x

q

)

ꢀꢀ

(5)

[0070]

在一种可能的实现方式中,可以为一个任务创建一个第二描述符,第二描述符存储在描述符存储空间,用于指示此任务所使用到的一个较大的张量或一个张量集,第二描述符对应的张量或张量集可以存储在数据存储区域。此任务下指令中的操作数可以包括第一描述符。第一描述符可以在第二描述符的基础上提取操作数对应的数据地址。可以根据第一描述符中的形状参数和第二描述符中的形状参数得到操作数对应的数据地址。例如,

第一描述符可以包括基准地址,第二描述符可以包括各操作数的形状参数,可以根据基准地址参数和各第二描述符中的形状参数,根据上述实施例得到各第二描述符对应的操作数的数据地址。还可以通过创建环境参数的方式给出基准地址后,第一描述符中的形状参数给出一个较大的张量,各第二描述符在第一描述符的基础上截取数据,此方式下,由于第一描述符对应的数据已经存储在数据存储区域,此任务下的指令所需的操作数不用再对此进行片上片下的数据传输,可以减少数据io瓶颈。

[0071]

在一种可能的实现方式中,所述操作数还包括第一描述符的标识,所述描述符解析电路还配置为根据所述第一描述符的标识,在描述符存储空间中确定与所述第一描述符对应的第二描述符,并根据所述第一描述符的第一内容和所述第二描述符的第二内容,确定与所述处理指令的操作数对应的数据在数据存储空间中的数据地址。

[0072]

在一种可能的实现方式中,可以为一个任务创建多个第二描述符,各第二描述符可以利用标识进行区分。此任务下指令中的操作数可以包括第一描述符,还可以包括所述第一描述符所对应的第二描述符的标识。此种方式下,第一描述符所描述的张量的形状可以小于对应的第二描述符所描述的张量的形状。第一描述符所描述的张量的形状也可以与对应的第二描述符所描述的张量的形状不同但有重叠。

[0073]

在一种可能的实现方式中,第一描述符可以与对应的第二描述符中的至少一个形状参数相同,相同的形状参数可以不在第一描述符中给出,只给出不同的形状参数即可。

[0074]

图2示出根据本公开实施例的数据处理方法的流程图。如图2所示,该数据处理方法包括:

[0075]

步骤s11,获取第一处理指令操作数中的第一描述符,所述第一描述符包括第一内容,所述第一内容用于指示张量的形状;

[0076]

步骤s12,根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令;

[0077]

步骤s13,在确定不执行所述第一处理指令时,阻塞或缓存所述第一处理指令。

[0078]

在一种可能的实现方式中,该数据处理方法可应用于处理器中,该处理器可包括通用处理器(例如中央处理器cpu、图形处理器gpu)和专用处理器(例如人工智能处理器、科学计算处理器或数字信号处理器等)。本公开对处理器的类型不作限制。

[0079]

在一种可能的实现方式中,可以根据第一内容中的用于描述张量形状的参数,确定第一处理指令操作数对应数据的数据地址。未完成的第二处理指令的操作数,可以是传统的数据地址的方式。可以根据第一内容确定出的数据地址,和未完成的第二处理指令的操作数中的数据地址,确定第一处理指令和第二处理指令之间是否存在数据冲突。如存在数据冲突,则确定不执行第一处理指令,阻塞或缓存第一处理指令。

[0080]

在一种可能实现方式中,所述根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令,包括:

[0081]

根据所述第一内容确定与所述第一处理指令的操作数对应数据的第一存储区域;

[0082]

确定与所述第二处理指令的操作数对应数据的第二存储区域;

[0083]

在所述第一存储区域和所述第二存储区域有重叠时,不执行所述第一处理指令,或

[0084]

在所述第一存储区域和所述第二存储区域无重叠时,执行所述第一处理指令。

[0085]

在一种可能的实现方式中,当根据第一内容确定出的第一处理指令的操作数对应数据的第一存储区域,和第二处理指令的操作数对应数据的第二存储区域之间有重叠时,说明第一处理指令和第二处理指令之间存在数据冲突。两个指令可能对于相同的数据存储区域中的数据进行有冲突的读/写操作,因此在第二处理指令未执行完毕时,不执行第一处理指令。当第一存储区域和第二存储区域之间没有重叠时,则两个指令不会对相同的数据存储区域中的数据进行有冲突的读/写操作,即两个指令之间不存在数据冲突,可以执行第一处理指令。

[0086]

在本实施例中,根据第一内容中的形状参数可以直接高效的确定第一处理指令的操作数对应数据的存储区域,进而可以快速判断是否可以执行第一处理指令,从而提高处理器的处理效率。

[0087]

在一种可能的实现方式中,所述根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令,包括:

[0088]

根据所述第一内容确定与所述第一处理指令的操作数对应数据的第一操作区域,所述第一操作区域小于所述第一处理指令的操作数对应数据的第一存储区域;

[0089]

确定与所述第二处理指令的操作数对应数据的第二操作区域,所述第二操作区域小于所述第二处理指令的操作数对应数据的第二存储区域;

[0090]

在所述第一操作区域和所述第二操作区域有重叠时,不执行所述第一处理指令,或

[0091]

在所述第一操作区域和所述第二操作区域无重叠时,执行所述第一处理指令。

[0092]

在一种可能的实现方式中,处理指令在对存储区域中的数据进行处理时,由于处理指令的运算量较大,或被处理数据的数据量较大等各种原因,处理指令在一个处理时刻可以只针对操作数对应数据中的部分数据进行处理。可以将数据存储区域划分为多个操作区域,处理指令可依次针对多个操作区域中的一个操作区域的数据进行操作。可以通过记录处理指令执行的拍数或时间的方式,确定处理指令当前时刻对应的操作区域。两个处理指令的操作数对应的数据的存储区域之间有重叠时,只要两个处理指令的操作数对应的数据的操作区域之间没有重叠,两个处理指令间就不存在数据冲突。

[0093]

在一种可能的实现方式中,可以根据第一内容确定第一处理指令当前时刻对应的第一操作区域,并根据第二处理指令当前时刻对应的第二操作区域,确定第一处理指令和第二处理指令间是否存在数据冲突。当第一操作区域和第二操作区域之间无重叠时,可以执行第一处理指令。有重叠时则不能执行第一处理指令。

[0094]

在本实施例中,根据第一内容中的形状参数可以直接高效的确定第一处理指令的操作数对应数据的操作区域,并根据操作区域判断处理指令之间是否存在数据冲突,可以对于处理指令进行更加精细的执行顺序的管理,提高处理器处理效率。

[0095]

在一种可能的实现方式中,所述第二处理指令的操作数中包括第二描述符,所述第二描述符包括第二内容,所述第二内容用于指示张量的形状,

[0096]

根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令,包括:

[0097]

根据所述第一内容和所述第二内容的形状参数和/或地址参数,确定是否执行所述第一处理指令。

[0098]

在一种可能的实现方式中,当第二处理指令的操作数中包括第二内容时,可以根据第一内容和第二内容中的形状参和/或地址参数,直接判断两个处理指令之间是否存在数据冲突,而不用在将第一内容或第二内容转换为操作数对应的数据的存储地址或操作地址。可以根据形状参数和/或地址参数中的参数值,判断第一处理指令的操作数和第二处理指令的操作数是否存在数据冲突。当所述第一内容和所述第二内容中的形状参数和/或地址参数的参数值有重合时,不执行所述第一处理指令,或当所述第一内容和所述第二内容中的形状参数和/或地址参数的参数值无重合时,执行所述第一处理指令。

[0099]

在本实施例中,当两个的处理指令均包括描述符时,可以根据描述符中的形状参数和/或地址参数中的参数值,直接确定两个处理指令是否存在数据冲突,进而确定是否执行第一处理指令,不用换算操作数对应数据的数据地址,可以提高处理器的处理效率。

[0100]

在一种可能的实现方式中,所述第一描述符还包括第一标识,所述第二描述符还包括第二标识,所述方法还包括:

[0101]

根据所述第一标识和所述第二标识确定是否执行所述第一处理指令。

[0102]

在一种可能的实现方式中,当第一描述符包括第一标识,第二描述符包括第二标识时,可以根据第一标识和第二标识直接确定第一处理指令和第二处理指令是否存在数据冲突。当未完成的第二处理指令的第二标识中,包括第一处理指令的第一标识时,可以确定两个处理指令之间存在数据冲突。

[0103]

在本实施例中,可以根据描述符的标识可以快速判断两个处理指令之间是否存在数据冲突。

[0104]

在一种可能的实现方式中,如上述实施例所述,可以将操作数对应的存储区域划分为多个操作区域,以使处理指令进行更细粒度的操作。在创建多个描述符时,各描述符对应数据的存储区域可以不重叠,也可以重叠。当个描述符对应数据的存储区域不允许重叠时,根据描述符的标识可以判断两个描述符对应数据是否存在数据冲突。而当创建多个描述符,且描述符对应数据的存储区域允许重叠时,根据所述第一内容和所述第二内容中形状参数和/或地址参数的参数值,确定是否执行所述第一处理指令。

[0105]

在一种可能的实现方式中,根据本公开实施例的方法可通过相关技术的硬件结构实现。在该情况下,应用该方法的处理器可包括控制单元及执行单元,控制单元用于进行控制,例如读取存储器或外部传入的指令,对指令进行解码(译码),向相应的部件发出微操作控制信号等。执行单元用于执行具体的指令,执行单元可以例如为算术逻辑单元(arithmetic and logic unit,alu)、内存存取单元(memory access unit,mau)、人工智能运算单元(neural functional unit,nfu)等。本公开对执行单元的具体硬件类型不作限定。本公开对实现本公开实施例的方法所采用的具体硬件结构不作限制。

[0106]

图3示出根据本公开实施例的数据处理装置的框图。如图3所示,本公开还提供了一种数据处理装置,包括:

[0107]

描述符获取电路11,用于获取第一处理指令操作数中的第一描述符,所述第一描述符包括第一内容,所述第一内容用于指示张量的形状;

[0108]

确定电路12,用于根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令;

[0109]

执行电路13,用于在确定不执行所述第一处理指令时,阻塞或缓存所述第一处理

指令。

[0110]

在一种可能的实现方式中,所述确定电路,具体用于:

[0111]

根据所述第一内容确定与所述第一处理指令的操作数对应数据的第一存储区域;

[0112]

确定与所述第二处理指令的操作数对应数据的第二存储区域;

[0113]

在所述第一存储区域和所述第二存储区域有重叠时,不执行所述第一处理指令,或

[0114]

在所述第一存储区域和所述第二存储区域无重叠时,执行所述第一处理指令。

[0115]

在一种可能的实现方式中,所述确定电路,还用于:

[0116]

根据所述第一内容确定与所述第一处理指令的操作数对应数据的第一操作区域,所述第一操作区域小于所述第一处理指令的操作数对应数据的第一存储区域;

[0117]

确定与所述第二处理指令的操作数对应数据的第二操作区域,所述第二操作区域小于所述第二处理指令的操作数对应数据的第二存储区域;

[0118]

在所述第一操作区域和所述第二操作区域有重叠时,不执行所述第一处理指令,或

[0119]

在所述第一操作区域和所述第二操作区域无重叠时,执行所述第一处理指令。

[0120]

在一种可能的实现方式中,所述第二处理指令的操作数中包括第二描述符,所述第二描述符包括第二内容,所述第二内容用于指示张量的形状,所述确定电路,还用于:

[0121]

根据所述第一内容和所述第二内容的形状参数和/或地址参数,确定是否执行所述第一处理指令。

[0122]

在一种可能的实现方式中,所述形状参数包括以下至少一种:所述数据存储空间在n个维度方向的至少一个方向上的尺寸、所述张量数据的存储区域在n个维度方向的至少一个方向上的尺寸、所述存储区域在n个维度方向的至少一个方向上的偏移量、处于n个维度方向的对角位置的至少两个顶点相对于所述数据基准点的位置、所述描述符所指示的张量数据的数据描述位置与数据地址之间的映射关系。

[0123]

在一种可能的实现方式中,所述第一描述符还包括第一标识,所述第二描述符还包括第二标识,所述装置还包括:

[0124]

标识确定电路,用于根据所述第一标识和所述第二标识确定是否执行所述第一处理指令。

[0125]

在一种可能的实现方式中,还公开了一种神经网络芯片,其包括了上述数据处理装置。

[0126]

在一种可能的实现方式中,还公开了一种板卡,其包括存储器件、接口装置和控制器件以及上述神经网络芯片;其中,所述神经网络芯片与所述存储器件、所述控制器件以及所述接口装置分别连接;所述存储器件,用于存储数据;所述接口装置,用于实现所述神经网络芯片与外部设备之间的数据传输;所述控制器件,用于对所述神经网络芯片的状态进行监控。

[0127]

图4示出根据本公开实施例的板卡的结构框图,参阅图4,上述板卡除了包括上述芯片389以外,还可以包括其他的配套部件,该配套部件包括但不限于:存储器件390、接口装置391和控制器件392;

[0128]

所述存储器件390与所述神经网络芯片通过总线连接,用于存储数据。所述存储器

件可以包括多组存储单元393。每一组所述存储单元与所述神经网络芯片通过总线连接。可以理解,每一组所述存储单元可以是ddr sdram(英文:double data rate sdram,双倍速率同步动态随机存储器)。

[0129]

ddr不需要提高时钟频率就能加倍提高sdram的速度。ddr允许在时钟脉冲的上升沿和下降沿读出数据。ddr的速度是标准sdram的两倍。在一个实施例中,所述存储装置可以包括4组所述存储单元。每一组所述存储单元可以包括多个ddr4颗粒(芯片)。在一个实施例中,所述神经网络芯片内部可以包括4个72位ddr4控制器,上述72位ddr4控制器中64bit用于传输数据,8bit用于ecc校验。可以理解,当每一组所述存储单元中采用ddr4-3200颗粒时,数据传输的理论带宽可达到25600mb/s。

[0130]

在一个实施例中,每一组所述存储单元包括多个并联设置的双倍速率同步动态随机存储器。ddr在一个时钟周期内可以传输两次数据。在所述芯片中设置控制ddr的控制器,用于对每个所述存储单元的数据传输与数据存储的控制。

[0131]

所述接口装置与所述神经网络芯片电连接。所述接口装置用于实现所述神经网络芯片与外部设备(例如服务器或计算机)之间的数据传输。例如在一个实施例中,所述接口装置可以为标准pcie接口。比如,待处理的数据由服务器通过标准pcie接口传递至所述芯片,实现数据转移。优选的,当采用pcie 3.0x 16接口传输时,理论带宽可达到16000mb/s。在另一个实施例中,所述接口装置还可以是其他的接口,本技术并不限制上述其他的接口的具体表现形式,所述接口单元能够实现转接功能即可。另外,所述神经网络芯片的计算结果仍由所述接口装置传送回外部设备(例如服务器)。

[0132]

所述控制器件与所述神经网络芯片电连接。所述控制器件用于对所述神经网络芯片的状态进行监控。具体的,所述神经网络芯片与所述控制器件可以通过spi接口电连接。所述控制器件可以包括单片机(micro controller unit,mcu)。如所述神经网络芯片可以包括多个处理芯片、多个处理核或多个处理电路,可以带动多个负载。因此,所述神经网络芯片可以处于多负载和轻负载等不同的工作状态。通过所述控制装置可以实现对所述神经网络芯片中多个处理芯片、多个处理和或多个处理电路的工作状态的调控。

[0133]

在一种可能的实现方式中,公开了一种电子设备,其包括了上述神经网络芯片。电子设备包括数据处理装置、机器人、电脑、打印机、扫描仪、平板电脑、智能终端、手机、行车记录仪、导航仪、传感器、摄像头、服务器、云端服务器、相机、摄像机、投影仪、手表、耳机、移动存储、可穿戴设备、交通工具、家用电器、和/或医疗设备。

[0134]

所述交通工具包括飞机、轮船和/或车辆;所述家用电器包括电视、空调、微波炉、冰箱、电饭煲、加湿器、洗衣机、电灯、燃气灶、油烟机;所述医疗设备包括核磁共振仪、b超仪和/或心电图仪。

[0135]

依据以下条款可更好地理解前述内容:

[0136]

a1、一种数据处理方法,所述方法包括:

[0137]

获取第一处理指令操作数中的第一描述符,所述第一描述符包括第一内容,所述第一内容用于指示张量的形状;

[0138]

根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令;

[0139]

在确定不执行所述第一处理指令时,阻塞或缓存所述第一处理指令。

[0140]

a2、根据条款a1所述的方法,所述根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令,包括:

[0141]

根据所述第一内容确定与所述第一处理指令的操作数对应数据的第一存储区域;

[0142]

确定与所述第二处理指令的操作数对应数据的第二存储区域;

[0143]

在所述第一存储区域和所述第二存储区域有重叠时,不执行所述第一处理指令,或

[0144]

在所述第一存储区域和所述第二存储区域无重叠时,执行所述第一处理指令。

[0145]

a3、根据条款a1所述的方法,所述根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令,包括:

[0146]

根据所述第一内容确定与所述第一处理指令的操作数对应数据的第一操作区域,所述第一操作区域小于所述第一处理指令的操作数对应数据的第一存储区域;

[0147]

确定与所述第二处理指令的操作数对应数据的第二操作区域,所述第二操作区域小于所述第二处理指令的操作数对应数据的第二存储区域;

[0148]

在所述第一操作区域和所述第二操作区域有重叠时,不执行所述第一处理指令,或

[0149]

在所述第一操作区域和所述第二操作区域无重叠时,执行所述第一处理指令。

[0150]

a4、根据条款a1所述的方法,所述第二处理指令的操作数中包括第二描述符,所述第二描述符包括第二内容,所述第二内容用于指示张量的形状,

[0151]

根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令,包括:

[0152]

根据所述第一内容和所述第二内容的形状参数和/或地址参数,确定是否执行所述第一处理指令。

[0153]

a5、根据条款a4所述的方法,所述形状参数包括以下至少一种:所述数据存储空间在n个维度方向的至少一个方向上的尺寸、所述张量数据的存储区域在n个维度方向的至少一个方向上的尺寸、所述存储区域在n个维度方向的至少一个方向上的偏移量、处于n个维度方向的对角位置的至少两个顶点相对于所述数据基准点的位置、所述描述符所指示的张量数据的数据描述位置与数据地址之间的映射关系。

[0154]

a6、根据条款a4所述的方法,所述第一描述符还包括第一标识,所述第二描述符还包括第二标识,所述方法还包括:

[0155]

根据所述第一标识和所述第二标识确定是否执行所述第一处理指令。

[0156]

a7、一种数据处理装置,所述装置包括:

[0157]

描述符获取电路,用于获取第一处理指令操作数中的第一描述符,所述第一描述符包括第一内容,所述第一内容用于指示张量的形状;

[0158]

确定电路,用于根据指令队列中在所述第一处理指令之前未完成的第二处理指令的操作数和所述第一内容,确定是否执行所述第一处理指令;

[0159]

执行电路,用于在确定不执行所述第一处理指令时,阻塞或缓存所述第一处理指令。

[0160]

a8、根据条款a7所述的装置,所述确定电路,具体用于:

[0161]

根据所述第一内容确定与所述第一处理指令的操作数对应数据的第一存储区域;

[0162]

确定与所述第二处理指令的操作数对应数据的第二存储区域;

[0163]

在所述第一存储区域和所述第二存储区域有重叠时,不执行所述第一处理指令,或

[0164]

在所述第一存储区域和所述第二存储区域无重叠时,执行所述第一处理指令。

[0165]

a9、根据条款a7所述的装置,所述确定电路,还用于:

[0166]

根据所述第一内容确定与所述第一处理指令的操作数对应数据的第一操作区域,所述第一操作区域小于所述第一处理指令的操作数对应数据的第一存储区域;

[0167]

确定与所述第二处理指令的操作数对应数据的第二操作区域,所述第二操作区域小于所述第二处理指令的操作数对应数据的第二存储区域;

[0168]

在所述第一操作区域和所述第二操作区域有重叠时,不执行所述第一处理指令,或

[0169]

在所述第一操作区域和所述第二操作区域无重叠时,执行所述第一处理指令。

[0170]

a10、根据条款a7所述的装置,所述第二处理指令的操作数中包括第二描述符,所述第二描述符包括第二内容,所述第二内容用于指示张量的形状,所述确定电路,还用于:

[0171]

根据所述第一内容和所述第二内容的形状参数和/或地址参数,确定是否执行所述第一处理指令。

[0172]

a11、根据条款a10所述的装置,所述形状参数包括以下至少一种:所述数据存储空间在n个维度方向的至少一个方向上的尺寸、所述张量数据的存储区域在n个维度方向的至少一个方向上的尺寸、所述存储区域在n个维度方向的至少一个方向上的偏移量、处于n个维度方向的对角位置的至少两个顶点相对于所述数据基准点的位置、所述描述符所指示的张量数据的数据描述位置与数据地址之间的映射关系。

[0173]

a12、根据条款a10所述的装置,所述第一描述符还包括第一标识,所述第二描述符还包括第二标识,所述装置还包括:

[0174]

标识确定电路,用于根据所述第一标识和所述第二标识确定是否执行所述第一处理指令。

[0175]

a13、一种神经网络芯片,所述芯片包括如条款a7-a12中任意一项所述的数据处理装置。

[0176]

a14、一种电子设备,所述电子设备包括如条款a13所述的神经网络芯片。

[0177]

a15、一种板卡,所述板卡包括:存储器件、接口装置和控制器件以及如条款a13所述的神经网络芯片;

[0178]

其中,所述神经网络芯片与所述存储器件、所述控制器件以及所述接口装置分别连接;

[0179]

所述存储器件,用于存储数据;

[0180]

所述接口装置,用于实现所述神经网络芯片与外部设备之间的数据传输;

[0181]

所述控制器件,用于对所述神经网络芯片的状态进行监控。

[0182]

a16、根据条款a15所述的板卡,

[0183]

所述存储器件包括:多组存储单元,每一组所述存储单元与所述神经网络芯片通过总线连接,所述存储单元为:ddr sdram;

[0184]

所述芯片包括:ddr控制器,用于对每个所述存储单元的数据传输与数据存储的控

制;

[0185]

所述接口装置为:标准pcie接口。

[0186]

以上已经描述了本公开的各实施例,上述说明是示例性的,并非穷尽性的,并且也不限于所披露的各实施例。在不偏离所说明的各实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。本文中所用术语的选择,旨在最好地解释各实施例的原理、实际应用或对市场中的技术的改进,或者使本技术领域的其它普通技术人员能理解本文披露的各实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。