1.本发明涉及一种用于制造衬底的方法、尤其一种用于制造功率半导体模块的衬底的方法。

背景技术:

2.功率半导体模块大多具有一个或多个半导体衬底,该半导体衬底可以布置在底板上或冷却体上。具有多个可控半导体元件(例如igbt)的半导体装置布置在所述衬底中的至少一个上。半导体衬底通常具有电绝缘的衬底层(例如陶瓷层)、第一导电层(例如金属层)以及第二导电层,第一导电层布置在该衬底层的第一侧上,第二导电层布置在衬底层的与第一侧相对置的第二侧上。可控半导体元件例如布置在第一导电层上。第二导电层大多与底板或冷却体连接,即,该第二导电层布置在底板/冷却体与绝缘衬底层之间。

3.至少第一导电层通常为结构化层。即,该层具有多个彼此间隔开的区段,这些区段通过第一导电层中的连续的凹槽彼此分离。第一导电层的不同区段之间的连接通常仅通过电连接元件(例如接合线)建立。在此,第一导电层的不同区段可以与不同电位连接。在此,相邻区段的不同电位之间的差可以达到几千伏(kv)。因此,在功率半导体模块的运行期间,在区段之间的凹槽中出现电场强度的最大值。这可能导致功率半导体模块的电气故障并且导致电子流的问题。

4.出于该原因,通常将特殊涂层施加到第一导电层的两区段之间的凹槽中,该涂层能够影响(例如降低)电场强度,并保护第一导电层免受电子流方面的不期望负面影响。

5.因此,需要一种用于制造衬底的方法,借助该方法能够有效地制造在第一导电层的不同区段之间的间隙中具有涂层的衬底,而在此不会不利地影响成品衬底的功能。

技术实现要素:

6.一种方法,其包括:在介电绝缘层的第一侧上形成第一导电层;在第一导电层的背向介电绝缘层的一侧上形成结构化的掩模层;在第一导电层中形成至少一个沟槽,其中,所述至少一个沟槽延伸穿过整个第一导电层直至介电绝缘层;形成涂层,该涂层至少覆盖至少一个沟槽的底部和侧壁;在形成该涂层之后去除掩膜层。

附图说明

7.在下文中根据示例并且参考附图更详细地阐述本发明。在此,相同的附图标记表示相同的元素。附图中的表示不是按比例的。

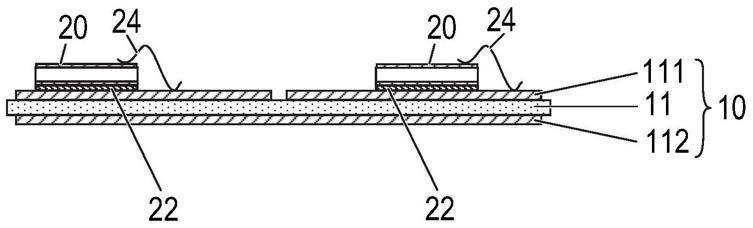

8.图1示例性示出具有布置在其上的半导体本体的衬底的横截面;

9.图2示例性示出在第一导电层的不同区段之间的间隙中具有涂层的衬底的横截面;

10.图3包括图3a至3g,其根据一个示例示出用于制造示例性衬底的方法;

11.图4示出图3e中所示步骤的一个替代方案;

12.图5示例性示出在执行图4中的步骤之后的衬底的横截面;

13.图6包括图6a至6c,其示例性示出第一导电层的两个区段之间的间隙中的不同涂层。

具体实施方式

14.在下文的详细描述中,根据具体示例示出如何实现本发明。应当理解的是,除非另有说明,否则在此描述的各个示例的特征可以彼此组合。如果确定的元素被表示为“第一元素”、“第二元素”......等,则“第一”、“第二”......的说明仅仅用于将不同元素彼此区分开。这种说明不与顺序或计数相关。这意味着,例如即使没有“第一元素”,也可以存在“第二元素”。

15.参照图1示出半导体衬底10。半导体衬底10例如具有介电绝缘层11、结构化的第一导电层111和(结构化的)第二导电层112。第一导电层111布置在介电绝缘层11的第一侧上,第二导电层112布置在介电绝缘层11的与第一侧相对置的第二侧上。因此,介电绝缘层11布置在第一导电层111与第二导电层112之间。但在此,第二导电层仅是可选的。同样可以仅将第一导电层111布置在介电绝缘层11上,并且完全省去第二导电层112。

16.第一导电层111和第二导电层112中的每个可以由以下材料中的一种构成或具有以下材料中的一种:铜、铜合金、铝、铝合金、在功率半导体模块运行期间保持为固态的任意其他金属或任意其他合金。半导体衬底10可以是陶瓷衬底,即介电绝缘层11由陶瓷构成的衬底。因此,介电绝缘层11的陶瓷例如可以是薄陶瓷层。介电绝缘层11的陶瓷例如可以由以下材料中的一种构成或具有以下材料中的一种:氧化铝、氮化铝、氧化锆、氮化硅、氮化硼或任意其他陶瓷。介电绝缘层11例如可以由以下材料中的一种构成或具有以下材料中的一种:al2o3、aln或si3n4。半导体衬底10例如可以是所谓的dcb(直接键合铜)衬底、dab(直接键合铝)衬底、ims(绝缘金属衬底)或amb(活性金属钎焊)衬底。半导体衬底10例如也可以是具有非陶瓷介电绝缘层11的常规电路板(pcb,printed circuit board)。非陶瓷介电绝缘层11例如可以由固化树脂构成或具有固化树脂。

17.继续参考图1,还可以将一个或多个半导体本体20布置在半导体衬底10上。布置在半导体衬底10上的这些半导体本体20中的每个都可以具有二极管、igbt(具有绝缘栅的双极晶体管)、mosfet(金属氧化物半导体场效应晶体管)、jfet(结型场效应晶体管)、hemt(高电子迀移率晶体管)或任意其他适合的可控半导体元件。所述一个或多个半导体本体20可以在半导体衬底10上构成半导体装置。在图1中仅示例性示出两个半导体本体20。

18.在图1中所示的第一导电层111是结构化层。在上下文中,“结构化层”表示:第一导电层111不是连续的层,而是在层的不同区段之间具有中断。不同的半导体本体20可以布置在第一导电层111的相同区段或不同区段上。第一导电层111的不同区段要么可以彼此不具有电连接,要么例如可以借助接合线彼此电连接。半导体本体20中的每个可以借助导电连接层22与半导体衬底10电气地并且机械地连接。图1示例性示出半导体衬底10,该半导体衬底具有布置在其上的连接层22。这种导电连接层22原则上可以是焊料层、由导电粘合剂构成的层或由烧结金属粉构成的层(例如烧结银粉层)。

19.第二导电层112(只要存在)要么可以是连续的层,要么可以是结构化层。

20.为了使半导体本体20与半导体衬底10连接,将半导体本体20布置在半导体衬底10

的表面(上表面)上,其中,连接层22布置在半导体衬底10与半导体本体20之间。半导体衬底10的上表面是第一导电层111的表面,该表面背向介电绝缘层11。替代或附加地,半导体本体20也可以借助接合线24与半导体衬底10连接。

21.(具有至少一个布置在其上的半导体本体20的)半导体衬底10例如可以是功率半导体模块的一部分并且可以布置在(未示出的)壳体中。

22.第一导电层111的不同区段可以与不同电位连接。相邻区段的不同电位之间的差可以达到几千伏(kv)。因此,在功率半导体模块的运行期间,在区段之间的凹槽中出现电场强度的最大值。这可能导致功率半导体模块的电气故障并且导致电子流的问题。

23.出于该原因,通常将特殊涂层施加到第一导电层111的两个区段之间的凹槽中,该涂层能够影响(例如降低)电场强度并保护第一导电层111免受电子流方面的不期望负面影响。在此,这种涂层114应当覆盖两个区段之间的凹槽的底部和侧壁。如果涂层114附加地还至少部分地覆盖第一导电层111的上侧,则这可能会对半导体模块的功能产生负面影响。

24.现在参考图3描述根据一个示例的方法,在该方法中,能够有效地制造衬底10(该衬底在第一导电层111的不同区段之间的间隙中具有涂层114),而在此不会不利地影响成品衬底10的功能。

25.在此,在第一步骤中,在介电绝缘层11上形成第一导电层111(参见图3a)。用于形成这种导电层(如金属化层)的相应方法是已知的,因此在此不进行更详细描述。可选地,在同一步骤中或者在随后的步骤中,也可以在介电绝缘层11上形成第二导电层112(参见图1)。然后至少将第一导电层111结构化。为此,首先将掩模层121(参见图3b)施加在第一导电层111的表面上。这例如可以是漆层(例如光刻胶)。例如可以借助旋涂将掩膜层121均匀施加在第一导电层上。然后例如可以使掩膜层121稳定化。接下来进行曝光步骤(参见图3c)。在此通常使用涂覆有铬的玻璃掩模。由此对掩膜层121的局部区域进行曝光,而不对其他区域进行。取决于所使用材料(漆)的类型,掩膜层121的曝光部分变为可溶的或不可溶的。随后借助显影剂溶液去除掩膜层121的可溶区域123。掩膜层121的可溶区域123在图3c中以深色示出。

26.在已经将掩模层121的可溶区域123去除之后,可以在随后的步骤中,在第一导电层111中构造至少一个沟槽124(参见图3d)。为此例如可以使用相应的蚀刻方法,例如湿法蚀刻方法或干法蚀刻方法。如此形成所述至少一个沟槽124,使得该沟槽延伸穿过整个第一导电层111。这意味着,至少一个沟槽124延伸直至介电绝缘层11。由此,可以形成第一导电层111的不同区段,这些区段彼此不再具有直接连接。而是不同区段通过相应的沟槽124完全彼此分离。

27.为了下一步骤,掩模层121仍保留在第一导电层111上。在下一步骤中(参见图3e)形成涂层31。一方面,涂层31可以至少覆盖至少一个沟槽124的底部和侧壁。附加地可能的是,涂层31也至少部分地覆盖掩膜层121。这例如取决于用于掩膜层121和涂层31的材料。掩膜层121例如可以具有常规合适的光刻胶、干抗蚀剂或无机材料。涂层31例如可以具有聚合物或者聚酰亚胺。例如,一些材料粘附在掩膜层121上,而其他材料仅粘附在介电绝缘层11的陶瓷(沟槽124的底部)上以及金属(沟槽124的侧壁或第一导电层111的区段的侧壁)上但不粘附在掩膜层121上。

28.在此,至少一个沟槽124可以至少部分地填充有涂层31。但也可能的是,借助涂层

31完全填充沟槽124,这例如在下文中更详细描述。

29.可以借助不同的适当方法形成涂层31。在图3e中示例性地示出一种喷涂法。在此,将涂层31的材料30大面积地喷射到衬底10上。在此,第一导电层111的上侧由掩膜层121保护并因此未直接被涂层31覆盖。用于施加涂层31的其他可能方法例如是:浸涂法、粉末涂覆法、热喷射法、等离子体涂覆法或点胶法。在图4中示例性示出浸涂法。在此,将整个衬底10完全浸入到相应的材料30中,该材料沉积在衬底10的表面上(可选地沉积在掩膜层121的表面上)。

30.在所有这些方法中,可以大面积地(即不仅在至少一个沟槽124中)施加涂层。这在图5中示例性示出。随后,在将涂层保留在至少一个沟槽124中期间(参见图3f),可以将涂层31例如从掩膜层121重新去除。为此,可以使用以下方法:在该方法中,在涂层31保留在至少一个沟槽124中期间,在期望区域中选择性地去除涂层。例如可以在使用感应耦合等离子体蚀刻(icp,英文:inductively coupled plasma etching)或反应性离子蚀刻(rie,英文:reactive ion etching)的情况下使用干法蚀刻方法。然而也可以使用研磨法、激光烧蚀、喷砂或干冰喷射来选择性地去除涂层31。同样可以借助水射束或空气射束来将涂层31从掩膜层121去除。在图3f中示例性所示的从掩膜层121去除涂层31的步骤之前或之后,可以可选地进行另一步骤,在该另一步骤中将涂层31固化。涂层31经常以液态或粘稠的形式被施加在衬底10上并因此仍包含大量水分。这种水分(例如通过加热涂层31)可以至少部分地去除。

31.然后,还可以去除掩膜层121(参见图3g)。例如可以借助适当的蚀刻溶液(去除剂)在干法蚀刻步骤中或者借助合适的溶剂去除掩膜层121。例如,可以将丙酮用作溶剂。其虽然去除掩膜层121但不会侵蚀其他层(例如沟槽124中的涂层31或第一导电层111)。

32.然而,在掩膜层121上整面地施加材料30或涂层31仅仅是示例性的。如上所述,一些能够用于涂层31的材料可能不粘附在掩膜层121上,使得该掩模层完全无法被涂层31覆盖。然而也可能的是,掩膜层的仅部分(例如掩膜层121的直接与沟槽124相邻的部分)被涂层31覆盖。这例如可以通过如下方式实现:仅在确定的区域中选择性地涂覆材料30,使得沟槽124的底部和侧壁被充分覆盖。在此,材料也可以到达掩膜层121的邻接区域上。如果至少一些掩模层121区域保持未被涂层31覆盖,则例如可以首先借助适当方法(例如湿化学蚀刻)去除掩模层121。为了进行去除,例如也可以在反应性气氛中或在增大的温度情况下(尤其当掩模层121比涂层31的温度稳定性更差或反应性更差时)使掩模层121分解。如果首先去除掩膜层121,则这导致涂层31的残留物自由悬浮在第一导电层111上方。随后,可以借助适当的方法(例如喷砂、压缩空气或者水射束)去除这些残留物,其中,涂层31保留在沟槽124中。

33.如已经描述的那样,可以借助涂层31至少部分地填充至少一个沟槽124。在图6a中示例性示出未被完全填充的沟槽124,但在该沟槽情况下,至少沟槽124的底部和侧壁被涂层覆盖。在此,涂层31具有如下厚度d31:该厚度小于第一导电层111在同一方向上的厚度d111。然而如图6b中示例性所示,同样可以借助涂层31完全填充沟槽124。在这种情况下,涂层31具有如下厚度d31:该厚度相应于第一导电层111的厚度d111。如图6c中示例性所示,原则上同样可能的是,涂层31具有如下厚度d31:该厚度大于第一导电层111在同一方向上的厚度d111。也就是说,涂层31也可以在一定程度上向外突出超过沟槽124。然而在此,涂层31

并不覆盖第一导电层111的上侧,因为第一导电层111在涂层31的形成期间由掩膜层121所保护。

34.所述方法非常有效,因为原则上需要用于形成至少一个沟槽124的掩模层121同时还在形成涂层31期间使用。因此,不需要第二附加掩膜层来阻止涂层31覆盖第一导电层111的表面的部分。

35.如图2中所示,除了至少一个沟槽124之外,还可以借助涂层114、31覆盖介电绝缘层11的边缘区域。如图中示例性所示,可能的是:第一导电层111没有完全覆盖介电绝缘层11。介电绝缘层11的边缘区域例如可以不由第一导电层111所覆盖。这意味着,除了布置在至少一个沟槽124下方的介电绝缘层11的区域之外,介电绝缘层11的边缘区域也可以露出。借助涂层114、31也可以覆盖介电绝缘层11的上述区域以及第一导电层111的相应邻接的侧壁。由此,这些表面也被充分保护。可以在至少一个沟槽124中形成涂层31期间的同一步骤期间,实现边缘区域中的涂层31。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。