1.本发明属于半导体器件领域,涉及一种超结功率器件及其制备方法。

背景技术:

2.在功率器件领域,vdmosfet(vertical double diffused metal oxide semiconductor field effect transistor,垂直双扩散金属氧化物场效应晶体管)因其工作频率高、热稳定性好及驱动电路简单等优点而被广泛应用。其中,击穿电压(bv)与导通电阻(ron)是功率器件中两个最重要的性能参数,对于这两个性能参数,普遍的设计要求是功率器件不仅要具有高的击穿电压,而且也要具有低的导通电阻,以降低功耗。

3.传统的功率器件的击穿电压和导通电阻的制约关系阻碍了器件性能的进一步提高,因此在传统vdmosfet器件的漂移区引入超结结构(super junction),形成超结晶体管(super junction mos,简称sjmos),以优化击穿电压和导通电阻的折衷关系,以其导通电阻小、导通速度快和开关损耗低等优点,引起了业界的广泛关注。

4.现有的关于超结结构的形成方法,通常采用在外延层中进行深沟道刻蚀和回填技术,或在外延层中进行多次外延和植入掺杂,以形成超结结构,从而基于电荷共享效应来提高bv,从而在保持相同的bv时,外延层的掺杂浓度可以显著增加,以在相同的bv下,即可获得较低的ron。然而,当在外延层中,通过深沟道刻蚀和回填技术,形成超结结构时,由于bv在很大程度上取决于沟槽的深度和电荷共享的精准度,深度越大,bv越高,而深沟槽会加大沟槽的深宽比,从而加大回填工艺的难度,可能导致应力、缺陷和均匀性等问题,进而影响器件的成品率和可靠性;而通过多次外延和植入掺杂的方式形成超结结构时,制备工艺较复杂,且成本较高。

5.因此,提供一种新型的超结功率器件及其制备方法,实属必要。

技术实现要素:

6.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种超结功率器件及其制备方法,用于解决现有技术中,超结功率器件所存在的应力、缺陷和均匀性的问题以及制备工艺复杂、成本较高的问题。

7.为实现上述目的及其他相关目的,本发明提供一种超结功率器件的制备方法,包括以下步骤:

8.形成第一导电类型外延层;

9.通过阱区掩膜版,于所述第一导电类型外延层内,形成第二导电类型阱区;

10.通过源区掩膜版,于所述第二导电类型阱区内,形成第一导电类型源区;

11.通过接触掩膜版,形成接触结构,所述接触结构短路连接所述第一导电类型源区,且与所述第二导电类型阱区相接触;

12.形成第二导电类型浮岛,所述第二导电类型浮岛位于所述第一导电类型外延层内,且所述第二导电类型浮岛的上表面及下表面均与所述第一导电类型外延层相接触;

13.形成第二导电类型柱,所述第二导电类型柱位于所述第一导电类型外延层内,并位于所述第二导电类型浮动的正上方,且与所述第二导电类型阱区相接触。

14.可选地,在形成所述第一导电类型外延层之后,在所述第一导电类型外延层的表面上形成超结掩膜版,并通过所述超结掩膜版,在所述第一导电类型外延层内注入第二导电类型杂质,以依次形成所述第二导电类型浮岛及第二导电类型柱。

15.可选地,在形成所述第二导电类型阱区之前或之后,通过所述阱区掩膜版,在所述第一导电类型外延层内注入第二导电类型杂质,以依次形成所述第二导电类型浮岛及第二导电类型柱。

16.可选地,在形成所述接触结构之前或之后,通过所述接触掩膜版,在所述第一导电类型外延层内注入第二导电类型杂质,以依次形成所述第二导电类型浮岛及第二导电类型柱。

17.可选地,形成的所述第二导电类型浮岛与形成的所述第二导电类型柱之间的所述第一导电类型外延层的厚度范围大于0.1μm。

18.可选地,所述第一导电类型为n型,所述第二导电类型为p型;或所述第一导电类型为p型,所述第二导电类型为n型。

19.可选地,还包括在所述第一导电类型外延层的下表面形成第一导电类型缓冲层的步骤。

20.可选地,还包括在所述第一导电类型外延层的下表面形成第二导电类型注入层的步骤。

21.本发明还提供一种超结功率器件,所述超结功率器件包括:

22.第一导电类型外延层;

23.第二导电类型阱区,位于所述第一导电类型外延层内;

24.第一导电类型源区,位于所述第二导电类型阱区内;

25.接触结构,短路连接所述第一导电类型源区,且与所述第二导电类型阱区相接触;

26.第二导电类型浮岛,位于所述第一导电类型外延层内,且所述第二导电类型浮岛的上表面及下表面均与所述第一导电类型外延层相接触;

27.第二导电类型柱,位于所述第一导电类型外延层内,并位于所述第二导电类型浮岛的正上方,且与所述第二导电类型阱区相接触。

28.可选地,所述第二导电类型浮岛与所述第二导电类型柱具有相同的宽度。

29.可选地,所述第二导电类型浮岛与所述第二导电类型柱之间的所述第一导电类型外延层的厚度范围大于0.1μm。

30.可选地,所述第一导电类型为n型,所述第二导电类型为p型;或所述第一导电类型为p型,所述第二导电类型为n型。

31.可选地,所述第一导电类型外延层的下表面还包括第一导电类型缓冲层。

32.可选地,所述第一导电类型外延层的下表面还包括第二导电类型注入层。

33.如上所述,本发明的超结功率器件及其制备方法,具有以下有益效果:

34.在制备超结功率器件时,可在形成第一导电类型外延层之后通过添加超结掩膜版、在形成第二导电类型阱区之前或之后直接通过阱区掩膜版,以及在形成接触结构之前或之后直接通过接触掩膜版,即可在第一导电类型外延层内注入第二导电类型杂质,以依

次形成第二导电类型浮岛及第二导电类型柱,该制备工艺无需进行多次外延工艺,且无需进行深沟道刻蚀,因此制备工艺简单、成本低,且成品率及可靠性较高。

35.同时具有第二导电类型浮岛及第二导电类型柱的超结功率器件,在断路状态,第二导电类型浮岛及第二导电类型柱,均有助于第一导电类型外延层中的漂移区的电荷共享效应,从而可提高功率器件的击穿电压,降低米勒电容和输入电容;在导通状态,第二导电类型浮岛及第二导电类型柱,可使得第一导电类型外延层中的漂移区具有较高的掺杂浓度,以显著地传导电流和降低vdmosfet器件的导通电阻,且由于第二导电类型浮岛及第二导电类型柱之间具有第一导电类型外延层,从而可在第一导电类型外延层内形成额外的三极管,以进一步的降低igbt器件的导通电阻。

附图说明

36.图1显示为本发明中超结功率器件的制备工艺流程图。

37.图2显示为实施例一中超结功率器件的制备工艺流程图。

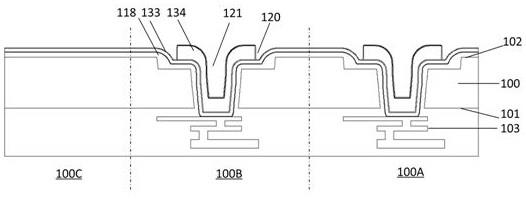

38.图3显示为实施例一中超结功率器件的结构示意图。

39.图4显示为实施例一中超结vdmosfet器件的结构示意图。

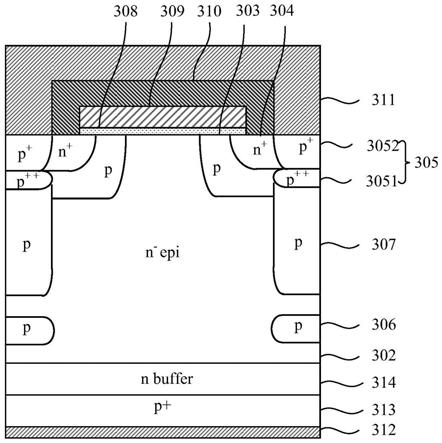

40.图5显示为实施例一中超结igbt器件的结构示意图。

41.图6显示为实施例二中超结功率器件的制备工艺流程图。

42.图7显示为实施例二中超结功率器件的结构示意图。

43.图8显示为实施例二中超结vdmosfet器件的结构示意图。

44.图9显示为实施例二中超结igbt器件的结构示意图。

45.图10显示为实施例三中超结功率器件的制备工艺流程图。

46.图11显示为实施例三中超结功率器件的结构示意图。

47.图12显示为实施例三中超结vdmosfet器件的结构示意图。

48.图13显示为实施例三中超结igbt器件的结构示意图。

49.元件标号说明

50.101、201、301

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一导电类型衬底

51.102、202、302

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一导电类型外延层

52.103、203、303

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型阱区

53.104、204、304

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一导电类型源区

54.105、205、305

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接触结构

55.3051

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型接触一区

56.3052

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型接触二区

57.106、206、306

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型浮岛

58.107、207、307

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型柱

59.108、208、308

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅氧化层

60.109、209、309

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极导电层

61.110、210、310

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

层间介质层

62.111、211、311

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极金属层

63.112、212、312

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

漏极金属层

64.113、213、313

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型注入层

65.314

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一导电类型缓冲层

具体实施方式

66.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

67.请参阅图1~图13。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

68.关于超结功率器件的制备可参阅图1,其中,形成第二导电类型浮岛及第二导电类型柱的步骤较为灵活,可根据具体的需要进行选择,以下将通过具体的实施例进行解释说明。

69.实施例一

70.参阅图2,本实施例提供一种同时具有第二导电类型浮岛及第二导电类型柱的超结功率器件的制备方法,其中,参阅图3~图5,显示为形成的所述超结功率器件的结构示意图。

71.本实施例,通过在形成第一导电类型外延层之后添加超结掩膜版,并以所述超结掩膜版作为掩膜,以在所述第一导电类型外延层内直接注入第二导电类型杂质,从而可依次形成具有相同宽度的第二导电类型浮岛及第二导电类型柱,该制备工艺无需进行多次外延工艺,且无需进行深沟道刻蚀,因此制备工艺简单、成本低,且成品率及可靠性较高。

72.需要说明的是,本实施例中关于第一导电类型所采用的为n型,第二导电类型为p型,但并非局限于此,在另一实施例中,所述第一导电类型也可为p型,以及所述第二导电类型也可为n型,此处不作过分限制。

73.参阅图2,具体制备工艺步骤包括:

74.提供第一导电类型衬底101;

75.于所述第一导电类型衬底101上形成第一导电类型外延层102;

76.在所述第一导电类型外延层102的表面上形成超结掩膜版;

77.通过所述超结掩膜版,在所述第一导电类型外延层102内注入第二导电类型杂质,形成第二导电类型浮岛106,所述第二导电类型浮岛106位于所述第一导电类型外延层102内,且所述第二导电类型浮岛106的上表面及下表面均与所述第一导电类型外延层102相接触;

78.通过所述超结掩膜版,在所述第一导电类型外延层102内注入第二导电类型杂质,形成第二导电类型柱107,所述第二导电类型柱107位于所述第一导电类型外延层102内,并位于所述第二导电类型浮岛106的正上方;

79.通过阱区掩膜版,于所述第一导电类型外延层102内,形成第二导电类型阱区103,所述第二导电类型阱区103位于所述第二导电类型柱107的上方,且与所述第二导电类型柱

107相接触;

80.通过源区掩膜版,于所述第二导电类型阱区103内,形成第一导电类型源区104;

81.通过接触掩膜版,形成接触结构105,所述接触结构105短路连接所述第一导电类型源区104,且与所述第二导电类型阱区103相接触。

82.具体的,首先,提供所述第一导电类型衬底101,所述第一导电类型衬底101的材质可为硅(si)、锗硅(sige)、氮化镓(gan)或碳化硅(sic)等掺杂半导体材料。

83.接着,在所述第一导电类型衬底101上,通过外延(epi)生长形成所述第一导电类型外延层102。

84.接着,在所述第一导电类型外延层102的表面上形成所述超结掩膜版。

85.具体的,可在所述第一导电类型外延层102的表面上,沉积硬掩膜材料层,其中,沉积方法可包括化学气相沉积,所述硬掩膜材料层可为二氧化硅层,但并非局限于此。接着,可在所述硬掩膜材料层的表面,通过光刻工艺,形成定义所述第二导电类型浮岛106及第二导电类型柱107的图形化光刻胶层,并通过干法刻蚀工艺,以所述光刻胶层作为刻蚀掩膜,对所述硬掩膜材料层进行干法刻蚀,以形成具有所述第二导电类型浮岛106及第二导电类型柱107图案的超结掩膜版。

86.接着,通过所述超结掩膜版,在所述第一导电类型外延层102内注入第二导电类型杂质,形成所述第二导电类型浮岛106,通过所述第二导电类型浮岛106,可使得功率器件在断路状态时,有助于所述第一导电类型外延层102中的漂移区的电荷共享效应,从而可提高功率器件的击穿电压,降低米勒电容和输入电容;且在导通状态,所述第二导电类型浮岛106,可使得所述第一导电类型外延层102中的漂移区具有较高的掺杂浓度,以显著地传导电流和降低器件的导通电阻。

87.接着,通过所述超结掩膜版,在所述第一导电类型外延层102内注入第二导电类型杂质,形成所述第二导电类型柱107,通过所述第二导电类型柱107,可使得功率器件在断路状态时,有助于所述第一导电类型外延层102中的漂移区的电荷共享效应,从而可提高功率器件的击穿电压,降低米勒电容和输入电容;且在导通状态,通过所述第二导电类型柱107,可使得所述第一导电类型外延层102中的漂移区具有较高的掺杂浓度,以显著地传导电流和降低器件的导通电阻。

88.其中,形成所述第二导电类型浮岛106及第二导电类型柱107的先后顺序,此处不作过分限制,为降低工艺复杂度,所述第二导电类型浮岛106及第二导电类型柱107的掺杂浓度可相同,掺杂注入源可采用b11,但并非局限于此。由于本实施例中,所述第二导电类型浮岛106及第二导电类型柱107采用同一所述超结掩膜版制备形成,从而所述第二导电类型浮岛106及第二导电类型柱107具有相同的宽度。

89.作为示例,形成的所述第二导电类型浮岛106与形成的所述第二导电类型柱107之间的所述第一导电类型外延层102的厚度范围大于0.1μm,以在所述第二导电类型柱107与所述第二导电类型浮岛106之间形成pnp三极管,从而可进一步的降低igbt器件的导通电阻。

90.接着,通过阱区掩膜版,于所述第一导电类型外延层102内,形成第二导电类型阱区103,所述第二导电类型阱区103位于所述第二导电类型柱107的上方,且与所述第二导电类型柱107相接触。

91.接着,通过源区掩膜版,于所述第二导电类型阱区103内,形成第一导电类型源区104。

92.接着,通过接触掩膜版,形成接触结构105,所述接触结构105短路连接所述第一导电类型源区104,且与所述第二导电类型阱区103相接触。

93.具体的,如图3,本实施例中,所述接触结构105通过在所述第二导电类型阱区103内注入第二导电类型杂质形成,以使所述第一导电类型源区104短接,以进一步的降低导通电阻。

94.接着,如图4,还可包括形成栅氧化层108、栅极导电层109、层间介质层110、源极金属层111及漏极金属层112的步骤,以形成vdmosfet器件。其中,关于所述栅氧化层108、栅极导电层109与所述超结功率器件的形成步骤的顺序,可根据具体的需要进行选择,此处不作过分限制。进一步的,栅极结构也可采用分栅结构,此处不作过分限制。

95.作为示例,还包括在所述第一导电类型外延层102的下表面形成第一导电类型缓冲层的步骤。

96.具体的,所述第一导电类型缓冲层的掺杂浓度可以介于所述第一导电类型衬底101和所述第一导电类型外延层102的掺杂浓度之间,以通过所述第一导电类型缓冲层,在所述vdmosfet器件中,可防止高温工艺过程中,所述第一导电类型衬底101的杂质原子扩散至所述第一导电类型外延层102内,避免所述第一导电类型外延层102的掺杂浓度提高而导致所述超结功率器件的击穿电压降低,且可通过所述第一导电类型衬底101,解决器件在关断时的拖尾电流问题。

97.参阅图5,本实施例还提供一种制备igbt器件的方法,其与图4中的制备所述vdmosfet器件的主要区别在于,在所述漏极金属层112与所述第一导电类型外延层102之间,添加了制备额外的第二导电类型注入层113的步骤。具体可通过cmp去除所述第一导电类型衬底101,并通过注入第二导电类型杂质,以形成所述第二导电类型注入层113,但并非局限于此。

98.参阅图3,本实施例还提供一种超结功率器件,所述超结功率器件可采用上述方法制备,但并非局限于此。

99.具体的,所述超结功率器件包括第一导电类型外延层102、第二导电类型阱区103、第一导电类型源区104、接触结构105、第二导电类型浮岛106及第二导电类型柱107。其中,所述第二导电类型阱区103,位于所述第一导电类型外延层102内;所述第一导电类型源区104位于所述第二导电类型阱区103内;所述接触结构105短路连接所述第一导电类型源区104,与所述第二导电类型阱区103相接触;所述第二导电类型浮岛106位于所述第一导电类型外延层102内,且所述第二导电类型浮岛106的上表面及下表面均与所述第一导电类型外延层102相接触;所述第二导电类型柱107,位于所述第一导电类型外延层102内,并位于所述第二导电类型浮岛106的正上方,且与所述第二导电类型阱区103相接触;且所述第二导电类型浮岛106与所述第二导电类型柱107具有相同的宽度。

100.本实施例的具有所述第二导电类型浮岛106及第二导电类型柱107的所述超结功率器件,在断路状态,所述第二导电类型浮岛106及第二导电类型柱107,均有助于所述第一导电类型外延层102中的漂移区的电荷共享效应,从而可提高功率器件的击穿电压,降低米勒电容和输入电容;在导通状态,所述第二导电类型浮岛106及第二导电类型柱107,可使得

所述第一导电类型外延层102中的漂移区具有较高的掺杂浓度,以显著地传导电流和降低导通电阻,且由于所述第二导电类型浮岛106及第二导电类型柱107之间具有所述第一导电类型外延层102,从而可在所述第一导电类型外延层102内形成额外的三极管,可进一步的降低igbt器件的导通电阻。

101.作为示例,所述第二导电类型浮岛106与所述第二导电类型柱107之间的所述第一导电类型外延层102的厚度范围大于0.1μm,如可为1μm、5μm等,此处不作过分限制。

102.作为示例,所述第一导电类型外延层102的下表面还可包括第一导电类型缓冲层,以避免高温工艺过程中,所述第一导电类型衬底101的杂质原子扩散至所述第一导电类型外延层102内,以避免所述第一导电类型外延层102的杂质浓度的提高,而导致所述超结功率器件的击穿电压降低,且可通过所述第一导电类型缓冲层,解决器件在关断时的拖尾电流问题。

103.作为示例,所述第一导电类型外延层102的下表面还包括第二导电类型注入层。

104.具体的,参阅图4,还可包括栅氧化层108、栅极导电层109、层间介质层110、源极金属层111及漏极金属层112,以形成vdmosfet器件,以及参阅图5,还可包括在所述漏极金属层112与所述第一导电类型外延层102之间,添加额外的第二导电类型注入层113,以形成igbt器件。进一步的,栅极结构也可采用分栅结构,此处不作过分限制。

105.实施例二

106.参阅图6,本实施例还提供另一种同时具有第二导电类型浮岛及第二导电类型柱的超结功率器件的制备方法,其中,参阅图7~图9,显示为形成的所述超结功率器件的结构示意图。与实施例一的不同之处主要在于,本实施例中,在形成所述第二导电类型阱区之前或之后,通过所述阱区掩膜版,在所述第一导电类型外延层内注入第二导电类型杂质,以依次形成与所述第二导电类型阱区具有相同宽度的所述第二导电类型浮岛及第二导电类型柱。

107.本实施例,直接通过所述阱区掩膜版,在所述第一导电类型外延层内直接注入第二导电类型杂质,以依次形成所述第二导电类型浮岛及第二导电类型柱,该制备工艺无需进行多次外延工艺,无需进行深沟道刻蚀,且无需额外添加掩膜版,因此制备工艺简单、成本低,且成品率及可靠性较高。

108.需要说明的是,本实施例中关于第一导电类型所采用的为n型,第二导电类型为p型,但并非局限于此,在另一实施例中,所述第一导电类型也可为p型,以及所述第二导电类型也可为n型。

109.参阅图6,具体制备工艺步骤可包括:

110.提供第一导电类型衬底201;

111.于所述第一导电类型衬底201上形成第一导电类型外延层202;

112.形成阱区掩膜版;

113.通过所述阱区掩膜版,于所述第一导电类型外延层202内注入第二导电类型杂质,形成第二导电类型浮岛206,所述第二导电类型浮岛206位于所述第一导电类型外延层202内,且所述第二导电类型浮岛206的上表面及下表面均与所述第一导电类型外延层202相接触;

114.通过所述阱区掩膜版,于所述第一导电类型外延层202内注入第二导电类型杂质,

形成第二导电类型柱207,所述第二导电类型柱207位于所述第一导电类型外延层内202,并位于所述第二导电类型浮岛206的正上方;

115.通过所述阱区掩膜版,于所述第一导电类型外延层202内,形成第二导电类型阱区203,且所述第二导电类型柱207与所述第二导电类型阱区203相接触;

116.通过源区掩膜版,于所述第二导电类型阱区203内,形成第一导电类型源区204;

117.通过接触掩膜版,形成接触结构205,所述接触结构205短路连接所述第一导电类型源区204,且与所述第二导电类型阱区203相接触。

118.具体的,通过所述阱区掩膜版形成所述第二导电类型浮岛206、第二导电类型柱207及第二导电类型阱区203的顺序并非局限于此,如所述第二导电类型浮岛206及第二导电类型柱207也可在形成所述第二导电类型阱区203之后,通过所述阱区掩膜版进行注入形成,具体可根据需要进行顺序的调整。所述第二导电类型浮岛206及第二导电类型柱207的作用,可参阅实施例一,此处不再赘述。

119.作为示例,形成的所述第二导电类型浮岛206与形成的所述第二导电类型柱207之间的所述第一导电类型外延层202的厚度范围大于0.1μm,如可为1μm、5μm等,此处不作过分限制。

120.接着,如图8,还可包括形成栅氧化层208、栅极导电层209、层间介质层210、源极金属层211及漏极金属层212的步骤,以形成vdmosfet器件。其中,关于所述栅氧化层208、栅极导电层209与所述超结功率器件的形成步骤的顺序,可根据具体的需要进行选择,此处不作过分限制。进一步的,栅极结构也可采用分栅结构,此处不作过分限制。

121.作为示例,还包括在所述第一导电类型外延层202的下表面形成第一导电类型缓冲层的步骤。

122.参阅图9,本实施例还提供一种制备igbt器件的方法,其与图8中的制备所述vdmosfet器件的主要区别在于在所述漏极金属层212与所述第一导电类型外延层202之间,添加了制备额外的第二导电类型注入层213的步骤。具体可通过cmp去除所述第一导电类型衬底201,并通过注入第二导电类型杂质,以形成所述第二导电类型注入层213,但并非局限于此。

123.参阅图7,本实施例还提供一种超结功率器件,所述超结功率器件可采用上述方法制备,但并非局限于此。

124.具体的,所述超结功率器件包括第一导电类型外延层202、第二导电类型阱区203、第一导电类型源区204、接触结构205、第二导电类型浮岛206及第二导电类型柱207。其中,所述第二导电类型阱区203,位于所述第一导电类型外延层202内;所述第一导电类型源区204位于所述第二导电类型阱区203内;所述接触结构205短路连接所述第一导电类型源区204,与所述第二导电类型阱区203相接触;所述第二导电类型浮岛206位于所述第一导电类型外延层202内,且所述第二导电类型浮岛206的上表面及下表面均与所述第一导电类型外延层202相接触;所述第二导电类型柱207,位于所述第一导电类型外延层202内,并位于所述第二导电类型浮岛206的正上方,且与所述第二导电类型阱区203相接触;且所述第二导电类型浮岛206、第二导电类型柱207及第二导电类型阱区203具有相同的宽度。

125.作为示例,所述第二导电类型浮岛206与所述第二导电类型柱207之间的所述第一导电类型外延层202的厚度范围大于0.1μm,如可为1μm、5μm等,此处不作过分限制。

126.作为示例,所述第一导电类型外延层202的下表面还可包括第一导电类型缓冲层。

127.作为示例,所述第一导电类型外延层202的下表面还包括第二导电类型注入层。

128.具体的,参阅图8,还可包括栅氧化层208、栅极导电层209、层间介质层210、源极金属层211及漏极金属层212,以形成vdmosfet器件,以及参阅图9,还可包括在所述漏极金属层212与所述第一导电类型外延层202之间,添加额外的第二导电类型注入层213,以形成igbt器件。进一步的,栅极结构也可采用分栅结构,此处不作过分限制。

129.实施例三

130.参阅图10,本实施例还提供另一种同时具有第二导电类型浮岛及第二导电类型柱的超结功率器件的制备方法,其中,参阅图11~图13,显示为形成的所述超结功率器件的结构示意图。与实施例一及实施例二的不同之处主要在于,本实施例中,在形成接触结构之前或之后,直接通过接触掩膜版,在第一导电类型外延层内注入第二导电类型杂质,以依次形成与所述接触结构具有相同宽度的所述第二导电类型浮岛及第二导电类型柱;所述接触结构包括不同掺杂浓度的第二导电类型接触区;在第一导电类型外延层的下表面形成有第一导电类型缓冲层。

131.本实施例,直接通过所述接触掩膜版,在所述第一导电类型外延层内直接注入第二导电类型杂质,以依次形成所述第二导电类型浮岛及第二导电类型柱,该制备工艺无需进行多次外延工艺,无需进行深沟道刻蚀,且无需额外添加掩膜版,因此制备工艺简单、成本低,且成品率及可靠性较高,且优选在形成所述接触掩膜版后,及形成所述接触结构之前,形成所述第二导电类型浮岛及第二导电类型柱,以便于通过所述接触结构的退火步骤,即可同时完成对所述第二导电类型浮岛及第二导电类型柱的退火工艺,从而可进一步的降低工艺复杂度,降低成本。

132.需要说明的是,本实施例中关于第一导电类型所采用的为n型,第二导电类型为p型,但并非局限于此,在另一实施例中,所述第一导电类型也可为p型,以及所述第二导电类型也可为n型。

133.参阅图10,具体制备工艺步骤可包括:

134.提供第一导电类型衬底301;

135.于所述第一导电类型衬底301上形成第一导电类型外延层302;

136.通过阱区掩膜版,于所述第一导电类型外延层302内,形成第二导电类型阱区303;

137.通过源区掩膜版,于所述第二导电类型阱区303内,形成第一导电类型源区304;

138.形成接触掩膜版;

139.通过所述接触掩膜版,于所述第一导电类型外延层302内注入第二导电类型杂质,形成第二导电类型浮岛306,所述第二导电类型浮岛306位于所述第一导电类型外延层302内,且所述第二导电类型浮岛306的上表面及下表面均与所述第一导电类型外延层302相接触;

140.通过所述接触掩膜版,于所述第一导电类型外延层302内注入第二导电类型杂质,形成第二导电类型柱307,所述第二导电类型柱307位于所述第一导电类型外延层302内,并位于所述第二导电类型浮岛306的正上方,且与所述第二导电类型阱区303相接触;

141.通过所述接触掩膜版,形成接触结构305,所述接触结构305短路连接所述第一导电类型源区304,且与所述第二导电类型阱区303相接触。

142.作为示例,形成所述接触结构305的步骤包括:

143.通过所述接触掩膜版,于所述第二导电类型阱区303内注入第二导电类型杂质,以形成第二导电类型接触二区3052;

144.通过所述接触掩膜版,于所述第二导电类型阱区303内注入第二导电类型杂质,以形成第二导电类型接触一区3051,其中,所述第二导电类型接触一区3051的掺杂浓度优选大于所述第二导电类型接触二区3052。

145.具体的,所述第二导电类型柱307与所述第二导电类型接触一区3051相接触,所述第二导电类型接触二区3052短路连接所述第一导电类型源区304,以进一步的降低导通电阻。且优选在形成所述接触掩膜版后,及形成所述接触结构305之前,形成所述第二导电类型浮岛306及第二导电类型柱307,以便于通过所述接触结构305的退火步骤,即可同时完成对所述第二导电类型浮岛306及第二导电类型柱307的退火工艺,从而进一步的降低工艺复杂度,降低成本。其中,通过所述接触掩膜版形成所述第二导电类型浮岛306、第二导电类型柱307及接触结构305的顺序并非局限于此,可根据需要进行设置。所述第二导电类型浮岛306及第二导电类型柱307的作用,可参阅实施例一,此处不再赘述。

146.作为示例,形成的所述第二导电类型浮岛306与形成的所述第二导电类型柱307之间的所述第一导电类型外延层302的厚度范围大于0.1μm,如可为1μm、5μm等,此处不作过分限制。

147.接着,如图12,还可包括形成栅氧化层308、栅极导电层309、层间介质层310、源极金属层311及漏极金属层312的步骤,以形成vdmosfet器件。其中,关于所述栅氧化层308、栅极导电层309与所述超结功率器件的形成步骤的顺序,可根据具体的需要进行选择,此处不作过分限制。进一步的,栅极结构也可采用分栅结构,此处不作过分限制。

148.作为示例,还包括在所述第一导电类型外延层302的下表面形成第一导电类型缓冲层314的步骤。

149.具体的,通过所述第一导电类型缓冲层314,可避免高温工艺过程中,所述第一导电类型衬底301的杂质原子扩散至所述第一导电类型外延层302内,以避免所述第一导电类型外延层302的杂质浓度的提高,而导致所述超结功率器件的击穿电压降低,且可通过所述第一导电类型缓冲层314,解决器件在关断时的拖尾电流问题。

150.参阅图13,本实施例还提供一种制备igbt器件的方法,其与图12中的制备所述vdmosfet器件的主要区别在于在所述漏极金属层313与所述第一导电类型外延层302之间,添加了制备额外的第二导电类型注入层313的步骤。具体可通过cmp去除所述第一导电类型衬底301,并通过注入第二导电类型杂质,以形成所述第二导电类型注入层313,但并非局限于此。

151.参阅图11,本实施例还提供一种超结功率器件,所述超结功率器件可采用上述方法制备,但并非局限于此。

152.具体的,所述超结功率器件包括第一导电类型外延层302、第二导电类型阱区303、第一导电类型源区304、接触结构305、第二导电类型浮岛306及第二导电类型柱307。其中,所述第二导电类型阱区303,位于所述第一导电类型外延层302内;所述第一导电类型源区304位于所述第二导电类型阱区303内;所述接触结构305短路连接所述第一导电类型源区304,与所述第二导电类型阱区303相接触;所述第二导电类型浮岛306位于所述第一导电类

型外延层302内,且所述第二导电类型浮岛306的上表面及下表面均与所述第一导电类型外延层302相接触;所述第二导电类型柱307,位于所述第一导电类型外延层302内,并位于所述第二导电类型浮岛306的正上方,且与所述第二导电类型阱区303相接触;且所述第二导电类型浮岛306、第二导电类型柱307及接触结构305具有相同的宽度。

153.作为示例,所述第二导电类型浮岛306与所述第二导电类型柱307之间的所述第一导电类型外延层302的厚度范围大于0.1μm,如可为1μm、5μm等,此处不作过分限制。

154.作为示例,所述第一导电类型外延层302的下表面还可包括第一导电类型缓冲层314。

155.作为示例,所述第一导电类型外延层302的下表面还包括第二导电类型注入层313。

156.具体的,参阅图12,还可包括栅氧化层308、栅极导电层309、层间介质层310、源极金属层311及漏极金属层312,以形成vdmosfet器件,以及参阅图13,还可包括在所述漏极金属层312与所述第一导电类型外延层302之间,添加额外的第二导电类型注入层313,以形成igbt器件。进一步的,栅极结构也可采用分栅结构,此处不作过分限制。

157.综上所述,本发明的超结功率器件及其制备方法,在制备超结功率器件时,可在形成第一导电类型外延层之后通过添加超结掩膜版、在形成第二导电类型阱区之前或之后直接通过阱区掩膜版,以及在形成接触结构之前或之后直接通过接触掩膜版,即可在第一导电类型外延层内注入第二导电类型杂质,以依次形成第二导电类型浮岛及第二导电类型柱,该制备工艺无需进行多次外延工艺,且无需进行深沟道刻蚀,因此制备工艺简单、成本低,且成品率及可靠性较高。同时具有第二导电类型浮岛及第二导电类型柱的超结功率器件,在断路状态,第二导电类型浮岛及第二导电类型柱,均有助于第一导电类型外延层中的漂移区的电荷共享效应,从而可提高功率器件的击穿电压,降低米勒电容和输入电容;在导通状态,第二导电类型浮岛及第二导电类型柱,可使得第一导电类型外延层中的漂移区具有较高的掺杂浓度,以显著地传导电流和降低vdmosfet器件的导通电阻,且由于第二导电类型浮岛及第二导电类型柱之间具有第一导电类型外延层,从而可在第一导电类型外延层内形成额外的三极管,以进一步的降低igbt器件的导通电阻。

158.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。