一种squid芯片与磁显微镜探头及其封装方法

技术领域:

1.本发明属于磁检测技术领域,涉及一种超导量子干涉器件(superconducting quantum interference device,简称为squid芯片,尤其是一种用作磁显微镜(magnetic microscope)探头核心元件的squid芯片,同时涉及以squid芯片为核心元件的磁显微镜探头及其封装结构装置与封装方法。

背景技术:

2.近年来由于超导量子干涉器件极好的空间、磁场分辨率和被动性无损检测的先天优势,同时随着集成电路技术的发展,使用squid芯片检测样品磁性的磁扫描squid显微镜(mssm)技术吸引了越来越多研究者的兴趣。

3.在目前的磁显微镜中,扫描squid显微镜因其具有较高的空间分辨率和磁场分辨率,是最灵敏的;其探头的设计精度要求是极其高的。squid芯片包括衬底层、绝缘层与夹在衬底层、绝缘层之间的磁通感应结区,squid芯片的磁通感应结区是磁显微镜的敏感源。检测时,squid芯片的磁通感应结区至待测样品之间的距离对磁显微镜空间分辨率和磁场分辨率具有显著的影响,可以说,磁显微镜空间分辨率和磁场分辨率在很大程度上取决于squid芯片的磁通感应结区至待测样品之间的距离h,二者距离越近,磁显微镜空间分辨率和磁场分辨率越高。

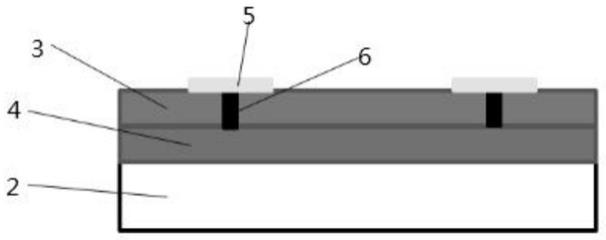

4.现有squid芯片根据其所适用的环境温度要求区间分为高温squid芯片与低温squid芯片。其中,高温squid芯片的适用环境温度要求为77k,约为零下196摄氏度左右。低温squid芯片的适用环境温度要求为4.2k,约为零下269摄氏度左右。二者基本结构均包括衬底层2、绝缘层3与夹在衬底层2、绝缘层3之间磁通感应结区。二者的外表没什么区别,均如图2、图3所示,绝缘层3外表面设置焊盘5,绝缘层3打孔,从磁通感应结区引出导电连接线6经绝缘层3的孔与焊盘5电连接。通常,焊盘5设置为4至6个。但二者的磁通感应结区结构有较大区别。

5.现有磁显微镜探头基本结构如图5、图6所示,包括杜瓦、冷指9与squid芯片1,冷指9材料为紫铜,具有优良导电性。杜瓦包括杜瓦外胆7与杜瓦内胆8,冷指9与杜瓦内胆8连接,杜瓦外胆7顶端设置开口,开口上设置有蓝宝石玻璃窗10,杜瓦外胆7及蓝宝石玻璃窗10形成密封容器,杜瓦内胆8上设置有排插引脚11,squid芯片1用低温胶19粘贴在冷指9顶端,squid芯片1的焊盘5与排插引脚11之间用导电连接线6连接。由于焊盘5很薄,只能从其上表面接线,焊盘5与排插引脚11之间的导电连接线6必定会产生一定的弯曲高度,芯片到样品18的总距离h=ha hb hc hd。ha为squid芯片1与排插引脚11之间的导电连接线6最高点到芯片敏感源的距离,hb为导电连接线到蓝宝石玻璃窗10的距离,hc为蓝宝石玻璃窗10的厚度,hd为样品18到蓝宝石玻璃窗10的距离。hd可以通过调节样品18位置来尽可能的减小。杜瓦工作时,内部处于真空,蓝宝石玻璃窗10会被大气压压弯,所以hc和hb有最小值,量级在百um以上。对于扫描squid显微镜,即使是几十um的距离缩短,对空间分辨率和磁场分辨率也有显著的影响。

6.为了降低squid芯片1的焊盘5与排插引脚11之间导电连接线6的弯曲程度,缩短ha,现有技术方案采用在冷指侧面引线的方式,如图7所示,其具体实施方式是:在squid芯片1与排插引脚11之间引出导电连接线6引线banding后,通过手动的方式将引线向冷指侧面拉动,再用低温胶将引线固定在冷指上。通过这种方式,可以小幅度降低引线弯曲程度,从而降低引线至芯片磁通感应区的距离。但这种方式有以下不足:1、操作难度大,只能使用手动方式,至今无法用机械装置完成;2、后期维护难度大,拆装不方便。

7.在现有的扫描squid显微镜磁显微镜探头方案中,都是使用现有squid芯片。对于该方案,其squid芯片的磁通感应结区到样品18的距离,主要由以下四个部分组成:squid芯片1与排插引脚11之间的导电连接线6的弯曲高度(几十um左右),导电连接线到蓝宝石窗的直线距离(百um以上),蓝宝石玻璃窗10的厚度(百um左右),蓝宝石玻璃窗10到样品18距离。其中蓝宝石玻璃窗10到样品18距离可以通过机械移动平台来尽可能地减小。蓝宝石玻璃窗10的厚度受到到杜瓦真空和材料性能的限制,降低难度极大。且由于杜瓦工作时,内部抽成真空,蓝宝石玻璃窗10会受压强影响而弯曲,所以导电连接线到蓝宝石窗的直线距离存在一个最小值,难以完全消除。虽然正孔squid芯片引出导线只需要简单的焊接即可完成,但是却因为在焊接时,导电连接线必定存在弯曲的状况。导电连接线弯曲直接拉远了squid芯片到蓝宝石玻璃窗10的距离,这限制了扫描squid显微镜空间分辨率和磁场分辨率。

8.现有squid芯片根据其磁通感应结区的膜层结构可分为单层膜squid芯片与三层膜squid芯片。

9.单层膜squid芯片的剖面如图1所示,单层膜squid芯片磁通感应结区常用膜层为单层的ybco层4,ybco全称为yttrium barium copper oxide,指氧化钇钡铜,是一种晶体,化学式为yba[2]cu[3]o[7

‑

x]。ybco是一种高温超导体材料,它能在高于液态氮气的沸点77k的温度下保持超导特性,ybco需工作在93k以下。使用该芯片的ha为引线最高点到单层膜的距离。

[0010]

三层膜squid芯片的剖面如图4所示,三层膜squid芯片的约瑟夫森结区为铌

‑

铝氧化铝

‑

铌三层膜结构,包括位于上面的小铌片20,位于中间的铝氧化铝片21,位于下面的大铌片22。三层膜squid芯片从约瑟夫森结区引出的导电连接线6,一部份从小铌片20引出,向上穿过绝缘层与焊盘电连接。另一部份是从大铌片22引出,向上穿过绝缘层3,与焊盘5电连接。约瑟夫森结区的俯视图为参照图12,使用该芯片的ha为导电连接线6最高点到铝氧化铝片21的距离。

[0011]

现有squid芯片通常的焊接方式是使用bonding机通过超声波震动或热压的方式,将导电连接线(铝线或金线)键合到squid芯片焊盘上。导电连接线从squid芯片焊盘5引出用于对外连接。因导电连接线非常细,操作难度大,在硬性材料bonding时,易堵出线口;手动操作bonding机进行bonding作业,对于操作者的熟练度要求较高;bonding机一次操作只能完成一个焊盘的键合。

技术实现要素:

[0012]

本发明所要解决的技术问题是提供一种squid芯片与磁显微镜探头及其封装方法。

[0013]

为了解决上述技术问题,本发明一种squid芯片的技术方案为:

[0014]

一种squid芯片,包括衬底层、绝缘层与夹在衬底层、绝缘层之间的磁通感应结区,其特征在于,所述衬底层外表面设置焊盘,所述衬底层打孔,从所述磁通感应结区引出导电连接线经衬底层的孔与所述焊盘电连接。

[0015]

本发明一种squid芯片进一步的技术方案为:

[0016]

所述磁通感应结区为单层的ybco层,从所述ybco层引出导电连接线经衬底层的孔与所述焊盘电连接。

[0017]

所述磁通感应结区为为铌

‑

铝氧化铝

‑

铌三层膜结构,包括位于上面的小铌片,位于中间的铝氧化铝片,位于下面的大铌片;所述从磁通感应结区引出的导电连接线,一部份从小铌片引出,穿过铝氧化铝片、衬底层与焊盘电连接;另一部份是从大铌片引出,穿过衬底层与焊盘电连接。

[0018]

所述焊盘设置为4个,所述衬底层打4个孔,从所述磁通感应结区引出4根导电连接线分别与所述4个焊盘电连接;或者,所述焊盘设置为6个,所述衬底层打6个孔,所述从磁通感应结区引出6根导电连接线分别与所述6个焊盘电连接。

[0019]

因为本发明squid芯片衬底层外表面设置焊盘,由衬底层打孔引线连接焊盘,相对于现有squid芯片从绝缘层打孔引线来说,属于背面打孔引线,所以也可简称其为背孔squid芯片。

[0020]

为了解决上述技术问题,本发明一种磁显微镜探头的技术方案为:

[0021]

一种磁显微镜探头,包括杜瓦、冷指与squid芯片,所述杜瓦包括杜瓦外胆与杜瓦内胆,冷指与杜瓦内胆连接,杜瓦外胆顶端设置开口,开口上设置有蓝宝石玻璃窗,杜瓦外胆及蓝宝石玻璃窗形成密封容器,杜瓦内胆上设置有排插引脚,其特征在于,所述squid芯片为以上所述的背孔squid芯片,所述冷指顶端按所述squid芯片焊盘数量从冷指顶端侧面向内开设非贯穿槽,各非贯穿槽互不相通,每个非贯穿槽配置1根铜引脚,所述铜引脚包括1个平整的导电面,其它均为绝缘面,所述铜引脚以其导电面朝上方式分别嵌入非贯穿槽中,铜引脚的外端设置导电连接线连接排插引脚,所述squid芯片以其焊盘朝下的方式放置在冷指顶端,squid芯片的每个焊盘分别对应其中1个铜引脚的导电面,每个焊盘与其对应铜引脚的导电面之间具有经加热压焊使之具有导电性的各向异性的导电胶。

[0022]

本发明一种磁显微镜探头进一步的技术方案为:

[0023]

所述冷指顶端的非贯穿槽为横截面呈矩形的方槽,所述铜引脚为横截面呈矩形的方形铜引脚,所述方形铜引脚长度方向4个面的其中1个面为导电面,所述方形铜引脚与冷指接触的面均为绝缘面,绝缘面包括其长度方向的其它3个面及与冷指接触的端面。

[0024]

所述各个绝缘面均涂有绝缘胶。

[0025]

所述每个铜引脚大部分嵌入在冷指顶端的非贯穿槽中,小部分露出在外。

[0026]

所述冷指顶部呈四方形,冷指顶端均从其4个侧面的近左侧处向内开设非贯穿槽,或者,冷指顶端均从其4个侧面的近右侧处向内开设非贯穿槽。

[0027]

为了解决上述技术问题,本发明一种磁显微镜的封装方法的技术方案为:

[0028]

一种磁显微镜的封装方法,包括杜瓦、冷指与squid芯片,所述杜瓦包括杜瓦外胆与杜瓦内胆,冷指与杜瓦连接内胆,杜瓦外胆顶端设置开口,开口上设置有蓝宝石玻璃窗,杜瓦外胆及蓝宝石玻璃窗形成密封容器,杜瓦内胆上设置有排插引脚;其特征在于,所述squid芯片使用以上所述的背孔squid芯片;所述冷指顶端按所述squid芯片焊盘数量从冷

指顶端侧面向内开设非贯穿槽,各非贯穿槽互不相通,每个非贯穿槽配置1根铜引脚,所述铜引脚包括1个平整的导电面,其它均为绝缘面,将所述铜引脚以其导电面朝上方式分别嵌入非贯穿槽中,在铜引脚的外端设置导电连接线连接排插引脚;事先选用各项异性的导电胶加热至100至200度后保温备用,在冷指顶端贴上经加热压焊使之具有导电性的各向异性的导电胶;将所述squid芯片以其焊盘朝向冷指顶端,使squid芯片的每个焊盘分别对应其中1个铜引脚的导电面的方式,将squid芯片压焊在冷指顶端的对应位置,使squid芯片的焊盘与所述铜引脚导电面之间的导电胶达到设定的压力和压焊时间,使squid芯片的焊盘与所述铜引脚电连通。

[0029]

本发明一种磁显微镜的封装方法进一步的技术方案为:

[0030]

使用芯片压焊装置,将所述squid芯片压焊在冷指顶端的对应位置,所述压焊装置包括由驱动装置驱动可作直线滑动的推进杆,所述推进杆包括位于其顶部的芯片推头,芯片推头的顶端设置有与所述squid芯片相应的芯片容纳槽;将squid芯片放置在推进杆推头的芯片容纳槽中,由驱动装置驱动推进杆将squid芯片压焊至冷指顶端的对应位置。

[0031]

所述压焊装置的驱动装置具有推进杆所施加压力的感知器及其压力显示器,当压力达到限定压力值x时驱动装置停止运行,等待设定时间y,使导电胶凝固;等待时间结束,驱动装置自动反向运行,回复原位,压焊结束。

[0032]

本发明提供一种新的背孔squid芯片与磁显微镜探头及其封装方法。与现有squid芯片设计方式相比,开发了一种在衬底打孔引出焊盘的背孔squid芯片,且背孔squid芯片封装方式不需要用引线键合squid芯片焊盘,完全消除了引线弯曲部分到squid芯片敏感源的距离,缩短了从squid芯片到杜瓦蓝宝石玻璃窗的距离。缩短的距离大概在几十um左右,相对于squid芯片到样品18之间的距离(几百um)来说,缩短了10%左右距离。这对于空间分辨率来说,提升率也约为10%。这样,就能较大幅度提升磁显微镜的空间分辨率和磁场分辨率,进而能较大幅度提升磁显微镜的检测灵敏度。

[0033]

本发明是一种在芯片检测技术领域值得推广的技术。另外,本发明所提供的一种新的背孔squid芯片与磁显微镜探头及其封装方法,可广泛应用于基于squid的磁探测系统,包含但不限于心磁,脑磁,肺磁,肌肉磁,地球物理,低场核磁共振和无损检测系统,尤其适用于检测半导体芯片电流磁异常的扫描squid显微镜系统。

[0034]

此外,本发明所提供的背孔squid芯片可采用芯片压焊装置焊接焊盘,一次性可压焊多个焊盘,大幅度地提高了焊接效率,降低了焊接成本。在将导电胶加热到近200度后进行压焊,并在设定薄膜压力传感器压力阈值为35牛顿且压焊时间设定为30秒时,芯片与铜引脚之间有很好的导电性。

附图说明

[0035]

图1为现有单层膜squid芯片剖面示意图;

[0036]

图2为现有squid芯片俯视示意图;

[0037]

图3为现有squid芯片仰视示意图;

[0038]

图4为现有三层膜squid芯片剖面示意图;

[0039]

图5为现有磁显微镜探头基本结构示意图;

[0040]

图6为现有squid芯片封装俯视示意图;

[0041]

图7为现有磁显微镜探头冷指侧面引线方式示意图;

[0042]

图8为本发明单层膜squid芯片剖面示意图;

[0043]

图9为本发明squid芯片俯视示意图;

[0044]

图10为本发明squid芯片仰视示意图;

[0045]

图11为本发明三层膜squid芯片剖面示意图;

[0046]

图12为本发明三层膜squid芯片磁通感应结区俯视示意图;

[0047]

图13为本发明磁显微镜探头基本结构示意图;

[0048]

图14为本发明squid芯片封装俯视示意图;

[0049]

图15为本发明冷指顶端结构示意图;

[0050]

图16为铜引脚示意图;

[0051]

图17为冷指非贯穿槽嵌入方形铜引脚状态示意图;

[0052]

图18为在冷指顶端贴上导电胶状态示意图;

[0053]

图19为squid芯片压焊在冷指顶端状态立体示意图;

[0054]

图20为squid芯片压焊在冷指顶端状态俯视示意图;

[0055]

图21为squid芯片压焊在冷指顶端状态侧视示意图。

[0056]

以上各附图均是示意性的,并不与实际比例相对应。例如:芯片到待测样品的总距离h的各组成部分ha、hb、hc、hd在图5、图10上均作了夸大的表示。

[0057]

各图中标号所指示的部分为:1、squid芯片;2、衬底层;3、绝缘层;4、ybco层;5、焊盘;6、导电连接线;7、杜瓦外胆;8、杜瓦内胆;9、冷指;10、蓝宝石玻璃窗;11、排插引脚;12、非贯穿槽;13、铜引脚;14、导电面;15、绝缘面;16、导电胶;17、导电颗粒;18、样品;19、低温胶;20、小铌片;21、铝氧化铝片;22、大铌片;23、缺口。

具体实施方式

[0058]

以下结合附图对本发明作进一步详细描述。

[0059]

本发明squid芯片1,如图8至图12所示,包括衬底层2、绝缘层3与夹在衬底层2、绝缘层3之间的磁通感应结区,衬底层2外表面设置焊盘5,衬底层2打孔,从磁通感应结区引出导电连接线6经衬底层2的孔与焊盘5电连接。本发明squid芯片1根据其磁通感应结区的膜层结构也可分为单层膜squid芯片1与三层膜squid芯片1两种。二者基本结构均包括衬底层2、绝缘层3与夹在衬底层2、绝缘层3之间的磁通感应结区。二者的外表没什么区别,均如图9、图10所示,绝缘层3外表面设置焊盘5,绝缘层3打孔,从磁通感应结区引出导电连接线6经绝缘层3的孔与焊盘5电连接。通常,焊盘5设置为4至6个。但二者的磁通感应结区的膜层结构有较大区别。

[0060]

单层膜squid芯片1如图8所示,其磁通感应结区为单层的ybco层4,从ybco层4引出导电连接线6经衬底层2的孔与焊盘5电连接。

[0061]

三层膜squid芯片1如图11、图12所示,其磁通感应结区为为铌

‑

铝氧化铝

‑

铌三层膜结构,包括位于上面的小铌片20,位于中间的铝氧化铝片21,位于下面的大铌片22;从磁通感应结区引出的导电连接线6,一部份从小铌片20引出,穿过铝氧化铝片21、衬底层2与焊盘5电连接;另一部份是从大铌片22引出,穿过衬底层2与焊盘5电连接。

[0062]

本发明squid芯片1,不管是单层膜squid芯片1还是三层膜squid芯片1,如图9、图

10所示,焊盘5设置为4个,衬底层2打4个孔,从磁通感应结区引出4根导电连接线6分别与4个焊盘5电连接;或者,焊盘5设置为6个,衬底层2打6个孔,从磁通感应结区引出6根导电连接线6分别与6个焊盘5电连接。

[0063]

因为本发明squid芯片衬底层外表面设置焊盘5,由衬底层2打孔引线连接焊盘5,相对于现有squid芯片从绝缘层打孔引线来说,属于背面打孔引线,所以也可简称其为背孔squid芯片。

[0064]

本发明磁显微镜探头,如图13、图14所示,包括杜瓦、冷指9与squid芯片1,杜瓦包括杜瓦外胆7与杜瓦内胆8,冷指9与杜瓦内胆8连接,杜瓦外胆7顶端设置开口,开口上设置有蓝宝石玻璃窗10,杜瓦外胆7及蓝宝石玻璃窗10形成密封容器,杜瓦内胆8上设置有排插引脚11,squid芯片1为以上的背孔squid芯片1,冷指9顶端按squid芯片1焊盘5数量从冷指9顶端侧面向内开设非贯穿槽12,各非贯穿槽12互不相通,每个非贯穿槽12配置1根铜引脚13,铜引脚13包括1个平整的导电面14,其它均为绝缘面15,铜引脚13以其导电面14朝上方式分别嵌入非贯穿槽12中,铜引脚13的外端设置导电连接线6连接排插引脚11,squid芯片1以其焊盘5朝下的方式放置在冷指9顶端,squid芯片1的每个焊盘5分别对应其中1个铜引脚13的导电面14,每个焊盘5与其对应铜引脚13的导电面14之间具有经加热压焊使之具有导电性的各向异性的导电胶16。

[0065]

如图15所示,冷指9顶部呈四方形,冷指9顶端均从其4个侧面的近左侧处向内开设非贯穿槽12,或者,冷指9顶端均从其4个侧面的近右侧处向内开设非贯穿槽12。冷指9顶端的非贯穿槽12为横截面呈矩形的方槽。如图16所示,铜引脚13为横截面呈矩形的方形铜引脚13,方形铜引脚13长度方向4个面的其中1个面为导电面14,方形铜引脚13与冷指9接触的面均为绝缘面15,绝缘面15包括其长度方向的其它3个面及与冷指9接触的端面,各个绝缘面15均涂有绝缘胶。如图17所示,每个铜引脚13大部分嵌入在冷指9顶端的非贯穿槽12中,小部分露出在外。

[0066]

本发明磁显微镜的封装方法,如图13所示,包括杜瓦、冷指9与squid芯片1,杜瓦包括杜瓦外胆7与杜瓦内胆8,冷指9与杜瓦连接内胆,杜瓦外胆7顶端设置开口,开口上设置有蓝宝石玻璃窗10,杜瓦外胆7及蓝宝石玻璃窗10形成密封容器,杜瓦内胆8上设置有排插引脚11。squid芯片1使用以上的背孔squid芯片1。冷指9顶端按squid芯片1焊盘5数量从冷指9顶端侧面向内开设非贯穿槽12,各非贯穿槽12互不相通,每个非贯穿槽12配置1根铜引脚13,铜引脚13包括1个平整的导电面14,其它均为绝缘面15,将铜引脚13以其导电面14朝上方式分别嵌入非贯穿槽12中,在铜引脚13的外端设置导电连接线6连接排插引脚11。事先选用各项异性的导电胶16加热至100至200度后保温备用。如图18所示,在冷指9顶端贴上经加热压焊使之具有导电性的各向异性的导电胶16。将squid芯片1以其焊盘5朝向冷指9顶端,使squid芯片1的每个焊盘5分别对应其中1个铜引脚13的导电面14的方式,将squid芯片1压焊在冷指9顶端的对应位置,使squid芯片1的焊盘与铜引脚13导电面14之间的导电胶16达到设定的压力和压焊时间,使squid芯片1的焊盘与铜引脚13电连通。

[0067]

作为本发明压焊装置专用压焊耗材的各向异性导电胶16,可从市场采购得到。这种各向异性导电胶内部含有离散状态导电颗粒17,未经压缩并不具有导电性;只有经过一定程度的加热压缩,使离散状态导电颗粒17在受压处聚集,导电颗粒17在压缩方向相互接触,才具有导电性。此导电胶的导电原理:通过压力将加热的导电胶进行压缩,可以提升导

电颗粒17的接触性,从而形成导电通路。各向异性导电胶则是只会在一个方向导电,如z方向导电,而在x和y方向只是不导电的胶黏剂。

[0068]

使用芯片压焊装置,将squid芯片1压焊在冷指9顶端的对应位置,压焊装置包括由驱动装置驱动可作直线滑动的推进杆,推进杆包括位于其顶部的芯片推头,芯片推头的顶端设置有与squid芯片1相应的芯片容纳槽;将squid芯片1放置在推进杆推头的芯片容纳槽中,由驱动装置驱动推进杆将squid芯片1压焊至冷指9顶端的对应位置。压焊装置的驱动装置具有推进杆所施加压力的感知器及其压力显示器,当压力达到限定压力值x时驱动装置停止运行,等待设定时间y,使导电胶16凝固;等待时间结束,驱动装置自动反向运行,回复原位,压焊结束。芯片压焊装置与压焊方法的具体实施方式,可参见申请人与本技术同日申请的名为“一种squid芯片压焊装置与压焊方法”的专利申请说明书及其附图。

[0069]

压焊完成后如图19、图20、图21所示。完成压焊过程后,如图21所示,仍滞留在squid芯片1的焊盘5与铜引脚13的导电面之间的导电胶16达到设定的压缩程度,离散状态导电颗粒17在受压处聚集,导电颗粒17在压缩方向相互接触而具有导电性,使squid芯片1的焊盘5与铜引脚13的导电面之间形成电连接。而非位于squid芯片1的焊盘5与铜引脚13的导电面之间的导电胶16压缩程度不足,不导电。压焊完成后的squid芯片1以其焊盘5朝下的方式放置在冷指9顶端,squid芯片1的焊盘5上面也不再有从焊盘5引出的用于对外连接的导电连接线6。

[0070]

封装完成后本发明磁显微镜探头,如图13所示,squid芯片1到样品18的总距离h=ha hb hc hd。ha为导电连接线最高点到芯片敏感源的距离,hb为导电连接线到蓝宝石玻璃窗10的距离,hc为蓝宝石玻璃窗10的厚度,hd为样品18到蓝宝石玻璃窗10的距离。hd可以通过调节样品18位置来尽可能的减小。杜瓦工作时,内部处于真空,蓝宝石玻璃窗10会被大气压压弯,所以hc和hb有最小值,量级在百um以上。所以为了缩小h,唯有缩小ha。在使用本发明背孔squid芯片1封装方式后,其芯片到样品的总距离h=ha hb hc hd。其中ha可减少几十um,其他参数没有变化,即h也可随之减少几十um。自然就削除了现有的扫描squid显微镜磁显微镜探头因从芯片焊盘引出的导电连接线形成几十um的弯曲高度而影响磁显微镜的空间分辨率和磁场分辨率,所以本发明能较大幅度提升磁显微镜的空间分辨率和磁场分辨率,进而能较大幅度提升磁显微镜的检测灵敏度。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。