1.本技术涉及计算机内存访问技术领域,具体涉及一种多内存通道的内存存取装置、方法和数据处理设备。

背景技术:

2.随着计算能力的提升,诸如中央处理器(central processing unit,简称cpu)、图形处理器(graphics processing unit,简称gpu)、人工智能(artificial intelligence,简称ai)视频编解码等芯片的内存通道越来越多,例如第一颗7nm gpu芯片amd vega20就包含了32个内存通道,未来出现包含更多内存通道的芯片将是大趋势。

3.然而,芯片制造在14 nm以下高工艺制程,良品率会急剧下降。当芯片中个别内存通道在制造过程中损坏,也会带来良品率急剧下降,从而大幅度提高芯片成本。此外,多内存通道芯片随着服务年限的增加,其中一个或者多个内存通道也可能损坏,从而导致芯片无法继续使用,降低了计算系统的可靠性。另外,在很多应用场景中,为了降低功耗,芯片需要工作在省电模式,而传统多内存通道芯片无法实现仅使用其中一部分内存通道。这些问题都对多内存通道芯片的应用发展提出了挑战。

技术实现要素:

4.有鉴于此,本技术提出一种多内存通道的内存存取装置、方法和数据处理设备,用于实现芯片的多内存通道的运行时灵活配置,从而提高多内存通道芯片的制造良品率、物理服务年限和系统可靠性。

5.第一方面,本技术提出一种多内存通道的内存存取装置,包括:配置寄存器,用于设置虚拟内存通道和物理内存通道的配置信息,所述配置信息包括虚拟内存通道索引和物理内存通道索引之间的映射关系;内存管理单元,用于基于内存访问请求的物理内存地址和所述配置信息,计算得到目标虚拟内存通道索引;所述内存管理单元还用于基于所述目标虚拟内存通道索引和所述映射关系,计算得到所述目标虚拟内存通道索引映射的目标物理内存通道索引;存储控制器,与所述物理内存通道对应设置,用于控制对存储器的存取访问;所述存储控制器,还用于根据所述内存访问请求的物理内存地址,经由所述目标物理内存通道索引对应的物理内存通道,对目标存储器中的目标数据进行存取访问。

6.作为本技术一个优选的实施方式,所述配置信息还包括虚拟内存通道数、可用的物理内存通道数和内存通道使能掩码,其中,所述虚拟内存通道数不大于所述可用的物理内存通道数,所述内存通道使能掩码用于指示与所述可用的物理内存通道数对应的可读写物理内存通道。

7.作为本技术一个优选的实施方式,所述配置信息还包括所述目标存储器中的寄存器库的数量和行大小。

8.作为本技术一个优选的实施方式,所述配置信息还包括虚拟内存通道使能标识,所述虚拟内存通道使能标识用于指示是否启用所述虚拟内存通道。

9.作为本技术一个优选的实施方式,所述内存管理单元用于将所述物理内存地址除以所述寄存器库的数量与行大小的乘积得到的商与所述虚拟内存通道数求模的结果,作为所述目标虚拟内存通道索引。

10.作为本技术一个优选的实施方式,所述存储控制器,还用于根据所述内存访问请求的物理内存地址,经由所述目标物理内存通道索引对应的物理内存通道,对目标存储器中的目标数据进行存取访问包括:所述存储控制器根据所述物理内存地址,计算得到所述目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移;所述存储控制器基于所述目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移,对所述目标数据进行存取访问。

11.作为本技术一个优选的实施方式,所述存储控制器根据所述物理内存地址,计算得到所述目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移包括:将所述物理内存地址除以所述寄存器库的行大小的商与寄存器库掩码进行逻辑与运算的结果,作为所述寄存器库索引,其中,所述寄存器库掩码为所述寄存器库的数量减1;将所述物理内存地址除以所述寄存器库的行大小、寄存器库的数量和虚拟内存通道数三者的乘积的商,作为所述目标数据所在存储区域的行索引;将所述物理内存地址与所述寄存器库的行大小减1的差进行逻辑与运算的结果,作为所述目标数据所在存储区域的行内地址偏移。

12.作为本技术一个优选的实施方式,该存取装置还包括:缓存单元,用于将所述内存访问请求转发至所述存储控制器。

13.作为本技术一个优选的实施方式,所述缓存单元包括二级缓存和三级缓存中的一者或两者。

14.作为本技术一个优选的实施方式,所述配置寄存器还用于为一个或多个处理核心设置虚拟内存通道和物理内存通道的多个配置信息,多个所述配置信息包括虚拟内存通道索引和物理内存通道索引之间不同的映射关系。

15.作为本技术一个优选的实施方式,多个所述配置信息还包括对应一个或多个所述处理核心的多个不同的虚拟内存通道数、可用的物理内存通道数和内存通道使能掩码。

16.第二方面,本技术提出一种多内存通道的内存存取方法,包括以下步骤:在配置寄存器中设置虚拟内存通道和物理内存通道的配置信息,所述配置信息包括虚拟内存通道索引和物理内存通道索引之间的映射关系;基于内存访问请求的物理内存地址和所述配置信息,计算得到目标虚拟内存通道索引;基于所述目标虚拟内存通道索引和所述映射关系,计算得到所述目标虚拟内存通道索引映射的目标物理内存通道索引;根据所述内存访问请求的物理内存地址,经由所述目标物理内存通道索引对应的物理内存通道,对目标存储器中的目标数据进行存取访问。

17.作为本技术一个优选的实施方式,所述配置信息还包括虚拟内存通道数、可用的物理内存通道数和内存通道使能掩码,其中,所述虚拟内存通道数不大于所述可用的物理内存通道数,所述内存通道使能掩码用于指示与所述可用的物理内存通道数对应的可读写物理内存通道。

18.作为本技术一个优选的实施方式,所述配置信息还包括所述目标存储器中的寄存器库的数量和行大小。

19.作为本技术一个优选的实施方式,所述配置信息还包括虚拟内存通道使能标识,所述虚拟内存通道使能标识用于指示是否启用所述虚拟内存通道。

20.作为本技术一个优选的实施方式,所述基于内存访问请求的物理内存地址和所述配置信息,计算得到目标虚拟内存通道索引包括:将所述物理内存地址除以所述寄存器库的数量与行大小的乘积的商与所述虚拟内存通道数求模的结果,作为所述目标虚拟内存通道索引。

21.作为本技术一个优选的实施方式,所述根据所述内存访问请求的物理内存地址,经由所述目标物理内存通道索引对应的物理内存通道,对目标存储器中的目标数据进行存取访问包括:根据所述物理内存地址,计算得到所述目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移;基于所述目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移,对所述目标数据进行存取访问。

22.作为本技术一个优选的实施方式,所述根据所述物理内存地址计算得到所述目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移包括:将所述物理内存地址除以所述寄存器库的行大小的商与寄存器库掩码进行逻辑与运算的结果,作为所述寄存器库索引,其中,所述寄存器库掩码为所述寄存器库的数量减1;将所述物理内存地址除以所述寄存器库的行大小、寄存器库的数量和虚拟内存通道数三者的乘积的商,作为所述行索引;将所述物理内存地址与所述寄存器库的行大小减1的差进行逻辑与运算的结果,作为所述目标数据所在存储区域的行内地址偏移。

23.作为本技术一个优选的实施方式,所述计算得到所述目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移包括:通过所述目标物理内存通道索引对应的物理内存通道所对应设置的存储控制器计算得到所述目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移。

24.作为本技术一个优选的实施方式,所述基于所述目标虚拟内存通道索引和所述映射关系,计算得到所述目标虚拟内存通道索引映射的目标物理内存通道索引包括:通过内存管理单元计算得到所述目标虚拟内存通道索引映射的目标物理内存通道索引。

25.作为本技术一个优选的实施方式,所述在配置寄存器中设置虚拟内存通道和物理内存通道的配置信息还包括:为一个或多个处理核心在配置寄存器中设置虚拟内存通道和物理内存通道的多个配置信息,多个所述配置信息包括虚拟内存通道索引和物理内存通道索引之间不同的映射关系。

26.作为本技术一个优选的实施方式,多个所述配置信息还包括对应一个或多个所述处理核心的多个不同的虚拟内存通道数、可用的物理内存通道数和内存通道使能掩码。

27.作为本技术一个优选的实施方式,根据所述内存访问请求的物理内存地址,经由所述目标物理内存通道索引对应的物理内存通道,对目标存储器中的目标数据进行存取访问还包括:经由缓存单元将所述内存访问请求转发至与所述目标物理内存通道索引对应的物理内存通道所对应设置的存储控制器。

28.第三方面,本技术提出了一种数据处理设备,包括:一个或多个处理单元和第一方面所述的多内存通道的内存存取装置。

29.作为本技术一个优选的实施方式,所述数据处理设备包括中央处理单元、图形处理单元、数字处理单元、现场可编程门阵列、人工智能芯片、视频编解码芯片中的一者或多者。

30.相对于现有技术,本技术至少具有如下有益效果:(1)即使在芯片出现内存通道损坏时,也能通过对剩余可用物理内存通道的灵活配置,确保内存数据读写正常,从而可以提高芯片制造的良品率,并提高芯片物理服务年限和系统可靠性;(2)可以实现虚拟化系统对资源的灵活分配,实现多用户虚拟机任意划分资源,达到最佳资源分配,还可以实现虚拟机之间的物理隔离,并且还可以无缝切换多内存通道系统的低功耗状态和高功耗状态时的多内存系统配置。

附图说明

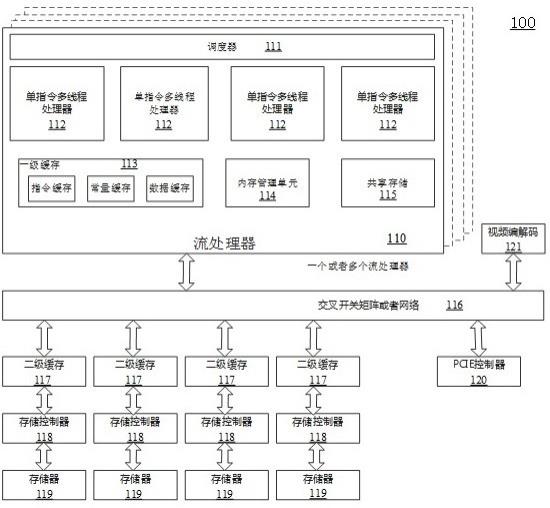

31.结合附图,并通过以下非限制性实施方式的详细描述将更充分地理解本技术的特征、目的和优点,其中:图1是现有的具有多内存通道的gpu芯片100的一种示例性结构;图2是多内存通道中一种常见的寄存器库结构示意图;图3是多内存通道系统中一种32位物理内存地址的示例性结构示意图;图4是根据本技术一实施例的多内存通道的内存存取装置400的结构示意图;图5是根据本技术一实施例的多内存通道的内存存取方法的流程示意图;图6是根据本技术一实施例的多内存通道的内存存取方法的具体步骤的流程示意图;图7是根据本技术另一实施例的多内存通道的内存存取方法的具体步骤的流程示意图;图8是根据本技术一实施例的数据处理设备800的结构示意图;图9

‑

图12是在8内存通道的gpu或cpu芯片中的具体应用示意图。

具体实施方式

32.下面通过实施例,并结合附图,对本技术的技术方案进行清楚、完整地说明,但是本技术不限于以下所描述的实施例。基于以下实施例,本领域普通技术人员在没有创造性劳动的前提下所获得的所有其它实施例,都属于本技术保护的范围。为了清楚起见,在附图中省略了与描述示例性实施方式无关的部分。

33.应理解,本技术中诸如“包括”或“具有”等的术语旨在指示本说明书中所公开的特征、数字、步骤、行为、部件或其组合的存在,并不排除一个或多个其它特征、数字、步骤、行为、部件或其组合存在或被添加的可能性。本技术中“多个”通常可以解释为两个或两个以上的含义。

34.图1是现有的具有多内存通道的gpu芯片100的一种示例性结构。如图1所示,gpu芯片100通常包含一个或者多个流处理器110,流处理器110还包括调度器111、一个或多个单指令多线程处理器112、一个或多个一级缓存113、内存管理单元114和共享存储115。流处理器110通过交叉开关矩阵或者交叉开关网络116与一个或多个二级缓存117以及pcie控制器120进行数据的读写。

35.一个或多个二级缓存117通过对应连接的存储控制器118对连接的存储器119进行读写访问。每个二级缓存117和与之对应连接的存储控制器118、存储器119即构成了4内存通道。除此之外,gpu芯片100还可以包含视频编解码121和/或其他处理核心(图中未示出)。

36.需要说明的是,图1仅示例性地描述了4个单指令多线程处理器112、4个二级缓存117、4个存储控制器118的gpu芯片结构,实际上,gpu芯片100还可以包括更多数量的单指令多线程处理器112、二级缓存117、存储控制器118,从而可以实现更多内存通道的存储结构。此外,除了图1所描述的gpu芯片,多内存通道芯片还可以包括并不限于cpu、ai、现场可编程门阵列、视频编解码等芯片,这些芯片结构中,涉及多内存通道的存储结构相类似,在此不再赘述。

37.本技术实施例仅以多内存通道的gpu芯片为例进行实施方式描述,但不表示本技术实施例的技术方案仅适用于图1所述的gpu芯片,上述图1所示gpu结构不能理解为限制本技术的保护范围。

38.图1中,内存管理单元114通常包含旁路转换缓冲器和地址翻译部件。旁路转换缓冲器,又称为页表缓冲,用于存放虚拟地址到物理内存地址的转换表,地址翻译部件用于基于旁路转换缓冲器将芯片处理核心发送的读写指令对应的虚拟地址翻译为物理内存地址。内存管理单元将虚拟地址翻译为物理内存地址之后,通知对应的存储控制器根据物理内存地址去对应的存储单元读写数据。

39.多内存通道芯片可以包含1个或多个内存通道,例如不同的计算系统可能根据需求采用1、2、4、8、16、32组等多种内存通道数量。如图2所示,为了提高内存读取的效率,通常将每片内存划分为多个寄存器库(称为bank),每个bank内部有多个行(称为row),每行的行大小row_size通常为64、128或者256字节。每个内存通道对应的存储器可以包括多个bank。

40.对于每个bank的一个行,假如行大小row_size 为256字节,寄存器库数量num_banks为4,内存通道数量num_channles为4,则内存一个页面的空间大小为4kb,即 row_size * num_banks* num_channles= 256 * 4 *4 = 4096字节。

41.其中,内存的通道数,实际上是一种内存的带宽加速技术,带宽倍增。最常见的是双通道,民用级电脑都支持。服务器还有3通道和4通道。下面以双通道为例,解释一下多通道技术:双通道,就是在北桥芯片级里设计两个内存控制器,这两个内存控制器可相互独立工作,每个控制器控制一个内存通道。

42.图3是多内存通道系统中一种32位物理内存地址的示例性结构示意图。如图3所

示,这种示例性的物理内存地址通常包括寄存器库索引、行索引、内存通道索引和行内地址偏移。其中,内存通道索引是指读写指令指定的物理内存通道号,寄存器库索引是指读写的目标数据所在的寄存器库编号,行索引是指目标数据位于当前寄存器库中的行地址,行内地址偏移是指目标数据在当前行中的偏移地址。

43.作为一种示例的地址计算方式,图3中以32位地址中31

‑

12位表示为行索引,11

‑

10位表示寄存器库索引,9

‑

8位表示内存通道索引,7

‑

0表示行内地址偏移。需要说明的是,本技术并不对物理内存地址的具体编码方式进行限定。

44.如前所述,上述具有多内存通道的芯片一旦部分内存通道发生损坏,并且每个芯片发生损坏的通道可能不同,而传统的多内存通道芯片无法实现仅使用其中一部分内存通道,只能将内存区域平均分配到全部内存通道,因此,这种部分内存通道的损坏会极大提高芯片制造和使用成本,降低计算系统的可靠性。为此,本技术实施例提出一种改进后的多内存通道的存取方式,通过定义虚拟内存通道和对芯片中多内存通道的运行时程序化配置,实现虚拟化系统对资源的灵活分配,从而即便发生个别通道损坏的情形,也能确保正确的内存数据读写。

45.图4是根据本技术一实施例的多内存通道的内存存取装置400的结构示意图。如图4所示,多内存通道的内存存取装置400包括:配置寄存器410,用于设置虚拟内存通道和物理内存通道的配置信息,该配置信息包括虚拟内存通道索引和物理内存通道索引之间的映射关系。

46.内存管理单元420,用于基于内存访问请求的物理内存地址和该配置信息,计算得到目标虚拟内存通道索引。

47.内存管理单元420,具体用于基于目标虚拟内存通道索引和映射关系计算,得到目标虚拟内存通道索引映射的目标物理内存通道索引。

48.存储控制器430,与所述物理内存通道对应设置,用于控制对存储器的存取访问。其中,存储控制器430具体用于根据内存访问请求的物理内存地址,经由目标物理内存通道索引对应的物理内存通道,对目标存储器中的目标数据进行存取访问。

49.本技术实施例通过配置寄存器定义物理内存通道和虚拟内存通道之间的映射关系,从而将芯片中多个物理内存通道映射到虚拟内存通道,通过对多内存通道的运行时程序化配置,来自处理核心的内存访问请求的物理内存地址仅需指定到虚拟内存通道,而无需指定具体的物理内存通道,这样即使出现内存通道的损坏,也能通过对剩余可用物理内存通道的配置,确保内存数据读写正常,从而可以提高芯片制造的良品率,并提高芯片物理服务年限和系统可靠性。进一步地,本实施例的技术方案还可以实现虚拟化系统对资源的灵活分配,实现多用户虚拟机任意划分资源,达到最佳资源分配,并且实现虚拟机之间的物理隔离,还可以无缝切换多内存通道系统的低功耗状态和高功耗状态时的多内存系统配置。

50.本实施例中,配置寄存器410可以采用一个或多个通用目的寄存器或者其他专用寄存器实现。配置寄存器410还可以用16位、32位或者64位进行上述配置信息的定义。需要说明的是,图4仅示意性地示出了4个内存通道的示例,实际上本实施例的方案不限于内存通道的数量,可以扩展到更多个内存通道的实施方式。

51.本实施例中,内存管理单元420可以是在现有的内存管理单元基础上改进软硬件

结构,其可以包括现有的内存管理单元通常包含的旁路转换缓冲和地址翻译部件等。在一些实施方式中,内存管理单元420也可以包括一个或多个,可以针对多个处理核心分别实现可配置的内存通道配置管理。

52.在一些实施方式中,该配置信息还包括虚拟内存通道数、可用的物理内存通道数和内存通道使能掩码,其中,虚拟内存通道数不大于可用的物理内存通道数,内存通道使能掩码用于指示与可用的物理内存通道数对应的可读写物理内存通道。其中,虚拟内存通道数是指当前配置信息中定义的虚拟内存通道数量,可用的物理内存通道数只是当前启用的物理内存通道数量,其与内存通道使能掩码的指示相一致。

53.在一些实施方式中,该配置信息还包括目标存储器中的寄存器库的数量和行大小。

54.在一些实施方式中,配置信息还包括虚拟内存通道使能标识,该虚拟内存通道使能标识用于指示是否启用虚拟内存通道。

55.在一些实施方式中,内存管理单元用于将物理内存地址除以寄存器库的数量与行大小的乘积的商与虚拟内存通道数求模的结果,作为目标虚拟内存通道索引。

56.在一些实施方式中,存储控制器,还用于根据内存访问请求的物理内存地址,经由目标物理内存通道索引对应的物理内存通道,对目标存储器中的目标数据进行存取访问包括:存储控制器根据物理内存地址,计算得到目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移;存储控制器基于目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移实现对目标数据的存取访问。

57.在一些实施方式中,存储控制器根据物理内存地址,计算得到目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移包括:将物理内存地址除以寄存器库的行大小的商与寄存器库掩码进行逻辑与运算的结果,作为寄存器库索引,其中,存器库掩码为寄存器库的数量减1;将物理内存地址除以寄存器库的行大小、寄存器库的数量和虚拟内存通道数三者的乘积的商,作为目标数据所在存储区域的行索引;将物理内存地址与寄存器库的行大小减1的差进行逻辑与运算的结果,作为目标数据所在存储区域的行内地址偏移。

58.在一些实施方式中,该内存存取装置400还可以包括(图4中未示出):缓存单元,用于将内存访问请求转发至与存储控制器430。在一些实施方式中,该缓存单元可以包括处理芯片中的二级缓存和三级缓存的一者或两者。

59.在一些实施方式中,配置寄存器还用于为一个或多个处理核心设置虚拟内存通道和物理内存通道的多个配置信息,多个配置信息包括虚拟内存通道索引和物理内存通道索引之间不同的映射关系。

60.在一些实施方式中,多个配置信息还包括对应一个或多个处理核心的多个不同的虚拟内存通道数、可用的物理内存通道数和内存通道使能掩码。

61.下面结合8内存通道的多内存通道配置寄存器描述本技术实施例的具体实施方式。

62.内存通道配置寄存器表1和表2是采用2个32位寄存器实现物理内存通道和虚拟内存通道的配置信息的示例。本示例中,内存通道配置寄存器1配置虚拟内存通道和物理内存通道的基本配置信息,内存通道配置寄存器2配置虚拟内存通道索引和物理内存通道索引的映射关系。

63.表1(内存通道配置寄存器1) 表2(内存通道配置寄存器2)

ꢀ

基于上述表1和表2的配置寄存器的定义,如果第一个内存条发生故障(编号从0开始),则计算系统中只有7个内存通道可用,假设即将要访问的目标数据的48bits物理内存地址pyh_addr为0x00023bac829c。

64.内存通道配置寄存器1的配置信息为:物理内存通道数num_phy_mc=0x8;虚拟内存通道数num_virtural_mc=0x7;虚拟内存通道使能标识enable_config=0x1;保留位reserved=0x0(该数据域将被忽略);内存通道使能掩码mc_enable_mask=0xfd,即11111101;寄存器库数量num_banks=0x4;行大小row_size=0(对应256bytes)。

65.内存通道配置寄存器2的配置信息为:虚拟内存通道0:virtual_0_map_phy_mc=0x0;虚拟内存通道1:virtual_1_map_phy_mc=0x2;虚拟内存通道2:virtual_2_map_phy_mc=0x3;虚拟内存通道3:virtual_3_map_phy_mc=0x4;

虚拟内存通道4:virtual_4_map_phy_mc=0x5;虚拟内存通道5:virtual_5_map_phy_mc=0x6;虚拟内存通道6:virtual_6_map_phy_mc=0x7;虚拟内存通道7:virtual_7_map_phy_mc=0x0(该数据域将被忽略);保留位reserved=0x0(该数据域将被忽略)。

66.计算目标虚拟内存通道索引内存管理单元根据物理内存地址的编码方式,对目标虚拟内存通道索引virtual_mc_index可以采用如下公式计算得到:virtual_mc_index=phy_addr/(num_banks*row_size_bytes)%num_virtural_mc。

67.以上述物理内存地址0x00023bac829c为例,根据上述内存通道配置寄存器1中的相关配置信息,寄存器库的数量num_banks=0x4,寄存器库的行大小row_size=256字节,虚拟内存通道数num_virtural_mc=0x7,代入上述公式得到:virtual_mc_index=0x00023bac829c/(4*256)%7=6即根据该物理内存地址和配置信息所计算得到的目标虚拟内存通道索引为6。

68.计算目标物理内存通道索引内存管理单元在计算得到物理内存地址对应的目标虚拟内存通道索引后,根据内存通道配置寄存器2中配置的虚拟内存通道索引和物理内存通道索引的映射关系,可以计算得到该目标虚拟内存通道索引映射的目标物理内存通道索引phy_mc_index。

69.以上述物理内存地址0x00023bac829c为例,上述步骤中计算得到的virtual_mc_index为6时,物理内存通道索引的对应映射关系为virtual_6_map_phy_mc=7,因此目标物理内存通道索引phy_mc_index=7。

70.计算寄存器库索引、行索引和行内地址偏移在计算得到目标物理内存通道索引后,为了实现对目标数据的存取访问,内存管理单元需要将包含物理内存地址和数据的内存访问请求发送到该目标物理内存通道索引对应的物理内存通道。

71.在一些实施方式中,对于cpu芯片,内存管理单元可以先将请求发送到高速总线;对于gpu芯片,内存管理单元可以先将请求发送到交叉开关矩阵或者交叉开关网络。随后,高速总线或者交叉开关矩阵或者交叉开关网络将请求转发到二级缓存或者三级缓存。二级缓存或者三级缓存将请求发送到该目标物理内存通道索引对应映射的存储控制器。该存储控制器负责计算寄存器库索引、行索引和行内地址偏移。计算过程如下:首先,定义寄存器库掩码bank_mask=寄存器库数量num_banks

‑

1。

72.则寄存器库索引bank_index可以采用如下公式计算得到:bank_index=(pyh_addr/row_size_bytes)&bank_mask;行索引row_index可以采用如下公式计算得到:row_index=pyh_addr/(row_size*num_banks*num_virtural_mc);行内地址偏移offset_in_row可以采用如下公式计算得到:offset_in_row=pyh_addr&(row_size

‑

1)。

73.继续以上述物理内存地址0x00023bac829c为例。本示例中,num_banks=4,

bank_mask=3,row_size=256,num_virtural_mc=7,因此可以计算得到:bank_index=(0x00023bac829c/256)&3=2;row_index=0x00023bac829c/(256*4*7)=0x51aae,对应10进制即为334510(从0开始计数);offset_in_row=0x00023bac829c&(256

‑

1)=0x00023bac829c&(0xff)=0x9c(从0开始计数)。

74.获得上述计算结果后,该存储控制器即可根据寄存器库索引、行索引和行内地址偏移实现去对应的存储单元中实现对目标数据的存取访问。

75.图5是根据本技术一实施例的多内存通道的内存存取方法的流程示意图。如图5所示,该多内存通道的内存存取方法可以包括:步骤s510,在配置寄存器中设置虚拟内存通道和物理内存通道的配置信息,该配置信息包括虚拟内存通道索引和物理内存通道索引之间的映射关系;步骤s520,基于内存访问请求的物理内存地址和该配置信息,计算得到目标虚拟内存通道索引;步骤s530,基于目标虚拟内存通道索引和映射关系,计算得到目标虚拟内存通道索引映射的目标物理内存通道索引;步骤s540,根据内存访问请求的物理内存地址,经由目标物理内存通道索引对应的物理内存通道对目标存储器中的目标数据进行存取访问。

76.在一些实施方式中,步骤s510中,该配置信息还包括虚拟内存通道数、可用的物理内存通道数和内存通道使能掩码,其中,虚拟内存通道数不大于可用的物理内存通道数,内存通道使能掩码用于指示与可用的物理内存通道数对应的可读写物理内存通道。

77.在一些实施方式中,步骤s510中,该配置信息还包括目标存储器中的寄存器的库数量和行大小。

78.在一些实施方式中,步骤s510中,该配置信息还包括虚拟内存通道使能标识,该虚拟内存通道使能标识用于指示是否启用虚拟内存通道。

79.在一些实施方式中,步骤s520中,基于内存访问请求的物理内存地址和配置信息,计算得到目标虚拟内存通道索引可以包括:将物理内存地址除以寄存器库的数量与行大小的乘积的商与虚拟内存通道数求模的结果,作为目标虚拟内存通道索引。

80.在一些实施方式中,如图6所示,步骤s540中,根据内存访问请求的物理内存地址,经由目标物理内存通道索引对应的物理内存通道对目标存储器中的目标数据进行存取访问可以包括:步骤s610,根据物理内存地址计算得到目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移;步骤s620,基于寄存器库索引、行索引和行内地址偏移,通过目标物理内存通道索引对应的物理内存通道所对应设置的存储控制器实现对目标数据的存取访问。

81.在一些实施方式中,如图7所示,步骤s610中,根据物理内存地址计算得到目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移可以包括:步骤s710,将物理内存地址除以寄存器库的行大小的商与寄存器库掩码进行逻辑与运算的结果,作为寄存器库索引,其中,寄存器库掩码为寄存器库的数量减1;

步骤s720,将物理内存地址除以寄存器库的行大小、寄存器库的数量和虚拟内存通道数三者的乘积的商,作为目标数据所在存储区域的行索引;步骤s730,将物理内存地址与寄存器库的行大小减1的差进行逻辑与运算的结果,作为目标数据所在存储区域的行内地址偏移。

82.在一些实施方式中,通过步骤s520和s530计算得到目标虚拟内存通道索引映射的目标物理内存通道索引是通过内存管理单元计算得到。

83.在一些实施方式中,通过步骤s610计算得到目标数据所在存储区域的寄存器库索引、行索引和行内地址偏移是通过目标物理内存通道索引对应的物理内存通道所对应设置的存储控制器计算得到。

84.在一些实施方式中,在配置寄存器中设置虚拟内存通道和物理内存通道的配置信息还包括:为一个或多个处理核心在配置寄存器中设置虚拟内存通道和物理内存通道的多个配置信息,多个配置信息包括虚拟内存通道索引和物理内存通道索引之间不同的映射关系。

85.在一些实施方式中,多个配置信息还包括对应一个或多个处理核心的多个不同的虚拟内存通道数、可用的物理内存通道数和内存通道使能掩码。

86.从而,在多个处理核心的多内存通道芯片中,可以针对一个或多个处理核心实现多种内存通道的灵活配置,满足虚拟化系统对资源的灵活配置需求。

87.在一些实施方式中,根据内存访问请求的物理内存地址,经由目标物理内存通道索引对应的物理内存通道,对目标存储器中的目标数据进行存取访问还可以包括:经由缓存单元将内存访问请求转发至与目标物理内存通道索引对应的物理内存通道所对应设置的存储控制器。缓存单元可以包括二级缓存和三级缓存中的一者或二者。

88.图8是根据本技术一实施例的数据处理设备800的结构示意图。如图8所示,该数据处理设备800包括:一个或多个处理单元810及如前述任一实施例所述的多内存通道的内存存取装置820。

89.其中,一个或多个处理单元810可以包括但不限于各类处理芯片中处理器核心,例如单指令多线程处理器。

90.在一些实施方式中,数据处理设备可以包括中央处理单元、图形处理单元、数字处理单元、现场可编程门阵列、人工智能芯片、视频编解码芯片中的一种或多种。

91.图9

‑

图12是在8内存通道的gpu或cpu芯片中的具体应用示意图。其中,图9描述了现有技术中的内存通道存取方式,如图9所示,原始gpu或cpu芯片中的8内存通道,所有内存通道0

‑

7都可正常工作,计算核心a和计算核心b可以访问所有内存通道的指定存储单元。

92.图10

‑

图12描述了采用本技术实施例的可配置内存通道存取方式。如图10所示,采用本技术实施例的灵活的内存通道配置,通过配置寄存器配置虚拟内存通道映射的可用物理内存通道,可以使得计算核心a仅仅能够都读写内存通道0

‑

2,计算核心b 只能读写内存通道3

‑

7,从而实现资源的灵活分配。

93.如图11所示,假设多内存通道gpu或cpu芯片中内存通道2和7损坏(或者对应的二级缓存2和7损坏),采用本技术实施例的灵活的内存通道配置,通过配置寄存器配置虚拟内存通道映射的可用物理内存通道,可以使得计算核心a仅仅能够都读写内存通道0

‑

1,计算核心b 只能读写内存通道3

‑

6,可以有效解决部分通道损坏导致的芯片良品率低的问题,提

高计算系统的物理服务年限和系统可靠性。

94.如图12所示,假设多内存通道gpu或cpu芯片中内存通道5(或者对应的二级缓存5损坏),采用本技术实施例的灵活的内存通道配置,通过配置寄存器配置虚拟内存通道映射的可用物理内存通道,可以使得计算核心a和b都能够读写内存通道0

‑

4和6

‑

7的指定存储单元,计算核心a和b的数据都不会被分配到内存通道5。

95.本技术实施例提出的多内存通道的存取装置、方法以及数据处理设备可以通过配置寄存器定义物理内存通道和虚拟内存通道之间的映射关系,从而将芯片中多内存通道映射到虚拟内存通道,实现对多内存通道的运行时程序化配置,使得来自处理核心的内存访问请求的物理内存地址仅需指定到虚拟内存通道,而无需指定具体的物理内存通道。相比现有技术,本技术实施例可以在处理芯片即使出现内存通道的损坏时,也能通过对剩余可用物理内存通道的灵活配置,确保内存数据读写正常,从而可以提高芯片制造良品率,并提高芯片物理服务年限和系统可靠性。

96.进一步地,本技术实施例还可以实现虚拟化系统对资源的灵活分配,在多核处理芯片中,每个计算核心或者应用进程都可以绑定一个或者多个的内存通道配置,实现多用户虚拟机任意划分资源,达到最佳资源分配,并且实现虚拟机之间的物理隔离,并且还可以无缝切换多内存通道系统的低功耗状态和高功耗状态时的多内存系统配置。

97.本技术实施例中所涉及到的步骤、单元或模块可以通过软件、硬件或其结合的方式实现。所描述的步骤、单元或模块也可以实现在计算处理设备的处理器中,其中单元或模块的名称并不构成对该单元或模块本身的限定。

98.本技术的实施方式并不限于上述实施例所述,在不偏离本技术的精神和范围的情况下,本领域普通技术人员可以在形式和细节上对本技术做出各种改变和改进,这些均被认为落入了本技术的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。