1.本发明属于微控制器芯片设计领域,尤其涉及一种含灵活多协议通讯接口外设的的微控制器芯片及其运行方法。

背景技术:

2.32位高性能微控制器(俗称mcu)应用广泛,为了支持各类用户的多种应用环境,实现微控制器的通用化,如图1所示,一般微控制器芯片会支持对外通讯的多种接口,包括串口(uart)、4线spi、两线i2c、两线usb等,并且有些接口还需要针对多元化应用提供多组冗余,导致mcu外设多、冗余。32位mcu例如ch32f103提供了3组串口、2组i2c、2组spi,但在大多数实际应用中,通常只会用到其中部分通讯接口。

3.大部分通讯接口是业界有共识的、协议明确的,但仍有部分通讯协议是各厂家自定义的非共识通讯协议,例如1线通讯接口就缺乏足够的业界共识,多个芯片厂商各自定义了自家的1线通讯协议,另外,两线通讯接口也存在多个名称类似但实际通讯协议不同的情况。

4.作为通用微控制器芯片厂家,如果考虑一芯通用,就需要在系统总线上挂载上述多种协议的通讯接口的控制器,这些控制器由纯硬件数字逻辑实现,支持多种灵活参数,但对于协议不够明确的非共识通讯接口,就远不是参数的问题,而是同名但协议不同的问题。所以微控制器芯片一般不提供这类非共识协议的通讯接口,而是留给用户自行用软件控制i/o模拟实现。但软件实现存在缺点,这类非共识通讯协议一般比较低速,多数在几十到几百kbit,传几个字节数据就可能需要数微秒到数百微秒,而高性能微控制器芯片的主处理器内核至少运行在几十或几百mhz,用于低速通讯非常占用cpu时间,也浪费了大量功耗,并且协议交互过程会被系统其它外设中断频繁打断。而如果采用中断方式实现,则会对微控制器芯片造成每隔数微秒就一次中断的频繁干扰,降低系统效率。

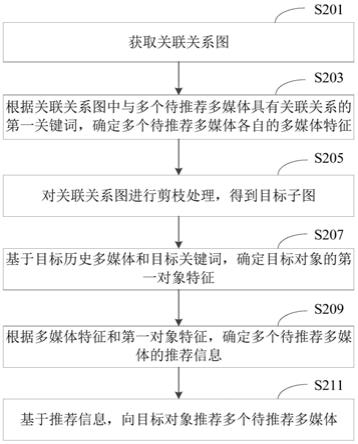

技术实现要素:

5.发明目的:为了解决现有高性能微控制器不便于支持非共识通讯协议的问题、以及现有通讯接口外设无法支持灵活协议、需要提供多组冗余固定协议通讯接口造成浪费的问题,本发明提供一种含多协议通讯接口外设的微控制器芯片及其运行方法。

6.技术方案:一种含多协议通讯接口外设的微控制器芯片,包括主处理器内核、系统总线、若干外设、i/o端口,所述外设包括多协议通讯接口外设,所述多协议通讯接口外设连接到系统总线上,所述多协议通讯接口外设与i/o端口连接,所述多协议通讯接口外设包括risc指令集微内核、代码存储器及存储在代码存储器上并可被risc指令集微内核执行的代码程序,所述代码程序至少包括置1和清0两种位操作指令,所述指令为单周期指令,当risc指令集微内核执行该代码程序时可实现i/o端口输出1或0。

7.进一步地,所述主处理器内核的数据位宽为32位或64位,所述risc指令集微内核的数据位宽为4位或8位。

8.进一步地,还包括选择器,所述多协议通讯接口外设、主处理器内核通过选择器连接i/o端口。

9.进一步地,所述代码存储器为sram,且所述代码存储器连接到系统总线上,所述代码存储器还可用于存储主处理器内核的数据。该sram便于动态加载不同协议的i/o端口控制程序的目标代码。该sram还可以在不需要多协议通讯接口外设时,作为主处理器的数据存储器使用。

10.进一步地,所述代码存储器为一次性可编程存储器otp,所述代码存储器中的代码程序在出厂前由微控制器芯片厂商预置。

11.进一步地,所述主处理器内核包含多个外设数据交换寄存器,所述外设数据交换寄存器设置在多协议通讯接口外设一侧,所述外设数据交换寄存器对应于n个risc指令集微内核的数据位宽的数据寄存器,n为主处理器内核的数据位宽除以risc指令集微内核的数据位宽的值。

12.进一步地,所述主处理器内核还包括中断控制器,所述多协议通讯接口外设通过中断请求信号线与所述中断控制器连接。

13.进一步地,还包括dma控制器、仲裁器中至少一种,所述多协议通讯接口外设通过若干信号线与dma控制器、仲裁器中至少一种连接。

14.进一步地,多协议通讯接口外设所连接的i/o端口数量不超过4个。

15.一种上述含多协议通讯接口外设的微控制器芯片的运行方法,其特征在于,包括以下步骤:向微控制器芯片的flash存储器中烧录主程序目标代码,所述主程序目标代码包括i/o端口控制程序的目标代码,i/o端口控制程序的目标代码基于risc指令集微内核开发而成;芯片上电或复位,risc指令集微内核默认处于禁用状态,主处理器内核将i/o端口控制程序的目标代码从芯片的flash存储器加载到多协议通讯接口外设中的代码存储器中;使能risc指令集微内核运行。

16.本发明提供一种含多协议通讯接口外设的微控制器芯片及其运行方法,相比较现有技术,具有以下有益效果:(1)灵活性和通用性。同样作为微控制器芯片内部的通讯接口外设,传统方案是针对单一通讯协议的,而依据本发明设计的多协议通讯接口外设,通过加载不同通讯协议的i/o端口控制程序的目标代码,就可以从容面对多元化的非共识通讯协议,进一步提高了微控制器芯片的通用性。

17.(2)可升级。一般微控制器芯片设计时已内置常用通讯接口控制器,制造完成后即无法新增,也无法适用通讯协议的较大改版和升级。而依据本发明设计的微控制器芯片制造完成后,仍然可以通过更新通讯协议的i/o端口控制程序去跟随第三方通讯协议的版本升级,提高了微控制器芯片的兼容性,以及适应技术和市场变化的能力。

18.(3)低成本。多协议通讯接口外设中的risc指令集微内核为专用risc指令集微内核,专用于处理i/o接口协议,可以对此核进行性能和成本优化,减小位宽以降低成本,增加或优化单周期的位操作指令以提高i/o操作效率,减少不必要的地址空间和算法类指令以

控制此内核的规模和成本,只需要2000到3500门的规模即可实现多协议的通讯接口外设。作为对比,常规的i2c协议两线接口专用外设控制器也需要2000多门的规模;作为主处理器内核的基本款32位m3内核约70000门规模,64位内核则成倍增加。可见,该专用risc指令集微内核规模与专用协议的普通外设为同一档次,远远小于主处理器内核的规模,与追求运算性能而采用双核甚至多核的微控制器方案的目标和思路完全不同。另外,通用性使得系统方案可以减少一部分冗余或备用的通讯接口,进一步节约成本。

19.之所以能以低成本实现高灵活性,得益于方案的针对性和微内核设计目标的理解,针对i/o接口协议,尤其是几mhz以下的中低速的串行接口协议,其数据量小,速度慢,适合专用risc指令集微内核用若干指令模拟接口通讯协议,以更多时间换取更小硬件规模和更高灵活性。相比之下,纯硬件数字逻辑专用控制器更适合协议确定的高速接口。

附图说明

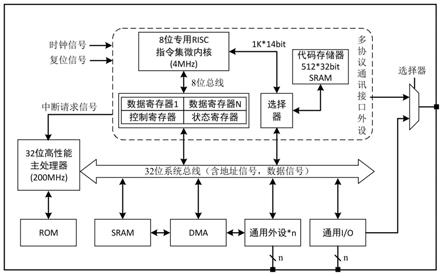

20.图1为现有技术32位高性能微控制器架构图,外设冗余,通常无1线接口;图2为实施例一含多协议通讯接口外设的微控制器架构图;图3为实施例二含多协议通讯接口外设的微控制器架构图;图4为实施例三含多协议通讯接口外设的微控制器架构图。

具体实施方式

21.下面结合附图和具体实施例对本发明做进一步解释说明。

22.实施例一:一种含多协议通讯接口外设的微控制器芯片,包括主处理器内核、系统总线、若干外设及i/o端口,所述外设包括多协议通讯接口外设,所述多协议通讯接口外设作为若干外设模块之一挂在于微控制器芯片的系统总线上,通过时钟信号线、复位信号线、地址信号线、数据信号线连接,地址信号线、数据信号线包含在系统总线中。所述多协议通讯接口外设与i/o端口连接,所述多协议通讯接口外设包括risc指令集微内核、代码存储器及存储在代码存储器上并可被risc指令集微内核执行的代码程序,所述代码程序至少包括置1和清0两种位操作指令,所述指令为单周期指令,当risc指令集微内核执行该代码程序时可高效实现i/o端口输出1或0。进一步地,还可以包括左移、右移等移位操作指令,位复制、位插入、位测试、循环等指令等,以便更高效地支持i/o状态读取、输出设置操作及模仿接口协议。

23.本实施例中的主处理器内核的数据位宽为32位,也可以是超过32位,如64位;risc指令集微内核的数据位宽为8位,也可以是不超过8位,如4位。

24.该risc指令集微内核为专用risc指令集微内核,专用于控制i/o端口的输出和输入,经过优化后,位宽小,速度高,位操作指令经过优化以提高i/o操作效率,减少不必要的较大地址空间和算法类指令以控制微内核规模以节约成本。与普通双核cpu中基本同等次并列的双核设计不同,该risc指令集微内核仅仅作为系统总线的一个外设,表现出与普通硬件逻辑专用控制器类似的特性和权限,专用于处理i/o接口协议,其规模和所需资源远远小于主处理器内核。

25.本实施例的多协议通讯接口外设含1线外部连接,与一个i/o端口连接,也可以根据需要连接不同数量的i/o端口,一般不超过四个。多协议通讯接口外设可以直接与i/o端

口连接,也可以通过选择器连接i/o端口。如图2,本实施例的多协议通讯接口外设、主处理器内核通过选择器连接i/o端口,选择器用于选择多协议通讯接口外设连接i/o还是主处理器内核连接i/o。当不需要此外设时,可以选择主处理器内核连接i/o,直接将该i/o当做普通gpio使用。

26.本实施例中的代码存储器中存储有risc指令集微内核的多条指令,本实施例中代码存储器采用512*32bit结构的sram,数据位宽为32位,便于高效连接到系统总线上。而在作为代码存储器提供指令时每32位舍弃4位,组合为1k*14bit的数据接口,可用于存储1024条14位宽的指令。sram允许用户自行编写通讯协议程序实现自定义通讯接口,当不使用多协议通讯接口外设时,该sram还可作为主处理器的数据存储器存储数据,不浪费资源。对于单口sram,系统总线和risc指令集微内核的指令通道可以通过选择器或者仲裁器后连接sram;对于双端口sram,则系统总线和risc指令集微内核的指令通道各自连接sram的一个端口。

27.所述主处理器内核包含多个外设数据交换寄存器,包括输入数据寄存器、输出数据寄存器、控制寄存器、状态寄存器等,所述外设数据交换寄存器设置在多协议通讯接口外设一侧,所述每个外设数据交换寄存器对应于不超过4个risc指令集微内核的数据位宽的数据寄存器,4为主处理器内核的数据位宽32除以risc指令集微内核的数据位宽8所得。4个8位宽的数据合并后按32位提交给系统总线,方便主处理器以单周期存取,可节约主处理器内核的cpu时间。

28.所述主处理器内核还包括中断控制器,所述多协议通讯接口外设通过中断请求信号线与所述中断控制器连接。

29.一种上述含多协议通讯接口外设的微控制器芯片的运行方法,包括以下步骤:向微控制器芯片的flash存储器中烧录主程序目标代码,所述主程序目标代码包括i/o端口控制程序的目标代码。i/o端口控制程序的目标代码基于risc指令集微内核预先开发而成,可以预先发开若干种通讯协议的i/o端口控制程序,根据实际需要选择对应通讯协议的i/o端口控制程序,整合到微控制器芯片的主程序目标代码中;芯片上电或复位,risc指令集微内核默认处于禁用状态,主处理器内核先运行,主处理器内核将i/o端口控制程序的目标代码从芯片的flash存储器加载到多协议通讯接口外设中的代码存储器中;使能risc指令集微内核运行。

30.其中,目标代码的加载以及risc指令集微内核运行,也可以只在需要使用时执行。

31.另外,也可以在芯片上电或复位后,由硬件自动将i/o端口控制程序的目标代码从芯片的flash存储器加载到多协议通讯接口外设中的代码存储器中并使能risc指令集微内核运行。

32.此外,根据需要,在risc指令集微内核运行期间,还可以随时更换i/o端口控制程序的目标代码,先将risc指令集微内核禁用,主处理器内核将新的i/o端口控制程序的目标代码从芯片的flash存储器加载到多协议通讯接口外设中的代码存储器中,重新运行risc指令集微内核即可实现通讯协议的更新。

33.实施例二:实施例二与实施例一相比,区别在于,实施例二的主处理器内核的数据位宽为32

位,主频200mhz;risc指令集微内核的数据位宽为8位,主频200mhz;其中代码存储器采用1k*32bit结构的双端口sram,在提供代码时由最低位地址信号选择32位数据的低16位或16位输出,构成2k*16bit的4kb指令存储空间;含2个外部io连接及其模式控制,通过多个控制信号线和模式信号线及输入输出信号线与2个i/o端口连接,可实现串口、两线及一线协议通讯。

34.微控制器芯片还包括dma控制器和/或仲裁器,所述多协议通讯接口外设通过若干信号线与dma控制器和/或仲裁器连接,便于直接与系统主存储器交换数据,进一步减少对主处理器内核的cpu时间的占用。

35.实施例三:实施例三与实施例一相比,区别仅在于,实施例三的主处理器内核为32位数据宽度,主频100mhz;risc指令集微内核的数据位宽为4位,主频10mhz。risc微内核侧的每8个数据寄存器组合成一个主处理器可高效存取的32位寄存器,包含多个这样的32位寄存器用于交换数据、控制位和状态;含1线外部io连接及其模式控制,通过多个信号与1个i/o端口连接。代码存储器采用比flash成本低的一次性可编程存储器otp,具有1k*10bit的指令存储空间;该otp中的代码可以在出厂前由微控制器芯片厂商预置,完全独立于微控制器的主程序,便于对用户保密,提高安全性。芯片出厂前预置接口协议的目标程序相比重新设计纯硬件控制器,节约了芯片后端布线、数据处理、制板、流片、封装等多个环节的时间,有利于快速升级协议、及时响应市场需求。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。