1.本技术涉及芯片技术,特别地,涉及提供可配置时钟的闪存通道的存储设备的控制部件及其存储设备。

背景技术:

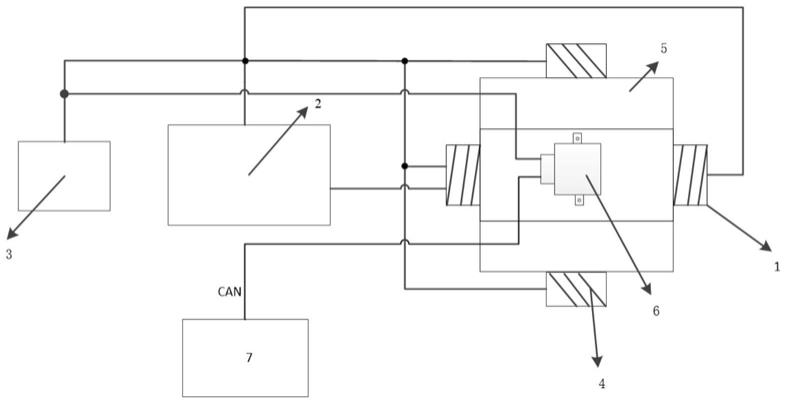

2.图1展示了存储设备的框图。存储设备102同主机相耦合,用于为主机提供存储能力。主机同存储设备102之间可通过多种方式相耦合,耦合方式包括但不限于通过例如sata(serial advanced technology attachment,串行高级技术附件)、scsi(small computer system interface,小型计算机系统接口)、sas(serial attached scsi,串行连接scsi)、ide(integrated driveelectronics,集成驱动器电子)、usb(universal serial bus,通用串行总线)、 pcie(peripheral component interconnect express,pcie,高速外围组件互联)、 nvme(nvm express,高速非易失存储)、以太网、光纤通道、无线通信网络等连接主机与固态存储设备102。主机可以是能够通过上述方式同存储设备相通信的信息处理设备,例如,个人计算机、平板电脑、服务器、便携式计算机、网络交换机、路由器、蜂窝电话、个人数字助理等。存储设备102 包括接口103、控制部件104、一个或多个nvm芯片105以及dram(dynamicrandom access memory,动态随机访问存储器)110。

3.nand闪存、相变存储器、feram(ferroelectric ram,铁电存储器)、 mram(magnetic random access memory,磁阻存储器)、rram(resistiverandom access memory,阻变存储器)、xpoint存储器等是常见的nvm。

4.接口103可适配于通过例如sata、ide、usb、pcie、nvme、sas、以太网、光纤通道等方式与主机交换数据。

5.控制部件104用于控制在接口103、nvm芯片105以及dram 110之间的数据传输,还用于存储管理、主机逻辑地址到闪存物理地址映射、擦除均衡、坏块管理等。控制部件104可通过软件、硬件、固件或其组合的多种方式实现,例如,控制部件104可以是fpga(field

‑

programmable gate array,现场可编程门阵列)、asic(application specific integrated circuit,应用专用集成电路)或者其组合的形式。控制部件104也可以包括处理器或者控制器,在处理器或控制器中执行软件来操纵控制部件104的硬件来处理io (input/output)命令。控制部件104还可以耦合到dram 110,并可访问 dram 110的数据。在dram可存储ftl表和/或缓存的io命令的数据。

6.控制部件104包括闪存接口控制器(或称为介质接口控制器、闪存通道控制器),闪存接口控制器耦合到nvm芯片105,并以遵循nvm芯片105 的接口协议的方式向nvm芯片105发出命令,以操作nvm芯片105,并接收从nvm芯片105输出的命令执行结果。已知的nvm芯片接口协议包括“toggle”、“onfi”等。申请号为201510253428.1、专利名称为“微指令序列执行方法及其装置”的中国专利中提供了介质接口控制器的例子,通过执行微指令,将存储介质访问命令施加给nvm芯片。申请号为 2020106080147、专利名称为“自适应nvm读取方法及其装置”的中国专利申请,申请号为“202010615178.2”、专利名称为“智能读重做方法及其

介质接口控制器”的中国专利申请,申请号为“202010207004.2”、专利名称为“用于读命令融合的介质接口控制器及存储控制器”的中国专利申请,申请号为201810380329.3、专利名称为“乱序执行nvm命令的方法与装置”的中国专利,申请号为201610836531.3、专利名称为“生成nvm芯片接口命令的方法与装置”的中国专利申请中均提供了介质接口控制器的例子。

7.nvm芯片包括一个或多个逻辑单元(logic unit,lun)。nvm芯片封装内可包括一个或多个管芯(die)。典型地,逻辑单元对应于单一的管芯。逻辑单元可包括多个平面(plane)。逻辑单元内的多个平面可以并行存取,而nvm芯片内的多个逻辑单元可以彼此独立地执行命令和报告状态。在可从

8.http://www.micron.com/~/media/documents/products/other%20documents/onfi3_0gold.ashx获得的“open nand flash interface specification(revision3.0)”中,提供了关于目标(target)、逻辑单元、平面(plane)的含义,其为现有技术的一部分。本技术中,除非另外指出,目标(target)与逻辑单元(lun)的使用可互换。

9.图2展示了存储设备的控制部件的详细的框图。

10.主机以遵循存储协议的io命令访问存储设备。控制部件根据来自主机的io命令,生成一个或多个存储命令并提供给介质接口控制器。介质接口控制器根据存储命令生遵循nvm芯片的接口协议的存储介质访问命令(例如,编程命令、读命令、擦除命令)。控制部件还跟踪从一个io命令生成的所有存储命令都被执行完成,并向主机指示io命令的处理结果。

11.参看图2,控制部件包括例如主机接口、主机命令处理单元、存储命令处理单元、介质接口控制器与存储介质管理单元。主机接口获取主机提供的 io命令,并生成存储命令提供给存储命令处理单元。存储命令例如访问相同大小的存储空间,例如4kb。将nvm芯片中记录的对应一个存储命令所访问数据的数据单元称为数据帧。物理页记录一个或多个数据帧。例如,物理页的大小17664字节,而数据帧大小为4kb,则一个物理页能存储4个数据帧。

12.存储介质管理单元为每个存储命令维护逻辑地址到物理地址的转换。例如,存储介质管理单元包括ftl表。对于读命令,存储介质管理单元输出存储命令所访问的逻辑地址对应的物理地址,对于写命令,存储介质管理单元为其分配可用的物理地址,并记录其访问的逻辑地址与分配的物理地址的映射关系。存储介质管理单元还维护诸如垃圾回收、磨损均衡等管理nvm芯片所需的功能。

13.存储命令处理单元根据存储介质管理单元提供的物理地址,操作介质接口控制器向nvm芯片发出存储介质访问命令。为了清楚的目的,将存储命令处理单元发送给介质接口控制器的命令称为介质接口命令,而将介质接口控制器发送给nvm芯片的命令称为存储介质访问命令。存储介质访问命令遵循nvm芯片的接口协议。

14.图3展示了控制部件中的介质接口控制器与多个通道。

15.nvm芯片有多种类型。各种类型的nvm芯片例如来自不同的供应商、遵循不同的nvm芯片接口协议(例如,“toggle”、“onfi”等)、提供用于不同应用场景的不同特性(例如,低延迟、大容量、高耐久度等),同时不同类型的nvm芯片的容量也不尽相同。

16.介质接口控制器通过通道耦合nvm芯片。为提高存储密度并且平衡控制器芯片的引脚数量,通常在单个通道耦合例如2个或更多nvm芯片(或者以lun或target为单位耦合到通道)。耦合到相同通道的多个target共享总线(包括控制总线与数据总线),以减少用于将

nvm芯片耦合到介质接口控制器所以的引脚数量。通道为耦合到该通道的各target提供其专用的芯片使能(ce)信号,以在任意时刻,避免向多于一个target传输信号。

17.例如图3中的介质接口控制器提供了4个通道引脚,分别是通道1引脚、通道2引脚、通道2引脚和通道4引脚。每个通道引脚用于耦合到通道 (channel),每个通道包括至少一个nvm芯片,在同一通道内的多个nvm 芯片共用一个时钟信号,从而通道可以理解为一组nvm芯片的集合。而在介质接口控制器内部,每个通道引脚连接到通道电路。不同于通道,通道电路为介质接口控制器中的一种电路,用于控制通道上的信号发送与接收。

技术实现要素:

18.op(over provisioning,过度供应)是固态存储设备中的一种常用的手段,通常采用增设预留空间实现,预留空间是存储设备的nvm芯片提供的存储容量与提供给使用者的存储容量的差。由于预留空间存在,使用者看到固态存储设备的容量是小于固态存储设备的实际容量。增大预留空间能够得到显而易见的好处,预留空间越大写放大(write amplification,wa)就越小,预留空间越大随机写的速度就越快,从而固态存储设备的写性能越好。

19.对预留空间的需求是变化的。不同容量、不同性能需求,都导致对预留空间的需求变化。而存储设备的控制部件(芯片)的通道数量无法快速改变。为了改变通道数量而开发一款芯片,需要数年时间。因而需要在既有的控制部件的既有通道数量配置的约束下,满足多样化预留空间的需求。进一步的需求在于,在存储设备的使用过程中,为其提供更多的预留空间。使用中的存储设备的nvm芯片已被写入了数据,而难以被替换。为了增加预留空间,可向存储设备的通道上增加新的nvm芯片,但这导致成本的升高。

20.增加新的nvm芯片来增大预留空间除了会导致成本升高之外,由于存储设备的电路板的面积的限制,通常无法在电路上预留很大的面积来容纳可能不会被使用的多颗nvm芯片。这导致无法将用于增加预留空间的nvm芯片均分到控制部件的多个或所有通道上,而若将增加的nvm芯片设置于1 个或少量的通道上,将导致出现不同的通道之间的容量产生差异。在存储设备的正常使用中,通道的容量同通道被访问的概率正相关。随着差异的增大,不同通道之间的均衡性也随之恶化。容量大的通道被更多访问,但通道的数据传输带宽的上限不依赖于容量而改变,从而容量大的通道会因访问过多、传输带宽达到上限而成为存储设备的性能瓶颈。由于配置了预留空间,一些通道的访问多,而另一些通道的访问少也导致固态存储设备均衡性变差的技术问题。

21.根据本技术的第一方面,提供了根据本技术第一方面的第一控制部件,包括至少一个锁相环和多个通道电路,所述多个通道电路用于耦合nvm芯片,每个通道电路与一个锁相环耦合;每个锁相环获取第一时钟信号,所述第一时钟信号为外部输入所述控制部件的时钟信号;每个锁相环根据配置信息,对第一时钟信号进行调整,生成第二时钟信号,所述第一时钟信号的频率与所述第二时钟信号的频率不同;每个锁相环向与自身耦合的通道电路,输出第二时钟信号;其中,多个通道电路接收到至少两种不同频率的时钟信号。

22.根据本技术第一方面的第一控制部件,提供了根据本技术第一方面的第二控制部件,每个通道电路均与每个锁相环耦合,每个通道电路均接收至少两种不同频率的第二时钟信号。

23.根据本技术第一方面的第一控制部件,提供了根据本技术第一方面的第三控制部件,所述多个通道电路包括至少一个第一通道电路和至少一个第二通道电路;其中,每个第一通道电路与输出具有第一频率的第二时钟信号的锁相环耦合,每个第二通道电路与输出具有第二频率的第二时钟信号的锁相环耦合,所述第一频率与所述第二频率不同。

24.根据本技术第一方面的第一控制部件,提供了根据本技术第一方面的第四控制部件,所述多个通道电路包括至少一个第一通道电路和至少一个第三通道电路;其中,每个第一通道电路与输出具有第一频率的第二时钟信号的锁相环耦合;每个第三通道电路与输出具有第二频率的第二时钟信号的锁相环耦合,且每个第三通道电路与输出具有第一频率的第二时钟信号的锁相环耦合;其中,所述第一频率与所述第二频率不同。

25.根据本技术第一方面的第一控制部件,提供了根据本技术第一方面的第五控制部件,所述多个通道电路包括至少一个第一通道电路、至少一个第二通道电路和至少一个第三通道电路;其中,每个第一通道电路与输出具有第一频率的第二时钟信号的锁相环耦合;每个第二通道电路与输出具有第二频率的第二时钟信号的锁相环耦合;每个第三通道电路与输出具有第二频率的第二时钟信号的锁相环耦合,且每个第三通道电路与输出具有第一频率的第二时钟信号的锁相环耦合;其中,所述第一频率与所述第二频率不同。

26.根据本技术第一方面的第一至第五控制部件之一,提供了根据本技术第一方面的第六控制部件,所述控制部件还包括多个分频器,所述多个分频器与至少一个锁相环耦合,且所述多个分频器与所述多个通道电路耦合;其中,每个分频器获取第二时钟信号;每个分频器根据配置信息,对第二时钟信号进行调整,生成第三时钟信号,所述第三时钟信号的频率与所述第二时钟信号的频率相同或不同;每个分频器向与自身耦合的通道电路,输出第三时钟信号,每个分频器输出的第三时钟信号相同或不同。

27.根据本技术第一方面的第六控制部件,提供了根据本技术第一方面的第七控制部件,每个通道电路均与每个分频器耦合,每个通道电路均接收至少两种不同频率的第三时钟信号。

28.根据本技术第一方面的第六控制部件,提供了根据本技术第一方面的第八控制部件,所述多个通道电路包括至少一个第四通道电路和至少一个第五通道电路;其中,每个第四通道电路与输出具有第三频率的第三时钟信号的分频器耦合,每个第五通道电路与输出具有第四频率的第三时钟信号的分频器耦合,所述第三频率与所述第四频率不同。

29.根据本技术第一方面的第六控制部件,提供了根据本技术第一方面的第九控制部件,所述多个通道电路包括至少一个第四通道电路和至少一个第六通道电路;其中,每个第四通道电路与输出具有第三频率的第三时钟信号的分频器耦合;每个第六通道电路与输出具有第四频率的第三时钟信号的分频器耦合,且每个第六通道电路与输出具有第三频率的第三时钟信号的分频器耦合;其中,所述第三频率与所述第四频率不同。

30.根据本技术第一方面的第六控制部件,提供了根据本技术第一方面的第十控制部件,所述多个通道电路包括至少一个第四通道电路、至少一个第五通道电路和至少一个第六通道电路;其中,每个第四通道电路与输出具有第三频率的第三时钟信号的分频器耦合;每个第五通道电路与输出具有第四频率的第三时钟信号的分频器耦合;每个第六通道电路与输出具有第四频率的第三时钟信号的分频器耦合,且每个第六通道电路与输出具有第三频率的第三时钟信号的分频器耦合;其中,所述第三频率与所述第四频率不同。

31.根据本技术第一方面的第一至第十控制部件之一,提供了根据本技术第一方面的第十一控制部件,所述控制部件还包括至少一个多路复用器,所述至少一个多路复用器将锁相环和/或分频器耦合到所述多个通道电路,每个多路复用器用于将多个时钟信号中的一个时钟信号输入通道电路。

32.根据本技术第一方面的第十一控制部件,提供了根据本技术第一方面的第十二控制部件,所述至少一个多路复用器的数量与有多个时钟信号输入的通道电路数量相等,每个多路复用器与有多个时钟信号输入的通道电路一一对应。

33.根据本技术第一方面的第十一或第十二控制部件,提供了根据本技术第一方面的第十三控制部件,每个多路复用器根据指示信号选通多个时钟信号中的一个时钟信号,所述指示信号指示多个时钟信号的序号/输入位置。

34.根据本技术第一方面的第一至第十三控制部件之一,提供了根据本技术第一方面的第十四控制部件,所述控制部件还包括配置模块,所述配置模块维护配置信息;响应于获取到配置信息更新命令,所述配置模块更新自身存储的配置信息;所述配置模块向至少一个锁相环和/或至少一个分频器发送更新后的配置信息;响应于获取到更新后的配置信息,至少一个锁相环生成第二时钟信号和/或至少一个分频器生成第三时钟信号。

35.根据本技术的第二方面,提供了根据本技术第二方面的第一固态存储设备,所述固态存储设备包括控制部件和多个nvm芯片;其中,所述控制部件包括多个通道电路,所述控制部件通过所述多个通道电路与所述多个nvm芯片耦合,所述多个nvm芯片包括至少一个第一nvm芯片和至少一个第二 nvm芯片,所述多个通道电路的第一通道电路耦合的所有第一nvm芯片的容量和为第一容量,所述多个通道电路的二通道电路耦合的所有第二nvm 芯片的容量和为第二容量,所述第一容量不等于所述第二容量。

36.根据本技术第二方面的第一固态存储设备,提供了根据本技术第二方面的第二固态存储设备,若第一容量大于第二容量,输入第一nvm芯片的时钟信号的频率大于输入第二nvm芯片的时钟信号的频率;若第一容量小于第二容量,输入第一nvm芯片的时钟信号的频率小于输入第二nvm芯片的时钟信号的频率。

37.根据本技术第二方面的第一或第二固态存储设备,提供了根据本技术第二方面的第三固态存储设备,所述第一容量为m,所述第二容量为n,输入第一nvm芯片的时钟信号的频率为x,输入第二nvm芯片的时钟信号的频率为y,使得x/y=m/n;其中,m、n、x、y均为正整数。

38.根据本技术第二方面的第一至第三固态存储设备之一,提供了根据本技术第二方面的第四固态存储设备,所述控制部件为如上述第一方面中任一项所述的控制部件。

附图说明

39.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术中记载的一些实施例,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图。

40.图1为现有技术中的存储设备的框图;

41.图2为现有技术中存储设备中的控制部件的框图;

42.图3为现有技术中的控制部件中的介质接口控制器与多个通道的示意图;

43.图4a为本技术实施例提供的一种控制部件的结构示意图;

44.图4b为本技术实施例提供的一种控制部件的结构示意图;

45.图5为本技术实施例提供的又一种控制部件的结构示意图;

46.图6为本技术实施例提供的又一种控制部件的结构示意图;

47.图7为本技术实施例提供的再一种控制部件的结构示意图;

48.图8为本技术实施例提供的一种固态存储设备的结构示意图。

具体实施方式

49.下面结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

50.根据本技术的实施例,为了增大存储设备的预留空间,在一个或多个通道(而非全部通道)上增加nvm芯片。例如,存储设备有8个通道,每个通道耦合了1颗容量为64gb的nvm芯片,存储设备的既有的容量是512gb,而为了获得额外64gb的预留空间,在其一个通道上增置一颗容量为64gb 的nvm芯片。这时,存储设备的7个通道(记为c0

‑

c6)的每个上耦合了 64gb的nvm芯片,而1个通道(记为c7)上耦合了2颗64gb的nvm芯片。

51.因通道c7的容量比其他通道大,使得通道c7被访问的概率增加,容易成为性能瓶颈。存储设备的通道的最大传输带宽同通道的时钟频率正相关。通过提高时钟频率,能提高通道的最大传输带宽。但提高时钟频率也为控制部件的驱动能力和/或功耗带来挑战。进一步地,根据本技术的实施例,为通道c7提供更高频率的时钟,而为其他通道(c0

‑

c6)提供低于通道c7的时钟。从而同其他通道相比,通道c7获得了更大的带宽,能处理更多的访问请求,进而使得通道c7的每个请求能被及时处理,而不会因通道c7的访问请求过多而被阻塞。

52.根据本技术的实施例,为一个或多个通道提供可配置的时钟,使得一个或多个通道(例如少数通道)的时钟频率高于其他通道,以提升这些通道的带宽,并且不显著增加控制部件的功耗,也不对控制部件的驱动能力提出过高的要求。

53.图4a展示了本技术实施例提供的一种控制部件40的示意图。

54.控制部件40包括锁相环41、锁相环42及8个通道电路(分别是通道电路1、通道电路2、通道电路3、通道电路4、通道电路5、通道电路6、通道电路7和通道电路8)。通道电路用于驱动其对应的通道,以访问耦合到通道的nvm芯片。可选地,通道电路的数量为正整数,例如4个、8个、12 个等,通道电路的数量可根据实际需求设置,在此不作限制。

55.锁相环41与8个通道电路耦合,锁相环42也与8个通道电路耦合。8个通道电路用于驱动耦合了nvm芯片的通道。例如,对应于通道电路3的通道3(未示出)包括3个nvm芯片,通道电路3耦合到该通道3,则通道电路3得到通过通道3访问该3个nvm芯片。例如,控制部件包括介质接口控制器,8个通道电路设置在介质接口控制器(未在图4a中示出,可参考图 3)内,则8个通道电路各自通过通道引脚与通道耦合。可选地,控制部件 40包括三个及三个以上的锁相环,锁相环的数量可根据需求设置,在此不做限定。

56.锁相环41与锁相环42获取外部输入的第一时钟信号,例如第一时钟信号由控制部

件40之外的晶振生成,频率为20mhz。通常情况下,锁相环41和锁相环42输入的是同一个晶振生成的第一时钟信号。可选地,锁相环41和锁相环42获取到的是不同频率的第一时钟信号,例如,锁相环41输入的时钟信号的频率为20mhz,锁相环42输入的时钟信号的频率为30mhz。

57.锁相环41及锁相环42根据配置信息,对输入自身的第一时钟信号进行调整,生成第二时钟信号,所述第一时钟信号的频率与所述第二时钟信号的频率不同。例如,配置信息预先存储在控制部件内。配置信息指示了每个锁相环提升频率的倍数,例如,锁相环41对应的提升倍数为100倍,第一时钟信号的频率为20mhz,锁相环41生成的第二时钟信号的频率为2ghz。又如,锁相环42对应的提升倍数为50倍,第一时钟信号的频率为20mhz,锁相环 42生成的第二时钟信号的频率为1ghz。锁相环41和锁相环42均可以通过 8个通道电路向外输出第二时钟信号,和/或使8个通道的一个、多个或全部工作在第二时钟信号的频率。例如,根据配置信息,锁相环41向通道电路1 至通道电路4输出第二时钟信号,锁相环42向通道电路5至通道电路8输出第二时钟信号。可选地,锁相环41与锁相环42输出的第二时钟信号的频率相同或不同。

58.可选地,8个通道中的每个通道电路均与锁相环41及锁相环42耦合,从而每个通道电路均接收至少两种不同频率的第二时钟信号。例如,通道电路 3接收到3ghz和2ghz这两种第二时钟信号,由通道电路3确定使用哪一个时钟信号。比如,通道电路3根据配置或根据配置信息,确定使用频率高的时钟信号,则通道电路3根据3ghz的第二时钟信号工作。其中的配置为例如在控制部件40初始化时对通道电路3进行的配置,配置信息则是从控制部件40中获取的信息。

59.可选地,8个通道电路包括至少一个第一通道电路和至少一个第二通道电路。例如,通道电路2为第一通道电路,通道电路4、通道电路6和通道电路7为第二通道电路。其中,每个第一通道电路与输出具有第一频率的第二时钟信号的锁相环耦合,每个第二通道电路与输出具有第二频率的第二时钟信号的锁相环耦合,所述第一频率与所述第二频率不同。继续沿用前例,通道电路2与锁相环41耦合,但通道电路2不与锁相环42耦合;通道电路4、通道电路6和通道电路7与锁相环42耦合,但不与锁相环41耦合(这种连接关系未在图中示出)。本实施方式中的锁相环41与锁相环42输出的第二时钟信号的频率不同。

60.图4b展示了本技术实施例的又一控制部件的示意图。

61.如图4b所示,控制部件40’包括锁相环41、锁相环42及8个通道电路 (分别是通道电路1、通道电路2、通道电路3、通道电路4、通道电路5、通道电路6、通道电路7和通道电路8)。其中,第一通道电路为通道电路1、通道电路2和通道电路3,第三通道电路为通道4至通道8。每个第一通道电路与输出具有第一频率的第二时钟信号的锁相环耦合,即通道电路1到通道电路3与锁相环41耦合。每个第三通道电路与输出具有第二频率的第二时钟信号的锁相环耦合,且每个第三通道电路与输出具有第一频率的第二时钟信号的锁相环耦合,即通道电路4至通道电路8与锁相环41和锁相环42耦合。其中,所述第一频率与所述第二频率不同。

62.可选地,所述多个通道电路包括至少一个第一通道电路、至少一个第二通道电路和至少一个第三通道电路;其中,每个第一通道电路与输出具有第一频率的第二时钟信号的锁相环耦合;每个第二通道电路与输出具有第二频率的第二时钟信号的锁相环耦合;每

个第三通道电路与输出具有第二频率的第二时钟信号的锁相环耦合,且每个第三通道电路与输出具有第一频率的第二时钟信号的锁相环耦合;其中,所述第一频率与所述第二频率不同。

63.图5展示了本技术实施例提供的又一控制部件的示意图。

64.如图5所示,控制部件50包括锁相环51、分频器52、分频器53及8个通道电路(分别是通道电路1、通道电路2、通道电路3、通道电路4、通道电路5、通道电路6、通道电路7和通道电路8)。可选地,控制部件50包括2个以上的分频器。

65.分频器52与分频器53与锁相环51耦合。分频器52及分频器53均与8 个通道电路耦合。锁相环51接收外部输入的第一时钟信号,并根据配置信息,对第一时钟信号进行调整,并生成第二时钟信号。分频器51及分频器52均获取锁相环51生成的第二时钟信号。分频器51及分频器52根据配置信息,对第二时钟信号进行调整,生成第三时钟信号,所述第三时钟信号的频率与所述第二时钟信号的频率相同或不同。本实施例中,配置信息指示了每个分频器的分频倍数z,z为正整数。例如,在z=1时,第二时钟信号的频率为 3ghz,则第三时钟信号的频率为3ghz/1=3ghz,又如z=10时,第三时钟信号的频率为3ghz/10=0.3ghz。例如,分频器52向通道电路1、3、5和7输出第三时钟信号,分频器53向通道电路2、4、6和8输出第三时钟信号,且分频器52及分频器53输出的第三时钟信号相同或不同。

66.可选地,在每个通道电路均与每个分频器耦合时,每个通道电路均接收至少两种不同频率的第三时钟信号。例如,分频器52及分频器53均向8个通道电路输出第三时钟信号,分频器52输出的时钟信号的频率为30mhz,而分频器53输出的第三时钟信号的频率为3ghz。

67.图6展示了本技术实施例提供的又一控制部件的示意图。

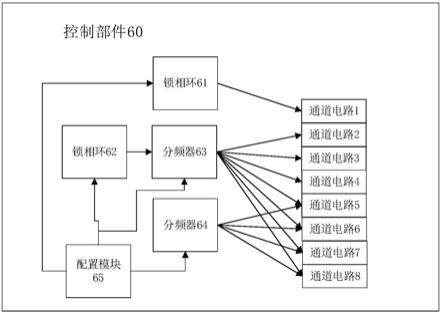

68.如图6所示,控制部件60包括锁相环61、锁相环62、分频器63、分频器64、配置模块65及8个通道电路(分别是通道电路1、通道电路2、通道电路3、通道电路4、通道电路5、通道电路6、通道电路7和通道电路8)。可选地,控制部件60包括2个以上的分频器和/或2个以上的锁相环。

69.本实施方式中,锁相环62与分频器63及分频器64耦合,配置模块65 与锁相环61、锁相环62、分频器63及分频器64耦合。配置模块64维护配置信息,配置模块65提供接口接收外部发送的配置信息更新命令。响应于获取到配置信息更新命令,配置模块65更新自身存储的配置信息。配置模块 65向至少一个锁相环和/或至少一个分频器发送更新后的配置信息。响应于获取到更新后的配置信息,至少一个锁相环生成第二时钟信号和/或至少一个分频器生成第三时钟信号。即配置模块65除了管理自身存储的配置信息,还在配置信息发生变更时,指示控制部件内的锁相环和分频器重新生成时钟信号,从而保证时钟信号的时效性。

70.进一步可选地,本技术的所有实施例中的控制部件均可设置如上述实施方式中的配置模块。

71.例如,锁相环61与通道电路1耦合,分频器63与通道电路2至通道电路 4耦合,分频器64与通道电路5至通道电路8耦合。通道电路5

‑

8是第四通道电路,通道电路2至通道电路4为第五通道电路。每个第四通道电路与输出具有第三频率的第三时钟信号的分频器耦合,即分频器64。每个第五通道电路与输出具有第四频率的第三时钟信号的分频器耦合,即分

频器63。所述第三频率与所述第四频率不同。

72.可选地,继续参见图6,例如通道电路2

‑

4是第四通道电路,通道电路5 至通道电路8为第六通道电路。每个第四通道电路与输出具有第三频率的第三时钟信号的分频器63耦合;每个第六通道电路与输出具有第四频率的第三时钟信号的分频器64耦合,且每个第六通道电路与输出具有第三频率的第三时钟信号的分频器63耦合;其中,所述第三频率与所述第四频率不同。

73.进一步可选地,8个通道电路包括至少一个第四通道电路、至少一个第五通道电路和至少一个第六通道电路;其中,每个第四通道电路与输出具有第三频率的第三时钟信号的分频器耦合;每个第五通道电路与输出具有第四频率的第三时钟信号的分频器耦合;每个第六通道电路与输出具有第四频率的第三时钟信号的分频器耦合,且每个第六通道电路与输出具有第三频率的第三时钟信号的分频器耦合;其中,所述第三频率与所述第四频率不同。

74.图7展示了本技术实施例提供的又一控制部件的示意图。

75.如图7所示,控制部件70包括锁相环71、分频器72、分频器73、8个通道电路(分别是通道电路1、通道电路2、通道电路3、通道电路4、通道电路5、通道电路6、通道电路7和通道电路8)及4个多路复用器(分别是多路复用器1、多路复用器2、多路复用器3及多路复用器4)。

76.所述至少一个多路复用器将锁相环和/或分频器耦合到所述多个通道电路,例如图7中的4个多路复用器将分频器72和73耦合到4个通道电路。本实施例中,多路复用器用于将多个时钟信号中的一个时钟信号输入通道电路,从而使得每个通道电路仅收到1个时钟信号。

77.进一步,所述至少一个多路复用器的数量与有多个时钟信号输入的通道电路数量相等,每个多路复用器与有多个时钟信号输入的通道电路一一对应。例如,图7中通道电路1

‑

4的前端不需要设置多路复用器是因为本身输入的时钟信号只有1个。

78.进一步可选地,每个多路复用器根据指示信号选通多个时钟信号中的一个时钟信号,所述指示信号指示多个时钟信号的序号/输入位置。例如,图7中的多路复用器2根据指示信号选通时钟信号,在指示信号的取值为0时,多路复用器2选通分频器72的时钟信号;在指示信号的取值为1时,多路复用器2选通分频器73的时钟信号。或者,在指示信号的取值为1时,多路复用器2选通分频器72的时钟信号;在指示信号的取值为0时,多路复用器2 选通分频器73的时钟信号。

79.图8示出了本技术实施例提供的固态存储设备80的示意图。

80.如图8所示,固态存储设备80包括控制部件40和8个通道(分别是通道 1、通道2、

……

、通道7和通道8)。其中,通道电路1与通道2耦合,通道电路2与通道1耦合,通道电路3与通道3耦合,通道电路4与通道4耦合,通道电路5与通道8耦合,通道电路6与通道5耦合,通道电路7与通道6耦合,通道电路8与通道7耦合。本实施例中仅以固态存储设备80包括控制部件40为例,固态存储设备80可以包括上述实施例中的任意一种控制部件。

81.每个通道包括至少一个nvm芯片。例如图8中每个通道包括2个nvm 芯片。又如,通道1包括1个nvm芯片,通道2包括2个nvm芯片,通道3包括3个芯片,通道4

‑

通道8均包括4个nvm芯片。控制部件40包括 8个通道电路,控制部件40通过8个通道电路与8个通道耦合,即控制部件 40通过8个通道电路与多个nvm芯片耦合。多个nvm芯片包括至少一个第一nvm芯

片和至少一个第二nvm芯片。本实施例中第一nvm芯片为第一通道电路耦合的通道中的nvm芯片,第二nvm芯片为第二通道电路耦合的通道中的nvm芯片。例如,第一通道电路为通道电路5,第二通道电路为通道电路4,则第一nvm芯片为通道8中的两个nvm芯片,第二nvm 芯片为通道4中的两个nvm芯片。第一容量为通道8中的两个nvm芯片的容量之和,第一容量为通道4中的两个nvm芯片的总容量,且第一容量不等于第二容量。

82.可选地,若第一容量大于第二容量,输入第一nvm芯片的时钟信号的频率大于输入第二nvm芯片的时钟信号的频率。若第一容量小于第二容量,输入第一nvm芯片的时钟信号的频率小于输入第二nvm芯片的时钟信号的频率。根据本技术的实施例,频率高的通道相比于频率低的通道有更高的数据传输带宽。通过为耦合容量之和更大的nvm芯片的通道提供更高频率的时钟,使得不同的通道之间的均衡性很好。均衡性代表例如通过各通道对 nvm芯片访问请求的处理延迟。

83.进一步可选地,例如第一容量为m,第二容量为n,输入第一nvm芯片的时钟信号的频率为x,输入第二nvm芯片的时钟信号的频率为y,使得x/y=m/n;其中,m、n、x、y均为正数。本实施方式提供了一种频率的设置方式,在x/y=m/n时,不同通道之间的均衡性最佳。

84.虽然当前申请参考的示例被描述,其只是为了解释的目的而不是对本技术的限制,对实施方式的改变,增加和/或删除可以被做出而不脱离本技术的范围。

85.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。