一种基于嵌入式集成上下拉电阻ipd的sip封装结构

技术领域

1.本发明涉及封装集成技术领域,特别涉及一种基于嵌入式集成上下拉电阻ipd的sip封装结构。

背景技术:

2.随着集成电路制造技术向更小的工艺节点发展,同时系统功能要求向着更强大发展,在单个集成电路芯片上设计整个系统变得越来越具有挑战性,sip正在逐渐成为一种替代方案。

3.为了满足日益增长的系统功能要求,集成到sip里的裸芯片数量也在不断攀升,与之匹配的上下拉电阻数量也在不断增加,给sip的走线和小型化带来了比较大的压力。

技术实现要素:

4.本发明的目的在于提供一种基于嵌入式集成上下拉电阻ipd的sip封装结构,以解决目前sip系统越来越难实现小型化、轻型化、通用化的问题。

5.为解决上述技术问题,本发明提供了一种基于嵌入式集成上下拉电阻ipd的sip封装结构,包括:封装基板,其内部嵌入有嵌入式集成上下拉电阻ipd;芯片,安装在所述封装基板顶部;印刷电路板,安装在所述封装基板底部。

6.可选的,通过粘合层将嵌入式集成上下拉电阻ipd安装在封装基板中的背面导体上。

7.可选的,所述嵌入式集成上下拉电阻ipd的侧面留有腔体。

8.可选的,所述芯片的数量为2个,分别为第一芯片和第二芯片。

9.可选的,所述第一芯片和所述第二芯片通过第一焊锡与所述嵌入式集成上下拉电阻ipd连接;信号通过所述第一焊锡和所述嵌入式集成上下拉电阻ipd在所述第一芯片和所述第二芯片之间传输。

10.可选的,所述第一芯片通过第一焊锡、连线一与所述嵌入式集成上下拉电阻ipd连接;所述第二芯片通过第一焊锡、连线二与所述嵌入式集成上下拉电阻ipd连接。

11.可选的,所述封装基板通过第二焊锡与所述印刷电路板连接。

12.可选的,所述封装基板和所述第一芯片、所述第二芯片之间还设有第三焊锡,所述第三焊锡与所述第二焊锡通过内部连线连接。

13.可选的,所述连线一与所述第二焊锡通过连线三连接,所述连线二与所述第二焊锡通过连线四连接;信号能够通过所述第一焊锡、所述嵌入式集成上下拉电阻ipd、所述连线三和所述第二焊锡实现信号在所述第一芯片、所述第二芯片和所述印刷电路板之间的传输。

14.在本发明提供的基于嵌入式集成上下拉电阻ipd的sip封装结构中,包括封装基

板、芯片和印刷电路板。所述封装基板的内部嵌入有嵌入式集成上下拉电阻ipd,完成多种不同电平的上拉及下拉功能;所述芯片安装在所述封装基板顶部;所述印刷电路板安装在所述封装基板底部。所述嵌入式集成上下拉电阻ipd可实现芯片电路端口的上拉、下拉偏置,将芯片的端口与电源端、地端的互连,可针对不同需求进行专用设计,连接方式固定之后不能进行改变。基于嵌入式集成上下拉电阻ipd的sip封装结构能够在很大程度上减小直线压力,减小布线层数;同时,几乎完成节省了sip里上下拉电阻的体积,很好的满足了sip小型化、轻型化、通用化的需求。

附图说明

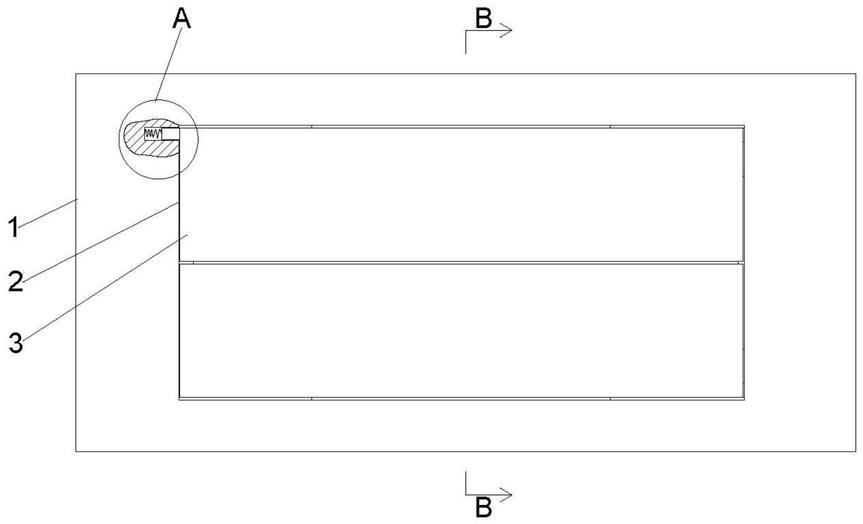

15.图1是本发明提供的基于嵌入式集成上下拉电阻ipd的sip封装结构的横截面侧视图;图2是多芯片封装的横截面侧视图;图3是单颗嵌入式集成上下拉电阻版图。

具体实施方式

16.以下结合附图和具体实施例对本发明提出的一种基于嵌入式集成上下拉电阻ipd的sip封装结构作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

17.实施例一本发明提供了一种基于嵌入式集成上下拉电阻ipd的sip封装结构,其横截面侧视图如图1所示,包括封装基板100、芯片和印刷电路板140。所述封装基板100的内部嵌入有嵌入式集成上下拉电阻ipd 120,完成多种不同电平的上拉及下拉功能;所述芯片安装在所述封装基板100顶部;所述印刷电路板140安装在所述封装基板100底部。所述嵌入式集成上下拉电阻ipd 120可实现芯片电路端口的上拉、下拉偏置,将芯片的端口与电源端、地端的互连,可针对不同需求进行专用设计,连接方式固定之后不能进行改变。

18.如图2所示为多芯片封装的横截面侧视图,在制造封装基板100时,通过粘合层214将嵌入式集成上下拉电阻ipd 120安装在封装基板100中的背面导体210上;为所述嵌入式集成上下拉电阻ipd 120提供上下拉电压;也可以通过粘合层214和导电胶216与其他嵌入式专用桥片的电源层连接,从而为嵌入式集成上下拉电阻ipd 120提供上下拉电压。为了减小嵌入式集成上下拉电阻ipd 120和封装基板100之间的热膨胀系数差异,所述嵌入式集成上下拉电阻ipd 120的侧面留有腔体212,能够降低嵌入式集成上下拉电阻ipd 120上的热应力。

19.请继续参阅图1,所述芯片的数量为2个,分别为第一芯片101和第二芯片103;所述第一芯片101和所述第二芯片103通过第一焊锡107与所述嵌入式集成上下拉电阻ipd 120连接;信号通过所述第一焊锡107和所述嵌入式集成上下拉电阻ipd 120在所述第一芯片101和所述第二芯片103之间传输。所述第一芯片101通过第一焊锡107、连线一122与所述嵌入式集成上下拉电阻ipd 120连接;所述第二芯片103通过第一焊锡107、连线二126与所述嵌入式集成上下拉电阻ipd 120连接。

20.所述封装基板100通过第二焊锡109与所述印刷电路板140连接。所述封装基板100和所述第一芯片101、所述第二芯片103之间还设有第三焊锡105,所述第三焊锡105与所述第二焊锡109通过内部连线112连接。所述连线一122与所述第二焊锡109通过连线三114连接,所述连线二126与所述第二焊锡109通过连线四115连接;信号能够通过所述第一焊锡107、所述嵌入式集成上下拉电阻ipd 120、所述连线三114和所述第二焊锡109实现信号在所述第一芯片101、所述第二芯片103和所述印刷电路板140之间的传输。

21.所述第一焊锡107、所述第二焊锡109和所述第三焊锡105可以为焊锡球,也可以为焊锡凸点。所述连线一122、所述连线二126、所述连线三114和所述内部连线112可根据电流的大小采用不同线宽设计,可以直接提高电阻的功率。嵌入式集成上下拉电阻ipd针对不同的应用需求可进行专用设计,为适应不同需求,嵌入式集成上下拉电阻ipd可嵌入到封装基板的表层,也可在内部使用。

22.单颗嵌入式集成上下拉电阻ipd的结构示意图如图3所示。其中1、4为电阻的焊盘,2为电阻的电阻体、3为电阻阻值的修调区。

23.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

技术特征:

1.一种基于嵌入式集成上下拉电阻ipd的sip封装结构,其特征在于,包括:封装基板(100),其内部嵌入有嵌入式集成上下拉电阻ipd(120);芯片,安装在所述封装基板(100)顶部;印刷电路板(140),安装在所述封装基板(100)底部。2.如权利要求1所述的基于嵌入式集成上下拉电阻ipd的sip封装结构,其特征在于,通过粘合层(214)将嵌入式集成上下拉电阻ipd(120)安装在封装基板(100)中的背面导体(210)上。3.如权利要求2所述的基于嵌入式集成上下拉电阻ipd的sip封装结构,其特征在于,所述嵌入式集成上下拉电阻ipd(120)的侧面留有腔体(212)。4.如权利要求3所述的基于嵌入式集成上下拉电阻ipd的sip封装结构,其特征在于,所述芯片的数量为2个,分别为第一芯片(101)和第二芯片(103)。5.如权利要求4所述的基于嵌入式集成上下拉电阻ipd的sip封装结构,其特征在于,所述第一芯片(101)和所述第二芯片(103)通过第一焊锡(107)与所述嵌入式集成上下拉电阻ipd(120)连接;信号通过所述第一焊锡(107)和所述嵌入式集成上下拉电阻ipd(120)在所述第一芯片(101)和所述第二芯片(103)之间传输。6.如权利要求5所述的基于嵌入式集成上下拉电阻ipd的sip封装结构,其特征在于,所述第一芯片(101)通过第一焊锡(107)、连线一(122)与所述嵌入式集成上下拉电阻ipd(120)连接;所述第二芯片(103)通过第一焊锡(107)、连线二(126)与所述嵌入式集成上下拉电阻ipd(120)连接。7.如权利要求6所述的基于嵌入式集成上下拉电阻ipd的sip封装结构,其特征在于,所述封装基板(100)通过第二焊锡(109)与所述印刷电路板(140)连接。8.如权利要求7所述的基于嵌入式集成上下拉电阻ipd的sip封装结构,其特征在于,所述封装基板(100)和所述第一芯片(101)、所述第二芯片(103)之间还设有第三焊锡(105),所述第三焊锡(105)与所述第二焊锡(109)通过内部连线(112)连接。9.如权利要求8所述的基于嵌入式集成上下拉电阻ipd的sip封装结构,其特征在于,所述连线一(122)与所述第二焊锡(109)通过连线三(114)连接,所述连线二(126)与所述第二焊锡(109)通过连线四(115)连接;信号能够通过所述第一焊锡(107)、所述嵌入式集成上下拉电阻ipd(120)、所述连线三(114)和所述第二焊锡(109)实现信号在所述第一芯片(101)、所述第二芯片(103)和所述印刷电路板(140)之间的传输。

技术总结

本发明公开一种基于嵌入式集成上下拉电阻IPD的SIP封装结构,属于封装集成领域,包括封装基板、芯片和印刷电路板。所述封装基板的内部嵌入有嵌入式集成上下拉电阻IPD,完成多种不同电平的上拉及下拉功能;所述芯片安装在所述封装基板顶部;所述印刷电路板安装在所述封装基板底部。所述嵌入式集成上下拉电阻IPD可实现芯片电路端口的上拉、下拉偏置,将芯片的端口与电源端、地端的互连,可针对不同需求进行专用设计,连接方式固定之后不能进行改变。基于嵌入式集成上下拉电阻IPD的SIP封装结构能够在很大程度上减小直线压力,减小布线层数;同时,几乎完成节省了SIP里上下拉电阻的体积,很好的满足了SIP小型化、轻型化、通用化的需求。需求。需求。

技术研发人员:王金刚 王璟瑞 武亚恒

受保护的技术使用者:中科芯集成电路有限公司

技术研发日:2021.09.08

技术公布日:2021/12/7

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。