mos管高速高可靠性dfn封装引线框架及mos管

技术领域

1.本实用新型涉及技术领域,尤其涉及一种mos管高速高可靠性dfn封装引线框架及dfn封装的mos管。

背景技术:

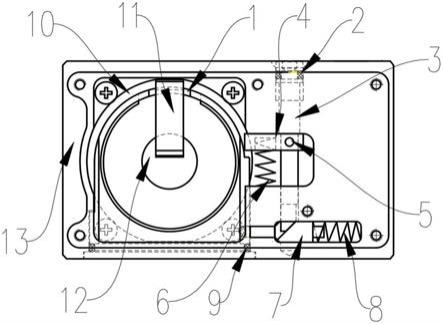

2.随着电子产品微小型、便携式的快速发展,例如智能手表、蓝牙耳机、小型检测设备等,再加上集成电路行业本身的成本方面的考虑,集成电路也快速向体积更小更薄的dfn、qfn产品发展。一部分厂家更直接要求封装厂将原先体积较大的sop8l产品设计封装成dfn、qfn产品,比如传统的一种mos管采用sop8l封装的体积为4.9*3.9*1.55mm,具体如图1和图2所示,每条引线框架上的引线框架单元数量仅为256粒,生产效率低,生产成本高,这对于封装厂来讲提出了更高的设计及制程可靠性要求。

技术实现要素:

3.本实用新型的目的在于提供一种mos管高速高可靠性dfn封装引线框架及dfn封装的mos管,采用dfn封装,体积小巧,而且降低了成本。

4.本实用新型是这样实现的:一种mos管高速高可靠性dfn封装引线框架,包括引线框架单元、支撑筋和切割道,每个引线框架单元至少包括一个基岛和两排管脚,两排管脚分布在基岛的二侧,所述基岛与部分管脚通过连筋连接。

5.其中,所述引线框架的基材为铜,上表层镀银。

6.其中,单条引线框架尺寸为258mm*78mm,承载的引线框架单元数量为2856粒,基岛尺寸为2.8*1.8mm。

7.其中,所述基岛两边均设有4个管脚,其中一排管脚的4个管脚均与基岛通过连筋连接。

8.其中,与基岛连接的4个管脚之间还通过侧面连筋半连接,另外一排管脚中的3个管脚之间也通过侧面连筋半连接,所述侧面连筋底面为半蚀刻。

9.本实用新型提供的另一种技术方案为:一种dfn封装的mos管,包括基岛、两排管脚、mosfet芯片、金属线和塑封体,两排管脚分布在基岛的二侧,所述基岛与部分管脚通过连筋连接,所述mosfet芯片通过导电胶固定在基岛上,基岛形成一个电路端口,mosfet芯片还通过金属线与其它管脚实现电气连接,所述塑封体用于包裹并保护基岛、管脚、mosfet芯片和金属线。

10.其中,所述mos管的封装尺寸为3.3*3.3*0.75mm。

11.其中,所述基岛两边均设有4个管脚,其中一排管脚中的4个管脚通过连筋与基岛连接。

12.其中,与基岛连接的4个管脚之间还通过侧面连筋半连接,另外一排管脚中的3个管脚之间也通过侧面连筋半连接,所述侧面连筋底面为半蚀刻。

13.其中,所述基岛和管脚的下表面露出塑封体,形成散热面。

14.本实用新型的有益效果为:采用dfn封装后,体积大幅变小,单个引线框架上承载的引线框架单元数量也大幅增加,极大的减少了塑封料、金属线、电镀等物料成本,提高了生产效率,能产生丰厚的利润回报。由于mos管发热量大,产品散热不良容易导致mos管的损坏,为了保证产品的可靠性,需要考虑散热问题,本技术人不使用普通dfn引线框架的基岛与管脚分离的设计方案,而是把基岛与部分管脚通过连筋连接,mosfet芯片产生的热量首先传导到基岛,基岛再通过这些管脚快速传导出来,相当于增大了散热面积,增强了产品整体散热性能,另外dfn封装超薄的封装厚度,也更利于产品的整体散热,满足了mos管产品的特殊散热要求,提高了产品寿命和可靠性。

附图说明

15.图1是现有技术中sop8l封装结构的俯视图;

16.图2是现有技术中sop8l封装结构的侧视图;

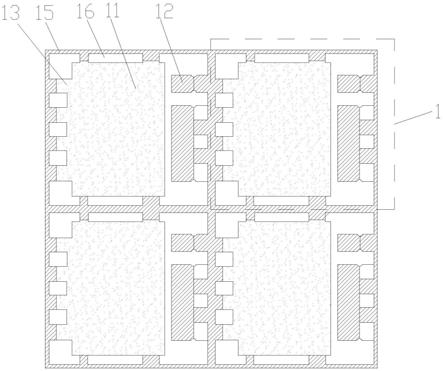

17.图3是本实用新型所述mos管高速高可靠性dfn封装引线框架的结构示意图(正面);

18.图4是本实用新型所述mos管高速高可靠性dfn封装引线框架的结构示意图(背面);

19.图5是本实用新型所述dfn封装的mos管的剖面示意图;

20.图6是本实用新型所述dfn封装的mos管的立体图。

21.1、引线框架单元;11、基岛;12、管脚;13、连筋;14、侧面连筋;15、支撑筋;16、切割道;2、mosfet芯片;3、金属线;4、塑封体;5、导电胶。

具体实施方式

22.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

23.作为本实用新型所述mos管高速高可靠性dfn封装引线框架的实施例,如图3和图4所示,包括引线框架单元1、支撑筋15和切割道16,每个引线框架单元1至少包括一个基岛11和两排管脚12,两排管脚12分布在基岛11的二侧,所述基岛11与部分管脚12通过连筋13连接。

24.作为本实用新型所述dfn封装的mos管的实施例,如图5和图6所示,包括基岛11、两排管脚12、mosfet芯片2、金属线3和塑封体4,两排管脚12分布在基岛11的二侧,所述基岛11与部分管脚12通过连筋13连接,所述mosfet芯片2通过导电胶5固定在基岛11上,基岛11形成一个电路端口,mosfet芯片2还通过金属线3与其它管脚实现电气连接,所述塑封体4用于包裹并保护基岛11、管脚12、mosfet芯片2和金属线3。

25.采用dfn封装后,体积大幅变小,单个引线框架上承载的引线框架单元1数量也大幅增加,极大的减少了塑封料、金属线、电镀等物料成本,提高了生产效率,能产生丰厚的利润回报。由于mos管发热量大,产品散热不良容易导致mos管的损坏,为了保证产品的可靠性,需要考虑散热问题,本技术人不使用普通dfn引线框架的基岛与管脚分离的设计方案,而是把基岛11与部分管脚12通过连筋13连接,mosfet芯片2产生的热量首先传导到基岛11,

基岛11再通过这些管脚12快速传导出来,相当于增大了散热面积,增强了产品整体散热性能,另外dfn封装超薄的封装厚度,也更利于产品的整体散热,满足了mos管产品的特殊散热要求,提高了产品寿命和可靠性。

26.在本实施例中,所述引线框架的基材为铜,上表层镀银(图3中沙点部分为镀银区)。可以增加mosfet芯片2与基岛11之间的导电性能。

27.在本实施例中,单条引线框架尺寸为258mm*78mm,承载的引线框架单元1数量为2856粒,相比原来sop8l封装结构,数量增加11倍,基岛尺寸为2.8*1.8mm,能够满足最大2.7*1.77mm芯片尺寸的mos管产品的应用。在本实施例中,所述基岛两边均设有4个管脚,其中一排管脚的4个管脚均与基岛通过连筋连接。所述mos管的封装尺寸为3.3*3.3*0.75mm。相对sop8l封装结构,体积缩小至27%。

28.在本实施例中,与基岛11连接的4个管脚之间还通过侧面连筋14半连接,另外一排管脚中的3个管脚之间也通过侧面连筋14半连接,所述侧面连筋14底面为半蚀刻(如图4中阴影部分所示)。在塑封时有塑封料注入,形成锁扣型结构,增强了基岛部分与塑封体部分的结合强度,进而增强整体产品的抗分层能力。

29.在本实施例中,所述基岛11和管脚12的下表面露出塑封体4,形成散热面,能够与应用端的pcb板紧密接触,也增强了产品整体散热性能。

30.以上所述仅为本实用新型的较佳实施例而已,并不用以限制本实用新型,凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本实用新型的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。