技术特征:

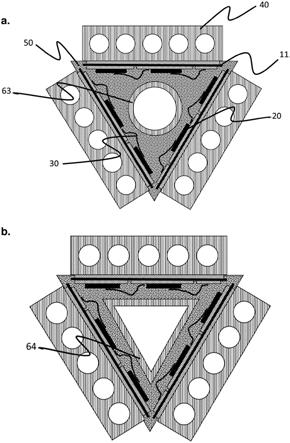

1.一种碳化硅半导体器件,具有碳化硅衬底,所述碳化硅衬底具有第一主面和与所述第一主面相反侧的第二主面,所述碳化硅衬底包含:第一杂质区,所述第一杂质区位于所述第一主面与所述第二主面之间,并且具有第一导电型;第二杂质区,所述第二杂质区位于所述第一主面与所述第二主面之间,与所述第一杂质区相接地设置,并且具有与所述第一导电型不同的第二导电型;第三杂质区,所述第三杂质区位于所述第一主面与所述第二主面之间,以与所述第一杂质区隔开的方式与所述第二杂质区相接地设置,并且具有所述第一导电型;第一超结部,所述第一超结部具有第一区和第二区,所述第一区与所述第一杂质区相接,位于所述第一杂质区与所述第二主面之间,并且具有所述第一导电型,所述第二区与所述第二杂质区和所述第一区各自相接,并且具有所述第二导电型;第四杂质区,所述第四杂质区位于所述第一主面与所述第二主面之间,并且具有所述第一导电型;第五杂质区,所述第五杂质区位于所述第一主面与所述第二主面之间,与所述第四杂质区相接地设置,并且具有所述第二导电型;第六杂质区,所述第六杂质区位于所述第一主面与所述第二主面之间,以与所述第四杂质区隔开的方式与所述第五杂质区相接地设置,并且具有所述第一导电型;和第二超结部,所述第二超结部具有第三区和第四区,所述第三区与所述第四杂质区相接,位于所述第四杂质区与所述第二主面之间,并且具有所述第一导电型,所述第四区与所述第五杂质区和所述第三区各自相接,并且具有所述第二导电型,所述第二区具有与所述第二杂质区相接的第一端面和与所述第一端面相反侧的第二端面,所述第四区具有与所述第五杂质区相接的第三端面和与所述第三端面相反侧的第四端面,所述第一区、所述第二区、所述第四区、所述第三区在与所述第二主面平行的第一方向上排列设置,所述第二区位于所述第一区与所述第四区之间,并且所述第四区位于所述第二区与所述第三区之间,所述第一主面中设置有第一沟槽,所述第一沟槽将所述第二区与所述第四区隔开,所述碳化硅半导体器件还具有第一绝缘体,所述第一绝缘体设置在所述第一沟槽的内部,在相对于所述第二主面垂直的方向上,所述第一沟槽的底面位于所述第二端面与所述第二主面之间,并且位于所述第四端面与所述第二主面之间。2.如权利要求1所述的碳化硅半导体器件,其中,所述第一区和所述第三区各自的杂质浓度为3

×

10

16

cm

‑3以上且3

×

10

17

cm

‑3以下。3.如权利要求1或权利要求2所述的碳化硅半导体器件,其中,在所述第一方向上将所述第一区的宽度设为第一宽度、将所述第二区的宽度设为第二宽度、并且将所述第一区的杂质浓度设为第一浓度、将所述第二区的杂质浓度设为第二浓

度的情况下,将其中所述第一浓度乘以所述第一宽度而得的值除以其中所述第二浓度乘以所述第二宽度而得的值,由此得到的值为0.5以上且1.5以下,并且在所述第一方向上将所述第三区的宽度设为第三宽度、将所述第四区的宽度设为第四宽度、并且将所述第三区的杂质浓度设为第三浓度、将所述第四区的杂质浓度设为第四浓度的情况下,将其中所述第三浓度乘以所述第三宽度而得的值除以其中所述第四浓度乘以所述第四宽度而得的值,由此得到的值为0.5以上且1.5以下。4.如权利要求3所述的碳化硅半导体器件,其中,所述第二宽度和所述第四宽度各自为0.2μm以上且2μm以下。5.如权利要求1~权利要求4中任一项所述的碳化硅半导体器件,其中,所述第一方向上所述第一沟槽的宽度为0.5μm以上且5μm以下。6.如权利要求1~权利要求5中任一项所述的碳化硅半导体器件,其中,所述第一沟槽的深度为1μm以上且100μm以下。7.如权利要求1~权利要求6中任一项所述的碳化硅半导体器件,其中,将所述第一沟槽的深度除以所述第一方向上所述第一沟槽的宽度而得到的值为0.5以上且25以下。8.如权利要求1~权利要求7中任一项所述的碳化硅半导体器件,其中,所述第一沟槽具有第一侧面和第二侧面,所述第一侧面与所述第二区相接并且从所述第二区朝向所述第一区凹陷,所述第二侧面与所述第四区相接并且从所述第四区朝向所述第三区凹陷。9.如权利要求8所述的碳化硅半导体器件,其中,在所述第一方向上,从所述第一区的最大宽度减去所述第一区的最小宽度而得到的值为0.05μm以上且2.0μm以下,并且在所述第一方向上,从所述第三区的最大宽度减去所述第三区的最小宽度而得到的值为0.05μm以上且2.0μm以下。10.如权利要求1~权利要求9中任一项所述的碳化硅半导体器件,其中,所述第一杂质区与所述第一区为一体,并且所述第四杂质区与所述第三区为一体。11.如权利要求1~权利要求10中任一项所述的碳化硅半导体器件,其中,所述第一主面中设置有第二沟槽,在相对于所述第二主面垂直的方向观察时所述第二沟槽包围所述第一沟槽,并且所述碳化硅半导体器件还具有第二绝缘体,所述第二绝缘体设置在所述第二沟槽的内部。12.一种碳化硅半导体器件的制造方法,具有:准备碳化硅外延衬底的工序,所述碳化硅外延衬底包含碳化硅单晶衬底和碳化硅外延层,所述碳化硅外延层设置在所述碳化硅单晶衬底上并且具有能够赋予第一导电型的杂质离子;在所述碳化硅外延层中形成沟槽的工序,所述沟槽具有第一侧面和与所述第一侧面相对的第二侧面;通过对所述第一侧面倾斜注入能够赋予第二导电型的杂质离子而形成第二区的工序;和通过对所述第二侧面倾斜注入能够赋予所述第二导电型的杂质离子而形成第四区的工序,

所述碳化硅外延层包含第一超结部和第二超结部,所述第一超结部具有所述第二区和具有所述第一导电型并且与所述第二区相接的第一区,所述第二超结部具有所述第四区和具有所述第一导电型并且与所述第四区相接的第三区,在相对于所述碳化硅单晶衬底与所述碳化硅外延层的边界面垂直的方向上,所述沟槽的底面位于所述第二区与所述碳化硅单晶衬底之间以及所述第四区与所述碳化硅单晶衬底之间,并且所述碳化硅半导体器件的制造方法还具有利用绝缘体填埋所述沟槽的工序。13.如权利要求12所述的碳化硅半导体器件的制造方法,其中,在所述形成第二区的工序和所述形成第四区的工序的各自中,对所述底面注入能够赋予所述第二导电型的杂质离子,并且所述碳化硅半导体器件的制造方法还具有通过蚀刻将对所述底面注入的能够赋予所述第二导电型的杂质离子除去的工序。14.如权利要求12所述的碳化硅半导体器件的制造方法,其中,在所述形成第二区的工序和所述形成第四区的工序的各自中,以不对所述底面注入能够赋予所述第二导电型的杂质离子的方式进行倾斜注入。

技术总结

碳化硅半导体器件具有碳化硅衬底、第一绝缘体、第一电极和第二电极。碳化硅衬底包含第一杂质区、第二杂质区、第三杂质区、第一超结部、第四杂质区、第五杂质区、第六杂质区和第二超结部。第一超结部具有第一区和第二区。第二超结部具有第三区和第四区。在相对于第二主面垂直的方向上,第一沟槽的底面位于第二端面与第二主面之间,并且位于第四端面与第二主面之间。间。间。

技术研发人员:增田健良

受保护的技术使用者:住友电气工业株式会社

技术研发日:2020.05.13

技术公布日:2021/12/3

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。